介绍一款基于MPC8548的数据处理板

- 格式:pdf

- 大小:4.12 MB

- 文档页数:9

飞思卡尔双核处理器MPC8572开发参考平台为帮助⽹络设备⼚商简化系统设计和构建智能应⽤⽹络,MICETEK推出基于MPC8572的开发板。

这套开发系统由MPC8572处理器卡(MPC8572PC)和Type-N载板(PQCBN)组成,使开发⼈员能快速⽅便搭建硬件平台,⼤⼤缩短开发周期,加快产品上市。

开发⼈员可以直接迅速得在此平台上进⾏软件设计和调试。

Type-N载板是⼀个MPC85XX系列处理器卡的通⽤I/O 平台。

它提供了千兆以太⽹接⼝,PCI插槽,PCI-Express插槽和串⼝等,⽤于⾼端⽹络通信应⽤,例如企业⽹络,电信传输和交换,3G⽆线架构,存贮和⾼端影像等市场。

我们同时提供Linux BSP给开发⼈员,包括U-BOOT,Linux kernel和⼀些底层接⼝驱动,另外还提供载板设计⽂件和处理器卡原理图(PDF⽂档)。

下图为MT8572-N实物照⽚。

MPC8572系列处理器能够提供⾼达1.2GHz到1.5GHz的设计时钟速率,采⽤了两个强⼤的e500处理器内核,通过增强型外围设备和⾼速互连技术,对处理器性能和I/O系统吞吐量进⾏平衡。

MPC8572基于飞思卡尔90nm规格的绝缘体硅芯⽚(SOI)铜连接制程技术,能够实现更⾼的性能和更低的功耗。

MPC8572在处理器性能⽅⾯有了极⼤的提⾼,并且代表了PowerQUICC 系列主流嵌⼊式处理器在不断创新过程中的最⾼⽔平。

通过⽆损化集成,MPC8572平台构建在⾼性能的嵌⼊式Power Architecture技术之上,加⼊了更多新的⾼级特性,增强了深度数据报检测、分类管理和安全加速等功能。

开发板主要性能:CPU: MPC8572 双e500内核,每个核主频最⾼可达1.333GHz;性能:6897 MIPS@1500 MHzMemory:— 512Mbytes DDR2 at 533MHz SDRAM— 8MBytes NOR flash memory at 16-bit port size— 32MBytes NAND flash memory in 8-bit mode接⼝:— 四个千兆以太⽹接⼝— 三个PCI 插槽— ⼀个PCI Express插槽— ⼀个RS-232 串⼝MPC8572处理器卡总体情况:— COP接⼝— 5V风扇连接器— 由载板提供的3.3V 和 5V 电源— 灵活的POR配置,由不同的拨码开关设置— 10层PCB布线— 尺⼨:147mm x 70.9mmType-N载板总体情况:— 由4pin连接器提供的12 V 和5 V 电源— 6层PCB布线— 尺⼨:220mm x 148mm这套开发系统由MPC8541E处理器卡(MPC8541EPC)和Type-N载板(PQCBN)组成,使开发⼈员能快速⽅便搭建硬件平台,⼤⼤缩短开发周期,加快产品上市。

2008年第 4 期 声学与电子工程 总第 92 期40PowerPC平台引导加载程序的移植张 磊(第七一五研究所,杭州,310012)摘要引导加载程序(Boot Loader)是嵌入式系统软件开发的第一个环节,它把嵌入式操作系统和硬件平台衔接在一起,对于嵌入式系统的后续开发起到十分重要的作用。

U-Boot是目前比较流行且功能强大的Boot Loader,支持种类繁多的体系结构,尤其对PowerPC提供了完善的支持。

MPC8548E是基于E500v2内核,并提供多种接口控制器的处理器。

详细介绍了在基于MPC8548 CPU 的SBC8548E开发板上Boot Loader的移植过程。

关键词引导加载;程序设计;程序移植引导加载程序(Boot Loader)是用来启动设备以及执行内核加载的系统软件组件,配置Boot Loader是所有嵌入式操作系统的一项必要工作。

Linux内核有许多Boot Loader可用,不同架构之间的Boot Loader的质和量也有很大的差异。

Das U-Boot(一般称为U-Boot)被认为是功能最多、最具有弹性以及开发最积极的开放源码Boot Loader。

而基于E500内核的PowerPC芯片是Freescale公司未来高端通信领域的发展方向。

因此研究分析基于E500内核的U-Boot对于深入理解PowerPC架构以及开发后续嵌入式操作系统Linux具有积极的意义。

1 U-Boot移植过程分析MPC8548E是基于E500v2内核的处理器,支持36-bit实地址模式(物理寻址能力达到64 GB,虚拟寻址能力达到1TB)和双精度浮点运算[1],支持DDR2 SDRAM、PCI-X、PCI-E和RapidIO高速串行总线。

主要适用在收发基站(BTS)、媒体网关(MGW)、无线网络控制(RNC)、刀片服务器等网络通信高端领域,同时在工业控制领域也有着广泛的应用。

但是对于应用程序开发人员来说,要想充分发挥其性能就需要深入理解E500内核和外围器件接口的全部寄存器配置和外围总线使用方法,开发难度较大。

整个系统的硬件具高成熟度、高稳定度、高安全性、高集成度特性。

板集成度很高,采用14层的PCB。

PCB使用等级为FR-阻燃材料制成。

为确保系统的稳定性,选用芯片都采用业界成熟稳定的芯片,主芯片信息介绍如下:CPU芯片采用飞思卡尔公司的MPC 8548,MPC8548它基于Freescale(飞思卡尔)的PowerPC架构的PowerQuicc III处理器,同时兼容MPC8548E,MPC8547E、PC8545E、MPC8543E系列处理器,其强大的处理能力特别适合于高速低时延的处理。

基本特性如下:(1)处理器:Freescale PowerQuiccIII MPC8548E、MPC8547E、MPC8545E、MPC8543E系列处理器,最高频率1.5GHz(2)内存:最高2GByte DDR2 SDRAM(3)Flash:最高512KByte + 64MByte*2 + 1GByte。

支持从表贴大Flash直接启动以支持抗震指标基带芯片采用德州仪器(TI)的TMS320TCI6487,6487是并行频率高达3.6 GHz 的三核数字信号处理器,它完美结合了功能强大的软件库,全面优异的性能足以满足TD-SCDMA/TD-LTE 等复杂基带算法要求。

基本特性如下:(1)TCI6487 包括三个运行频率均为1.2 GHz 的DSP 内核。

(2)每个内核都拥有自己专用的1 Mb L2、32k L1 数据以及程序高速缓存,从而不仅可最大限度地减少片外存储器存取,还能实现高效率的软件架构。

(3)TI 简单易用的高效率编译器工具可显著节约开发与测试最新软件特性所需的时间。

(4)TCI6487 包含额外的高性能加速器和外设接口,并为蜂窝式基础局端产品进行了优化。

TI DSP 高度的灵活性与优异的简单易用性非常适用于多标准设计,也能作为多种目标设计的核心技术。

(5)除LTE 软件库之外,TI 还针对WiMAX 和WCDMA 提供了优化库,可进一步支持多标准开发。

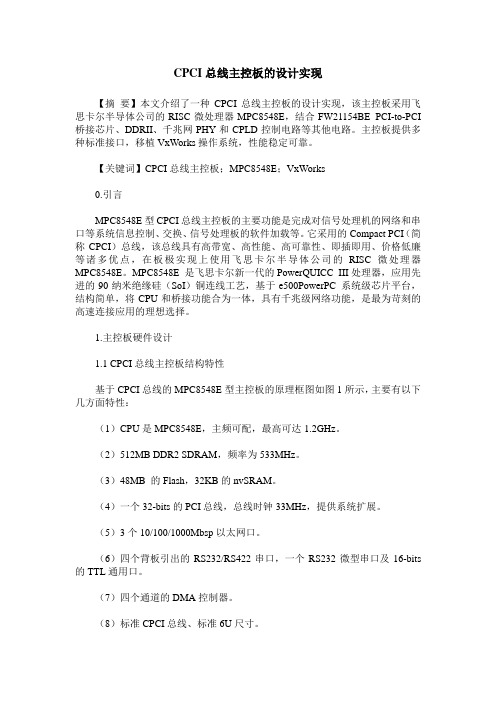

CPCI总线主控板的设计实现【摘要】本文介绍了一种CPCI总线主控板的设计实现,该主控板采用飞思卡尔半导体公司的RISC微处理器MPC8548E,结合FW21154BE PCI-to-PCI 桥接芯片、DDRII、千兆网PHY和CPLD控制电路等其他电路。

主控板提供多种标准接口,移植VxWorks操作系统,性能稳定可靠。

【关键词】CPCI总线主控板;MPC8548E;VxWorks0.引言MPC8548E型CPCI总线主控板的主要功能是完成对信号处理机的网络和串口等系统信息控制、交换、信号处理板的软件加载等。

它采用的Compact PCI(简称CPCI)总线,该总线具有高带宽、高性能、高可靠性、即插即用、价格低廉等诸多优点,在板极实现上使用飞思卡尔半导体公司的RISC 微处理器MPC8548E。

MPC8548E 是飞思卡尔新一代的PowerQUICC III处理器,应用先进的90纳米绝缘硅(SoI)铜连线工艺,基于e500PowerPC 系统级芯片平台,结构简单,将CPU和桥接功能合为一体,具有千兆级网络功能,是最为苛刻的高速连接应用的理想选择。

1.主控板硬件设计1.1 CPCI总线主控板结构特性基于CPCI总线的MPC8548E型主控板的原理框图如图1所示,主要有以下几方面特性:(1)CPU是MPC8548E,主频可配,最高可达1.2GHz。

(2)512MB DDR2 SDRAM,频率为533MHz。

(3)48MB 的Flash,32KB的nvSRAM。

(4)一个32-bits的PCI总线,总线时钟33MHz,提供系统扩展。

(5)3个10/100/1000Mbsp以太网口。

(6)四个背板引出的RS232/RS422串口,一个RS232微型串口及16-bits 的TTL通用口。

(7)四个通道的DMA控制器。

(8)标准CPCI总线、标准6U尺寸。

(9)工作环境温度:-40℃-+80℃。

(10)功耗:CPU工作频率533MHz,整板功耗约11W。

基于MPC8548E的嵌入式数据处理系统设计

纪雄飞

【期刊名称】《现代导航》

【年(卷),期】2012(003)005

【摘要】提出了一种基于PowerPC的嵌入式数据处理系统设计方案,该方案以MPC8548E处理器为核心,详细阐述了系统的硬件设计和软件设计流程.

【总页数】6页(P373-378)

【作者】纪雄飞

【作者单位】中国电子科技集团公司第二十研究所,西安710068

【正文语种】中文

【中图分类】TP273

【相关文献】

1.基于嵌入式及触摸技术的核谱数据处理系统设计 [J], 杨忠;魏涛

2.基于MPC8548E的嵌入式实时系统自举优化设计 [J], 孙亮;杨斌;钟瑜

3.基于MPC8548E的通用嵌入式计算机平台系统软件研究和实现 [J], 李文光

4.基于MPC8548E的通用嵌入式计算机平台系统软件研究和实现 [J], 庞春辉

5.基于嵌入式的电脑横机数据处理系统设计 [J], 项贤军;马东玲

因版权原因,仅展示原文概要,查看原文内容请购买。

PowerPC处理器MPC8548E的DDR2接口实现

苏鹏;卞春江;张磊

【期刊名称】《微计算机信息》

【年(卷),期】2010(026)035

【摘要】本论文研究了DDR2的特性和M PC8548 E处理器的相关资料,给出了MPC8548E DDR2接口的硬件电路设计,并且通过实例讨论了在U-Boat下对MPC8548 E相关寄存器的配置,给出了试验结果.

【总页数】3页(P174-176)

【作者】苏鹏;卞春江;张磊

【作者单位】100190,北京,中国科学院空间科学与应用研究中心;100190,北京,中国科学院研究生院;100190,北京,中国科学院空间科学与应用研究中心;100190,北京,中国科学院空间科学与应用研究中心

【正文语种】中文

【中图分类】TN368

【相关文献】

1.基于FPGA的嵌入式处理器与PC/104总线接口实现 [J], 韩鸿凌

2.基于FPGA的嵌入式处理器与PC/104总线接口实现 [J], 韩鸿凌

3.基于POWERPC的ARINC429总线接口实现 [J], 李兴旺;颜国正;沈勇

4.Tundra向市场投放第一款用于PowerPC的DDR2内存支持的主桥 [J],

5.PMC—Sierra新推1.8GHz主频双CPU核64位MIPS—Powered多处理器——第三代多处理器RM11200增加了新CPU核心、PCI Express和DDR2 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

DDR2 SDRAM介绍及其基于MPC8548 CPU的硬件设计2009-02-26 01:35:44 文章出处:与非网DDR2 SDRAM芯片提供一个ODT引脚来控制开或关芯片内部的终结电阻。

在只有一个DDR2 SDRAM芯片作为存储器控制器的负载的情况下,写操作时,由于DDR2 SDRAM作为接收端,所以ODT引脚为高电平以打开芯片内部终结电阻DDR2 SDRAM引入的新技术DDR2(Double Data Rate 2,两倍数据速率,版本2) SDRAM,是由JEDEC标准组织开发的基于DDR SDRAM的升级存储技术。

相对于DDR SDRAM,虽然其仍然保持了一个时钟周期完成两次数据传输的特性,但DDR2 SDRAM在数据传输率、延时、功耗等方面都有了显著提高,而这些性能的提高,主要来源于以下技术的提升:ODT,Post CAS,4n数据预取,封装等。

ODTODT(On-Die Termination),即芯片内部匹配终结。

在DDR SDRAM应用中,需要通过大量的外部电阻上拉到VTT电平(1.25V)以实现信号匹配,以16位芯片为例,以下信号需要通过这种方式进行匹配:CK,CK#,DQ[15:0],LDQS,UDQS, ADDR[10:0],RAS#,CAS#,WE#,即一片芯片需要34个外部上拉电阻,极大的占用了宝贵的PCB面积。

同时,由于DQ[15:0],LDQS,UDQS等信号是双向信号,即读和写时,对匹配电阻的位置有不同要求,因此在电阻布局时很难在两个方向上同时实现最佳的信号完整性。

在DDR2 SDRAM中,采用ODT技术将许多外部的匹配电阻移到芯片内部从而节省了大量的PCB板上面积。

另外,ODT技术允许存储控制器(如下文的MPC8548 CPU)通过配置DDR2 SDRAM的内部寄存器以及控制ODT信号,来实现对匹配电阻的值及其开关状态进行控制,从而可以实现读,写操作时最佳的信号完整性。