微机原理(8086指令系统)

- 格式:doc

- 大小:475.00 KB

- 文档页数:20

微机原理及应⽤(陈继红、徐晨)课后习题答案微机原理及应⽤(陈继红、徐晨)课后习题答案第三章8086/8088指令系统和寻址⽅式习题答案(部分)3.1总结计算机中⼗进制、⼆进制、⼋进制及⼗六进制数的书写形式。

123D、0AFH、77Q、1001110B分别表⽰什么计数制的数?答案:123D、0AFH、77Q、1001110B分别表⽰⼗进制、⼗六进制、⼋进制、⼆进制。

3.2字长为8位、16位⼆进制数的原码、补码表⽰的最⼤数和最⼩数分别是什么?答案:8位原码表⽰的最⼤数:(27-1)、8位补码表⽰的最⼤数:(27-1)、8位原码表⽰的最⼩数:-(27-1)、8位补码表⽰的最⼩数-27。

16最⼩数:-215。

3.3答案:7DH。

(2)255(3)7248H。

(4)509013E2H。

3.4答案:240D0F0H。

128D80H。

(3)11111111⼗进制数:255D;⼗六进制数:0FFH。

(4)01010101⼗进制数:85D;⼗六进制数:55H。

3.5把下列⽆符号⼗六进制数分别转换为⼗进制数和⼆进制数。

(1)FF(2)ABCD(3)123(4)FFFF答案:(1)FF⼗进制数:255D;⼆进制数;11111111B。

1010101111001101B。

(3)123⼗进制数:291D;⼆进制数;000100100011B。

(4)FFFF⼗进制数:65535D;⼆进制数;1111111111111111B。

3.6分别⽤8位⼆进制数和16位⼆进制数写出下列⼗进制数的原码和补码。

(1)16(2)-16(3)+0(4)-0(5)127(6)-128(7)121(8)-9 答案:(1)16800010000(2)-16800010000(3)+0800000000(4)-0800000000(5)127801111111(6)-128810000000(7)1218:01111001;16位⼆进制数原码:0000000001111001补码:0000000001111001。

西北师范大学计算机科学与技术系版权声明本电子教案内容为西北师范大学计算机科学系微机原理与汇编语言课讲义,大家可以自己个人使用。

但由于本教案同时也部分使用了其他人所写讲义或CAI课件的内容,因此禁止使用本材料进行任何商业性或赢利性活动。

同时作者不承担由于使用本教案而引发的其他连带责任。

转载时请保留本版权声明。

-索国瑞suogr@8086微处理器❑概要❑功能结构❑基本执行环境❑基本编程寄存器❑存储器组织❑I/O端口组织概要❑8086微处理器由Intel公司于1978年推出的16位微处理器,随后被IBM公司用于新开发的IBM PC微型计算机上,由此奠定其MPU霸主地位❑8086采用HMOS工艺制造,约含29000个晶体管❑8086有16根数据线和20根地址线,可寻址1MB 内存空间❑8086工作时只要单一的5V电源和单相时钟,时钟频率为5MHz。

❑8086CPU已经发展成为一个系列,其早期的系列成员以16位微处理器8086和准16位微处理器8088为基础,加上各种支持芯片,以及一些提升系统功能的协处理器(如8087、8089)等组成。

❑从8086开始,Intel 先后推出了80286、80386、80486、Pentium、Pentium MMX、Pentium PRO、PII、PIII、PIV微处理器,形成了80X86系列,其基本设计结构被称为IA-32结构❑新的IA-64结构也正在推出,目前已经投入实际运行的有安腾-itenium系列CPU,并且开始出现具有双内核的CPU❑INTEL公司80X86架构系列CPU发展简图 4004:1971年,4位,2300晶体管/片,640B存储器8080:1974年,8位,6000晶体管/片,64KB存储器8086:1978年,16位,29000晶体管/片,1M存储器,奠定了最基本的X86汇编指令集 80286:1982年,16位,134000晶体管,16MB存储器80386:1985年,32位,32位总线,275000晶体管,4GB存储器,速度5 MIPS,IA-3280486:1989年,32位,1.2M晶体管,片内数学协处理器Pentium:1993年,32位数据路径,64位总线,3.1M晶体管,2路超标量流水线,深度5,速度90 MIPS,4GB存储器Pentium Pro:1995年,64位数据路径,64位总线,5.5M晶体管,3路超标量流水线,深度12,速度300MIPS,架构属P6,64GB存储器Pentium II:1997年,32位,7.5M晶体管,加MMX指令,开始出现XEON、K6芯片Pentium III:1999年,64位1Gbps系统总线,9.5M系统晶体管,SSE指令,超标量流水线处理机,深度10Pentium IV:2000年,64位32Gbps系统总线,42M晶体管,SSE2指令,超标量处理机,深度至少为20,以上为IA-32结构Itanium :2001年,IA-64结构,10级深度流水线16TB存储器,开始在服务器领域应用 Itanium II:……在推出Intel 8086的同时,Intel公司还推出了Intel 8088。

![微机原理(杭州电子科技大学【4】8086系统结构[2-3]](https://uimg.taocdn.com/3b8cd1f4f90f76c661371a65.webp)

![[微机原理课件].ch5-2](https://uimg.taocdn.com/1feeac3f5727a5e9856a61a7.webp)

第3章8086/8088指令系统与寻址方式习题3.3 8086系统中,设DS=1000H,ES=2000H,SS=1200H,BX=0300H,SI=0200H,BP=0100H,VAR的偏移量为0600H,请指出下列指令的目标操作数的寻址方式,若目标操作数为存储器操作数,计算它们的物理地址。

(1)MOV BX,12 ;目标操作数为寄存器寻址(2)MOV [BX],12 ;目标操作数为寄存器间址 PA=10300H(3)MOV ES:[SI],AX ;目标操作数为寄存器间址 PA=20200H(4)MOV VAR,8 ;目标操作数为存储器直接寻址 PA=10600H(5)MOV [BX][SI],AX ;目标操作数为基址加变址寻址 PA=10500H(6)MOV 6[BP][SI],AL ;目标操作数为相对的基址加变址寻址 PA=12306H (7)MOV [1000H],DX ;目标操作数为存储器直接寻址 PA=11000H(8)MOV 6[BX],CX ;目标操作数为寄存器相对寻址 PA=10306H(9)MOV VAR+5,AX ;目标操作数为存储器直接寻址 PA=10605H3.4 下面这些指令中哪些是正确的?那些是错误的?如果是错误的,请说明原因。

(1)XCHG CS,AX ;错,CS不能参与交换(2)MOV [BX],[1000] ;错,存储器之不能交换(3)XCHG BX,IP ;错,IP不能参与交换(4)PUSH CS(5)POP CS ;错,不能将数据弹到CS中(6)IN BX,DX ;输入/输出只能通过AL/AX(7)MOV BYTE[BX],1000 ;1000大于255,不能装入字节单元(8)MOV CS,[1000] ;CS不能作为目标寄存器(9)MOV BX,OFFSET VAR[SI] ;OFFSET只能取变量的偏移地址(10)MOV AX,[SI][DI] ;SI、DI不能成为基址加变址(11)MOV COUNT[BX][SI],ES:AX ;AX是寄存器,不能加段前缀3.7 设当前 SS=2010H,SP=FE00H,BX=3457H,计算当前栈顶的地址为多少?当执行PUSH BX 指令后,栈顶地址和栈顶2个字节的内容分别是什么?当前栈顶的地址=2FF00H当执行PUSH BX 指令后,栈顶地址=2FEFEH(2FEFEH)=57H(2FEFFH)=34H3.8 设DX=78C5H,CL=5,CF=1,确定下列各条指令执行后,DX和CF中的值。

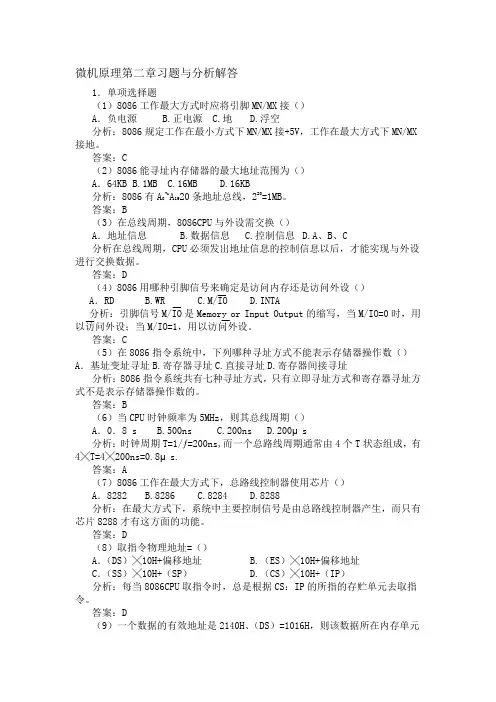

第3章8086CPU指令系统1.写出完成下列要求的变量定义语句:(1)在变量var1中保存6个字变量:4512H,4512,-1,100/3,10H,65530;(2)在变量var2中保存字符串:’BYTE’, ’word’, ’WORD’;(3)在缓冲区buf1中留出100个字节的存储空间;(4)在缓冲区buf2中,保存5个字节的55H,再保存10个字节的240,并将这一过程重复7次;(5)在变量var3中保存缓冲区buf1的长度;(6)在变量pointer中保存变量var1和缓冲区buf1的偏移地址。

解:var1 DW 4512H,4512,-1,100/3,10H,65530var2 DB ’BYTE’,’word’,’WORD’buf1 DB 100 DUP(?)buf2 DB 7 DUP(5 DUP(55H),10 DUP(240))var3 DB LENGTH buf1pointer DW var1,buf1 (或者pointer DW OFFSET var1,OFFSET buf1)2.设变量var1的逻辑地址为0100:0000,画出下列语句定义的变量的存储分配图:var1 DB 12,-12,20/6,4 DUP(0,55H)var2 DB ‘Assemble’var3 DW ‘AB’, ‘cd’, ‘E’var4 DW var2var5 DD var2解:3.指令正误判断,对正确指令写出源和目的操作数的寻址方式,对错误指令指出原因(设VAR1, VAR2为字变量, L1为标号):(1)MOV SI,100 (2)MOV BX,VAR1[SI](3)MOV AX, [BX] (4)MOV AL, [DX](5)MOV BP, AL (6)MOV VAR1, VAR2(7)MOV CS, AX (8)MOV DS, 0100H(9)MOV [BX][SI], 1 (10)MOV AX, VAR1+VAR2(11)ADD AX, LENGTH VAR1 (12)OR BL, TYPE VAR2(13)SUB [DI], 78H (14)MOVS VAR1, VAR2(15)PUSH 100H (16)POP CS(17)XCHG AX, ES (18)MOV DS, CS(19)JMP L1+5 (20)DIV AX, 10(21)SHL BL, 2 (22)MOV AL, 15+23(23)MUL CX (24)XCHG CL, [SI](25)ADC CS:[0100], AH (26)SBB VAR1-5,154解:(1)MOV SI,100 正确。

微机原理第二章习题与分析解答1.单项选择题(1)8086工作最大方式时应将引脚MN/MX接()A.负电源 B.正电源 C.地 D.浮空分析:8086规定工作在最小方式下MN/MX接+5V,工作在最大方式下MN/MX 接地。

答案:C(2)8086能寻址内存储器的最大地址范围为()A.64KB B.1MB C.16MB D.16KB分析:8086有A0~A1920条地址总线,220=1MB。

答案:B(3)在总线周期,8086CPU与外设需交换()A.地址信息 B.数据信息 C.控制信息 D.A、B、C分析在总线周期,CPU必须发出地址信息的控制信息以后,才能实现与外设进行交换数据。

答案:D(4)8086用哪种引脚信号来确定是访问内存还是访问外设()A.RD B.WR C.M/IO D.INTA分析:引脚信号M/IO是Memory or Input Output的缩写,当M/IO=0时,用以访问外设;当M/IO=1,用以访问外设。

答案:C(5)在8086指令系统中,下列哪种寻址方式不能表示存储器操作数()A.基址变址寻址B.寄存器寻址C.直接寻址D.寄存器间接寻址分析:8086指令系统共有七种寻址方式,只有立即寻址方式和寄存器寻址方式不是表示存储器操作数的。

答案:B(6)当CPU时钟频率为5MHz,则其总线周期()A.0.8 s B.500ns C.200ns D.200μs分析:时钟周期T=1/ƒ=200ns,而一个总路线周期通常由4个T状态组成,有4╳T=4╳200ns=0.8μs.答案:A(7)8086工作在最大方式下,总路线控制器使用芯片()A.8282 B.8286 C.8284 D.8288分析:在最大方式下,系统中主要控制信号是由总路线控制器产生,而只有芯片8288才有这方面的功能。

答案:D(8)取指令物理地址=()A.(DS)╳10H+偏移地址 B.(ES)╳10H+偏移地址C.(SS)╳10H+(SP) D.(CS)╳10H+(IP)分析:每当8086CPU取指令时,总是根据CS:IP的所指的存贮单元去取指令。

第二章8086体系结构与80x86CPU1.8086CPU由哪两部分构成?它们的主要功能是什么?答:8086CPU由两部分组成:指令执行部件(EU,Execution Unit)和总线接口部件(BIU,Bus Interface Unit)。

指令执行部件(EU)主要由算术逻辑运算单元(ALU)、标志寄存器FR、通用寄存器组和EU控制器等4个部件组成,其主要功能是执行指令。

总线接口部件(BIU)主要由地址加法器、专用寄存器组、指令队列和总线控制电路等4个部件组成,其主要功能是形成访问存储器的物理地址、访问存储器并取指令暂存到指令队列中等待执行,访问存储器或I/O端口读取操作数参加EU运算或存放运算结果等。

2.8086CPU预取指令队列有什么好处?8086CPU内部的并行操作体现在哪里?答:8086CPU的预取指令队列由6个字节组成,按照8086CPU的设计要求,指令执行部件(EU)在执行指令时,不是直接通过访问存储器取指令,而是从指令队列中取得指令代码,并分析执行它。

从速度上看,该指令队列是在CPU 内部,EU从指令队列中获得指令的速度会远远超过直接从内存中读取指令。

8086CPU内部的并行操作体现在指令执行的同时,待执行的指令也同时从内存中读取,并送到指令队列。

3.8086CPU中有哪些寄存器?各有什么用途?答:指令执行部件(EU)设有8个16位通用寄存器AX、BX、CX、DX、SP、BP、SI、DI,主要用途是保存数据和地址(包括内存地址和I/O端口地址)。

其中AX、BX、CX、DX主要用于保存数据,BX可用于保存地址,DX还用于保存I/O端口地址;BP、SI、DI主要用于保存地址;SP用于保存堆栈指针。

标志寄存器FR用于存放运算结果特征和控制CPU操作。

BIU中的段寄存器包括CS、DS、ES、SS,主要用途是保存段地址,其中CS代码段寄存器中存放程序代码段起始地址的高16位,DS数据段寄存器中存放数据段起始地址的高16位,SS堆栈段寄存器中存放堆栈段起始地址的高16位,ES扩展段寄存器中存放扩展数据段起始地址的高16位。

8086指令系统一览表 类型 汇编指令格式 功 能 操作数说明 时钟周期数 字节数 数 据 传 送 类

MOV dst, src (dst) ← (src) mem, reg reg, mem reg, reg reg, imm mem, imm seg, reg seg, mem mem, seg reg, seg mem, acc acc, mem 9+EA 8+EA 2 4 10+EA 2 8+EA 9+EA 2 10 10 2 ~ 4 2 ~ 4 2 2 ~ 3 3 ~ 6 2 2 ~ 4 2 ~ 4 2 3 3 PUSH src (SP) ← (SP)-2 ((SP)+1, (SP)) ← (src) reg seg mem 11 10 16+EA 1 1 2 ~ 4 POP dst (dst) ← ((SP)+1, (SP)) (SP) ← (SP)+2 reg seg mem 8 8 17+EA 1 1 2 ~ 4 XCHG op1, op2 (op1) ←→ (op1) reg, mem reg, reg reg, acc 17+EA 4 3 2 ~ 4 2 1 IN acc, port IN acc, DX (acc) ← (port) (acc) ← ((DX)) 10 8 2 1 OUT port, acc OUT DX, acc (port) ← (acc) ((DX)) ← (acc) 10 8 2 1 XLAT 11 1 LEA reg, src (reg) ← src reg, mem 2+EA 2 ~ 4 LDS reg, src (reg) ← src (DS) ← (src+2) reg, mem 16+EA 2 ~ 4

LES reg, src (reg) ← src (ES) ← (src+2) reg, mem 16+EA 2 ~ 4 LAHF (AH) ← (FR低字节) 4 1 SAHF (FR低字节) ← (AH) 4 1 PUSHF (SP) ← (SP)-2 ((SP)+1, (SP)) ← (FR低字节) 10 1

POPF (FR低字节) ← ((SP)+1, (SP)) (SP) ← (SP)+2 8 1 算 术 运 算 类

ADD dst, src (dst) ← (src) + (dst) mem, reg reg, mem reg, reg reg, imm mem, imm acc, imm 16+EA 9+EA 3 4 17+EA 4 2 ~ 4 2 ~ 4 2 3 ~ 4 3 ~ 6 2 ~ 3 ADC dst, src (dst) ← (src) + (dst) + CF mem, reg reg, mem reg, reg reg, imm mem, imm acc, imm 16+EA 9+EA 3 4 17+EA 4 2 ~ 4 2 ~ 4 2 3 ~ 4 3 ~ 6 2 ~ 3 INC op1 (op1) ← (op1)+1 reg mem 2 ~ 3 15+EA 1 ~ 2 2 ~ 4 SUB dst, src (dst) ← (src) - (dst) mem, reg reg, mem reg, reg reg, imm mem, imm acc, imm 16+EA 9+EA 3 4 17+EA 4 2 ~ 4 2 ~ 4 2 3 ~ 4 3 ~ 6 2 ~ 3 SBB dst, src (dst) ← (src) - (dst) - CF mem, reg reg, mem reg, reg reg, imm mem, imm acc, imm 16+EA 9+EA 3 4 17+EA 4 2 ~ 4 2 ~ 4 2 3 ~ 4 3 ~ 6 2 ~ 3 DEC op1 (op1) ← (op1) - 1 reg mem 2 ~ 3 15+EA 1 ~ 2 2 ~ 4 NEG op1 (op1) ← 0 - (op1) reg mem 3 16+EA 2 2 ~ 4 CMP op1, op2 (op1) - (op2) mem, reg reg, mem reg, reg reg, imm mem, imm acc, imm 9+EA 9+EA 3 4 10+EA 4 2 ~ 4 2 ~ 4 2 3 ~ 4 3 ~ 6 2 ~ 3 MUL src (AX) ← (AL) * (src) (DX, AX) ← (AX) * (src) 8位reg 8位mem 16位reg 16位mem 70 ~ 77 (76 ~ 83)+EA 118 ~ 133 (124 ~ 139)+EA 2 2 ~ 4 2 2 ~ 4 IMUL src (AX) ← (AL) * (src) (DX, AX) ← (AX) * (src) 8位reg 8位mem 16位reg 16位mem 80 ~ 98 (86 ~ 104)+EA 128 ~ 154 (134 ~ 160)+EA 2 2 ~ 4 2 2 ~ 4 DIV src (AL) ← (AX) / (src) 的商 (AH) ← (AX) / (src) 的余数 (AX) ← (DX, AX) / (src) 的商 (DX) ← (DX, AX) / (src) 的余数 8位reg 8位mem 16位reg 16位mem 80 ~ 90 (86 ~ 96)+EA 144 ~ 162 (150 ~ 168)+EA 2 2 ~ 4 2 2 ~ 4 IDIV src (AL) ← (AX) / (src) 的商 (AH) ← (AX) / (src) 的余数 (AX) ← (DX, AX) / (src) 的商 (DX) ← (DX, AX) / (src) 的余数 8位reg 8位mem 16位reg 16位mem 101 ~ 112 (107 ~ 118)+EA 165 ~ 184 (171 ~ 190)+EA 2 2 ~ 4 2 2 ~ 4 DAA (AL) ← AL中的和调整为组合BCD 4 1 DAS (AL) ← AL中的差调整为组合BCD 4 1 AAA (AL) ← AL中的和调整为非组合BCD (AH) ← (AH)+调整产生的进位值 4 1

AAS (AL) ← AL中的差调整为非组合BCD (AH) ← (AH)-调整产生的进位值 4 1 AAM (AX) ← AX中的积调整为非组合BCD 83 2 AAD (AL) ← (AH) * 10 + (AL) (AH) ← 0 (注意是除法进行前调整被除数) 60 2

逻 辑 运 算 类

AND dst, src (dst) ← (dst) ∧ (src) mem, reg reg, mem reg, reg reg, imm mem, imm acc, imm 16+EA 9+EA 3 4 17+EA 4 2 ~ 4 2 ~ 4 2 3 ~ 4 3 ~ 6 2 ~ 3 OR dst, src (dst) ← (dst) ∨ (src) mem, reg reg, mem reg, reg reg, imm mem, imm acc, imm 16+EA 9+EA 3 4 17+EA 4 2 ~ 4 2 ~ 4 2 3 ~ 4 3 ~ 6 2 ~ 3 NOT op1 (op1) ← (1op) reg mem 3 16+EA 2 2 ~ 4 XOR dst, src (dst) ← (dst) ⊕ (src) mem, reg reg, mem reg, reg reg, imm mem, imm acc, imm 16+EA 9+EA 3 4 17+EA 4 2 ~ 4 2 ~ 4 2 3 ~ 4 3 ~ 6 2 ~ 3 TEST op1, op2 (op1) ∧ (op2) reg, mem reg, reg reg, imm mem, imm acc, imm 9+EA 3 5 11+EA 4 2 ~ 4 2 3 ~ 4 3 ~ 6 2 ~ 3 SHL op1, 1 SHL op1, CL 逻辑左移 reg mem reg mem 2 15+EA 8 + 4/bit 20+EA+ 4/bit 2 2 ~ 4 2 2 ~ 4 SAL op1, 1 SAL op1, CL 算术右移 reg mem reg mem 2 15+EA 8 + 4/bit 20+EA+ 4/bit 2 2 ~ 4 2 2 ~ 4 SHR op1, 1 SHR op1, CL 逻辑右移 reg mem reg mem 2 15+EA 8 + 4/bit 20+EA+ 4/bit 2 2 ~ 4 2 2 ~ 4 SAR op1, 1 SAR op1, CL 算术右移 reg mem reg mem 2 15+EA 8 + 4/bit 20+EA+ 4/bit 2 2 ~ 4 2 2 ~ 4 ROL op1, 1 ROL op1, CL 循环左移 reg mem reg mem 2 15+EA 8 + 4/bit 20+EA+ 4/bit 2 2 ~ 4 2 2 ~ 4 ROR op1, 1 ROR op1, CL 循环右移 reg mem reg mem 2 15+EA 8 + 4/bit 20+EA+ 4/bit 2 2 ~ 4 2 2 ~ 4 RCL op1, 1 RCL op1, CL 带进位位的循环左移 reg mem reg mem 2 15+EA 8 + 4/bit 20+EA+ 4/bit 2 2 ~ 4 2 2 ~ 4 RCR op1, 1 RCR op1, CL 带进位位的循环右移 reg mem reg mem 2 15+EA 8 + 4/bit 20+EA+ 4/bit 2 2 ~ 4 2 2 ~ 4 串 操 作 类

MOVSB MOVSW ((DI)) ← ((SI)) (SI) ← (SI)±1, (DI) ← (DI)±1 ((DI)) ← ((SI)) (SI) ← (SI)±2, (DI) ← (DI)±2 不重复:18 重复:9+17/rep 不重复:18 重复:9+17/rep 1 1 STOSB STOSW ((DI)) ← (AL) (DI) ← (DI)±1 ((DI)) ← (AX) (DI) ← (DI)±2 不重复:11 重复:9+10/rep 不重复:11 重复:9+10/rep 1 1 LODSB LODSW (AL) ← ((SI)) (SI) ← (SI)±1 (AX) ← ((SI)) (SI) ← (SI)±2 不重复:12 重复:9+13/rep 不重复:12 重复:9+13/rep 1 1