集成电路模拟版图设计基础

- 格式:ppt

- 大小:11.03 MB

- 文档页数:105

模拟cmos集成电路设计知识点总结模拟CMOS集成电路设计是一个涉及多个学科领域的复杂课题,包括电子工程、物理、材料科学和计算机科学等。

以下是一些关键知识点和概念的总结:1. 基础知识:半导体物理:理解半导体的基本性质,如本征半导体、n型和p型半导体等。

MOSFET(金属-氧化物-半导体场效应晶体管)工作原理:理解MOSFET的基本构造和如何通过电压控制电流。

2. CMOS工艺:了解基本的CMOS工艺流程,包括晶圆准备、热氧化、扩散、光刻、刻蚀、离子注入和退火等步骤。

理解各种工艺参数对器件性能的影响。

3. CMOS电路设计:了解基本的模拟CMOS电路,如放大器、比较器、振荡器等。

理解如何使用SPICE(Simulation Program with Integrated Circuit Emphasis)进行电路模拟。

4. 噪声:理解电子器件中的噪声来源,如热噪声、散粒噪声和闪烁噪声等。

了解如何减小这些噪声的影响。

5. 功耗:理解CMOS电路中的功耗来源,如静态功耗和动态功耗。

了解降低功耗的方法,如电源管理技术和低功耗设计技术。

6. 性能优化:理解如何优化CMOS电路的性能,如提高速度、减小失真和提高电源效率等。

7. 可靠性问题:了解CMOS电路中的可靠性问题,如闩锁效应和ESD(静电放电)等。

8. 版图设计:了解基本的版图设计规则和技巧,以及如何使用EDA(Electronic Design Automation)工具进行版图设计和验证。

9. 测试与验证:理解如何测试和验证CMOS集成电路的性能。

10. 发展趋势与挑战:随着技术的进步,模拟CMOS集成电路设计面临许多新的挑战和发展趋势,如缩小工艺尺寸、提高集成度、应对低功耗需求等。

持续关注最新的研究和技术进展是非常重要的。

以上是对模拟CMOS集成电路设计的一些关键知识点的总结,具体内容可能因实际应用需求和技术发展而有所变化。

深入学习这一领域需要广泛的知识基础和持续的研究与实践。

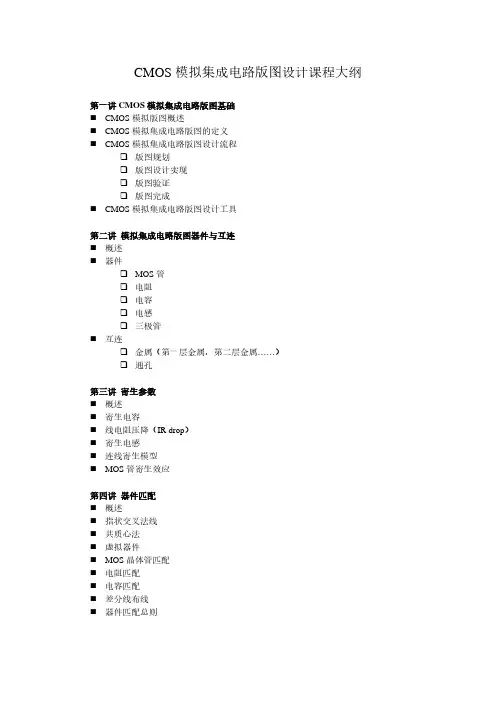

CMOS模拟集成电路版图设计课程大纲第一讲CMOS模拟集成电路版图基础⏹CMOS模拟版图概述⏹CMOS模拟集成电路版图的定义⏹CMOS模拟集成电路版图设计流程❑版图规划❑版图设计实现❑版图验证❑版图完成⏹CMOS模拟集成电路版图设计工具第二讲模拟集成电路版图器件与互连⏹概述⏹器件❑MOS管❑电阻❑电容❑电感❑三极管⏹互连❑金属(第一层金属,第二层金属……)❑通孔第三讲寄生参数⏹概述⏹寄生电容⏹线电阻压降(IR drop)⏹寄生电感⏹连线寄生模型⏹MOS管寄生效应第四讲器件匹配⏹概述⏹指状交叉法线⏹共质心法⏹虚拟器件⏹MOS晶体管匹配⏹电阻匹配⏹电容匹配⏹差分线布线⏹器件匹配总则第五讲设计规则⏹概述⏹工艺库中各类器件的层信息⏹设计规则细则⏹工业标准的基本数据格式第六讲验证⏹设计规则检查(DRC)Design Rule Check⏹版图与电路图的对照(LVS)Layout Versus Schematic⏹电气规则检查(ERC)Electrical Rule Check⏹天线规则检查(ANT)⏹静电放电检查(ESD)第七讲可靠性设计⏹天线效应⏹闩锁效应⏹静电放电保护(Electro-Static Discharge ,ESD)⏹数模混合集成电路版图设计第八讲工艺设计工具包(PDK)⏹ 1.PDK名称的涵义⏹ 2.PDK中包含的内容● 2.1 IO lib2.1.1 GDS文件的导入操作2.1.2 网表导入2.1.3 IO使用文档介绍● 2.2 SMIC_13_PDK_v2.6_20142.2.1 Smic13mmrf_1233文件夹2.2.2 model 文件夹2.2.3 Calibre 文件夹● 2.3 SMIC_13_TF_LG_LIST_2014122.3.1 Standard cell Timing lib2.3.2 Calview.cellmap2.3.3 Standard cell netlist及网表导入操作2.3.4 Ant rule (天线规则)第九讲Cadence spectre概述与操作界面⏹Cadence spectre 概述⏹Cadence spectre的特点⏹Cadence spectre的仿真设计方法⏹Cadence spectre与其他EDA软件的连接⏹Cadence spectre的基本操作第十讲Spectre窗口和库元件⏹模拟设计环境(Analog Design Environment)⏹波形显示窗口(Waveform)⏹波形计算器(Waveform Calculator)⏹Spectre库中的基本器件第十讲Cadence Virtuoso版图设计工具⏹Cadence Virtuoso概述⏹Virtuoso 界面介绍⏹Virtuoso 基本操作第十一讲Mentor Calibre版图验证工具⏹Mentor Calibre版图验证工具概述⏹Mentor Calibre版图验证工具调用⏹Mentor Calibre DRC验证⏹Mentor Calibre LVS验证⏹Mentor Calibre寄生参数提取(PEX)第十二讲版图设计与验证流程实例⏹设计环境准备⏹反相器链电路的建立和前仿真⏹反相器链版图设计⏹反相器链版图验证与参数提取⏹反相器链电路后仿真⏹输入输出单元环设计⏹主体电路版图与输入输出单元环的连接⏹导出GDSII文件。

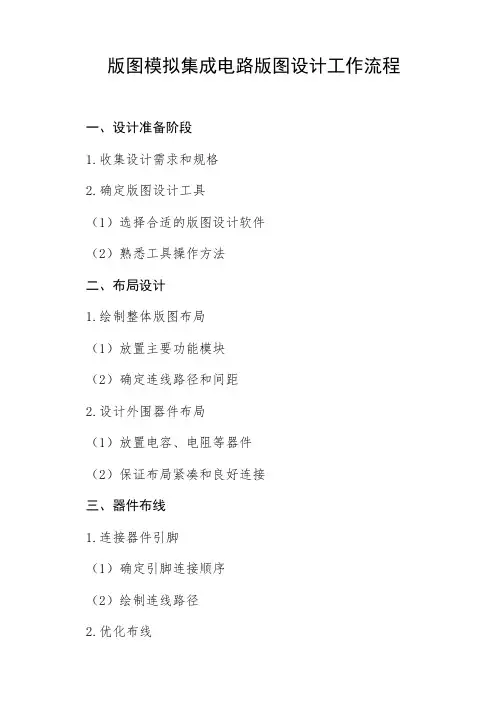

版图模拟集成电路版图设计工作流程

一、设计准备阶段

1.收集设计需求和规格

2.确定版图设计工具

(1)选择合适的版图设计软件

(2)熟悉工具操作方法

二、布局设计

1.绘制整体版图布局

(1)放置主要功能模块

(2)确定连线路径和间距

2.设计外围器件布局

(1)放置电容、电阻等器件

(2)保证布局紧凑和良好连接

三、器件布线

1.连接器件引脚

(1)确定引脚连接顺序

(2)绘制连线路径

2.优化布线

(1)考虑信号传输和功耗(2)调整布线路径提高性能

四、特殊器件设计

1.设计特殊功能模块

(1)绘制模拟电路部分(2)完成数字逻辑设计

2.验证特殊器件功能

(1)模拟仿真验证

(2)数字仿真测试

五、验证与调试

1.进行版图验证

(1)检查器件连接和间距(2)确保布局符合设计规范2.仿真验证

(1)电气仿真测试

(2)时序分析和功耗测试

六、提交版图

1.准备版图文件

(1)导出版图文件格式

(2)打包必要设计文件2.提交给布局工程师(1)交流设计细节和要求(2)确认后提交版图。

实验38 模拟集成电路的版图设计模拟集成电路设计是现代集成电路设计的重要组成部分。

模拟集成电路的版图设计是模拟集成电路设计环节中的重要关键环节。

模拟集成电路版图设计的优劣直接影响着整个集成电路的性能和设计的成败。

本实验要求学生在系统地学习了《半导体物理》、《场效应器件物理》、《模拟集成电路设计》和《集成电路制造技术》等专业知识的基础上,使用Tanner公司设计开发的集成电路版图设计工具Ledit软件,独立完成CMOS模拟集成电路单元的版图设计和布局工作,提高模拟集成电路版图设计和布局能力,强化对模拟集成电路制造技术的理解和知识运用能力,培养学生初步的模拟集成电路版图设计能力。

一、实验原理1. 模拟集成电路版图中的器件与设计规则在模拟集成电路中,主要器件有NMOS、PMOS、NPN和PNP晶体管,二极管、电阻和电容等。

这些器件在Ledit软件中,实现的方法存在较大差异,但都是遵循器件的定义实现的。

器件的定义存储在以.ext为后缀的器件萃取文件中。

在Ledit软件环境下,P型衬底N阱CMOS 2P2M工艺下(两层多晶两层金属),模拟集成电路版图中器件的设计规则,除去与数字集成电路版图设计中通用的规则外,主要还有:NPN、PNP晶体管设计规则、电容设计规则和电阻设计规则等,表38.1中摘录了这些规则中的部分内容。

使用这些设计规则可以实现NPN、PNP、MOS电容和电阻等器件版图。

=1.0μm部分设计规则表38.1 P型衬底N阱CMOS工艺下,182在绘制模拟集成电路版图时,所绘制的各种基本图形尺寸不能小于这些设计规则要求的尺寸,否则将导致设计规则错误。

在Ledit软件环境下,完成设计规则检查的功能称为设计规则检查(Design Rule Check,DRC)。

在集成电路版图绘制过程中,需要经常性地使用DRC功能来检查版图是否存在错误,这样做可以避免同时有太多违反设计规则的错误产生,决定着版图的完成效率和完成质量。