实验模拟集成电路版图方案

- 格式:doc

- 大小:142.50 KB

- 文档页数:6

实验报告课程名称:集成电路原理实验名称:模拟集成电路版图设计与验证小组成员:实验地点:科技实验大楼606实验时间:2017年6月19日2017年6月19日微电子与固体电子学院一、实验名称:模拟集成电路版图设计与验证二、实验学时:4三、实验原理1、电路设计与仿真实验2内容,根据电路的指标和工作条件,然后通过模拟计算,决定电路中各器件的参数(包括电参数、几何参数等),EDA软件进行模拟仿真。

2、工艺设计根据电路特点结合所给的工艺,再按电路中各器件的参数要求,确定满足这些参数的工艺参数、工艺流程和工艺条件。

3、版图设计按电路设计和确定的工艺流程,把电路中有源器件、阻容元件及互连以一定的规则布置在Candence下的版图编辑器内。

并优化版图结构。

四、实验目的本实验是基于微电子技术应用背景和《集成电路原理》课程设置及其特点而设置,为IC设计性实验。

其目的在于:1、根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路版图设计,掌握基本的IC版图布局布线技巧。

2、学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行版图的的设计与验证。

通过该实验,使学生掌握CMOS模拟IC版图设计的流程,加深对课程知识的感性认识,增强学生的设计与综合分析能力。

五、实验内容1、UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。

2、根据实验2所得参数,自主完成版图设计,并掌握布局布线的基本技巧。

3、整理版图生成文件,总结、撰写并提交实验报告。

六、实验仪器设备(1)工作站或微机终端一台(2)EDA仿真软件1套七、实验步骤1、根据实验指导书掌握Cadence EDA仿真环境的调用。

熟悉版图编辑器Layout Editor的使用。

了解基本的布局布线方法及元器件的画法。

2、根据实验2所计算验证的两级共源CMOS运放的元器件参数如表1所示,在版图设计器里画出相应的元器件,对V+、V-、V out、V DD、GND的压焊点位置合理化放置,通过金属画线将各个元器件按实验2的电路图合理连接,避免跳线。

西安邮电大学集成电路版图设计实验报告学号:XXX姓名:XX班级:微电子XX日期:20XX目录实验一、反相器电路的版图验证1)反相器电路2)反相器电路前仿真3)反相器电路版图说明4)反相器电路版图DRC验证5)反相器电路版图LVS验证6)反相器电路版图提取寄生参数7)反相器电路版图后仿真8)小结实验二、电阻负载共源放大器版图验证9)电阻负载共源放大器电路10)电阻负载共源放大器电路前仿真11)电阻负载共源放大器电路版图说明12)电阻负载共源放大器电路版图DRC验证13)电阻负载共源放大器电路版图LVS验证14)电阻负载共源放大器电路版图提取寄生参数15)电阻负载共源放大器电路版图后仿真16)小结实验一、反相器电路的版图验证1、反相器电路反相器电路由一个PMOS、NPOS管,输入输出端、地、电源端和SUB 端构成,其中VDD接PMOS管源端和衬底,地接NMOS管的漏端,输入端接两MOS管栅极,输出端接两MOS管漏端,SUB端单独引出,搭建好的反相器电路如图1所示。

图1 反相器原理图2、反相器电路前仿真通过工具栏的Design-Create Cellview-From Cellview将反相器电路转化为symbol,和schemetic保存在相同的cell中。

然后重新创建一个cell,插入之前创建好的反相器symbol,插入电感、电容、信号源、地等搭建一个前仿真电路,此处最好在输入输出网络上打上text,以便显示波形时方便观察,如图2所示。

图2 前仿真电路图反相器的输入端设置为方波信号,设置合适的高低电平、脉冲周期、上升时间、下降时间,将频率设置为参数变量F,选择瞬态分析,设置变量值为100KHZ,仿真时间为20u,然后进行仿真,如果仿真结果很密集而不清晰可以右键框选图形放大,如图3所示。

图3 前仿真结果3、反相器电路版图说明打开之前搭建好的反相器电路,通过Tools-Design Synthesis-Laout XL新建一个同cell目录下的Laout文件,在原理图上选中两个MOS管后在Laout中选择Create-Pick From Schematic从原理图中调入两个器件的版图模型。

电子科技大学实验报告学生姓名:连亚涛/王俊颖学号:2011031010032/0007指导教师:王向展实验地点:微固楼606实验时间:2014.6.一、实验室名称:微电子技术实验室二、实验项目名称:模拟集成电路版图设计和绘制三、实验学时:4四、实验原理参照实验指导书。

五、实验目的本实验是基于微电子技术应用背景和《集成电路原理》课程设置及其特点而设置,为IC设计性实验。

其目的在于:根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路版图设计,掌握基本的IC版图布局布线技巧。

学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行版图的的设计。

六、实验内容1、UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。

2、根据设计指标要求,自主完成版图设计,并掌握布局布线的基本技巧。

七、实验仪器设备(1)工作站或微机终端一台八、实验步骤1、根据实验指导书熟悉UNIX操作系统常用命令的使用,掌握CadenceEDA 仿真环境的调用。

2、根据设计指标要求,设计出如下图所示的运算放大器电路版图,过程中应注意设计规则。

九、实验数据及结果分析:1、通过本次实验掌握了UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。

达到了实验目的。

2、根据设计指标要求,设计出运算放大器模拟集成电路版图。

(备注:小组共同完成)十、实验结论:通过这次实验,学习并掌握国际流行的EDA仿真软件Cadence的使用方法,完成了运算放大器集成电路版图的设计,其难点是版图的布局布线和设计规则的理解。

十一、总结及心得体会:2学会了cadence在linux下的使用,在回去安装Ubuntu的过程中发生了很多错误,有了一定的提高,让我了解到使用免费破解的专业软件的不易。

其次,cadence使用过程中,有很多技巧值得认真学习,如左手键盘右手鼠标操作,以及先画基本的接触孔,再画mos管,再用已有的Mos管拼接出其他宽长比的方法。

实验33 模拟集成电路版图的反向提取模拟集成电路具有设计难度大、应用范围宽等优点,早已成为了集成电路设计领域的重要研究热点,引起了研究者的广泛关注。

模拟集成电路版图的反向提取关乎电路设计的成败,是设计过程中的重要关键环节之一。

本实验要求学生能够独立对标准CMOS模拟集成电路版图单元,完成电路的反向提取、绘制整理和功能分析等工作。

通过对CMOS模拟集成电路版图单元的反向提取实践,锻炼和提高学生对集成半导体器件和模拟集成电路版图的认知能力和对电路整理与结构优化技能,培养学生对模拟集成电路反向设计思想的理解,加强学生灵活运用所学《半导体物理》、《场效应器件物理》、《模拟集成电路设计》和《集成电路制造技术》等理论知识的能力。

一、实验原理1. 模拟集成电路中的集成器件在标准CMOS工艺下,模拟集成半导体器件主要有:MOS晶体管、扩散电阻、多晶硅电阻、多晶硅电容和MOS电容等。

在P型衬底N阱CMOS工艺条件下,NMOS器件直接制作在衬底材料上,PMOS器件制作在N阱中。

在模拟集成电路中,MOS晶体管常常工作在线性区或饱和区,需要承受较大的功耗,这些晶体管具有较大的宽长比。

模拟集成电路版图常常不规则,这就要求在电路提取时要充分注意电路连接关系。

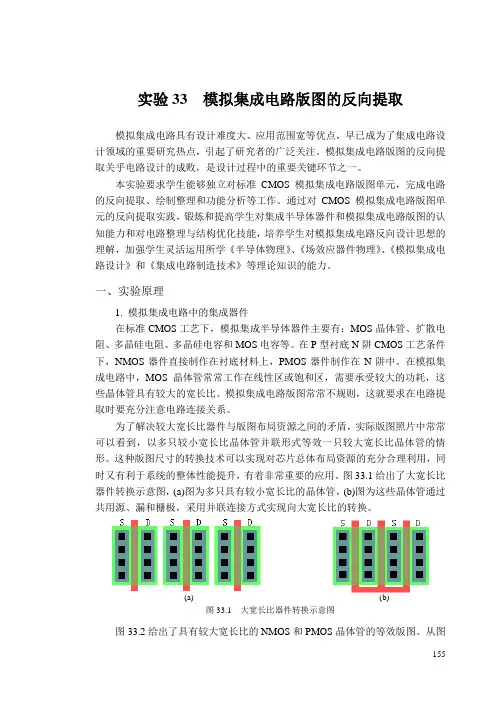

为了解决较大宽长比器件与版图布局资源之间的矛盾,实际版图照片中常常可以看到,以多只较小宽长比晶体管并联形式等效一只较大宽长比晶体管的情形。

这种版图尺寸的转换技术可以实现对芯片总体布局资源的充分合理利用,同时又有利于系统的整体性能提升,有着非常重要的应用。

图33.1给出了大宽长比器件转换示意图,(a)图为多只具有较小宽长比的晶体管,(b)图为这些晶体管通过共用源、漏和栅极,采用并联连接方式实现向大宽长比的转换。

(a) (b)图33.1 大宽长比器件转换示意图图33.2给出了具有较大宽长比的NMOS和PMOS晶体管的等效版图。

从图155中可以看出,NMOS和PMOS晶体管都是由四只晶体管并联组成的,由于源极、漏极和栅极分别接在一起,所以晶体管从漏极流向源极的电流具有四条路径,那么,作用结果相当于四倍宽长比的单只晶体管。

集成电路版图分析与设计实验指导书本科上海建桥学院机电学院2015年8月目录实验一熟悉Unix操作命令 .................................... 错误!未指定书签。

实验二建立设计库及绘图技术 ................................. 错误!未指定书签。

实验三Virtuoso设计CMOS反相器版图 ......................... 错误!未指定书签。

实验四CMOS门电路版图设计 .................................. 错误!未指定书签。

实验五版图DRC/LVS验证..................................... 错误!未指定书签。

实验六高级门级电路版图设计 ................................. 错误!未指定书签。

实验七CMOS模拟电路版图设计(一) .......................... 错误!未指定书签。

实验八CMOS模拟电路版图设计(二) .......................... 错误!未指定书签。

实验一熟悉Unix操作命令一、实验目的1、熟悉Unix系统环境;2、了解目录和文件的操作命令,並要掌握常用的目录操作命令和文件操作命令;3、学会使用Vi编辑器。

二、实验原理Unix操作系统是Cadence软件工具安装的平台,使用Cadence工具创建、生成文件需要保存成文件。

(一)文件及目录操作1、Unix系统以目录树结构组织文件和目录,如图1-1所示。

图1-1Unix系统目录树结构2、目录操作命令在进行系统管理时,需要知道当前处在哪个文件(目录)层,以及如何从文件所在目录更换到另一个目录上。

(1)cd命令:改变当前目录到新的目录格式: cd新的目录路径cd..返回上级目录cd.当前目录cd~返回家目录cd/返回根目录cd/home/shiyan1返回/home/shiyan1目录(2)pwd命令:显示当前工作目录Pwd(3)ls命令:列出目录内容格式:ls[-ltrfda]目录路径名ls-l 以长格式列出当前目录内容ls-l /home/shiyan1 以长格式列出/home/shiyan1目录内容ls-lt/home/shiyan1以长格式、时间排序列出/home/shiyan1目录内容ls-al/home/shiyan2 以长格式列出/home/shiyan2目录(包含.文件)内容格式:mkdir[-p]新的目录名mkdirinvert 在当前目录下创建invert文件目录mkdir-p/home/shiyan1/temp 创建/home/shiyan1/temp目录,如果父目录不存在,则创建父目录(5)rmdir命令:删除目录格式:rmdir[-f]目录名rmdirinvert 删除当前目录文件invertrmdir/home/shiyan1/temp 删除/home/shiyan1/temp目录rmdir-f/home/shiyan1/temp 强制删除/home/shiyan1/temp目录(6)mv命令:更改目录名格式:mv旧目录名新目录名mv/home/shiyan1/home/shiyan23、文件操作命令格式:cat[-n]文件名cat/home/shiyan1/myfile 列出/home/shiyan1/myfile文件内容cat-n/home/shiyan1/myfile 列出/home/shiyan1/myfile文件内容,并给出行号(2)cp命令:文件复制格式:cp[-rf]旧文件(目录)名新文件(目录)名cp/home/shiyan1/myfile/home/shiyan1/myfile-temp复制/home/shiyan1/myfile 文件为/home/shiyan1/myfile-tempcp-rf/home/shiyan1/temp/home/shiyan1/tmp 复制/home/shiyan1/temp目录为/home/shiyan1/tmp(3)mv命令:移动文件或换名格式:mv旧文件名新文件名mv/home/shiyan1/temp/home/shiyan1/tmp 将/home/shiyan1/temp换名为/home/shiyan1/tmp格式:rm[-f]文件(目录)名rm-f/home/shiyan1/tmp 强制删除/home/shiyan1/tmp目录(5)?、*:通配符?匹配单个字符* 匹配任意目录字符(6)find命令:查找文件格式:find[-option]path–namefilename[–print]find/-name*.jpg 在根目录中查找所有.jpg的文件,并显示所有.jpg文件名(7)grep命令:文件中查找指定内容格式:grep[-inR]string文件名grepDRC/home/shiyan1/myfile 在/home/shiyan1/myfile中查找DRC字符串grep-iDRC/home/shiyan1/myfile 在/home/shiyan1/myfile中查找DRC字符串,忽略大小写(8)more命令:浏览文件格式:more文件名more/home/shiyan1/myfile4、文件存取权限(1)ls查看文件权限r读权限w写权限x执行权限-无此权限u用户主g用户组o其他用户a所有用户(2)chmod命令:改变文件权限格式:chmod[-R]mod文件(目录)名(二)shell与进程1、ShellCshell、kshell、bshell、tshell2、进程(1)&后台进程(2)权限为x的文件为可执行文件(3)ps命令:查看进程信息格式:ps[-options]进程名(4)kill命令:终止进程格式:kill[-options]进程号(三)使用vi文本编辑器1、vi编辑器有三种不同的模式:插入模式——这个模式是通过在命令模式按下“i”键进入的。

福州大学物信学院《集成电路版图设计》实验报告姓名:席高照学号:111000833系别:物理与信息工程专业:微电子学年级:2010指导老师:江浩一、实验目的1.掌握版图设计的基本理论。

2.掌握版图设计的常用技巧。

3.掌握定制集成电路的设计方法和流程。

4.熟悉Cadence Virtuoso Layout Edit软件的应用5.学会用Cadence软件设计版图、版图的验证以及后仿真6.熟悉Cadence软件和版图设计流程,减少版图设计过程中出现的错误。

二、实验要求1.根据所提供的反相器电路和CMOS放大器的电路依据版图设计的规则绘制电路的版图,同时注意CMOS查分放大器电路的对称性以及电流密度(通过该电路的电流可能会达到5mA)2.所设计的版图要通过DRC、LVS检测三、有关于版图设计的基础知识首先,设计版图的基础便是电路的基本原理,以及电路的工作特性,硅加工工艺的基础、以及通用版图的设计流程,之后要根据不同的工艺对应不同的设计规则,一般来说通用的版图设计流程为①制定版图规划记住要制定可能会被遗忘的特殊要求清单②设计实现考虑特殊要求及如何布线创建组元并对其进行布局③版图验证执行基于计算机的检查和目视检查,进行校正工作④最终步骤工程核查以及版图核查版图参数提取与后仿真完成这些之后需要特别注意的是寄生参数噪声以及布局等的影响,具体是电路而定,在下面的实验步骤中会体现到这一点。

四、实验步骤I.反相器部分:反相器原理图:反相器的基本原理:CMOS反相器由PMOS和NMOS构成,当输入高电平时,NMOS导通,输出低电平,当输入低电平时,PMOS导通,输出高电平。

注意事项:(1)画成插齿形状,增大了宽长比,可以提高电路速度(2)尽可能使版图面积最小。

面积越小,速度越高,功耗越小。

(3)尽可能减少寄生电容和寄生电阻。

尽可能增加接触孔的数目可以减小接触电阻。

(4)尽可能减少串扰,电荷分享。

做好信号隔离。

反相器的版图:原理图电路设计:整体版图:DRC检测:LVS检测:II.CMOS差分放大器部分:CMOS差分放大器的原理图:在该电路中,M1、M2为有源负载,M3、M4为电流源,M5为电流源器件。

或非门版图实验

1、打开L-Edit程序

2、另存新文件:选择File---Save As命令,打开“另存为”对话框,在“保存在”

下拉表框中选择存储目录,在“文件名”文本框中输入新的文件名。

3、取代设定:选择File----Replace Setup命令,将出现一个对话框,单机Form file

下拉列表框右侧的Browser按钮,并选择light.tdb文件,在单击确定。

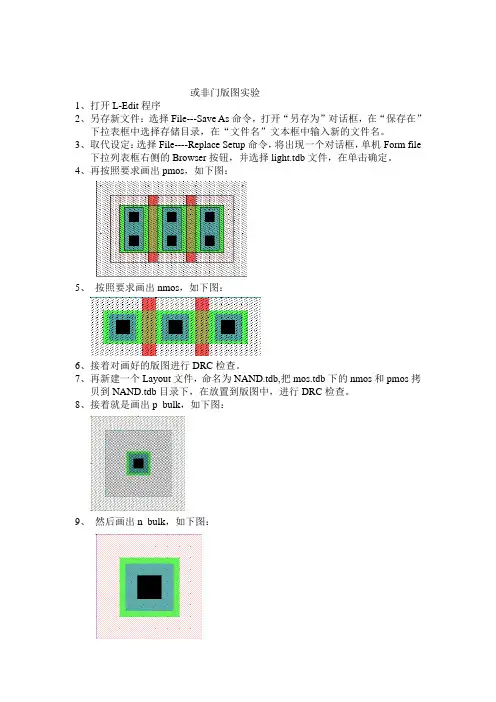

4、再按照要求画出pmos,如下图:

5、按照要求画出nmos,如下图:

6、接着对画好的版图进行DRC检查。

7、再新建一个Layout文件,命名为NAND.tdb,把mos.tdb下的nmos和pmos拷

贝到NAND.tdb目录下,在放置到版图中,进行DRC检查。

8、接着就是画出p_bulk,如下图:

9、然后画出n_bulk,如下图:

10、然后把各部分放到一张版图上,进行连接,然后进行DRC检查,如下图:

11、然后将图导出,生成网表文件,接着用T-spice打开,进行模拟。

对模拟

的量添加命令,如下:

.include "E:\Program Files\Tanner\tanner\TSpice70\models\ml2_125.md"

.tran/op 2n 80n method=bdf

.print tran v(A) v(B) v(Y)

vdc1 Vdd GND 5

vpulse1 A GND PULSE (0 5 0 2n 2n 8n 20n)

vpulse2 B GND PULSE (0 5 0 4n 4n 16n 40n)

仿真波形图如下:。

CMOS模拟集成电路设计与仿真实验指导书模拟集成电路原理实验指导书二零一二年五月实验1 集成电路版图识别与提取一、实验目的随着IT产业的迅速发展,集成电路在国民经济和国防建设中的地位日益突出。

IC设计技术尤显重要。

版图识别与提取是微电子IC逆向设计的关键技术。

一方面可借鉴并消化吸收先进、富有创意的版图设计思想、结构。

建立自己的版图库;另一方面通过分析、优化已有版图可将原有芯片的性能加以改进提高。

本实验是基于微电子技术应用背景和《模拟集成集成电路》课程设置及其特点而设置,目的在于:1增加对塑封、陶瓷封装等不同封装形式的感性认识;2 增加对硅圆片、芯片的感性认识;3 学习并掌握集成电路版图的图形识别、电路拓扑结构提取。

4能对提取得到的电路进行功能分析、确定,并可运用EDA软件展开模拟仿真。

二、实验原理本实验重点放在版图识别、电路拓扑提取、版图编辑三大模块,实验流程如下:三、实验内容1.观察典型集成电路的封装形式;2.观察集成电路成品剖片的电路结构;3.观察硅圆片与未封装的芯片;4.在芯片上找出划片槽、测试单管、分布在芯片边缘的压焊点、对位标记,并测出有关图形的尺寸和间距。

仔细观察芯片图形的总体布局,找出电源线、地线、输入端、输出端以及相应的压焊点;6.判断集成电路的工艺类别;7.根据以上判断、提取芯片上图形所示电路图的拓扑结构;复查、修正,并进行仿真验证。

四、实验步骤1.观察典型集成电路的封装形式;2.对集成电路成品剖片的电路结构进行观察;3.观察测试单管。

仔细观察芯片的布局布线,找出电源线和地线。

4.确定芯片工艺类别,分清单个的元件结构,提取版图电路拓扑结构五、实验报告1.版图识别与提取过程总结2.绘出所提版图的电路拓扑结构六、附:版图照片(含铝线照片):金属1层去铝线照片衬底层课下思考练习: 金属1层去铝线照片衬底层实验2CMOS模拟集成电路设计与仿真一、实验目的与意义随着IT产业的迅猛发展,微电子集成电路在通讯、计算机及其他消费类电子产品中的重要地位日益突出,而IC的生产和设计技术水平是决定IC芯片性能的两大要素。

版图模拟集成电路版图设计工作流程

一、设计准备阶段

1.收集设计需求和规格

2.确定版图设计工具

(1)选择合适的版图设计软件

(2)熟悉工具操作方法

二、布局设计

1.绘制整体版图布局

(1)放置主要功能模块

(2)确定连线路径和间距

2.设计外围器件布局

(1)放置电容、电阻等器件

(2)保证布局紧凑和良好连接

三、器件布线

1.连接器件引脚

(1)确定引脚连接顺序

(2)绘制连线路径

2.优化布线

(1)考虑信号传输和功耗(2)调整布线路径提高性能

四、特殊器件设计

1.设计特殊功能模块

(1)绘制模拟电路部分(2)完成数字逻辑设计

2.验证特殊器件功能

(1)模拟仿真验证

(2)数字仿真测试

五、验证与调试

1.进行版图验证

(1)检查器件连接和间距(2)确保布局符合设计规范2.仿真验证

(1)电气仿真测试

(2)时序分析和功耗测试

六、提交版图

1.准备版图文件

(1)导出版图文件格式

(2)打包必要设计文件2.提交给布局工程师(1)交流设计细节和要求(2)确认后提交版图。

一、实验目的1.熟练掌握使用Cadence Virtuoso ADE5.1.41软件进行原理图的编辑2.使用器件设计参数表格的数据进行电路设计3.掌握基本差分对电路的设计方法二、实验软件:Cadence IC Virtuoso ADE 5.1.41第一部分 基本差分对设计独立完成实验设计指标: 已知:VDD=3.3V , Iss=300uA要求:Av>40dB ,共模输入范围1.2 2.5inCM V ≤≤,最大共模输入电压下,输出摆幅1V >,共模抑制比85CMRR dB ≥1.1 基本差分对设计分析及参数估算一、参数估算1.根据共模输入范围inCM V 和输出摆幅的要求,各个MOS 管的过驱动电压并估算偏置电压VB 和输出Vout (也即VA )的静态值,电路如图1所示,min 131 1.2inCM GSN B TN on B V V V V V V =+-≈+≤B N30.2, 1.00.8,0.80.540.26on V V V V V ⇒=≤==-=onN1B 可以取V V 取max 121212|| 2.5inCM A TN GSP TN onP TN TP V V V VDD V V VDD V V V =+=-+=-+-≥即2 3.3 2.50.540.750.59onP V ≤-+-=指标要求最大共模输入电压,输出摆幅要求大于1Vmin max 1 2.50.54 2.06out inCM Tn V V V =-=-=故max 2.061 3.06out V ≥+=,由此可得2max 3.3 3.060.24onP out V VDD V ≤-=-=该值要和通过共模输入范围要求得到的2 3.3 2.50.540.750.59onP V ≤-+-=求交集,取20.2onP V V =,于是估算输出点的静态电压223.3(||) 3.3(0.20.75) 2.35out A onP TP V V V V ==-+=-+=2.确定输入的静态共模电平值。

集成电路设计综合实验报告班级:微电子学1201班姓名:学号:日期:2016年元月13日一.实验目的1、培养从版图提取电路的能力2、学习版图设计的方法和技巧3、复习和巩固基本的数字单元电路设计4、学习并掌握集成电路设计流程二.实验内容1. 反向提取给定电路模块(如下图所示),要求画出电路原理图,分析出其所完成的逻辑功能,并进行仿真验证;再画出该电路的版图,完成DRC验证。

2. 设计一个CMOS结构的二选一选择器。

(1)根据二选一选择器功能,分析其逻辑关系。

(2)根据其逻辑关系,构建CMOS结构的电路图。

(3)利用EDA工具画出其相应版图。

(4)利用几何设计规则文件进行在线DRC验证并修改版图。

三.实验原理1. 反向提取给定电路模块方法一:直接将版图整体提取(如下图)。

其缺点:过程繁杂,所提取的电路不够直观,不易很快分析出其电路原理及实现功能。

直接提取的整体电路结构图方法二:将版图作模块化提取,所提取的各个模块再生成symbol,最后将symbol按版图连接方式组合成完整电路结构(如下图)。

其优点:使电路结构更简洁直观、结构严谨、层次清晰,更易于分析其原理及所实现的功能。

CMOS反相器模块CMOS反相器的symbolCMOS传输门模块 CMOS传输门的symbolCMOS三态门模块 CMOS三态门的symbolCMOS与非门模块 CMOS与非门的symbol各模块symbol按版图连接方式组合而成的整体电路经分析可知,其为一个带使能端的D锁存器,逻辑功能如下:①当A=1,CP=0时,Q=D,Q—=D—;②当A=1,CP=1时,Q、Q—保持;③当A=0,Q=0,Q—=1。

2.CMOS结构的二选一选择器二选一选择器(mux2)的电路如图所示,它的逻辑功能是:①当sel=1时,选择输入A通过,Y=A;②当sel=0时,选择输入B通过,Y=B。

二选一选择器(mux2)由三个与非门(nand)和一个反相器(inv)构成(利用实验1 的与非门和反相器symbol即可)。

实验37 数字集成电路的版图设计在集成电路产品中,数字集成电路占据相当大的市场份额,有着广泛的应用领域。

数字集成电路的版图设计是设计过程中的重要关键步骤之一,版图设计与布局是关乎数字集成电路设计成败和品质优劣的重要环节,是数字集成电路生产的前提。

数字集成电路的版图设计实验是《半导体物理》、《场效应器件物理》、《集成电路制造技术》和《数字集成电路设计》等理论课程的重要实践。

本实验要求学生在Tanner公司开发的版图设计软件Ledit环境中,按照给定设计规则完成几个数字集成电路单元的版图设计与布局,以此来锻炼和提高学生的数字集成电路版图设计与布局能力,强化学生理论联系实际和灵活应用所学知识的能力。

一、实验原理1. Ledit软件简介Ledit软件是Tanner公司设计开发的用于集成电路版图设计与布局的软件,它包括有集成电路工艺图层与半导体器件定义、晶体管级集成电路版图布局、版图设计规则验证和集成电路提取与网表生成等重要功能单元。

它是一种简单易学的集成电路版图设计与布局开发软件,具有良好的人机交互界面,在集成电路的版图设计中有着重要的应用。

2. 集成电路版图的设计规则与验证在实际集成电路生产环节中,由于各条生产线工艺设备性能的不同、所使用的半导体材料物理特性的差异、工艺过程中存在的误差等诸多因素的影响,产生了一系列集成电路图形加工时的最小尺寸极限要求,这些尺寸的极限要求就是集成电路版图的设计规则。

在进行集成电路版图设计时,不违背这些设计规则的要求,集成电路版图的布局设计才可能是正确的。

图37.1给出了集成电路版图绘制过程中,基本图形之间,可能出现的相对关系示意图。

相对关系包括有:间距(Space)、宽度(Width)、交叠覆盖(Overlap)、延伸图37.1 集成电路版图基本图形间的相对位置176(Extension)、围绕(Enclose)和不同基本层间的间隙(Clearance)等等。

表37.1给出了Ledit软件环境下,特征尺寸为1.0μm (λ=1.0μm),P型衬底N阱CMOS工艺的部分设计规则。

实验38 模拟集成电路的版图设计模拟集成电路设计是现代集成电路设计的重要组成部分。

模拟集成电路的版图设计是模拟集成电路设计环节中的重要关键环节。

模拟集成电路版图设计的优劣直接影响着整个集成电路的性能和设计的成败。

本实验要求学生在系统地学习了《半导体物理》、《场效应器件物理》、《模拟集成电路设计》和《集成电路制造技术》等专业知识的基础上,使用Tanner公司设计开发的集成电路版图设计工具Ledit软件,独立完成CMOS模拟集成电路单元的版图设计和布局工作,提高模拟集成电路版图设计和布局能力,强化对模拟集成电路制造技术的理解和知识运用能力,培养学生初步的模拟集成电路版图设计能力。

一、实验原理1. 模拟集成电路版图中的器件与设计规则在模拟集成电路中,主要器件有NMOS、PMOS、NPN和PNP晶体管,二极管、电阻和电容等。

这些器件在Ledit软件中,实现的方法存在较大差异,但都是遵循器件的定义实现的。

器件的定义存储在以.ext为后缀的器件萃取文件中。

在Ledit软件环境下,P型衬底N阱CMOS 2P2M工艺下(两层多晶两层金属),模拟集成电路版图中器件的设计规则,除去与数字集成电路版图设计中通用的规则外,主要还有:NPN、PNP晶体管设计规则、电容设计规则和电阻设计规则等,表38.1中摘录了这些规则中的部分内容。

使用这些设计规则可以实现NPN、PNP、MOS电容和电阻等器件版图。

=1.0μm部分设计规则表38.1 P型衬底N阱CMOS工艺下,182在绘制模拟集成电路版图时,所绘制的各种基本图形尺寸不能小于这些设计规则要求的尺寸,否则将导致设计规则错误。

在Ledit软件环境下,完成设计规则检查的功能称为设计规则检查(Design Rule Check,DRC)。

在集成电路版图绘制过程中,需要经常性地使用DRC功能来检查版图是否存在错误,这样做可以避免同时有太多违反设计规则的错误产生,决定着版图的完成效率和完成质量。

集成电路版图设计教师:* * *专业:* * *姓名:* * *学号:**********时间:2015.12.17第一部分:Tanner的L-Edit使用利用Tanner L-edit进行电路图的线路编辑;至少画出一个版图,并查看截面图。

(参考P58-63,P158-161,P172-205反相器、与、或门、串联、并联等,或则自己设计)反相器:CMOS反相器由NMOS晶体管和PMOS晶体管构成,我们将利用调用元件操作将已经完成的两个晶体管例化到反相器中,连接构成CMOS反相器。

反相器:i no u t PMOS:NMOS:第二部分设计规则检查和版图提取利用Tanner L-edit进行电路图的设计规则检查;至少画出一个版图。

(参考P161-171反相器、与、或门、串联、并联等,或则自己设计)。

可以选择上面的版图,给出设计规则检查的截图反相器:第三部分:Tanner的S-Edit使用利用Tanner S-edit进行电路图的线路编辑;至少画出一个原理图和符号图,并输出网表。

仿真测试结果截图。

(参考P206-217反相器、与、或门、串联、并联等,或则参考廖裕评-TannerPro集成电路设计实战指导,或者自己设计)V =5.0o u ti nV =5.0Ao u t B第四部分:电路图与版图一致性检查LVS是指电路图与版图的一致性检查,即用LVS比较器来比较版图与电路图所表述的电路是否相同。

将第一部分和第三部分版图与线路图的LVS并对LVS结果进行版图分析、修改;(参考P218-228)心得体会:通过这次L-edit软件的训练,我已经初步的掌握了L-edit软件的基本操作方法,并能够独立的运用该软件设计版图,灵活的根据要求绘制版图,我想这对我今后学习或者工作大有裨益,今后,我要更多的运用该软件,达到熟练掌握的目的,在我们锻炼动手能力的同时,学到更多的有关专业知识。

在做集成电路版图设计的过程中,我觉得这样做可以提高版图制作效率。

实验38 模拟集成电路的版图设计

模拟集成电路设计是现代集成电路设计的重要组成部分。

模拟集成电路的版图设计是模拟集成电路设计环节中的重要关键环节。

模拟集成电路版图设计的优劣直接影响着整个集成电路的性能和设计的成败。

本实验要求学生在系统地学习了《半导体物理》、《场效应器件物理》、《模拟集成电路设计》和《集成电路制造技术》等专业知识的基础上,使用Tanner公司设计开发的集成电路版图设计工具Ledit软件,独立完成CMOS模拟集成电路单元的版图设计和布局工作,提高模拟集成电路版图设计和布局能力,强化对模拟集成电路制造技术的理解和知识运用能力,培养学生初步的模拟集成电路版图设计能力。

一、实验原理

1. 模拟集成电路版图中的器件与设计规则

在模拟集成电路中,主要器件有NMOS、PMOS、NPN和PNP晶体管,二极管、电阻和电容等。

这些器件在Ledit软件中,实现的方法存在较大差异,但都是遵循器件的定义实现的。

器件的定义存储在以.ext为后缀的器件萃取文件中。

在Ledit软件环境下,P型衬底N阱CMOS 2P2M工艺下(两层多晶两层金属>,模拟集成电路版图中器件的设计规则,除去与数字集成电路版图设计中通用的规则外,主要还有:NPN、PNP晶体管设计规则、电容设计规则和电阻设计规则等,表38.1中摘录了这些规则中的部分内容。

使用这些设计规则可以实现NPN、PNP、MOS电容和电阻等器件版图。

表38.1 P型衬底N阱CMOS工艺下,=1.0μm部分设计规则

在绘制模拟集成电路版图时,所绘制的各种基本图形尺寸不能小于这些设计规则要求的尺寸,否则将导致设计规则错误。

在Ledit软件环境下,完成设计规则检查的功能称为设计规则检查<Design Rule Check,DRC)。

在集成电路版图绘制过程中,需要经常性地使用DRC功能来检查版图是否存在错误,这样做可以避免同时有太多违反设计规则的错误产生,决定着版图的完成效率和完成质量。

版图的设计规则是最小尺寸要求,将基本图形的尺寸有意绘制大些,DRC检查不认为是一种设计规则错误,但在整个集成电路中将造成芯片面积的浪费,所以在布局基本图形时,充分考虑器件必要的几何尺寸的同时,应使用尽量小的基本图形尺寸。

2.模拟集成电路版图图层定义

在Ledit软件环境中,P型衬底N阱CMOS 2P2M工艺条件下,模拟集成电路版图中除去与数字部分定义相同的基本层外,主要还定义有:一层多晶硅电阻识别标记<Poly Resistor ID)、二层多晶硅电阻识别标记<Poly2 Resistor ID)、N型扩散电阻识别标记<N Diff Resistor ID)、P型扩散电阻识别标记<P Diff Resistor ID)、P型基区电阻识别标记<P Base Resistor ID)和N 阱电阻识别标记<N Well Resistor ID)等电阻类基本层;一层多晶硅与二层多晶硅电容识别标记<Poly12 Capacitor ID)、NMOS电容识别标记<NMOS Capacitor ID)和PMOS电容识别标记<PMOS Capacitor ID)等电容类基本层;NPN晶体管识别标记<NPN ID)、P型基区识别标记<P Base)、横向PNP晶体管识别标记<LPNP ID)、横向PNP晶体管发射极识别标记<LPNP Emitter ID)和二极管识别标记<DIODE ID)等有源器件类基本层。

所有识别标记都是电路萃取标记。

使用上述模拟集成电路版图的基本层定义,可以用来制作MOS晶体管、双极晶体管、二极管、电阻和电容等器件。

集成电路版图中的基本层就是相关工艺的光刻掩模。

图38.1给出了NMOS、PMOS晶体管的纵向剖面结构。

图中有源区的不同,充分地说明了N型和P型选择区是重要的有源区掺杂类型识别标记。

图中是采用多支晶体管并联结构实现的较大宽长比晶体管。

图38.1 NMOS、PMOS晶体管的纵向剖面结构

图38.2绘出了NPN、PNP晶体管的纵向剖面结构。

左侧NPN晶体管存在P型基区,右侧PNP晶体管中没有类似结构,这正是纵向NPN晶体管与横向PNP晶体管的一个重要差别。

在CMOS工艺条件下,可以同时实现纵向NPN晶体管和横

向PNP晶体管的制造,实现了CMOS工艺与双极工艺的兼容。

图38.2 NPN、PNP晶体管的纵向剖面结构

图38.3画出了N型和P型扩散电阻,N型扩散电阻制作在P型衬底上,P型扩散电阻制作在N阱中。

左图电阻层与P型外延层之间、右图电阻层与N阱之间均构成了寄生PN结,通常采取将电阻所在的衬底或阱连接到适合电位,达到PN结反向偏置工作条件,从而减小寄生PN结对电阻性能的影响。

图38.3 N型、P型扩散电阻的纵向剖面结构

图38.4是由多晶硅制作的两种多晶硅电阻,可以看出它们都是制作在两层氧化层之间,通过氧化层实现上下方区域彼此绝缘。

在CMOS工艺条件下,多晶硅通常需要进行重掺杂,所以形成的多晶硅电阻通常具有较小的方块电阻。

图38.4 一层、二层多晶硅电阻的纵向剖面结构

图38.5为N阱电阻和P型基区电阻,由于N阱掺杂浓度较低,P型基区掺杂浓度较高,所以N阱适于制作阻值较大的电阻,P型基区电阻适于制作较小阻值的电阻。

图38.6是NMOS电容和PMOS电容版图的纵向剖面结构。

这些电容是以P型有源区或N型有源区作为电容的一个极板,一层多晶硅作为电容的另一个极板,采用平行板电容器原理制成的。

图38.5 N阱电阻、P型基区电阻的纵向剖面结构

图38.6 NMOS、PMOS电容的纵向剖面结构

3. 模拟集成电路版图单元布局实例

在模拟集成电路版图单元的绘制过程中,合理的版图分割和位置分布是保证版图布局设计品质的基本前提。

图38.7是一个模拟集成运算放大器电路的差分输入级部分,同时跨接了一个电容作为负载,右侧给出了各器件的尺寸参数,要求采用λ=1.0μm,特征尺寸为2.0μm的设计规则,在100μm×90μm芯片面积内完成版图的布局。

依据大宽长比晶体管版图布局原则,M1、M2采用18μm/2μm×4支晶体管并联连接,M3、M4采用10μm/2μm×2支晶体管并联连接,M5采用16μm/2μm×4支晶体管并联连接,电容C1采用NMOS电容结构,实现的版图布局形式见图38. 8,版图的最终尺寸为90μm×76μm。

图38.7 模拟电路单元逻辑电路及其W/L图38.8 模拟电路单元版图布局结果

二、实验内容

1. 采用

2.0U<λ=1.0μm)设计规则绘制完成N沟道电流镜负载电路单元版图,具体电路和各器件尺寸

见图38.9,总芯片面积不超过80μm×100μm;

图38.9N沟道电流镜负载电路与各器件参数

2. 采用2.0U<λ=1.0μm)设计规则完成威尔逊电流镜负载电路单元版图,具体电路和各器件尺寸见图38.10,总芯片面积不超过120μm×150μm;

图38.10威尔逊电流镜负载电路和各器件尺寸

3. 采用通用2.0U<λ=1.0μm)设计规则绘制完成高摆幅共源共栅电流漏单元版图,具体电路和各器件尺寸见图38.11,总芯片面积不超过110μm×110μm;

图38.11高摆幅共源共栅电流漏和各器件尺寸

4. 采用2.0U<λ=1.0μm)设计规则绘制完成标准共源共栅电流漏单元版图,具体电路和各器件尺寸见图38.12,总芯片面积在100μm×100μm以内。

图38.12标准共源共栅电流漏和各器件尺寸

三、实验数据处理

1. 写出生产各集成电路单元芯片所需光刻掩膜板的张数及其名称;

2. 写出各单元电路的电路网表(Spice语句>。

3.简要叙述电路所完成的功能。

四、实验思考题

1. 试从工艺角度来解释场区氧化和栅氧的含义与区别。

2.

在P型衬底N阱CMOS工艺中,存在的各种类型电阻,比较其方块电阻大小,说明理由。

3.

较大宽长比MOS晶体管可以采用多支晶体管并联连接的方式实现,请问宽长比为1/120的NMOS晶体管在版图设计时如何实现,有何措施?

4. 版图的λ设计规则是否可以不管特征尺寸的大小无条件约束地使用,为什么?

5. 说明数字集成电路与模拟集成电路在版图上的差别。

五、参考资料

[1] 李乃平,《集成电路制造技术》,华中理工大学出版社,1995。

[2]. Allen,R.E.等著,《CMOS模拟集成电路设计<第二版)》,电子工业出版社,2005。