组合逻辑电路实验报告

- 格式:docx

- 大小:29.12 KB

- 文档页数:3

组合逻辑电路实验报告

一实验目的和实验要求:

1、了解全加器的工作原理及其典型的应用,并验证4位全加器功能。

2、了解和掌握数字比较器的工作原理及如何比较大小。

3、了解和掌握译码器的工作原理,并测试其逻辑功能。

4、了解和掌握编码器的工作原理,并测试其逻辑单元。

5、了解和掌握数码选择器的工作原理及逻辑功能。

二实验方案:

器件:8-3编码器74HC148 3-8译码器74HC138 4选1数据选择器74HC153 4位数字比较器74HC85 4位全加器74HC283

在GDUT-J-1 数字电路试验箱中使用以上芯片,按照实验书连接好线路,通过拨码开关和LED开关来模拟逻辑输入和逻辑输出,观察LED灯的亮灭来判断逻辑状态,完成对应芯片的输入输出状态表(及真值表)来得出芯片的逻辑表达式。

三实验结果和数据处理:

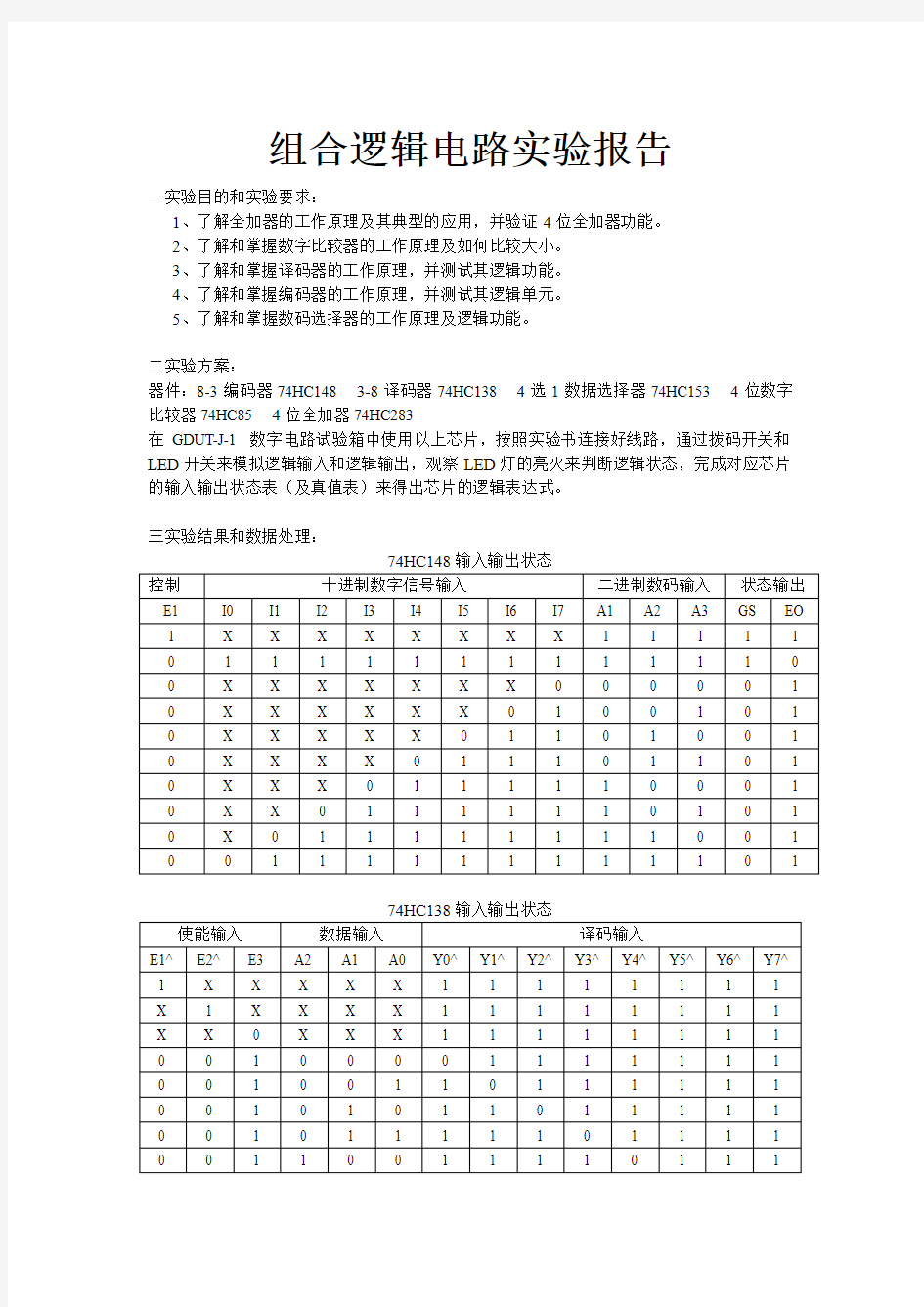

74HC148输入输出状态

控制十进制数字信号输入二进制数码输入状态输出E1 I0 I1 I2 I3 I4 I5 I6 I7 A1 A2 A3 GS EO

1 X X X X X X X X 1 1 1 1 1

0 1 1 1 1 1 1 1 1 1 1 1 1 0

0 X X X X X X X 0 0 0 0 0 1

0 X X X X X X 0 1 0 0 1 0 1

0 X X X X X 0 1 1 0 1 0 0 1

0 X X X X 0 1 1 1 0 1 1 0 1

0 X X X 0 1 1 1 1 1 0 0 0 1

0 X X 0 1 1 1 1 1 1 0 1 0 1

0 X 0 1 1 1 1 1 1 1 1 0 0 1

0 0 1 1 1 1 1 1 1 1 1 1 0 1

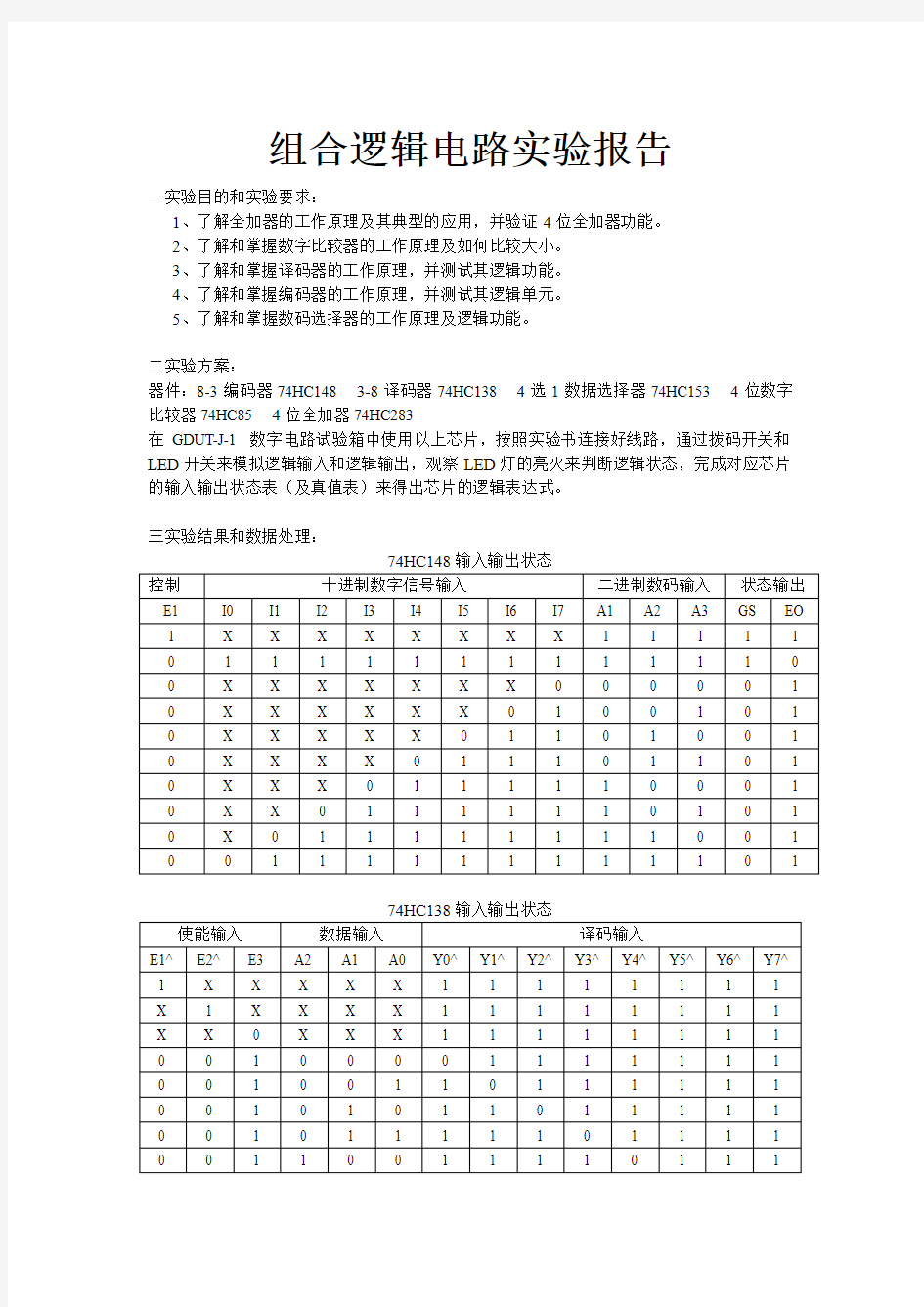

74HC138输入输出状态

使能输入数据输入译码输入

E1^ E2^ E3 A2 A1 A0 Y0^ Y1^ Y2^ Y3^ Y4^ Y5^ Y6^ Y7^ 1 X X X X X 1 1 1 1 1 1 1 1

X 1 X X X X 1 1 1 1 1 1 1 1

X X 0 X X X 1 1 1 1 1 1 1 1

0 0 1 0 0 0 0 1 1 1 1 1 1 1

0 0 1 0 0 1 1 0 1 1 1 1 1 1

0 0 1 0 1 0 1 1 0 1 1 1 1 1

0 0 1 0 1 1 1 1 1 0 1 1 1 1

0 0 1 1 0 0 1 1 1 1 0 1 1 1

0 0 1 1 1 0 1 1 1 1 1 1 0 1

0 0 1 1 1 1 1 1 1 1 1 1 1 0 (^表示逻辑非)

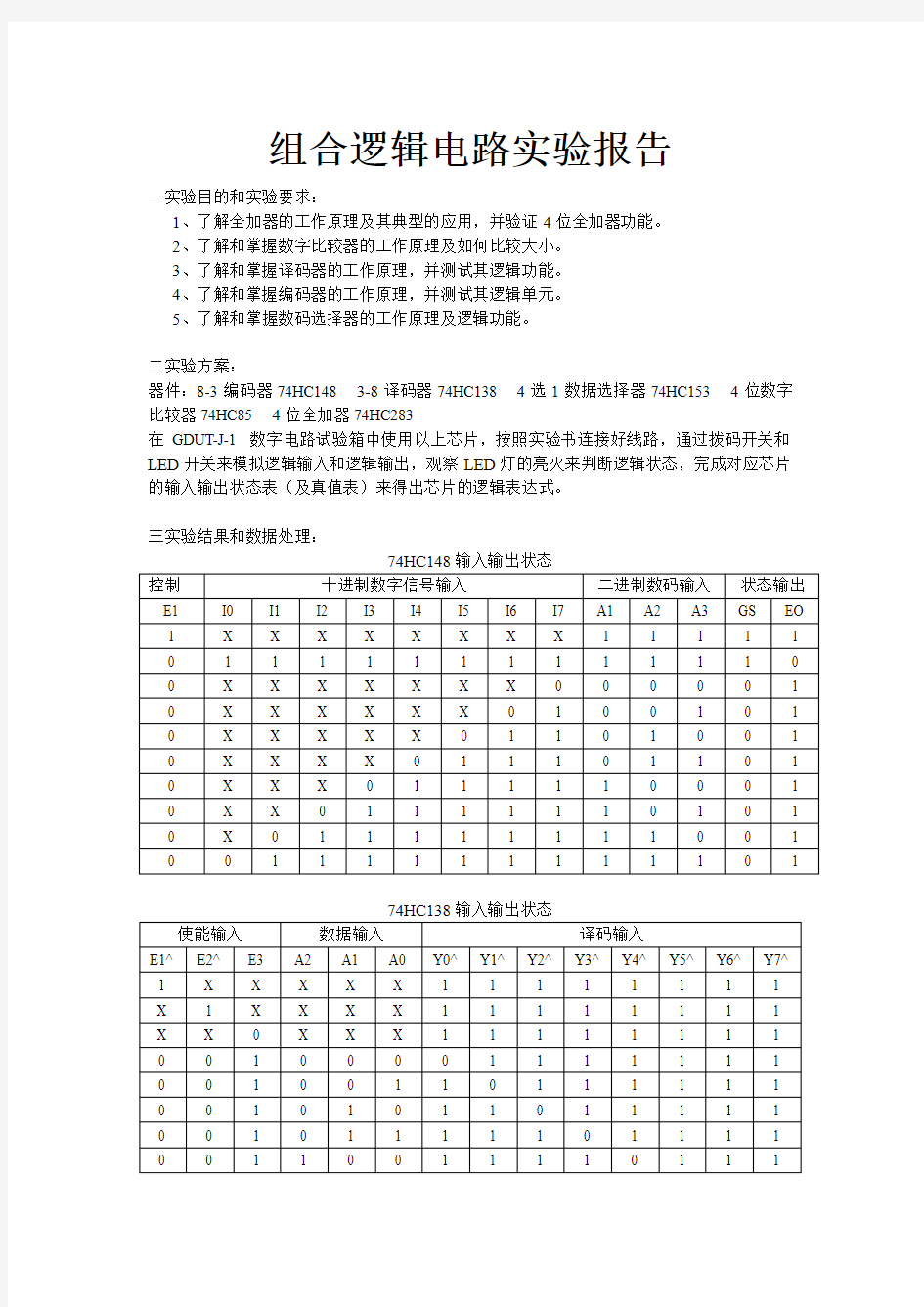

74HC153输入输出状态

选择输入数据输入输出使能输入输出S1 S0 II0 II1 II2 II3 1E^ 1Y X X X X X X 1 0

0 0 0 X X X 0 0

0 0 1 X X X 0 1

1 0 X X 0 X 0 0

1 0 X X 1 X 0 1

0 1 X 0 X X 0 0

0 1 X 1 X X 0 1

1 1 X X X 0 0 0

1 1 X X X 1 0 1 (^表示逻辑非)

74HC85输入输出状态

比较输入级联输入输出

A3 A2 A1 A0 B3 B2 B1 B0 1A>B 1AB A

0 X X X 1 X X X X X X 0 1 0

1 1 X X 1 0 X X X X X 1 0 0

0 0 X X 0 1 X X X X X 0 1 0

1 0 1 X 1 0 0 X X X X 1 0 0

0 0 0 X 0 0 1 X X X X 0 1 0

1 1 0 1 1 1 0 0 X X X 1 0 0

0 0 1 0 0 0 1 1 X X X 0 1 0

1 1 0 1 1 1 0 1 0 0 0 1 1 0

0 1 0 0 0 1 0 0 0 0 1 0 0 1

1 1 0 1 1 1 0 1 1 0 0 1 0 0

0 0 0 0 0 0 0 0 1 0 1 0 0 1

1 1 1 1 1 1 1 1 X 1 X 0 1 0

X 1 X 0 0 0

X 1 X 0 0 1

74HC283输入输出状态

4位加数输入4位被加数输入输出加法结果和进位

A4 A3 A2 A1 B4 B3 B2 B1 COUT S4 S3 S2 S1

1 1 1 1 1 1 1 1 1 1 1 1 0 0 1 1 1 0 0 1 0 0 1 0 0 1 0 1 0 0 0 1 1 0 0 1 0 1 0

0 1 0 1 0 1 1 1 0 1 1 0 0

1 0 0 0 0 1 1 1 0 1 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 0

四结论:

1、74HC148编码器编码输入低电平有效;编码输出是反码;当E1=0时编码器处于工作状态,E1=1时编码器处于禁止状态。

2、74HC148当E1^+E2^=0、E3=1,译码器处于工作状态,否则译码器被禁止;低电平输出有效。

五问题与讨论及实验总结:

1、组合电路中常用特定组合表示无效的逻辑状态。

2、在编码器和译码器中,一般输入输出信号数量关系为2n-1 六思考选择题: 用门电路设计4选1的逻辑电路。