用verilog语言编写交通灯程序.doc

- 格式:doc

- 大小:48.36 KB

- 文档页数:7

基于同步FSM交通信号控制器试验目的1、进一步熟悉FSM原理;2、交通信号控制逻辑的抽象建模方法;3、掌握同步有限状态机的置位与复位方法;3、掌握编写可综合的FSM一般指导原则;试验原理Verilog HDL和VHDL亍为描述用于综合还只有十年的历史,可综合风格的VerilogHDL和VHD啲语法只是它们各自语言的一个子集;HDL的可综合性研究近年来非常活跃,可综合子集的国际标准目前尚未最后形成,因此,各厂商的综合器所支持的HDL子集也略有不同;对于有关可综合的VerilogHDL的内容我们只着重于介绍RTL算法级和门级结构的描述;把一个时序逻辑抽象成一个同步有限状态机是设计可综合VerilogHDL 模块的关键。

有限状态机是设计各种时序逻辑电路的关键。

具体的有限状态机的原理可以参看试验七有关原理的介绍。

下面介绍一般的可综合有限状态机的编写原则每个always 块只能有一个事件控制@(event_expression) ,而且要紧跟在always 关键字后面;always 可以表示时序逻辑或者组合逻辑;也可以用always 块既表示电平敏感的锁存器又同时表示组合逻辑;带有posedge或negedge关键字的事件表达式表示边沿触发的时序逻辑,没有posedge或negedge关键字的表示组合逻辑或者电平敏感的锁存器,或者两者都表示;每个表示时序的always 块只能由一个时钟跳变沿触发,置位和复位最好也由该始终跳变沿触发;每个在always 块中赋值的信号必须定义为reg 类型或者整型;Always 块中应该避免组合反馈回路;实验步骤和实验内容1、本试验交通信号控制灯的逻辑关系该交通信号灯控制器用于控制一条主干道与一条乡村公路的交叉口的交通( 如图8-1 所示) ,它必须具有下面的功能;由于主干道上来往的车辆较多,因此控制主干道的交通信号灯具有最高优先级,在默认情况下,主干道的绿灯点亮;乡村公路间断性地有车经过,有车来时乡村公路的交通灯必须变为绿灯,只需维持一段足够的时间,以便让车通过。

课程设计报告2015-2016学年第2学期课程设计名称:电子综合设计EDA课程设计院(系):电子信息学院专业:电子信息工程班级:电子1313 :xx 学号:1310034303xx综合实验时间:2016/7/11-2016/7/15 指导教师:钟旭提交时间:2016/7/15电机学院课程设计任务书目录第一章设计原理 (4)1.1设计要求 (4)1.2设计思路和原理 (4)1.3实现方法 (4)第二章Verilog HDL程序设计 (6)2.1整体设计 (6)2.2 具体设计 (7)第三章仿真测试 (7)3.1 波形仿真 (7)第四章设计总结 (10)第一章设计原理1.1设计要求设计一个交通控制器,用LED显示灯表示交通状态,并以7段数码显示器显示当前状态剩余秒数主干道绿灯亮时,支干道红灯亮;反之亦然,二者交替允许通行,主干道每次放行35s,支干道每次放行25s。

每次由绿灯变为红灯的过程中,亮光的黄灯作为过渡,黄灯的时间为5s。

能进行特殊状态显示,特殊状态时东西、南北路口均显示红灯状态。

用LED灯显示倒计时,并且能实现总体清零功能,计数器由初始状态开始计数,对应状态的显示灯亮。

能实现特殊状态的功能显示。

[1]1.2设计思路和原理(1) 主、支干道用传感器检测车辆到来情况,实验电路用逻辑开关代替。

(2) 选择1HZ时钟脉冲作为系统时钟。

(3) 45s、25s、5s定时信号可用顺计时,也可用倒计时,计时起始信号由主控电路给出,每当计满所需时间,启、闭三色信号灯,并启动另一计时电路。

(4) 交通灯状态变化如表1及图1所示:表1 交通灯状态图检测到支状态2状态1状态0Emergency路无行人和车辆图1 交通灯状态图(5) 交通灯设计输入信号4个:CLK(时钟),EN(使能),EMERGENCY(紧急),BCHECK(检测) ;输出信号4个:LAMPA(主干道信号灯),LAMPB(支干道信号灯),ACOUNT(主干道计数器),BCOUNT(支干道计数器)。

交通灯控制的verilog实现12赵宪文王兰兰(1.天津东方凯发电气自动化技术有限公司天津 300384;2.天津理工大学电子信息工程学院天津 300384)摘 要:本设计用于控制一个十字路口南北和东西方向的交通灯,让其按特定的规律进行变化,以维持城市的交通秩序。

是在Max + Plus Ⅱ开发平台上使用Verilog HDL语言进行开发的。

其主要功能模块包括分频器、控制器以及译码电路。

基于FPGA的交通灯控制系统的系统功能和设计过程都做出详细的阐述。

设计完成后在计算机上进行仿真,经测试,该系统工作性能稳定,实用性强,易于操作,维护简单。

关键词: Max+Plus 2;Verilog HDL;交通灯控制;FPGA中图分类号:TP39 文献标识码:A 文章编号:1671-7597(2011)0720061-030 引言从状态转换表中可以看出,每个方向四种灯依次按照如下顺序点亮,并不断的循环:红绿灯安装在各个道口上,是疏导交通车辆最常见和最有效的手段。

绿灯>黄灯>左拐灯>黄灯>红灯这一技术起源于19世纪。

信号灯的出现,使交通得以有效管制,对于疏导并且每个方向红灯亮的时间应该与另一方向的绿灯、黄灯、左拐、黄交通流量、提高道路通行能力,减少交通事故有明显效果。

灯亮的时间相同。

黄灯亮起来的的作用是用来在绿灯和左拐灯后进行缓实现路口交通灯系统的控制方法很多。

可以用标准逻辑器件。

可编程冲,以提醒行人该方向马上就要禁行了。

控制器PLC。

单片机等方案来实现。

但是这些控制方法的功能修改及调试2 软件设计及仿真都需要硬件电路的支持,在一定程度上增加了功能修改及系统调试的困难。

因此,在设计中采用EDA技术,应用目前广泛应用的Verilog HDL硬件根据交通控制器要实现的功能,考虑两个并行执行的always模块来分电路描述语言,实现交通灯系统控制器的设计,利用MAX+PLUS 集成开发别控制A和B两个方向的四盏灯,这两个always模块使用同一个时钟信号,环境进行综合、仿真,并下载到FPGA中,完成系统的控制作用。

交通灯控制器专业:电子信息科学与技术_班级:学号:学生姓名:指导教师:*** _摘要交通灯是城市交通监管系统的重要组成部分,对于保证机动车辆的安全运行,维持城市道路的顺畅起到了重要作用。

目前很多城市交叉路口的交通灯实行的是定时控制,灯亮的时间是预先设定好的,在时间和空间方面的应变性能较差,一定程度上造成了交通资源的浪费,加重了道路交通压力。

本文在EDA技术的基础上,利用FPGA的相关知识设计了交通灯控制系统,可以根据实际情况对灯亮时间进行自由调整,通过数码管显示等待时间,点阵显示运行状态,蜂鸣器提示紧急状况,很好地维护了道路的交通规则。

整个设计系统通过Quartus Ⅱ软件中的Verilog HDL语言进行代码编写,并下载到FPGA器件中进行硬件调试,验证了设计的交通信号灯控制电路完全可以实现预定的功能,具有一定的实用性。

关键字:交通灯、定时控制、FPGA、Verilog HDL一、设计原理根据交通灯循环顺序表可以得到如表1的循环状态表,遇到紧急状况的时候,这时候有东西通行、南北通行和全部禁行三种情况,紧急状态结束后条件满足的情况下状态依次往后跳转。

表1 交通灯循环状态表1. 方案比较方案一:直接用GPIO口驱动双色点阵;方案二:用两块3-8译码器控制双色点阵,一个控制红色,另一个控制绿色;方案三:用一块4-16选择器控制双色点阵;通过比较方案一需要24个GPIO,方案二需要14个GPIO口,而方案三只需要12个GPIO 口,考虑到IO口的数量限制和资源的优化,故选择方案三,硬件部分还包括Led灯和蜂鸣器,用洞洞板搭建好了硬件电路。

2.系统框架图1 状态机状态转换图随着现代生活节奏的加快,人们出门便更多地选择自家的交通工具,这无疑加大了交通流量,如何控制十字路口的红绿灯,便显得相当的重要。

简单的,有效地控制红绿灯,是减小客流量,甚至减少交通事故的重要保障。

而此次课题,我选择了交通灯控制电路,能熟悉Verilog HDL 硬件描述语言在现实生活中的重要意义,为以后的学习和工作打好基础。

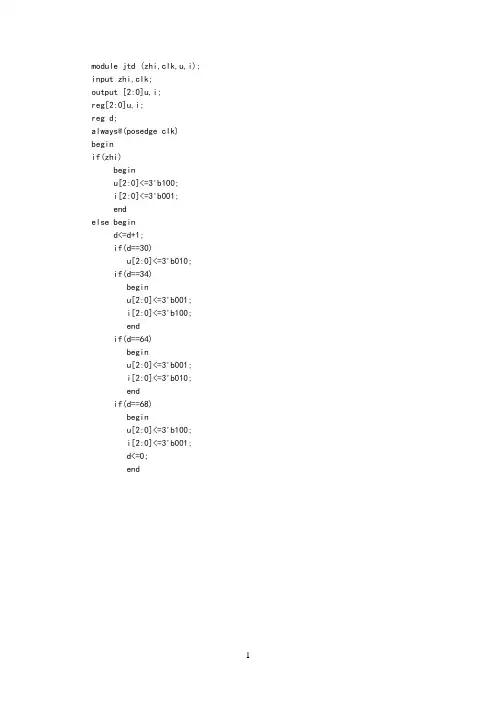

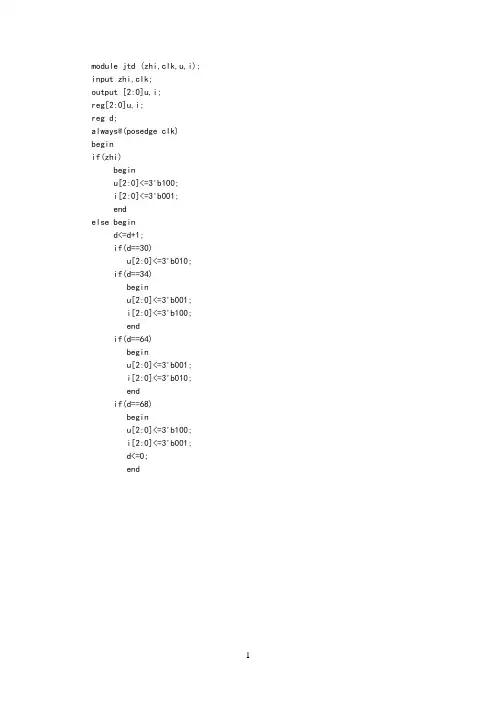

module jtd (zhi,clk,u,i); input zhi,clk;output [2:0]u,i;reg[2:0]u,i;reg d;always@(posedge clk) beginif(zhi)beginu[2:0]<=3'b100;i[2:0]<=3'b001;endelse begind<=d+1;if(d==30)u[2:0]<=3'b010; if(d==34)beginu[2:0]<=3'b001; i[2:0]<=3'b100; endif(d==64)beginu[2:0]<=3'b001; i[2:0]<=3'b010; endif(d==68)beginu[2:0]<=3'b100; i[2:0]<=3'b001; d<=0;endmodule jtd(zhi,u,i,clk,rst);input zhi,clk,rst;output [2:0]u,i;reg [2:0]u,i;reg[4:0]state;reg [5:0]d;initial d=0;parameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always@(posedge clk)beginif(!rst) begin state<=s0;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:begin u[2:0]<=3'b100;i[2:0]<=3'b001;if(zhi)begin state<=s0;end else state<=s4;ends0:begin u[2:0]<=3'b100;i[2:0]<=3'b001;d=d+1;if(d==30)begin state<=s1;d=0;end else state<=s0;ends1:begin u[2:0]<=3'b010;i[2:0]<=3'b001;d=d+1;if(d==4)begin state<=s2;d=0;end else state<=s1;ends2:begin u[2:0]<=3'b001;i[2:0]<=3'b100;d=d+1;if(d==30) begin state<=s3;d=0;end else state<=s2;ends3:begin u[2:0]<=3'b001;i[2:0]<=3'b010;d=d+1;if(d==4)begin state<=s4;d=0;end else state<=s3;enddefault: state<=s4;endcaseendendendmodule黄灯闪module jtde(zhi,u,i,clk,rst);input zhi,clk,rst;output [2:0]u,i;reg [2:0]u,i;reg[4:0]state;reg [6:0]d;initial d=0;parameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always@(posedge clk)beginif(!rst) begin state<=s4;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:begin u[2:0]<=3'b100;i[2:0]<=3'b001;if(zhi)begin state<=s0;end else state<=s4;ends0:begin u[2:0]<=3'b100;i[2:0]<=3'b001;d=d+1;if(d==30)begin state<=s1;d=0;end else state<=s0;ends1:begin d=d+1;if(d==1)begin u[2:0]<=3'b000;i[2:0]<=3'b001;state<=s1;endif(d==2)begin u[2:0]<=3'b010;i[2:0]<=3'b001;state<=s1;endif(d==3)begin u[2:0]<=3'b000;i[2:0]<=3'b001;state<=s1;endif(d==4)begin u[2:0]<=3'b010;i[2:0]<=3'b001;state<=s2;d=0;endends2:begin u[2:0]<=3'b001;i[2:0]<=3'b100;d=d+1;if(d==30) begin state<=s3;d=0;end else state<=s2;ends3:begin d=d+1;if(d==1)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==2)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s3;endif(d==3)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==4)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s4;d=0;endenddefault: state<=s4;endcaseendend黄灯闪且倒计时module mnb(zhi,u,i,clk,rst,ugx,usx,igx,isx);input zhi,clk,rst;output [2:0]u,i;output [3:0]ugx,usx,igx,isx;reg [2:0]u,i;reg[4:0]state;reg [4:0]ugx,usx,igx,isx;reg [6:0]d,e,f;initialbegin d<=0;e<=30;f<=34;endparameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always@(posedge clk)beginif(!rst) begin state<=s4;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:beginu[2:0]<=3'b100;i[2:0]<=3'b001;ugx<=0;usx<=0;igx<=0;isx<=0;if(zhi)beginstate<=s0;d<=0;e<=30;f<=35;end else state<=s4;ends0:beginu[2:0]<=3'b100;i[2:0]<=3'b001;ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e< =e-1;f<=f-1;if(d==30)begin state<=s1;d<=0;e<=4;f<=4;end else state<=s0;ends1:begin ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;e<=e-1;f<=f-1;if(d==0)begin u[2:0]<=3'b010;i[2:0]<=3'b001;d<=d+1;state<=s1;end if(d==1)begin u[2:0]<=3'b000;i[2:0]<=3'b001;d<=d+1;state<=s1;end if(d==2)begin u[2:0]<=3'b010;i[2:0]<=3'b001;d<=d+1;state<=s1;end if(d==3)beginu[2:0]<=3'b000;i[2:0]<=3'b001;state<=s2;d<=0;e<=35;f<=30;endends2:beginu[2:0]<=3'b001;i[2:0]<=3'b100;ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e< =e-1;f<=f-1;if(d==30) begin state<=s3;d<=0;e<=4;f<=4;end else state<=s2;ends3:begin ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e<=e-1;f<=f-1;if(d==1)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==2)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s3;endif(d==3)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==4)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s4;d<=0;endenddefault: state<=s4;endcaseendendendmodule黄灯闪。

module jtd (zhi,clk,u,i); input zhi,clk;output [2:0]u,i;reg[2:0]u,i;reg d;always@(posedge clk) beginif(zhi)beginu[2:0]<=3'b100;i[2:0]<=3'b001;endelse begind<=d+1;if(d==30)u[2:0]<=3'b010; if(d==34)beginu[2:0]<=3'b001; i[2:0]<=3'b100; endif(d==64)beginu[2:0]<=3'b001; i[2:0]<=3'b010; endif(d==68)beginu[2:0]<=3'b100; i[2:0]<=3'b001; d<=0;endmodule jtd(zhi,u,i,clk,rst);input zhi,clk,rst;output [2:0]u,i;reg [2:0]u,i;reg[4:0]state;reg [5:0]d;initial d=0;parameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always@(posedge clk)beginif(!rst) begin state<=s0;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:begin u[2:0]<=3'b100;i[2:0]<=3'b001;if(zhi)begin state<=s0;end else state<=s4;ends0:begin u[2:0]<=3'b100;i[2:0]<=3'b001;d=d+1;if(d==30)begin state<=s1;d=0;end else state<=s0;ends1:begin u[2:0]<=3'b010;i[2:0]<=3'b001;d=d+1;if(d==4)begin state<=s2;d=0;end else state<=s1;ends2:begin u[2:0]<=3'b001;i[2:0]<=3'b100;d=d+1;if(d==30) begin state<=s3;d=0;end else state<=s2;ends3:begin u[2:0]<=3'b001;i[2:0]<=3'b010;d=d+1;if(d==4)begin state<=s4;d=0;end else state<=s3;enddefault: state<=s4;endcaseendendendmodule黄灯闪module jtde(zhi,u,i,clk,rst);input zhi,clk,rst;output [2:0]u,i;reg [2:0]u,i;reg[4:0]state;reg [6:0]d;initial d=0;parameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always@(posedge clk)beginif(!rst) begin state<=s4;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:begin u[2:0]<=3'b100;i[2:0]<=3'b001;if(zhi)begin state<=s0;end else state<=s4;ends0:begin u[2:0]<=3'b100;i[2:0]<=3'b001;d=d+1;if(d==30)begin state<=s1;d=0;end else state<=s0;ends1:begin d=d+1;if(d==1)begin u[2:0]<=3'b000;i[2:0]<=3'b001;state<=s1;endif(d==2)begin u[2:0]<=3'b010;i[2:0]<=3'b001;state<=s1;endif(d==3)begin u[2:0]<=3'b000;i[2:0]<=3'b001;state<=s1;endif(d==4)begin u[2:0]<=3'b010;i[2:0]<=3'b001;state<=s2;d=0;endends2:begin u[2:0]<=3'b001;i[2:0]<=3'b100;d=d+1;if(d==30) begin state<=s3;d=0;end else state<=s2;ends3:begin d=d+1;if(d==1)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==2)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s3;endif(d==3)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==4)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s4;d=0;endenddefault: state<=s4;endcaseendend黄灯闪且倒计时module mnb(zhi,u,i,clk,rst,ugx,usx,igx,isx);input zhi,clk,rst;output [2:0]u,i;output [3:0]ugx,usx,igx,isx;reg [2:0]u,i;reg[4:0]state;reg [4:0]ugx,usx,igx,isx;reg [6:0]d,e,f;initialbegin d<=0;e<=30;f<=34;endparameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always@(posedge clk)beginif(!rst) begin state<=s4;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:beginu[2:0]<=3'b100;i[2:0]<=3'b001;ugx<=0;usx<=0;igx<=0;isx<=0;if(zhi)beginstate<=s0;d<=0;e<=30;f<=35;end else state<=s4;ends0:beginu[2:0]<=3'b100;i[2:0]<=3'b001;ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e< =e-1;f<=f-1;if(d==30)begin state<=s1;d<=0;e<=4;f<=4;end else state<=s0;ends1:begin ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;e<=e-1;f<=f-1;if(d==0)begin u[2:0]<=3'b010;i[2:0]<=3'b001;d<=d+1;state<=s1;end if(d==1)begin u[2:0]<=3'b000;i[2:0]<=3'b001;d<=d+1;state<=s1;end if(d==2)begin u[2:0]<=3'b010;i[2:0]<=3'b001;d<=d+1;state<=s1;end if(d==3)beginu[2:0]<=3'b000;i[2:0]<=3'b001;state<=s2;d<=0;e<=35;f<=30;endends2:beginu[2:0]<=3'b001;i[2:0]<=3'b100;ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e< =e-1;f<=f-1;if(d==30) begin state<=s3;d<=0;e<=4;f<=4;end else state<=s2;ends3:begin ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e<=e-1;f<=f-1;if(d==1)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==2)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s3;endif(d==3)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==4)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s4;d<=0;endenddefault: state<=s4;endcaseendendendmodule黄灯闪。

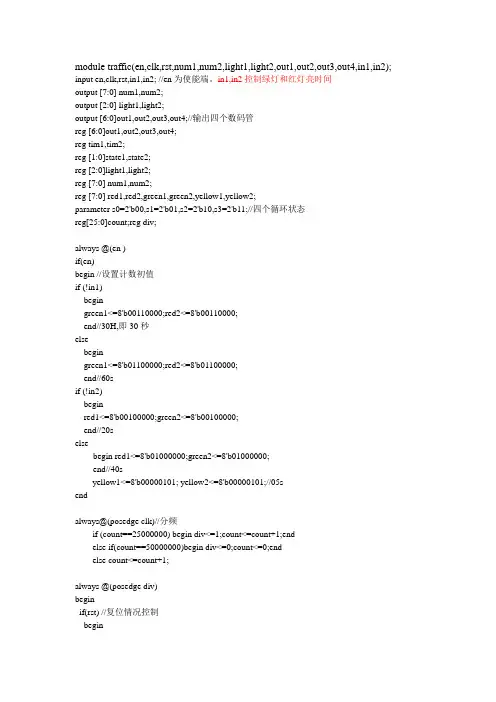

module traffic(en,clk,rst,num1,num2,light1,light2,out1,out2,out3,out4,in1,in2); input en,clk,rst,in1,in2; //en为使能端。

in1,in2控制绿灯和红灯亮时间output [7:0] num1,num2;output [2:0] light1,light2;output [6:0]out1,out2,out3,out4;//输出四个数码管reg [6:0]out1,out2,out3,out4;reg tim1,tim2;reg [1:0]state1,state2;reg [2:0]light1,light2;reg [7:0] num1,num2;reg [7:0] red1,red2,green1,green2,yellow1,yellow2;parameter s0=2'b00,s1=2'b01,s2=2'b10,s3=2'b11;//四个循环状态reg[25:0]count;reg div;always @(en )if(en)begin //设置计数初值if (!in1)begingreen1<=8'b00110000;red2<=8'b00110000;end//30H,即30秒elsebegingreen1<=8'b01100000;red2<=8'b01100000;end//60sif (!in2)beginred1<=8'b00100000;green2<=8'b00100000;end//20selsebegin red1<=8'b01000000;green2<=8'b01000000;end//40syellow1<=8'b00000101; yellow2<=8'b00000101;//05sendalways@(posedge clk)//分频if (count==25000000) begin div<=1;count<=count+1;endelse if(count==50000000)begin div<=0;count<=0;endelse count<=count+1;always @(posedge div)beginif(rst) //复位情况控制beginlight1<=3'b001;num1<=green1;endelse if(en)begin //使能有效开始控制计数if(!tim1) //开始控制begin //主干道交通灯点亮控制tim1<=1;case(state1)//状态机s0:begin num1<=green1;light1<=3'b001;state1<=s1;end s1:begin num1<=yellow1;light1<=3'b010;state1<=s2;end s2:begin num1<=red1;light1<=3'b100;state1<=s3;ends3:begin num1<=yellow1;light1<=3'b010;state1<=s0;end default:light1<=3'b100;endcaseendelsebegin //倒数计时if(num1>0)if(num1[3:0]==0)beginnum1[3:0]<=4'b1001;num1[7:4]<=num1[7:4]-1;//十位减1endelse num1[3:0]<=num1[3:0]-1; //个位减1 if(num1==1) tim1<=0;endendelsebeginlight1<=3'b010;num1=2'b00;tim1<=0;endendalways @(posedge div ) //从干道beginif(rst) //复位情况控制beginlight2<=3'b100;num2<=red2;endelse if(en)beginif(!tim2)begintim2<=1;case(state1)s0:begin num2<=red2;light2<=3'b100;state2<=s1;ends1:begin num2<=yellow1;light2<=3'b010;state2<=s2;ends2:begin num2<=green2;light2<=3'b001;state2<=s3;ends3:begin num2<=yellow2;light2<=3'b010;state2<=s0;enddefault:light2<=3'b100;endcaseendelsebegin //倒数计时if(num2>0)if(num2[3:0]==0)beginnum2[3:0]<=4'b1001;num2[7:4]<=num2[7:4]-1;endelse num2[3:0]<=num2[3:0]-1;if(num2==1) tim2<=0;endendelsebegintim2<=0;state2<=2'b00;light2<=3'b010;endendalways @(posedge clk)begin //数码管译码显示case(num1[3:0])4'b0000: out1<=~7'b0111111; //0 ,3F4'b0001: out1<=~7'b0000110; //1 ,064'b0010: out1<=~7'b1011011; //2 ,5B4'b0011: out1<=~7'b1001111; //3 ,4F4'b0100: out1<=~7'b1100110; //4 ,664'b0101: out1<=~7'b1101101; //5 ,6D4'b0110: out1<=~7'b1111101; //6 ,7D 4'b0111: out1<=~7'b0000111; //7 ,07 4'b1000: out1<=~7'b1111111; //8, 7F 4'b1001: out1<=~7'b1101111; //9, 6F default: out1<=~7'b0111111; //0 ,3F endcaseendalways @(posedge clk)begin //数码管译码显示case(num1[7:4])4'b0000: out2<=~7'b0111111; //0 ,3F 4'b0001: out2<=~7'b0000110; //1 ,06 4'b0010: out2<=~7'b1011011; //2 ,5B 4'b0011: out2<=~7'b1001111; //3 ,4F 4'b0100: out2<=~7'b1100110; //4 ,66 4'b0101: out2<=~7'b1101101; //5 ,6D 4'b0110: out2<=~7'b1111101; //6 ,7D 4'b0111: out2<=~7'b0000111; //7 ,07 4'b1000: out2<=~7'b1111111; //8, 7F 4'b1001: out2<=~7'b1101111; //9, 6F default: out2<=~7'b0111111; //0 ,3F endcaseendalways @(posedge clk)begin //数码管译码显示case(num2[3:0])4'b0000: out3<=~7'b0111111; //0 ,3F 4'b0001: out3<=~7'b0000110; //1 ,06 4'b0010: out3<=~7'b1011011; //2 ,5B 4'b0011: out3<=~7'b1001111; //3 ,4F 4'b0100: out3<=~7'b1100110; //4 ,66 4'b0101: out3<=~7'b1101101; //5 ,6D 4'b0110: out3<=~7'b1111101; //6 ,7D 4'b0111: out3<=~7'b0000111; //7 ,07 4'b1000: out3<=~7'b1111111; //8, 7F 4'b1001: out3<=~7'b1101111; //9, 6F default: out3<=~7'b0111111; //0 ,3F endcaseendalways @(posedge clk)begin //数码管译码显示case(num2[7:4])4'b0000: out4<=~7'b0111111; //0 ,3F 4'b0001: out4<=~7'b0000110; //1 ,06 4'b0010: out4<=~7'b1011011; //2 ,5B 4'b0011: out4<=~7'b1001111; //3 ,4F 4'b0100: out4<=~7'b1100110; //4 ,66 4'b0101: out4<=~7'b1101101; //5 ,6D 4'b0110: out4<=~7'b1111101; //6 ,7D 4'b0111: out4<=~7'b0000111; //7 ,07 4'b1000: out4<=~7'b1111111; //8, 7F 4'b1001: out4<=~7'b1101111; //9, 6F default: out4<=~7'b0111111; //0 ,3F endcaseendendmodule。

武汉科技大学课题:交通灯控制器的设计编号:17指导老师:冯玉林班级:自动化0703班姓名:筱启…………………………坚持,就是胜利………………………目录1. 设计内容与要求 (22. 交通灯控制系统的组成框图 (33. 交通灯控制电路的设计 (44. 交通灯控制电路设计的难点与解决方法 (55. 交通灯控制电路的Verilog 语句 (65. 交通灯控制电路的程序和波形分析 (126. EPF10K10LC84-4芯片引脚分配图 (207. 实验小结 (21一、设计内容与要求①设计一个十字路口交通信号灯的定时控制电路。

要求红、绿灯按一定的规律亮和灭,并在亮灯期间进行倒计时,并将运行时间用数码管显示出来。

②绿灯亮时,为该车道允许通行信号,红灯亮时,为该车道禁止通行信号。

要求主干道每次通行时间为99秒,支干道每次通行时间为30秒。

每次变换运行车道前绿灯闪烁,持续时间为5秒。

即车道要由主干道转换为支干道时,主干道在通行时间只剩下5秒钟时,绿灯闪烁显示,支干道仍为红灯,以便主干道上已过停车线的车继续通行,未过停车线的车停止通行。

同理,当车道由支干道转换为主干道时,支干道绿灯闪烁显示5秒钟,主干道仍为红灯。

③对红、绿灯的运行时间要能比较方便的进行重新设置。

④添加左转灯的控制,可自行到实际十字路口观看规律并实现。

对器件进行在系统编程和实验验证。

⑤用Verilog 语言对设计进行描述,设计一个测试方案,通过Muxplus 对设计进行仿真验证。

并能够下载到实验板上调试成功。

二、交通灯控制系统的组成框图交通信号灯控制原理图绿灯左拐灯红灯绿灯左拐灯红灯交通信号灯控制系统框图三、交通灯控制电路的设计交通灯控制器设计的重点是控制电路的设计,根据设计要求分析,控制电路的算法可用下图所示的ASM图描述。

各状态的详细说明如下:S0状态:主干道绿灯亮,支干道红灯亮,此时若主干道有车等待左拐,而且主干道绿灯已亮足规定的时间间隔Ts;在主干道绿灯亮了(Ts-5s后,则开始闪亮,直至绿灯亮了Ts;控制器发出状态转换信号Tempm==0,输出从状态S0转换到S1。

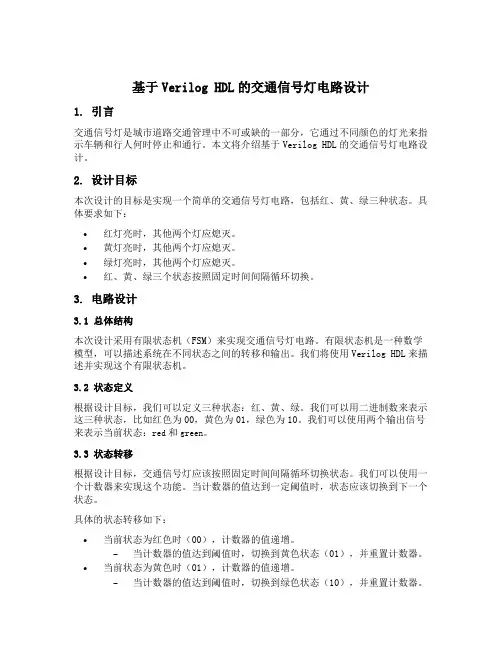

基于Verilog HDL的交通信号灯电路设计1. 引言交通信号灯是城市道路交通管理中不可或缺的一部分,它通过不同颜色的灯光来指示车辆和行人何时停止和通行。

本文将介绍基于Verilog HDL的交通信号灯电路设计。

2. 设计目标本次设计的目标是实现一个简单的交通信号灯电路,包括红、黄、绿三种状态。

具体要求如下:•红灯亮时,其他两个灯应熄灭。

•黄灯亮时,其他两个灯应熄灭。

•绿灯亮时,其他两个灯应熄灭。

•红、黄、绿三个状态按照固定时间间隔循环切换。

3. 电路设计3.1 总体结构本次设计采用有限状态机(FSM)来实现交通信号灯电路。

有限状态机是一种数学模型,可以描述系统在不同状态之间的转移和输出。

我们将使用Verilog HDL来描述并实现这个有限状态机。

3.2 状态定义根据设计目标,我们可以定义三种状态:红、黄、绿。

我们可以用二进制数来表示这三种状态,比如红色为00,黄色为01,绿色为10。

我们可以使用两个输出信号来表示当前状态:red和green。

3.3 状态转移根据设计目标,交通信号灯应该按照固定时间间隔循环切换状态。

我们可以使用一个计数器来实现这个功能。

当计数器的值达到一定阈值时,状态应该切换到下一个状态。

具体的状态转移如下:•当前状态为红色时(00),计数器的值递增。

–当计数器的值达到阈值时,切换到黄色状态(01),并重置计数器。

•当前状态为黄色时(01),计数器的值递增。

–当计数器的值达到阈值时,切换到绿色状态(10),并重置计数器。

•当前状态为绿色时(10),计数器的值递增。

–当计数器的值达到阈值时,切换到红色状态(00),并重置计数器。

3.4 Verilog HDL代码实现以下是基于Verilog HDL实现交通信号灯电路的代码:module traffic_light(input wire clk,output reg red,output reg yellow,output reg green);reg [1:0] state;reg [3:0] counter;parameter THRESHOLD = 4'b1010; // 阈值always @(posedge clk) begincase(state)2'b00: begin// 红灯状态if(counter == THRESHOLD) beginstate <= 2'b01; // 切换到黄灯状态counter <= 0;end else begincounter <= counter + 1;endend2'b01: begin// 黄灯状态if(counter == THRESHOLD) beginstate <= 2'b10; // 切换到绿灯状态counter <= 0;end else begincounter <= counter + 1;endend2'b10: begin// 绿灯状态if(counter == THRESHOLD) beginstate <= 2'b00; // 切换到红灯状态counter <= 0;end else begincounter <= counter + 1;endendendcaseendalways @(state) begincase(state)2'b00: begin// 红灯亮,其他两个灯熄灭red <= 1;yellow <= 0;green <= 0;end2'b01: begin// 黄灯亮,其他两个灯熄灭red <= 0;yellow <= 1;green <= 0;end2'b10: begin// 绿灯亮,其他两个灯熄灭red <= 0;yellow <= 0;green <= 1;endendcaseendendmodule4. 总结本文介绍了基于Verilog HDL的交通信号灯电路设计。

V e r i l o g-H D L的交通灯控制器设计(总16页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--课程设计报告2015-2016学年第2学期课程设计名称:电子综合设计EDA课程设计院(系):电子信息学院专业:电子信息工程班级:电子1313 姓名: xx 学号: 03xx综合实验时间: 2016/7/11-2016/7/15 指导教师:钟旭提交时间: 2016/7/15上海电机学院课程设计任务书目录第一章设计原理 ........................................... 错误!未定义书签。

设计要求.................................................. 错误!未定义书签。

设计思路和原理............................................ 错误!未定义书签。

实现方法.................................................. 错误!未定义书签。

第二章 Verilog HDL程序设计.............................. 错误!未定义书签。

整体设计.................................................. 错误!未定义书签。

具体设计................................................. 错误!未定义书签。

第三章仿真测试 ........................................... 错误!未定义书签。

波形仿真................................................. 错误!未定义书签。

第四章设计总结 ........................................... 错误!未定义书签。

中文摘要与关键词摘 要:V e r i l o g H D L作为一种规范的硬件描述语言,被广泛应用于电路的设计中。

他的设计描述可被不同的工具所支持,可用不同器件来实现。

利用V e r i l o g H D L语言自顶向下的设计方法设计交通灯控制系统,使其实现道路交通的正常运转,突出了其作为硬件描述语言的良好的可读性、可移植性和易理解等优点,并通过Q u a r t u s I I完成综合、仿真、进行管脚分配、绘出仿真波形及R T L 原理图。

此程序通过下载到F P G A芯片后,可应用于实际的交通灯控制系统中。

关键词:V e r i l o g H D L;硬件描述语言;状态;F P G A英文摘要与关键词A b s t r a c t:A s a c o m m o n l a n g u a g e f o r t h e d e s c r i p t i o n o f h a r d w a r e,V e r i l o g H D L i s w i d e l y a p p l i e d i n c i r c u i t d e s i g n i n g T h e d e s i g n d e s c r i p t i o nc a n b e s u p p o r t t ed b y d i f fe r e n t t o o l s a n d i m p l e m e n t e d b y d if f e r e n t d e v i c e sI n t h i s p a p e r,t h e p r o c e s s o f d e s i g n i n g t r a f f i c l i g h t c o n t r o l l e r s y s t e m b y t h e V e r i l o g H D L t o p d o w n d e s i g n m e t h o d i s p r e s e n t e d,w h i c h h a s m a d e t h er o a d t r a f f i c w o r k w e l l,t h e d e s i g n o f t h i s s y s t e m h a s s h o w n t h er e a d a b i l i t y,p o r t a b i l i t y a n d e a s i l y u n d e r s t a n d i n g o f V e r i l o g H D L a s a h a r dd e s c r i p t i o n l a n g u a g e C i r c u i t s y n t h e s i s、s i m u l a t i o n、t o p i n a l l o c a t i o n a n d R T L s i m u l a t i o n w a v e f o r m d r a w n s c h e m a t i c a r e p e r f o r m e d b y Q u a r t u s I I.T h ep r o g r a m c a n b e u s e d i n t h e t r u l y t r a f f i c l i g h t c o n t r o l l e r s y s t e m b yd o w n l o a d i n g t o t he F P G A c h i pK e y w o r d s:V e r i l o g H D L;h a r d w a r e d e s c r i p t i o n l a n g u a g e;s t a t e;F P G A第一章绪论近20年来,电子系统的设计方法都发生了深刻的变化。

modulepanpan(clock,aa,bb,cc,s,rst,clk,tt,RA,RB,GA,GB,Y A,YB,RC,RD,YC,YD,GC,GD,out1,out2,out3, out4,out5,out6,out7,out8);input clock,aa,bb,cc;input s,rst,clk,tt;output RA,RB,GA,GB,Y A,YB,RC,RD,YC,YD,GC,GD;output [6:0]out1,out2,out3,out4;output [6:0]out5,out6,out7,out8;reg [6:0]out1,out2,out3,out4;reg RA,RB,GA,GB,YA,YB,RC,RD,YC,YD,GC,GD;reg [2:0] state1,state2;reg [3:0] H1,L1,H2,L2;reg rt11,rt12,rt13,rt14,rt21,rt22,rt23,rt24;reg [25:0]count;reg [25:0]div;reg [3:0]A1,A2,B1,B2;reg [6:0]out5,out6,out7,out8;always@(posedge clk)// fenpinbeginif(rst)begincount=0;div=0;endelse if(count==10)begincount=0;div=1;endelsebegincount=count+1;div=0;endendalways@(posedge clock)beginif(aa)B1[3:0]<=4'd0000;A1[3:0]<=4'd0000;B2[3:0]<=4'd0000;A2[3:0]<=4'd0000;endelsebeginif(bb)beginA1[3:0]<=A1[3:0]+1'b1;if(A1[3:0]==4'b1001)beginA1[3:0]<=4'b0000;B1[3:0]<=B1[3:0]+1'b1;endendelse if(cc)beginA2[3:0]<=A2[3:0]+1'b1;if(A2[3:0]==4'b1001)beginA2[3:0]<=4'b0000;B2[3:0]<=B2[3:0]+1'b1;endendendendalways @(posedge div) //zhu gandaoif(rst)beginrt11<=0;rt12<=0;rt13<=0;rt14<=0;state1<=3'b001;if(tt)H1[3:0]<=4'b0110;L1[3:0]<=4'b0000;//60sendelsebeginH1[3:0]<=B1[3:0];L1[3:0]<=A1[3:0]; //30Sendendelse if(s==1&&rt11==1)beginstate1<=3'b001;rt11<=0;endelse if(s==1&&rt12==1)beginstate1<=3'b010;rt12<=0;endelse if(s==1&&rt13==1)beginstate1<=3'b011;rt13<=0;endelsebegincase(state1)3'b000: beginRA<=1'b1;GA<=1'b0;Y A<=1'b0;RC<=1'b1;GC<=1'b0;YC<=1'b0;H1[3:0]=4'b0000;L1[3:0]=4'b0000;end3'b001: beginGA<=1'b1;RA<=1'b0;YA<=1'b0;GC<=1'b1;RC<=1'b0;YC<=1'b0;if(!s)beginrt11<=1;state1<=3'b000;endelse if(H1[3:0]==0&&L1[3:0]==0)beginstate1<=3'b010;rt11<=0;H1[3:0]=4'b0000;L1[3:0]=4'b0101;//5sendelse if(H1[3:0]!=0&&L1[3:0]==0)beginH1[3:0]<=H1[3:0]-1'b1;L1[3:0]<=4'b1001;endelseL1[3:0]<=L1[3:0]-1'b1;end3'b010: beginY A<=1'b1;RA<=1'b0;GA<=1'b0;YC<=1'b1;RC<=1'b0;GC<=1'b0;if(!s)beginrt12<=1;state1<=3'b000;endelse if(H1[3:0]==0&&L1[3:0]==0)beginstate1<=3'b011;rt12<=0;if(tt)beginL1[3:0]=4'b0101;//55sendelsebeginH1[3:0]<=B2[3:0];L1[3:0]<=A2[3:0];//25sendendelse L1[3:0]<=L1[3:0]-1'b1;end3'b011: beginRA<=1'b1;Y A<=1'b0;GA<=1'b0;RC<=1'b1;YC<=1'b0;GC<=1'b0;if(!s)beginrt13<=1;state1<=3'b000;endelse if(H1[3:0]==0&&L1[3:0]==0)beginif(tt)beginL1[3:0]=4'b0000;H1[3:0]=4'b0110;//60sendelsebeginL1[3:0]<=A1[3:0];H1[3:0]<=B1[3:0];//30sendrt13<=0;state1<=3'b001;endelse if(H1[3:0]!=0&&L1[3:0]==0)beginH1[3:0]<=H1[3:0]-1'b1;L1[3:0]<=4'b1001;endenddefault: state1<=3'd000;endcaseendalways @(posedge div) //ci gandao if(rst)beginrt21<=0;rt22<=0;rt23<=0;rt24<=0;state2<=3'b001;if(tt)beginH2[3:0]<=4'b0110;L2[3:0]<=4'b0000;//60sendelsebeginH2[3:0]<=B1[3:0];L2[3:0]<=A1[3:0];//30sendendelse if(s==1&&rt21==1)beginstate2<=3'b001;rt21<=0;endelse if(s==1&&rt22==1)beginstate2<=3'b010;rt22<=0;endelse if(s==1&&rt23==1)beginstate2<=3'b011;rt23<=0;endelse if(s==1&&rt24==1)beginstate2<=3'b100;rt24<=0;endelsebegincase(state2)3'b000: beginRB<=1'b1;GB<=1'b0;YB<=1'b0;RD<=1'b1;GD<=1'b0;YD<=1'b0;H2[3:0]=4'b0000;L2[3:0]=4'b0000;end3'b001: beginRB<=1'b1;GB<=1'b0;YB<=1'b0;RD<=1'b1;GD<=1'b0;YD<=1'b0;if(!s)beginrt21<=1;state2<=3'b000;endelse if(H2[3:0]==0&&L2[3:0]==0)beginstate2<=3'b010;rt21<=0;if(tt)beginL2[3:0]=4'b0101;H2[3:0]=4'b0101;//55sendelsebeginL2[3:0]=A2[3:0];H2[3:0]=B2[3:0];//25sendendelse if(H2[3:0]!=0&&L2[3:0]==0)beginH2[3:0]<=H2[3:0]-1'b1;L2[3:0]<=4'b1001;endelseL2[3:0]<=L2[3:0]-1'b1;end3'b010: beginGB<=1'b1;YB<=1'b0;RB<=1'b0;GD<=1'b1;YD<=1'b0;RD<=1'b0;if(!s)beginrt22<=1;state2<=3'b000;endelse if(H2[3:0]==0&&L2[3:0]==0)beginstate2<=3'b011;rt22<=0;H2[3:0]=4'b0000;L2[3:0]=4'b0101;//5sendelse if(H2[3:0]!=0&&L2[3:0]==0)beginH2[3:0]<=H2[3:0]-1'b1;L2[3:0]<=4'b1001;endelseL2[3:0]<=L2[3:0]-1'b1;end3'b011: beginYB<=1'b1;GB<=1'b0;RB<=1'b0;YD<=1'b1;GD<=1'b0;RD<=1'b0;if(!s)beginrt23<=1;state2<=3'b000;endelse if(H2[3:0]==0&&L2[3:0]==0)beginrt23<=0;state2<=3'b001;if(tt)beginL2[3:0]<=4'b0000;H2[3:0]<=4'b0110;//60sendelsebeginL2[3:0]<=A1[3:0];H2[3:0]<=B1[3:0];//30sendendelse L2[3:0]<=L2[3:0]-1'b1;enddefault: state2<=3'd0;endcaseendalways @(A1) //xianshibegincase(A1[3:0])4'b0000: out5<=~7'b0111111; //0 ,3F4'b0001: out5<=~7'b0000110; //1 ,064'b0010: out5<=~7'b1011011; //2 ,5B4'b0011: out5<=~7'b1001111; //3 ,4F4'b0100: out5<=~7'b1100110; //4 ,664'b0101: out5<=~7'b1101101; //5 ,6D4'b0110: out5<=~7'b1111101; //6 ,7D4'b0111: out5<=~7'b0000111; //7 ,074'b1000: out5<=~7'b1111111; //8, 7F4'b1001: out5<=~7'b1101111; //9, 6Fdefault: out5<=~7'b0111111; //0 ,3Fendcaseendalways @(B1)begincase(B1[3:0])4'b0000: out6<=~7'b0111111; //0 ,3F 4'b0001: out6<=~7'b0000110; //1 ,06 4'b0010: out6<=~7'b1011011; //2 ,5B 4'b0011: out6<=~7'b1001111; //3 ,4F 4'b0100: out6<=~7'b1100110; //4 ,66 4'b0101: out6<=~7'b1101101; //5 ,6D 4'b0110: out6<=~7'b1111101; //6 ,7D 4'b0111: out6<=~7'b0000111; //7 ,07 4'b1000: out6<=~7'b1111111; //8, 7F 4'b1001: out6<=~7'b1101111; //9, 6F default: out6<=~7'b0111111; //0 ,3F endcaseendalways @(A2)begincase(A2[3:0])4'b0000: out7<=~7'b0111111; //0 ,3F 4'b0001: out7<=~7'b0000110; //1 ,06 4'b0010: out7<=~7'b1011011; //2 ,5B 4'b0011: out7<=~7'b1001111; //3 ,4F 4'b0100: out7<=~7'b1100110; //4 ,66 4'b0101: out7<=~7'b1101101; //5 ,6D 4'b0110: out7<=~7'b1111101; //6 ,7D 4'b0111: out7<=~7'b0000111; //7 ,07 4'b1000: out7<=~7'b1111111; //8, 7F 4'b1001: out7<=~7'b1101111; //9, 6F default: out7<=~7'b0111111; //0 ,3F endcaseendalways @(B2)begincase(B2[3:0])4'b0000: out8<=~7'b0111111; //0 ,3F 4'b0001: out8<=~7'b0000110; //1 ,06 4'b0010: out8<=~7'b1011011; //2 ,5B 4'b0011: out8<=~7'b1001111; //3 ,4F 4'b0100: out8<=~7'b1100110; //4 ,664'b0101: out8<=~7'b1101101; //5 ,6D4'b0110: out8<=~7'b1111101; //6 ,7D4'b0111: out8<=~7'b0000111; //7 ,074'b1000: out8<=~7'b1111111; //8, 7F4'b1001: out8<=~7'b1101111; //9, 6Fdefault: out8<=~7'b0111111; //0 ,3Fendcaseendalways @(L1) //xianshibegincase(L1[3:0])4'b0000: out1<=~7'b0111111; //0 ,3F4'b0001: out1<=~7'b0000110; //1 ,064'b0010: out1<=~7'b1011011; //2 ,5B4'b0011: out1<=~7'b1001111; //3 ,4F4'b0100: out1<=~7'b1100110; //4 ,664'b0101: out1<=~7'b1101101; //5 ,6D4'b0110: out1<=~7'b1111101; //6 ,7D4'b0111: out1<=~7'b0000111; //7 ,074'b1000: out1<=~7'b1111111; //8, 7F4'b1001: out1<=~7'b1101111; //9, 6F default: out1<=~7'b0111111; //0 ,3F endcaseendalways @(H1)begincase(H1[3:0])4'b0000: out2<=~7'b0111111; //0 ,3F4'b0001: out2<=~7'b0000110; //1 ,064'b0010: out2<=~7'b1011011; //2 ,5B4'b0011: out2<=~7'b1001111; //3 ,4F4'b0100: out2<=~7'b1100110; //4 ,664'b0101: out2<=~7'b1101101; //5 ,6D4'b0110: out2<=~7'b1111101; //6 ,7D4'b0111: out2<=~7'b0000111; //7 ,074'b1000: out2<=~7'b1111111; //8, 7F4'b1001: out2<=~7'b1101111; //9, 6F default: out2<=~7'b0111111; //0 ,3Fendcaseendalways @(L2)begincase(L2[3:0])4'b0000: out3<=~7'b0111111; //0 ,3F 4'b0001: out3<=~7'b0000110; //1 ,06 4'b0010: out3<=~7'b1011011; //2 ,5B 4'b0011: out3<=~7'b1001111; //3 ,4F 4'b0100: out3<=~7'b1100110; //4 ,66 4'b0101: out3<=~7'b1101101; //5 ,6D 4'b0110: out3<=~7'b1111101; //6 ,7D 4'b0111: out3<=~7'b0000111; //7 ,07 4'b1000: out3<=~7'b1111111; //8, 7F 4'b1001: out3<=~7'b1101111; //9, 6F default: out3<=~7'b0111111; //0 ,3F endcaseendalways @(H2)begincase(H2[3:0])4'b0000: out4<=~7'b0111111; //0 ,3F 4'b0001: out4<=~7'b0000110; //1 ,06 4'b0010: out4<=~7'b1011011; //2 ,5B 4'b0011: out4<=~7'b1001111; //3 ,4F 4'b0100: out4<=~7'b1100110; //4 ,66 4'b0101: out4<=~7'b1101101; //5 ,6D 4'b0110: out4<=~7'b1111101; //6 ,7D 4'b0111: out4<=~7'b0000111; //7 ,07 4'b1000: out4<=~7'b1111111; //8, 7F 4'b1001: out4<=~7'b1101111; //9, 6F default: out4<=~7'b0111111; //0 ,3F endcaseendendmodule。

西北工业大学实验报告》FPGA《学院:软件与微电子学院2011303596 号:学名:姓杨清山专业:微电子学2013/11/11 实验时间:毅字楼335 实验地点:韩兵指导教师:西北工业大学2013 年11 月2.总体设计框图及说明:图一输入:clk 全局时钟信号,50MHzrst 全局复位端,高电平有效输出:ctrl_1s 倒计时个位上数字ctrl_10s 倒计时十位上数字blu,yel,red 各个灯状态框图说明:状态机的输入,只有时钟信号clk和复位信号reset.输出为数码管十位和个位的二进制显示状态以及三个灯的颜色显示(blu,yel,red,分别是绿黄红灯,“1”表示灯亮,“0”表示灭)。

输入clk的频率很大,需要通过计数器对其进行分频。

首先计数产生一个1Hz的输出,通过该输出再次循环计数,产生周期为130的计数变量,从而控制各个灯的亮灭。

而控制黄灯闪烁的分频,为方便起见,仍以1s为单位,每秒钟改变一次。

嵌套语句来控制三灯亮与灭,同时间接地进行倒计时的过程,输出个位和十位上的数,if用.输入端口:din_1s 显示器个位数据,由控制模块输入din_10s 显示器十位数据,由控制模块输入输出端口:led_data_1s 显示器个位数据的译码led_data_10s 显示器十位数据的译码时序说明:和clk(50MHz) (系统时钟)并间接受此模块接受主模块输出的个位和十位的数值控制,上图中blu,yel,red,三个信号反映的绿黄红交通灯的状态,其中包括绿灯亮60秒,黄灯以2HZ为周期闪烁,红灯亮60s,总周期为130s。

上图为循环控制变量的值随分频后信号从129到0的循环计数。

综合结果:顶层及控制,分频模块的综合RTL级电路如图:译码显示模块的综合如下:RTL级门级6.代码及注释此为顶层及控制模块代码:`include ./decode.vmodule bulb(clk,rst,red,blu,yel,led1,led10);input clk,rst;output blu,yel,red,led1,led10;reg red,yel,blu;wire [6:0] led1;wire [6:0] led10;reg[3:0] out10,out1;reg[5:0] j;reg[7:0] k; //j,kreg clk1;//initialbegink='d129;blu<=0;。

交通灯

一、 实验目的

写一个交通灯,要求:

① 有东西南北四个方向,两组交通灯轮流交替变换,其中,红灯时间为

30个时间单位,绿灯时间为25个时间单位,黄灯时间为5个时间单位。

最后用modelsim软件进行仿真。

② 要求设计是一个可综合设计。

二、 实验原理

根据实验要求的逻辑功能描述,可以分析得出原理图如下:

控制器即可以设计为一个有限状态机的形式:

E-W方向 状态 0—— S-N方向 25——30—— 状态

55——60

R 方向 Y G 25 R 30 Y G 55

1 东0 ew 0 红 1 0 0 绿 IDLE 黄

西方向 红

1 南北方向 0 sn 0 绿 0 黄 0 1 红 S1 红

1 0 0 0 1 0 S2

0 0 1 1 0 0 S3

0 1 0 1 0 0 S4

根据实验要求画出控制器的状态转移图如下:

三、 代码

1、 源代码

(1)控制器模块

module traffic_lights(clk,rst,count,ew,sn); input clk,rst;

input[5:0] count; output[2:0] ew,sn; reg[2:0] ew,sn; reg[3:0]

state;

parameter Idle=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100;

always @(posedge clk) if(!rst)

begin

state<=Idle; end else

casex(state) Idle: if(rst)

begin

state<=s1;

end

s1: if(count=='d25)

begin

state<=s2; end

s2: if(count=='d30) begin

state<=s3; end

s3: if(count=='d55)

begin

state<=s4; end

s4: if(count=='d60) begin

state<=s1; end

endcase

always @(posedge clk) begin if(!rst) begin

ew<=3'b100; sn<=3'b100; end

else

casex(state) Idle: if(rst)

begin

ew<=3'b100;

sn<=3'b001; end

s1: if(count=='d25) begin

ew<=3'b100;

sn<=3'b010; end

s2: if(count=='d30) begin

ew<=3'b001;

sn<=3'b100; end

s3: if(count=='d55) begin

ew<=3'b010;

sn<=3'b100; end

s4: if(count=='d60) begin

ew<=3'b100;

sn<=3'b001; end

default: state<=Idle; endcase end

endmodule (2)计数器模块

module counter(en,clk,rst,out); output[5:0]out; input en,clk,rst;

reg[5:0] out;

always@(posedge clk or negedge rst) begin if(!rst)

out<='d0; else if(!en&&out<'d60) out<=out+1;

else

out<='d1; end

endmodule

(3)将控制器与计数器进行连接

module traffic_lights_top(out,clk,rst,en,ew,sn); input clk,rst,en;

output[2:0] ew,sn; output[5:0]out; wire[5:0] out;

traffic_lights u1(

.clk(clk), .rst(rst),

.count(out), .ew(ew),

.sn(sn) ); counter u2(

.en(en), .clk(clk),

.rst(rst), .out(out)

);

endmodule

2、激励

`timescale 1ns/100ps module traffic_lights_tb;

reg clk,rst,en;

wire[2:0] ew,sn; wire[5:0]out;

traffic_lights_top m(

.clk(clk), .rst(rst

),

.en(en), .ew(ew),

.sn(sn), .out(out)

);

always

#5 clk=~clk; initial

en<=1; initial

begin

clk<=1;

en<=0;

rst<=0;

#5 rst<=1;

end endmodule 四、 仿真波形

(图一)

(图二)

五、波形说明

波形图中,从上至下依次为:时钟信号clk、复位信号rst、计数器使能

端en、东西方向上灯的状态ew、南北方向上灯的状态sn、计数器的输出

out。该程序实现的功能是在一个十字路口的交通灯的轮流交替变换: 灯

的状态

图一可以完整的看到60个时间单位内两个方向上灯交替的状况

图二可以清楚的看到在时间从0——30过程中灯的跳变时间和结果。

五、 实验过程中遇到的问题及解决方法

1、在实验过程中得到的波形图跟我设计的时间间隔不一致,仔细检查过

后发现是因为控制器和计数器没有很好的连接在一起,导致灯的跳变跟计

数器的控制脱离了,修改之后得到时间间隔比例跟设计一致的波形。

2、在检查波形的过程中发现计数器实现的不是模60,而是模64,将计数

器程序中的选择条件从if(!en)改为if(!en&&out<'d60)之后得到了自己

想要的计数器。

六、 实验心得

刚开始,程序调试过程中始终都有些莫名其妙的错误,自己只能凭着自己

的理解和单纯靠一些感觉去修改。有时候越改错误越多,到后来程序显示

没有错误了,但是仿真却无法执行,一长串的警告看的我有点崩溃。静下

心来后从头开始分析每一句的程序,最后发现其实只是一个很小的失误。