GF2m上的一种可并行快速乘法器结构

- 格式:pdf

- 大小:274.62 KB

- 文档页数:4

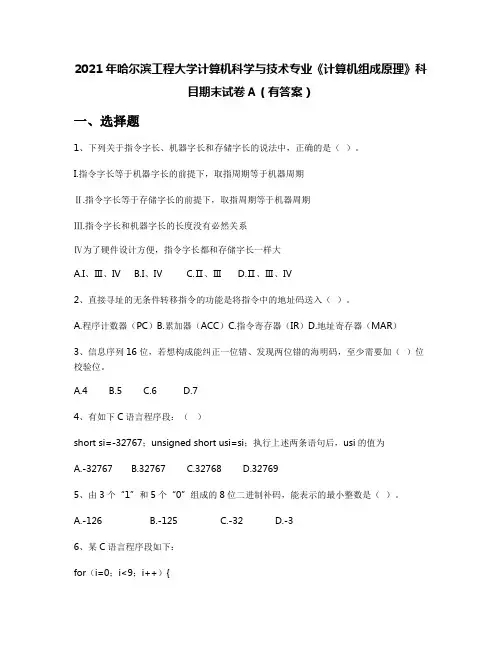

2021年哈尔滨工程大学计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、下列关于指令字长、机器字长和存储字长的说法中,正确的是()。

I.指令字长等于机器字长的前提下,取指周期等于机器周期Ⅱ.指令字长等于存储字长的前提下,取指周期等于机器周期Ⅲ.指令字长和机器字长的长度没有必然关系Ⅳ为了硬件设计方便,指令字长都和存储字长一样大A.I、Ⅲ、IVB.I、ⅣC.Ⅱ、ⅢD.Ⅱ、Ⅲ、Ⅳ2、直接寻址的无条件转移指令的功能是将指令中的地址码送入()。

A.程序计数器(PC)B.累加器(ACC)C.指令寄存器(IR)D.地址寄存器(MAR)3、信息序列16位,若想构成能纠正一位错、发现两位错的海明码,至少需要加()位校验位。

A.4B.5C.6D.74、有如下C语言程序段:()short si=-32767;unsigned short usi=si;执行上述两条语句后,usi的值为A.-32767B.32767C.32768D.327695、由3个“1”和5个“0”组成的8位二进制补码,能表示的最小整数是()。

A.-126B.-125C.-32D.-36、某C语言程序段如下:for(i=0;i<9;i++){temp=1;for(j=0;j<=i;j++)temp+=a[J];sum+=temp;}下列关于数组a的访问局部性的描述中,正确的是()。

A.时间局部性和空间局部性皆有B.无时间局部性,有空间局部性C.有时间局部性,无空间局部性D.时间局部性和空间局部性皆无7、连续两次启动同一存储器所需的最小时间间隔称为()。

A.存储周期B.存取时间C.存储时间D.访问周期8、CPU中不包括()。

A.操作码译码器B.指令寄存器C.地址译码器D通用寄存器9、CPU中的译码器要用()。

A.地址译码人B.指令译码C.数据译码1D.控制信号译码10、总线宽度与下列()有关。

A.控制线根数B.数据线根数C.地址线根数D.以上都不对11、在()结构中,外部设备可以和主存储器单元统一编址。

模拟乘法器原理乘法器是一种电路设计,用于将两个输入数相乘,并输出它们的乘积。

乘法器常用于数字信号处理、计算机和通信系统中。

乘法器的原理基于布尔代数和逻辑门。

它通常由多个逻辑门和触发器组成,以实现乘法运算。

乘法器的设计要考虑精度和运算速度。

一种常见的乘法器设计是Booth乘法器,它使用偏置编码技术来减少部分乘积的计算。

另一种常见的设计是Wallace树乘法器,它通过级联多个片段乘法器来提高速度。

乘法器的操作原理是分别将两个输入数的每个位进行乘法运算,并将结果相加。

具体步骤如下:1. 将两个输入数分别展开为二进制形式,对应位分别相乘。

最低位乘积直接输入到第一级部分乘积的输入。

2. 对每一位乘积进行部分乘积运算。

部分乘积运算是将当前位乘积和之前的部分乘积相加,并将结果输出到下一级。

3. 重复步骤2,直到所有位的乘积都被计算出来。

4. 对所有部分乘积进行累加,得到最终的乘积结果。

乘法器还需要考虑进位和溢出的问题。

在每一位相乘时,会产生进位位和当前位的乘积。

如果乘积超过了位数的范围,就会产生溢出。

乘法器的性能可以通过速度和面积这两个指标来评估。

速度是指乘法器完成一次乘法运算所需的时间,面积是指乘法器所占据的芯片空间大小。

总结来说,乘法器是一种常见的电路设计,用于将两个输入数相乘。

乘法器的原理基于布尔代数和逻辑门,它的设计考虑了精度和运算速度。

乘法器的操作原理是对输入数的每一位进行乘法运算,并将结果累加得到最终的乘积。

乘法器还需要考虑进位和溢出的问题。

乘法器的性能可以通过速度和面积来评估。

一种基于LPM调用的快速乘法器的设计摘要:乘法器是数字系统中的常见电路模块,本文设计了一种采用EDA技术、基于FPGA 芯片、调用LPM模块实现一种快速乘法器的方案。

调用LPM模块可以化简数字系统的设计,方法是根据系统的功能需求调用适当的LPM模块,根据系统功能对其各项参数进行设置,再配备适当的设计文件即可。

关键词:乘法器;LPM调用;EDA;MIF文件0 引言乘法器是通信系统中的重要模块,常用于卷积、傅里叶变换、滤波、变频等计算过程。

采用FPGA实现乘法器的算法有很多,如移位相加、加法器树乘等算法,而基于FPGA快速RAM资源实现的乘法器,具有更高的速度,在信号处理系统中,具有快速响应的优势。

在EDA设计中,集成开发环境自带丰富的参数可设置模块库(LPM),设计者可根据系统功能的需要,在LPM中调用适当的模块,编写相应的参数,配备相应的设计文件,即可实现设计。

LPM模块通常都是各项指标优化的优秀成熟设计半成品,可以减轻设计者的调试工作,对于较复杂的数字系统LPM调用法可以简化设计过程,提高了设计者的开发效率。

本文讨论了一种基于FPGA芯片通过LPM模块调用实现4位快速乘法器的方法。

1 快速乘法器的LPM的调用方案与实现在集成开发环境maxplus2下,LPM调用有原理图调用和VHDL调用两种方法,本文采用第一种方法。

在maxplus2原理图编辑器下,从参数可设置模块库…\maxplus2\max2lib\mega_lpm\*中调用LPM_ROM模块,设置其输入为两个4位的二进制乘数,将这两个4位二进制数组合为ROM的地址,在相应的地址单元里存放其乘积值。

因此该模块具有两个输入端口,分别为时钟信号CLK、地址输入端INPUT[7..0],乘法结果输出端OUTPUT[7..0]。

在原理图编辑器下双击LPM_ROM右上角的参数显示区域,弹出Edit Ports/Parameters 设置对话框,设置LPM_ROM模块相应的参数。

基于MPI的卷积计算并行实现鲁金;马可;高剑【摘要】针对传统的卷积并行计算模型中,存在着大量的消息传递,负载不均衡等问题;提出一种新的基于MPI同步模型的并行卷积算法;该模型采用消息传递的方式进行进程间的通信,同时有效平衡负载,避免大量的消息传递;通过分析该模型的加速比和效率,实验结果表明,此方法显著提高了并行效率和长序列的运算速度,充分发挥了节点间分布式存储和多核并行处理的优势,是一种有效可行的并行策略.【期刊名称】《计算机测量与控制》【年(卷),期】2016(024)001【总页数】3页(P292-294)【关键词】卷积计算;并行;消息传递接口;负载平衡【作者】鲁金;马可;高剑【作者单位】西安电子工程研究所,西安710100;西安电子工程研究所,西安710100;西安电子工程研究所,西安710100【正文语种】中文【中图分类】TP311近年来,受到程工艺的限制,单核处理器的性能已接近极限,通过提高单处理器的时钟频率来提高计算机性能的方法越来越难以达到良好的效果。

因此,多核技术成为CPU制造商显著提高处理器的性能的共同解决方案[1-2]。

多核设备为应用程序提供了并行计算的硬件平台,使计算机的计算速度得到了巨大提高。

而另一方面,在数字信号处理领域中,要处理的数据量越来越庞大,实时性的要求也越来越高,,将并行处理的思想运用在信号处理中,构建一个具有并行性的系统,必将是一个未来发展的趋势。

卷积计算作为信号与系统时域分析的一种重要方法。

在科学计算领域中起着重要的作用[3],广泛应用于通信,航空航天,生物医学工程,雷达信号处理等工程领域。

因此,将并行化的思想应用在卷积计算中,从而大大加快卷积计算的速度,提高卷积计算的效率,具有重要的研究意义。

并行计算是指在并行系统上,将一个大的任务分解为多个小的子任务,分配给不同计算单元上,各个计算单元之间相互协同,并行地执行各个子任务,最后汇合同步,从而达到加速求解任务的目的。

1简述机构的特征,画出二例常见机构示意图机构是机器的重要组成部分,其主要功能是实现运动和动力的传递和变换。

因此,机构也具有机器的前两个特性,即∙是一种通过加工制造而成的机件组合体。

∙机器中各个机件之间都具有确定的相对运动。

4-74是曲柄滑块机构这一个里面随便挑一个就行,下面有名称的2是说明黄金分割法在优化计算机中的应用原理黄金分割法是用于一元函数f(x)在确定的初始区间[a,b]内搜索极小点a*的一种方法。

它是优化计算中的经典算法,以算法简单、效果明显而著称,是许多优化算法的基础。

但它只适用于一维区间上的凸函数。

其基本思想是:依照“去坏留好”原则、对称原则、以及等比收缩原则来逐步缩小搜索范围。

具体地说,就是在区间[a,b]中取点,,如果令;如果令,重新开始。

这样每次可将搜索区间缩小倍或倍,直至缩为一点。

黄金分割法原理如图1所示,其中K=0.618,区间长度为L。

该算法为收敛速度很快的一维搜索方法。

3简述有限元法在机械工程的应用原理将连续的求解域离散为一组单元的组合体,用在每个单元内假设的近似函数来分片的表示求解域上待求的未知场函数,近似函数通常由未知场函数及其导数在单元各节点的数值插值函数来表达。

从而使一个连续的无限自由度问题变成离散的有限自由度问题。

应用平面问题:空间问题和壳版问题静力平衡:动力响应和结构稳定国体力学:流体力学,传热学,电磁学等弹性材料:弹塑性,塑性,粘弹性,粘塑性和复合材料等三维问题1应力与平衡方程2应变与几何方程3物理问题4边界问题二维问题平面应力与应变问题都是我自己在网上找的,不知道和你们学的一样不,仅供参考哈!。

2022年河南农业大学计算机应用技术专业《计算机系统结构》科目期末试卷A(有答案)一、选择题1、浮点数尾数基值rm=8,尾数数值部分长6位,可表示的规格化最小正尾数为( )A.0.5B.0.25C.0.125D.1/642、除了分布处理、MPP和机群系统外,并行处理计算机按其基本结构特征可分为流水线计算机,阵列处理机,多处理机和()四种不同的结构。

A.计算机网络B.控制流计算机C.机群系统D.数据流计算机3、推出系列机的新机器,不能更改的是( )A.原有指令的寻址方式和操作码B.系统总线的组成C.数据通路宽度D.存贮芯片的集成度4、若输入流水线的指令既无局部性相关,也不存在全局性相关,则()。

A.可获得高的吞吐率和效率B.流水线的效率和吞吐率恶化C.出现瓶颈D.可靠性提高5、全相联地址映象是指()。

A.任何虚页都可装入主存中任何实页的位置B.一个虚页只装进固定的主存实页位置C.组之间是固定的,而组内任何虚页可以装入任何实页位置D.组间可任意装入,组内是固定装入6、指令间“一次重叠”说法有错的是( )A.仅“执行k”与“分析k+1”重叠B."分析k”完成后立即开始“执行k”C.应尽量使“分析k+1”与“执行k”时间相等D.只需要一套指令分析部件和执行部件7、IBM360/91属于()A.向量流水机B.标量流水机C.阵列流水机D.并行流水机8、计算机组成设计不考虑( )。

A.专用部件设置B.功能部件的集成度C.控制机构的组成D.缓冲技术9、IBM360/91对指令中断的处理方法是()A.不精确断点法B.精确断点法C.指令复执法D.对流水线重新调度10、下列说法中不正确的是( )A.软件设计费用比软件重复生产费用高B.硬件功能只需实现一次,而软件功能可能要多次重复实现C.硬件的生产费用比软件的生产费用高D.硬件的设计费用比软件的设计费用低二、判断题11、能做为评价其它置换算法标准的置换算法是RAND。

计算机工程与应用!""#$%!图%&’(()*+,-./’并行域乘结构图!!!!!!!!!!!!值%"0+%1!%1!+%0"%0"+!%"!%"+0""相同安全强度234密钥长度#%!+506506+%"!7%"!7+!"76!"76+!%"""!型正规基!!0!1"型正规基1#%"07%引言%86#年!9:;<=>%@和&<AA)/?!B 分别提出了椭圆曲线密码体制"这种新型的公钥密码体制因其每比特最大的安全性!受到人们的青睐"该密码体制特别适合于计算能力#集成电路空间和带宽受限的环境"椭圆曲线的实现很快也成为一个热门的研究方向!椭圆曲线密码体制的硬件实现受到越来越多的关注""#$!!%域的椭圆曲线成为硬件实现的主要类型"有限域上乘法运算的速度直接影响到椭圆曲线密码体制的执行效率"为了提高运行速度!通常选取存在优化正规基的域上的椭圆曲线"优化正规基的类型值越小!其上的有限域乘法运算复杂度越低"在标准C%101上公布的表格中!可以发现DD 型优化正规基的资源比D 型优化正规基的资源丰富"因此!设计基于DD 型优化正规基的乘法器显得更加重要些"表%"#!!!"域上的优化正规基的个数该文提出的有反馈结构的乘法器结构!比&’(()*+,-./’1B乘法器和文献0B 中的方法所使用的门资源有了很大的减少&&’(()*+,-./’乘法器需要!$!!+!%个异或门!文献?0B 中的乘法器需要%$#$!!+!%个异或门!而该设计仅需要6$!+%%个异或门和6!+5个与门!大大地节约了组合逻辑资源"这种乘法器结构用在椭圆曲线密码体制中!使其更适合于资源受限的环境!比如智能卡#无线通信等环境"!研究背景用正规基表示的域元的乘法运算是代价比较大的一种运算!但所幸的是&采用"型优化正规基的方法表示的域元!乘法运算同样也可以是比较简单#有效的"设$!%!&!"#$!!%!&是两个域元的乘积!#E $##!#!’#!%是基底"适合资源受限环境的!"!!#"域上乘法器结构谭丽娟陈运!电子科技大学通信与信息工程学院"成都0%""#7#F+-’<A &=AG.’HI(=J$.)(=K$)J.$KH摘要椭圆曲线密码体制因其每比特最大的安全性受到越来越广泛的重视$而有限域上的乘法运算"成为决定椭圆曲线上的标量乘法运算速度的主要因素$文中基于&’(()*+,-./’乘法器"和另外一种并行乘法器"提出了一种新型的有反馈的并行乘法器结构"结构需要6!!+%%个异或门和!6!+5%个与门$比起原来的乘法器"门数有了很大的减少$因此这种结构比较适合资源受限的环境中应用$关键词正规基椭圆曲线有限域标量乘文章编号%""!+611%+!!""#%%!+""58+"1文献标识码4中图分类号LC1"8$5"#$%&’&()*+,-./,.&0#+.-12,&)(03&4(+0$&5(64-01.6-4"//,.$1-.(6.6!"$!#%7168.9+165%&6:+6$FA)K=/:H<K L)KMH:A:N*OH<P)/(<=*!QM)HNJ.0%""#7%"24-01$-&LM))AA<R=<K K./P)K/*R=:(*(=)-<(S<J)A*K:HK)/H)J J.)=:=M)()K./)(=R)/;<=$LM)-.A=<RA<K’=<:H <H T<H<=)T<)AJ J:-<H’=)(=M)(R))J :T (K’A’/-.A=<RA<K’=<:H :H =M))AA<R=<K K./P)$U’()J :H &’(()*+,-./’-.A=<RA<K’=<:H ’HJ ’R’/’AA)A -.A=<RA<K’=<:H (=/.K=./)!’H)S (KM)-)S<=M T))J;’KV (=/.K=./)<(R.=T:/S’/J <H =M<(R’R)/$Q:-R’/)J =:R/)P<:.((KM)-)(!;.AV :T N’=)(’/)N/)’=A*/)J.K)J <H =M)H)S (KM)-)$W)HK)!<=<(X.<=)(.<=’;A)T://)(:./K)K:H(=/’<H=(’RRA<K’Y =<:H((.KM ’(CZ4’HJ (-’/=K’/J()=K$;&<=(0>4&H:/-’A ;’(<(!)AA<R=<K K./P)!T<H<=)T<)AJ !(K’A’/-.A=<RA<K’=<:H作者简介#谭丽娟!研究生!密码学专业"陈运!副教授!主要研究方向&密码学与信息安全"!"!""#$%!计算机工程与应用乘积子项!%!!!&具体系数"%#!’"!#%""$#$’"!#&’"&#!’!’"$(%#$’"$#$)%项数!$)!"%表!*基表示下域元乘法运算各乘积子项对应的!%的系数!!!!"+""""%!"$)%#+""","%"!’!’"$)%"!+"""%##+"#"#%!#$)%#+#""’#%"!’!’#$)%"!+#""!#%&"""#"#’&""""’##’&"(#’"&#’表示向量的转置$为了提高硬件运行速度%-.//01)23456.提出了一种并行的处理方法%提高整个乘法运算的速度$这种结构需要!"$)%#个%位的移位寄存器和$个)函数处理器$其中)函数处理器是"%#的函数%可以表示为&*+&)"""%"%%!%"$)%%#"%#%%!%#$)%#"7#移位寄存器在硬件上很好实现%所以关键是)函数处理器的设计$但是%通常情况下)函数是很复杂的$针对#型优化正规基%现在有好几种改进算法87%#9%但是对于$型优化正规基的改进算法的文献却很少$对于::型优化正规基%文献8;9中给出了一种乘法器结构$将正规基的基底(转换成一种适合乘法运算的基底,$(+<!%!!%!!%!%!!=%!&%-.%/-"##,+<!%%!!%!&%!%!$=%!&%-.%0+";#12"!$#中的域元3可用基底(和基底,分别表示成&3&"%>!’"!>!!’"&>!!’!’"$>!!%!&%.%0%"?#3&"%!%’"!!!’"&!&’!’"$!$%!+&%+.%0+"@#两个表达式之间的系数确定是此次转换的关键%文献8;9中已证明%两个基的元素!和!+是等价的$因此%系数"+>和"-实际上也是对应的%两者满足置换关系$"-+"+>%-+4%4!8%%$9"!$’%#)4%4!8$’%%!$"9%4+!+"4AB "!$,%##"C #,基下的3&$+&%#"+"%+.%0+#%5&$-&%$#-"%-.%0-#乘法运算的操作如图!所示$表!列举了各个乘积项的!%系数%并且统计了各个乘积项含有的系数个数%其中系数的项数决定了硬件实现所需异或门的个数%总计!$)!,%+!$)%个异或门$,基表示下域元乘法运算&!&35&$+&%$"+"%+.%0+#$-&%$#-"%-.%0-#&$"%+%-%$%+&-"+#-"%+0-.%0"+0-##."$+&%$$0+-&%$"+#-"%+.-.%0"+0-##.$+&%$$-&$0+.%"+#-"%8"!$.%#0"+.-#9.%)8"!$.%#0"+.-#9#&!%.!!.!&&改进的乘法器结构该文并没有直接使用文献8;9中的方法&分别计算每位的乘法结果$这样虽然能使构造乘法器的异或门数量减少到%$#"$!)$#个%但每位乘法结构各不相同%硬件实现上不利于模块化的设计$因此%文章结合-.//01)2456.的并行结构%构造了如图!的乘法器结构$图中!函数处理器是针对图%中的)函数处理器进行的改进$改进后的!函数处理器执行表达式"%"#的操作$操作涉及到!$)!个异或操作%和!$)%个与操作&"%#!,"!#%,"!#&,"&#!,!,"$0%#$,"$#$0%,"$#$"%"#相对图%的另一个改进就是%在进行运算之前和数据输出之前%进行式"C #的变换%该变换的正向和反向变换是可逆的%只是将变换的输入输出进行对换$但是这种方法并不是最优的$按照计算机表示的习惯%脚码统一从"开始标记$则!"的系数可以记作&""#%,""%#","%#!#,!,""$0!#$0&,"$0!#$0%#,"$0%#$0!,"$0%#$0%"%%#计算!%的时候%需要将输入的数据分别循环左移一位$输入的数据分别变成&""$0!"$0&!"%"""$0%#和"#$0!#$0&!#%#"#$0%#%将两个输入代入到公式"%%#中&"""#%,""#$0%#,""%#","%#!#,!,""$0!#$0&,"$0!#$0%#,"$0%#""%!#图&线框中的部分是两个系数中相同的部分%用6表示$则!"和!%的系数分别用!"和!%表示&图!改进的并行乘法器结构图!"图&!"和!%的系数结构图’有反馈的并行有限域乘法器结构!上接(’页"询)*+$电子学报#!"""$!,!,"%!"-!’,$常继传#郭立峰#马黎$可复用软件构件的表示和检索)*+$计算机科学# %...%’#-’..$徐如志#钱乐秋#程建平等$基于/01的软件构件查询匹配算法研究)*+$软件学报#!""&$%’!2"%"$王渊峰#张涌#任洪敏等$基于刻面描述的构件检索)*+$软件学报# !""!$%&!,"%%$王渊峰#薛云皎#张涌等$刻面分类构件的匹配模型)*+$软件学报# !""&$%’!&"!!!!!"3!"#$%!&$%%4#$%%&$%!4#$%%&$%%!%&"!%3!"#$%!&$%!4#$%%&"4#"&$%%!%’"为了利用并行结构#系数计算全部采用位移之后的输入来进行&设循环左移%位的输入分别为!#’$%%#’$%!’#’%#’""和!&’$%%&’$%!(&’%&’""#则容易发现移位操作之后的数据与原数据存在这样的式!%#"的关系&这样表示使得结论更加具有广泛性&#(53#(%%#(!)%#$%!+#$%%#()""#&(53&(%%#(!)%#$%!+&$%%#()""!%#"由于式!%&"和!%’"的运算都是模!加#因此#两式相加#再利用式!%#"便可得到式!%("&以上的改进实际是在处理的时候增加了一个反馈的级联电路&在图!的的基础上进一步改进#可以得到图’的结构&*%3*"4!#$%!&$%!4#$%%&"4#"&$%%"4!#$%!&$%%4#$%%&$%!4#$%%&$%%"3*"4!#’$%%&’$%%4#’$%%&’""4#’%&’""!#’"&’%4#’%&’$6%4#’"&’""!%("对比图!中的结构%图!中包含了$个+函数处理器#而图’中只有一个+函数处理器#和$6%个,函数处理器#其中,函数处理器执行公式!%2"的操作&-(6%和-(分别作为,函数处理器的输入和输出&-(6%表示来自上一个+或,函数处理器的反馈输出&公式中涉及了(个与操作和(个或操作&-()-(6%"!#’$%%&’$%%4#’$%%&’""4#’%&’"" !#’"&’%4#’%&’$6%4#’"&’""#(!)%#$%%+!%2"总体上#两种乘法器结构涉及的与和异或操作的次数如表&所示#有反馈的结构比起改进的并行乘法器结构#无论是与还是异或操作#都有了很大的减少&这对算法的执行效率和面积开销将有很大的影响&实现的结果比较将在第’节给出&’结论使用789:;<的开发工具=><;9>?@@!$!进行综合#选用789:;<的7AB/@@系列中的BA!"7芯片#在%""0CD的时钟约束的条件下#图&)图’中两个乘法器结构综合结果如表’所示*表’中的数据表明了有反馈的并行乘法器的面积开销几乎是改进并行乘法器的一半#但是时间却是其两倍多!每个厂商的器件的逻辑单元数的计算各不相同#逻辑单元数并不是与逻辑门数完全对应的#因此#表’中列出的综合结果的差距是同表&中的门数差别并不是完全一样的"*改进并行乘法器用的是一种是以时间换空间的思想*在资源受限的环境下!如智能卡的使用中"#有反馈的并行乘法器具有更大的优势*文中提出的乘法器结构#有效地减少了组合逻辑的开销#很适合于EAF7应用*实际上#在椭圆曲线密码体制的实现中收到了很好的效果*!收稿日期%!""’年2月"参考文献%$G H0I88:;$J?:KL B88IM9IN O>;P:?IQ O;RM9KS;<MTR)O+$@Q%7UP<QN:?IQO;RM9K8KSR O;RM9KV,##1:N9>;:WK9:?IQ OKXM>9:;HNI:QN:WK!%,#HM;IQS6G:;8<S Y:;8IQ#%.,#%’%2-’!(!$W ZK[8I9D$B88IM9IN O>;P:O;RM9K?R?9:X?)*+$0<9T OKXM#%.,2$’,%!"&-!".&$@BBB H9<QU<;U HM:NILIN<9IKQ?LK;A>[8IN6Z:R O;RM9KS;<MTR)H+$@BBBA%&(&#!"""’$*\X>;<#*0<??:R$OKXM>9<9IKQ<80:9TKU<QU7MM<;<9>?LK;EIQI9:EI8:8U7;I9TX:9IN)A+$JH A<9:Q9#W>X[:;’#%.,($!’"%#,2-(!2#$07C<Q?<Q#0]^<QS#G Z YT<;S<P<$7XKUILI:U0<??:R6\X>;<M<;<88:8X>89IM8I:;LK;<N8<??KL LIQI9:LI:8U?)*+$@BBB_;<Q?<N9IKQ?KQOKXM>9:;?#%..&$’!!%""%%!2,-%!,"($Y H>Q<;#O Z ZKN$7Q:LLINI:Q9KM9IX<8QK;X<8[<?I?9RM:@@X>89I6M8I:;)*+$@BBB_;<Q?<N9IKQ?KQ OKXM>9:;?#!""%$#"!%"%,&-,2!!!!!!!!!!!!!!!!!!!!!!与操作异或操作有反馈的并行乘法器,$62,!$6%"改进的并行乘法器$!!$6%"!$!!$6%"有反馈结构减少的操作!$!%.$"2!$!%%"$",表&图!和图’中两种有限域乘法结构的比较!!!!!!!!!!!改进并行乘法器有反馈的并行乘法器@‘\引脚数#2##2#逻辑单元数!".,%!!%周期!./"!&$2"(’$#!表’有限域运算模块的综合结果!"计算机工程与应用!""#$%!适合资源受限环境的GF(2m)域上乘法器结构作者:谭丽娟, 陈运, Tan Lijuan, Chen Yun作者单位:电子科技大学通信与信息工程学院,成都,610054刊名:计算机工程与应用英文刊名:COMPUTER ENGINEERING AND APPLICATIONS年,卷(期):2005,41(12)被引用次数:0次1.V S Miller Use of Elliptic Curves in Cryptography 19852.N Koblitz Elliptic Curve Cryptosystems 19873.IEEE Standard Specifications for Public-Key Cryptography 20004.J Omura.J Massey Computational Method and Apparatus for Finite Fileld Arithmetic 19865.M A Hansan.M Z Wang.V K Bhargava A modified Massey-Omura parallel multiplier for a class of finite fields 1993(10)6.B Sunar.C K Koc An efficient optimal normal basis type Ⅱ multiplier 2001(01)1.期刊论文朱璇.陈韬.郁滨.ZHU Xuan.CHENG Tao.YU Bin Fn2上基于ONB的椭圆曲线乘法器的设计与实现-微电子学与计算机2005,22(7)文章在介绍有限域运算法则,域上椭圆曲线及点的运算法则的基础上,设计了一个F191 2上基于优化正规基的串行椭圆曲线乘法器,其点乘运算速度可达80.87次/秒,为进一步完成椭圆曲线加密系统提供了硬件基础.2.学位论文李宁基于正规基的椭圆曲线密码算法的研究和IP核实现2010在计算机和网络技术高速发展的今天,公钥密码技术得到了广泛的应用,也是构建安全应用所不可或缺的关键密码技术,然而随着计算能力的提高,RSA、离散对数等密码体制的安全强度不断受到挑战,目前认为安全的模长建议在1024比特以上。

专利名称:一种高精度高带宽的模拟乘法器电路专利类型:实用新型专利

发明人:徐凯英,章宇新,孔祥艺,黄立朝

申请号:CN202121647993.3

申请日:20210720

公开号:CN215642669U

公开日:

20220125

专利内容由知识产权出版社提供

摘要:本实用新型公开一种高精度高带宽的模拟乘法器电路,属于集成电路信号处理领域,包括带隙基准源、乘法算子模块、运算放大器和修调电阻阵列。

带隙基准源产生若干路高精度的基准电压给其他模块;乘法算子模块包括若干个乘法器,实现乘法运算的逻辑功能;运算放大器实现宽电压范围的信号输入;修调电阻阵列用于对乘法器进行误差的修正,实现高精度输出。

本实用新型能够同时完成四通道高精度的信号处理运算,可正负双电源供电,工作电压范围更宽,大电流环境下的工作能力更强。

申请人:中国电子科技集团公司第五十八研究所

地址:214000 江苏省无锡市滨湖区惠河路5号

国籍:CN

代理机构:无锡派尔特知识产权代理事务所(普通合伙)

代理人:杨立秋

更多信息请下载全文后查看。

适合资源受限环境的GF(2m)域上乘法器结构

谭丽娟;陈运

【期刊名称】《计算机工程与应用》

【年(卷),期】2005(041)012

【摘要】椭圆曲线密码体制因其每比特最大的安全性受到越来越广泛的重视.而有限域上的乘法运算,成为决定椭圆曲线上的标量乘法运算速度的主要因素.文中基于Massey-Omura乘法器,和另外一种并行乘法器,提出了一种新型的有反馈的并行乘法器结构,结构需要8(m-1)个异或门和(8m-7)个与门.比起原来的乘法器,门数有了很大的减少.因此这种结构比较适合资源受限的环境中应用.

【总页数】3页(P79-81)

【作者】谭丽娟;陈运

【作者单位】电子科技大学通信与信息工程学院,成都,610054;电子科技大学通信与信息工程学院,成都,610054

【正文语种】中文

【中图分类】TP309.7

【相关文献】

1.基于FPGA技术的GF(2m)域乘法器的研究和设计 [J], 靳济方;高献伟;欧海文;赵耿

2.GF(2m)域上Ⅱ型最优正规基的字级乘法器 [J], 倪乐;陈韬;戴紫彬;李淼

3.有限域GF(2m)上乘法器的实现 [J], 韩晓娱;王寿武

4.GF(2m)域上通用可配置乘法器的设计与实现 [J], 卫学陶;戴紫彬;陈韬

5.GF(2m)域乘法器的快速设计及FPGA实现 [J], 高献伟;靳济方;方勇;李为民因版权原因,仅展示原文概要,查看原文内容请购买。

2022年湖南文理学院计算机科学与技术专业《计算机系统结构》科目期末试卷B(有答案)一、选择题1、浮点数尾数下溢处理时,最大误差最大,但下溢处理不需要时间,平均误差又趋于0的方法是( )。

A.截断法B.舍入法C.ROM查表法D.恒置"1"法2、设16个处理器编号分别为0,1,2,...,15用Cube,互联函数时,第10号处理机与第()号处理机相联。

A.11B.8C.14D.23、“启动I/O”指令是主要的输入输出指令,是属于()。

A.目态指令B.管态指令C.目态、管态都能用的指令D.编译程序只能用的指令4、外部设备打印机适合于连接到( )。

A.数组多路通道B.字节多路通道C.选择通道D.任意一种通道5、计算机系统结构不包括( )。

A.主存速度B.机器工作状态C.信息保护D.数据6、在尾数下溢处理方法中,平均误差最大的是()A.截断法B.舍入法C.恒置"1"法D.ROM查表法7、微指令由()直接执行。

A.微指令程序B.硬件C.汇编程序D.编译程序8、1TFLOPS计算机能力,1TBYTE/S的I/O带宽和()称为计算机系统的3T性能目标。

A,1TBYTE 硬盘容量B.1TBYTE 软盘容量C.1TBYTE 主存容量D.A和B9、传统机器语言机器级,是用()来()机器指令。

A.硬件,翻译B.编译程序,翻译C.微指令程序,解释D.微指令程序,翻译10、在计算机系统设计中,比较好的方法是()。

A.从上向下设计B.从下向上设计C.从两头向中间设计D.从中间开始向上、向下设计11、除了分布处理、MPP和机群系统外,并行处理计算机按其基本结构特征可分为流水线计算机,阵列处理机,多处理机和()四种不同的结构。

A.计算机网络B.控制流计算机C.机群系统D.数据流计算机12、输入输出系统硬件的功能对()是透明的。

A.操作系统程序员B.应用程序员C.系统结构设计人员D.机器语言程序设计员13、虚拟存储器常用的地址映象方式是( )A.全相联B.段相联C.组相联D.直接14、下列说法正确的是( )A.Cache容量一般不大,命中率不会很高B.Cache芯片速度一般比CPU的速度慢数十倍C.Cache本身速度很快。

计算机原理_国防科技大学中国大学mooc课后章节答案期末考试题库2023年1.在CPU的组成中,不包括()答案:存储器2.计算机CPU主频的倒数指的是()答案:时钟周期3.以下是一段MIPS指令序列:addR1,R0,R1lwR0,0(R1)bneR0,R5,exitaddR3,R5,R4exit:以上指令序列中,()指令之间存在数据冒险。

答案:1和2_2和34.下列给出的指令系统特点中,有利于实现指令流水线的是()答案:指令格式规整且长度一致_指令和数据安边界对齐存放_只有Load/Store 指令才能对操作数进行存储访问5.在定点机中执行算术运算时会产生溢出,其根本原因是()答案:运算结果无法显示6.某计算机的指令流水线由4个功能段组成,指令流经各个功能段的时间分别是100ns,80ns,70ns和60ns,则该计算机的CPU时钟周期至少是()。

答案:100ns7.设CPU地址总线有24根,数据总线有32根,用512K x 8位的RAM芯片构成该机的主存储器,则该机主存最多需要()片这样的存储芯片。

答案:1288.某计算机的主存地址空间大小为256MB,按字节编址,指令Cache和数据Cache分离,均有8个Cache行,每个Cache行大小为64B,数据Cache 采用直接映射方式,现有程序A伪代码如下所示:inta[256][256];intsum_array(){inti,j,sum=0;for(i=0;i<256;i++){for(j=0;j<256;j++){sum+=a[i][j];}}returnsum;}假定int类型数据用32位补码表示,程序编译时i、j、sum均分配在寄存器中,数组a按行优先方式存放,其首地址为320(十进制)。

则数组元素a[1][1]所在的主存块对应的Cache行号是()(Cache行号从0开始)答案:59.下列部件中不属于控制部件的是()答案:状态条件寄存器10.某DRAM芯片内部的存储单元为256x256结构。

计算机组成与系统结构习题答案,上海交大陈泽宇着C1:以下哪些设备不属于冯?诺伊曼体系结构计算机的五大部件?寄存器,缓冲器适配器的作用是保证_____用计算机系统特性所要求的形式发送或接收信息。

正确答案是:I/O设备1966年,Flynn从计算机体系结构的并行性能出发,按照_____的不同组织方式,把计算机系统的结构分为SISD、SIMD、MISD和MIMD四类。

指令流,数据流具有相同_____的计算机,可以采用不同的_____。

:计算机体系结构,计算机组成冯?诺伊曼型计算机的设计思想是_____。

正确答案是:存储程序并按地址顺序执行1958C2:_____在定点在PCASCII32_____C3:CacheCacheCacheMOS SRAM,快EPROM相联存储器是以______来访问存储器的。

关键字,内容从CPU来看,增加Cache的目的,就是在性能上使______的平均读出时间尽可能接近Cache的读出时间。

主存,内存虚拟地址由______生成。

编译程序MOS半导体存储器中,______可大幅度提高集成度,但由于______操作,外围电路复杂,速度慢。

DRAM,刷新虚拟存储器可看作是一个容量非常大的______存储器,有了它,用户无需考虑所编程序在______中是否放得下或放在什么位置等问题。

逻辑,主存C4:存储器堆栈是由程序员设置出来作为堆栈使用的一部分______。

主存储器指令的顺序寻址方式,是指下一条指令的地址由______给出。

程序计数器指令格式中的______字段,用来表征指令的操作特性与功能操作码堆栈寻址方式中,设A为累加器,SP为堆栈指示器,MSP为SP指示的栈顶单元。

如果进栈操作的动作顺序是(A)→MSP,(SP)-1→SP,那么出栈操作的动作顺序应为______。

(SP)+1→SP,(MSP)→A指令格式就是______用二进制代码表示的结构形式。

指令字指令的跳跃寻址方式,是指下一条指令的地址由本条指令直接给出,因此,______的内容必须相应改变,以便及时跟踪新的指令地址。

数字信号处理_华侨大学中国大学mooc课后章节答案期末考试题库2023年1.FFT算法结构中的原位计算,可以节省大量的内存空间。

参考答案:正确2.假设【图片】,则根据DTFT的性质,【图片】参考答案:错误3.有限脉冲响应滤波器有三个主要特点:系统肯定是,容易得到因果系统,能获得线性相位的性能。

参考答案:稳定4.欧拉公式是恒等式,它说明虚指数是由实部余弦波和组成的。

参考答案:虚部正弦波5.如果把数字信号处理系统视为五部分组成,则这五部分分辨是:低通预滤,模数转换,数字信号处理,和低通滤波。

参考答案:数模6.以下关于滤波器设计的说法哪个是正确的。

参考答案:具有第二类线性相位特征的FIR滤波器不适合用来做低通滤波器。

7.在检测心脏信号时,必须滤除环境的交流电源干扰,实现这种功能的滤波器叫做。

参考答案:带阻滤波器8.FFT是以下哪个变换的快速算法?参考答案:离散傅里叶变换9.设计有限脉冲响应数字滤波器有两种基本方法,它们是和频率采样法。

参考答案:窗函数设计法10.数字滤波器一般分为无限脉冲响应滤波器和有限脉冲响应滤波器,无限脉冲响应滤波器的输出是。

参考答案:有反馈的11.模数转换前的低通滤波器是为了。

参考答案:防止混叠失真12.对N=128的序列进行FFT,共进行几级蝶形运算/分解?参考答案:7, 七13.对模拟信号进行采样前需要先做“预滤”,这是一个什么类型的滤波器?参考答案:低通14.x(n)和y(n)分别表示系统的输入和输出,说明y(n)=x(n)+b 差分方程所描述系统的线性性和时变性。

参考答案:非线性,时不变##%_YZPRLFH_%##非线性,非时变##%_YZPRLFH_%##非线性,移不变15.有两个序列x1(n)和x2(n)长度分别是N1和N2,在做线性卷积后结果长度是参考答案:N1+N2-116.令x(n)的z变换是X(z), y(n)的z变换是Y(z),写出x(n)*y(n)的z变换:参考答案:X(z)Y(z)17.序列经过傅里叶变换,其频谱呈现周期性。

2022年职业考证-通信工程师-初级通信工程师考试全真模拟全知识点汇编押题第五期(含答案)一.综合题(共15题)1.单选题1945年,计算机程序存储原理的提出者是()。

问题1选项A.图灵B.冯•诺依曼C.布尔D.摩尔【答案】B【解析】1854年,英国数学家布尔(George Boole,1824-1898年)提出了符号逻辑的思想,数十年后形成了计算科学软件的理论基础。

1936年,英国数学家图灵(Alan Turing,1912-1954年)提出了著名的“图灵机”模型,探讨了现代计算机的基本概念,从理论上证明了研制通用数字计算机的可行性。

1945年,数学家冯•诺依曼(John von Neumann,1903- -1958 年)提出了在数字计算机内部的存储器中存放程序的概念。

这是所有现代计算机的范式,被称为“冯•诺依曼结构”。

按这一结构制造的计算机称为存储程序计算机,又称为通用计算机。

虽然现在的计算机系统从性能指标、运算速度、工作方式、应用领域和价格等方面与当时的计算机有很大差别,但基本结构没有变,都属于冯•诺依曼结构。

故本题选B2.单选题SDN的最大特点就是可以对网络()。

问题1选项A.监控管理B.进行编程C.提供云服务D.进行大数据分析【答案】B【解析】软件定义网络技术实现了控制功能和转发功能的分离,通过灵活的软件编程能力,使得网络的自动化管理和控制能力得到大幅度的提升。

SDN技术的最大特点是可以对网络进行编程。

ONF定义的SDN架构体系分为3个平面,自下而上分别是:数据平面(基础设施层)、控制平面(控制层)和应用平面(应用层)组成。

其中,SDN控制器是控制平面的核心组件,担任着控制网络流量的重要任务。

故本题选B3.单选题高清晰度数字电视(HDTV)通常采用大屏幕和()的宽高比显示方式。

问题1选项A.3∶4B.4∶3C.16∶9D.9∶16【答案】C【解析】数字高清晰度电视(HDTV)是指电视节目的制作、传输和接收等各个环节都是以数字方式进行的电视系统,所以它是全数字化的电视,清晰度可以达到传统电视的一倍以上。

一种高速模(2n-2p-1)乘法器的设计

张清宇;李磊

【期刊名称】《电子技术应用》

【年(卷),期】2016(42)11

【摘要】结合余数系统以及模乘法器本身的特点,一种高速的模(2n-2p-1)乘法器被提出.得益于剩余范围的扩展和新型的部分积压缩树的采用,该设计相较于传统的模乘法器在关键路径上减少了一个长度为2n的加法器且避免了此类Booth编码模乘法器中复杂的负数修正问题.在90 nm工艺下的综合结果表明,该模乘(2n-2p-1)乘法器相较当前的模(2n-2p-1)乘法器有10.4%到49%的延迟性能提升.

【总页数】4页(P137-140)

【作者】张清宇;李磊

【作者单位】电子科技大学电子科学技术研究院,四川成都611731;电子科技大学电子科学技术研究院,四川成都611731

【正文语种】中文

【中图分类】TN402

【相关文献】

1.一种快速大数乘法器的设计方法——大数乘法的高速实现 [J], 丁顺全;杨永福

2.一种高速近似乘法器设计 [J], 吴德祥; 班恬

3.高速Booth编码模(2^n—1)乘法器的设计 [J], 李磊;胡剑浩;敖思远

4.一种高效模(2n-2p)乘法器的设计 [J], 周璐;李磊

5.一种新型高速低功耗可重构流水线乘法器设计 [J], 姚英;田心宇;韩晓聪

因版权原因,仅展示原文概要,查看原文内容请购买。