基于VHDL 4位电子密码锁的设计

- 格式:docx

- 大小:284.20 KB

- 文档页数:15

1 引言电子密码锁的使用体现了人们消费水平、保安意识和科技水平的提高,而且避免了携带甚至丢失钥匙的麻烦。

目前设计密码锁的方法很多,例如用传统的PCB 板设计、用PLC 设计或者用单片机设计。

而用V HDL 可以更加快速、灵活地设计出符合各种要求的密码锁,优于其他设计方法,使设计过程达到高度自动化。

本设计在Max + plus Ⅱ的环境中进行,用Al2tera 公司ACEX 1 K系列的EP1 K30 TC14423 来实现。

ACEX 1 K是Altera 公司着眼于通信、音频处理及类似场合的应用而推出的FPGA 器件芯片系列,其典型门数为10 万门,是当今Altera 多种产品中应用前景最好的器件系列之一。

EDA 技术设计电子系统具有用软件的方式设计硬件;设计过程中可用有关软件进行各种仿真,系统可现场编程、在线升级,整个系统可集成在一个芯片上等特点;不但设计周期短、设计成本低,而且将提高产品或设备的性能,缩小产品体积、提高产品的技术含量,提高产品的附加值。

用VHDL设计电子密码锁方案:作为通用电子密码锁,主要由3 个部分组成:数字密码输入电路、密码锁控制电路和密码锁显示电路,作为电子密码锁的输入电路。

可供选择的方案有数字机械式键盘和触摸式数字键盘等多种。

(1)密码锁输入电路包括时序产生电路、键盘扫描电路、键盘弹跳消除电路、键盘译码电路等几个小的功能电路。

(2)密码锁控制电路包括按键数据的缓冲存储电路,密码的清除、变更、存储、激活电锁电路(寄存器清除信号发生电路),密码核对(数值比较电路),解锁电路(开/关门锁电路)等几个小的功能电路。

(3)七段数码管显示电路主要将待显示数据的BCD码转换成数码器的七段显示驱动编码。

1.1 课题背景随着社会的发展和人们生活水平的提高,人们的安全意识也逐步加强。

传统的机械锁由于其构造的简单,失效的事件屡见不鲜,如何实现保密防盗这一问题变的尤其的突出,密码锁以其安全性高、成本低、功耗低、易操作等优点受到越来越多人的欢迎。

电子与信息工程学院EDA课程设计报告(2011 —2012 学年第一学期)课程名称:EDA课程设计与实现班级:电子0903学号:姓名:指导教师:陈智萍2011年09月一、目的1.掌握VHDL语言的使用,学会用VHDL语言来编程解决实际问题;2.学会使用EDA开发软件设计小型综合电路,掌握仿真的技巧;3.学会应用开发系统实现硬件电路,检验电路的功能。

二、内容和要求用VHDL语言设计一个密码锁,用波形仿真验证其功能后,实现到GW48实验系统。

功能描述:用于模仿密码锁的工作过程。

完成密码锁的核心控制功能。

功能要求:设计一个密码锁,平时处于等待状态。

管理员可以设置或更改密码。

如果不预置密码,密码缺省为“1234”。

用户如果需要开锁,按相应的按键进入输入密码状态,输入4位密码,按下确定键后,若密码正确,锁打开;若密码错误,将提示密码错误,要求重新输入,三次输入都错误,将发出报警信号。

报警后,只有管理员作相应的处理才能停止报警。

用户输入密码时,若输入错误,在按下确定键之前,可以通过按取消键重新输入。

正确开锁后,用户处理完毕后,按下确定键,系统回到等待状态。

系统操作过程中,只要密码锁没有打开,如果60秒没有对系统操作,系统回到等待状态。

要求密码在输入过程中被依次显示,即先输入的为密码的第一位,总是显示在最左边。

用两个发光二极管模拟显示,其中一个显示当前的工作模式,灭表示用户模式,亮表示管理员模式;另外一个指示锁的状态,灭表示锁处于锁定,亮表示锁被开启。

注意:用两个按键实现密码输入,Key1选择输入的是第几位密码,KEY2输入密码数字。

功能描述:初始状态:初次使用密码锁时,要先用Reset键初始化。

初始状态下,用户密码为“1234”,管理员密码为“0000”。

用户开锁:默认情况下,密码锁处于用户使用状态。

如果当前为管理员状态,则按下user键回到用户状态。

用户开锁时,输入四位数用户密码,可以从out_code6的输出状态确定密码输入状态。

《E D A仿真与实践实习》学院:信息科学与工程学院课题名称:硬件描述语言设计——基于VHDL的电子密码锁的设计班级:学生:学号:指导教师:1 引言在日常的生活和工作中, 住宅与部门的安全防、单位的文件档案、财务报表以及一些个人资料的保存多以加锁的办法来解决。

若使用传统的机械式钥匙开锁,人们常需携带多把钥匙, 使用极不方便, 且钥匙丢失后安全性即大打折扣。

随着科学技术的不断发展,人们对日常生活中的安全保险器件的要求越来越高。

为满足人们对锁的使用要求,增加其安全性,用密码代替钥匙的密码锁应运而生。

基于EDA技术设计的电子密码锁。

以其价格便宜、使用方便、安全性高、成本低、功耗低、易操作等优点,受到了人们的普遍关注。

而以可编程逻辑器件(FBDA)为设计载体,以硬件描述语言(VHDL)为主要表达方式,以QuartusⅡ5.1开发软件等为设计工具设计的电子密码锁,由于其能够实现密码输入、密码校验、密码设置和更改等功能,因此,能够满足社会对安全防盗的需求。

本设计的各个模块由相应的VHDL程序具体实现,并在Quartus Ⅱ5.1环境下进行了整体电路的模拟仿真,最终实现“密码锁控制器设计”的要求。

2 设计容和要求2.1 设计容:题目:电子密码锁容:设计一个4位串行数字锁。

(1)开锁代码为4位二进制,当输入代码的位数与锁给定的密码一致,且按规定程序开锁时,方可开锁,并点亮一个指示灯。

否则进入“错误”状态,并发出报警信号。

(2)锁的密码可调,且预置方便,性好。

(3)串行数字锁的报警由点亮一个灯,直到按下复位开关,报警才停下。

此时,数字锁又自动等待下一个开锁状态。

要求:(1)通过查阅相关技术资料,详细描述电子密码锁的基本原理。

(2)编写电子密码锁的Verilog HDL或VHDL程序,并仿真编译下载验证。

(3)给出完整的系统顶层模块图与波形仿真图。

3 设计分案密码锁控制器是硬件与软件的结合。

根据设计要求,决定以FBDA 芯片和VHDL语言设计此电子密码锁。

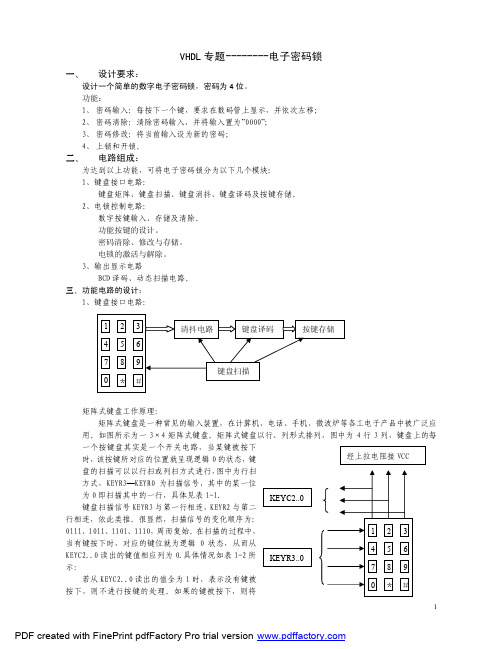

VHDL 专题--------电子密码锁一、设计要求:设计一个简单的数字电子密码锁,密码为4位。

功能:1、 密码输入:每按下一个键,要求在数码管上显示,并依次左移;2、 密码清除:清除密码输入,并将输入置为”0000”;3、 密码修改:将当前输入设为新的密码;4、 上锁和开锁。

二、 电路组成:为达到以上功能,可将电子密码锁分为以下几个模块: 1、键盘接口电路: 键盘矩阵、键盘扫描、键盘消抖、键盘译码及按键存储。

2、电锁控制电路: 数字按键输入、存储及清除。

功能按键的设计。

密码清除、修改与存储。

电锁的激活与解除。

3、输出显示电路BCD 译码、动态扫描电路。

三、功能电路的设计:1、键盘接口电路:矩阵式键盘工作原理: 矩阵式键盘是一种常见的输入装置,在计算机、电话、手机、微波炉等各工电子产品中被广泛应用。

如图所示为一3×4矩阵式键盘。

矩阵式键盘以行、列形式排列,图中为4行3列,键盘上的每一个按键盘其实是一个开关电路,当某键被按下时,该按键所对应的位置就呈现逻辑0的状态,键盘的扫描可以以行扫或列扫方式进行,图中为行扫方式,KEYR3—KEYR0为扫描信号,其中的某一位为0即扫描其中的一行,具体见表1-1. 键盘扫描信号KEYR3与第一行相连,KEYR2与第二行相连,依此类推。

很显然,扫描信号的变化顺序为:0111、1011、1101、1110,周而复始。

在扫描的过程中,当有键按下时,对应的键位就为逻辑0状态,从而从KEYC2..0读出的键值相应列为0.具体情况如表1-2所示: 若从KEYC2..0读出的值全为1时,表示没有键被按下,则不进行按键的处理。

如果的键被按下,则将KEYC2..0读出的送至键盘译码电路进行译码。

表1-2 键盘扫描与其对应的键值的关系时序产生电路: 在一个系统的设计中,往往需要多种时钟信号,最为方便的方法是利用一个自由计数器来产生各种需要的频率。

本电路需要:系统主时钟、消抖取样时钟和动态扫描时钟。

《基于VHDL语言和FPGA的电子密码锁》篇一一、引言随着科技的发展,电子密码锁已逐渐取代传统的锁具,成为了安全领域的重要组成部分。

而作为电子密码锁核心技术之一的FPGA(现场可编程门阵列)技术,以及VHDL语言编程的灵活性,更是对密码锁设计起到了重要的推动作用。

本文旨在详细探讨基于VHDL语言和FPGA的电子密码锁的设计与实现。

二、VHDL语言与FPGA概述VHDL(VHSIC Hardware Description Language)是一种硬件描述语言,用于描述电子系统的结构和行为。

而FPGA则是一种可编程逻辑器件,其内部由许多可配置的逻辑单元组成,通过编程可以实现各种复杂的数字电路功能。

将VHDL语言与FPGA相结合,可以实现电子密码锁的高效、灵活和可定制的设计。

三、电子密码锁的设计要求在基于VHDL语言和FPGA的电子密码锁设计中,首先需要明确设计要求。

这些要求包括:高安全性、易于使用、良好的扩展性以及低成本等。

此外,密码锁应能抵抗各种常见的攻击方式,如暴力破解等。

四、基于VHDL的密码锁设计与实现基于VHDL语言的电子密码锁设计主要分为几个模块:密码输入模块、解码模块、控制模块和输出模块等。

密码输入模块负责接收用户输入的密码;解码模块对输入的密码进行解码,判断其是否正确;控制模块根据解码结果控制输出模块的开关状态;而整个系统则由FPGA实现。

在VHDL编程中,需要详细描述各个模块的功能、接口以及它们之间的通信方式。

例如,密码输入模块应能接收一定长度的密码输入,并将其传递给解码模块。

解码模块则根据预设的算法对密码进行解码,并将结果传递给控制模块。

控制模块根据解码结果控制输出模块的开关状态,以实现密码锁的开启或关闭。

五、FPGA的实现与优化在FPGA上实现电子密码锁时,需要利用FPGA的编程工具进行编程和配置。

首先,将VHDL代码编译成可在FPGA上运行的二进制代码;然后,将二进制代码下载到FPGA中,实现对电子密码锁的硬件配置。

华南师范大学课程设计实验报告课程名称:可编程数字系统设计课程设计题目:电子密码锁姓名:程硕学院:物理与电信工程学院专业:理综一班年级:2011学号:20112600104一、设计原理用VHDL设计电子密码锁方案:作为通用电子密码锁,主要由 3 个部分组成:数字密码按键输入电路、密码锁控制电路和密码锁显示电路,作为电子密码锁的输入电路。

可供选择的方案有数字机械式键盘和触摸式数字键盘等多种。

(1)密码锁输入电路包括时序产生电路、键盘检测电路、键盘消抖电路等几个小的功能电路。

(2)密码锁控制电路包括按键数据存储电路,恢复出厂密码、两次正确输入后可修改密码、密码核对,多次错误报警,清屏等几个小的功能电路。

(3)八段数码管显示电路主要将待显示数据的BCD码转换成数码器的八段显示驱动编码。

二、系统分析本次课程设计成功地设计了一个简单的数字电子密码锁,密码为 4 位。

将电子密码锁分为以下几个模块:按键消抖模块、密码锁逻辑控制模块和密码锁显示模块,实现了以下功能:(1)密码输入:KEY1按下一次,数码管上显示数字加一,相应位置输入密码加一(2)位置选择:KEY2按下一次,数码管选择位左移一位(3)密码确认:KEY3按下一次,比较外部输入密码与原密码,正确LED长亮,错误LED变暗,同时显示密码置0;(4)密码修改:正确输入两次密码后,按下KEY4一次,将当前输入设为新的密码;(5)清屏:KEY5按下一次,外部输入置0;(6)恢复出厂设置:连续按下KEY5三次后恢复出厂密码“1234”;三、程序设计1由于程序稍显庞大,故采取分层次设计的方法,顶层采用画图法设计,底层采用VHDL 语言进行设计。

顶层电路图如图1所示图1Xiao_dou模块为按键消抖模块,main为密码锁控制模块,yima为数码管显示译码模块。

Set_shuma端口为数码管段选端口,用于选择数码管。

Led端口为led灯端口,key1,key2,key3,key4,key5为五个按键接口,show_shuma端口为数码管位选选择端口。

电子设计自动化实验实验名称综合性实验二、硬件描述语言的层次化设计实验设备(1)EDA实验箱(型号 ),(2)计算机,(3)EDA软件(QuartusII)实验目的1、熟悉EDA软件(QuartusII)的硬件描述语言输入设计方法;2、掌握VHDL语言的层次化设计方法和仿真分析方法;3、了解功能仿真、时序仿真和时序参数分析的意义。

实验容1、用VHDL语言完成4位十进制计数器、4位锁存器、测频控制器的设计,包括编译、综合、仿真;**2、采用层次化设计的方法,用VHDL语言的元件例化语句写出4位十进制频率计的顶层文件,并分别给出其测频功能和时序仿真分析波形图,并加以分析;**3、用EDA实验箱进行硬件验证,并分析测量结果;建议硬件测试实验电路采用NO.0 电路结构,待测信号F_IN接clock0;测频控制时钟CLK接clock2;**4、在2基础上将其扩展为8位十进制频率计,或带译码输出的4位十进制频率计。

实验报告要求根据以上实验容写出实验报告:1、简述4位频率计模块的工作原理及其设计、编译、仿真分析过程;2、给出模块设计文件、仿真测试文件、仿真结果波形图及其分析报告;3、简述硬件验证过程和验证结果。

1、简述4位频率计模块的工作原理根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为1秒的对输入信号脉冲计数允许的信号;1秒计数结束后,计数值锁入锁存器的锁存信号和为下一测频计数周期作准备的计数器清0信号。

这3个信号可以由一个测频控制信号发生器产生,即TESTCTL,它的设计要,TESTCTL的计数使能信号CNT_EN能产生一个1秒脉宽的周期信号,并对频率计的每一计数器CNT10的ENA使能端进行同步控制。

当CNT_EN高电平时,允许计数;低电平时停止计数,并保持其所计的脉冲数。

在停止计数期间,首先需要产生一个锁存信号LOAD,在该信号上升沿时,将计数器在前1秒钟的计数值锁存进各锁存器REG4B中,并由外部的7段译码器译出,显示计数值。

摘要摘要EDA 技术的应用引起了电子产品系统开发的革命性变革。

利用先进的EDA 工具,基于硬件描述语言,可以进行系统级数字逻辑电路的设计。

本文简述了VHDL 语言的功能及其特点,并以4位串行手机键盘电子密码锁设计为例,介绍了一种在QuartusⅡ6.0开发软件下,基于VHDL 硬件描述语言的复杂可编程逻辑器件(CPLD)的新型电子密码锁设计方法,阐述了其工作原理和软硬件设计方法。

该密码锁通过扫描电路、键盘译码电路、弹跳消除电路、控制电路和七段译码电路等实现了密码输入、数码清除、密码激活、电锁解除、密码更改和误码报警等功能。

本论文对该密码锁的程序进行了功能和时序仿真,结果表明该密码锁的功能满足设计要求,能够实现正常开锁、上锁和修改密码。

该密码锁体积小、功耗低、易于维护和升级,有很好的市场前景。

关键词:EDA,VHDL,FPGA,QuartusⅡ,电子密码锁ABSTRACTABSTRACTElectronic product and system development are being changed revolutionarily with EDA technology. We can design all kinds of digital logical circuits with advanced EDA tools and VHDL. The paper introduces the function and characteristic of programming of VHDL language briefly. Taking the design of the serial 4-bit electron coded lock for example, this paper introduces a new way to design electron coded lock with CPLD and QuartusⅡ6.0 as development software and VHDL as hardware description language. Its operating principles and the designing methods of hardware and software are explained in this article. This coded lock can perform the following functions, such as code input, code clear, code activating, code releasing, code correcting and wrong code alarming by scanning circuit, keyboard decode circuit, bounce eliminating circuit, control circuit. The functional and timing simulations are made. The results show that the design specification of the electronic coded lock is met and the unlock/lock and code correcting can be realized .This new electron coded lock has small size, low power. Its maintenance and upgrade are very convenient. And it has a better application prospect.Keywords: EDA , VHDL , FPGA, QuartusⅡ, Electron coded lock目录第1章引言 (1)1.1 课题背景 (1)1.2 国内外研究现状 (2)1.3 课题主要研究工作 (2)第2章EDA技术与VHDL语言简介 (3)2.1 EDA技术 (3)2.1.1 EDA技术的发展 (3)2.1.2 EDA技术的基本设计方法 (5)2.2 VHDL简介 (6)2.2.1 VHDL语言 (6)2.2.2 VHDL语言的特点 (9)第3章CPLD/FPGA硬件平台 (10)3.1 可编程逻辑器件的发展历史及概述 (10)3.2 FPGA/CPLD 概述 (11)3.3 CPLD工作原理 (12)3.4 FPGA工作原理 (13)第4章系统的原理设计 (14)4.1 系统设计要求 (14)4.2 系统设计方案 (14)4.2.1 密码锁输入电路的设计 (17)4.2.2 密码锁控制电路的设计 (23)4.2.3 密码锁显示电路的设计 (24)4.3 密码锁的整体组装设计 (25)第5章系统的程序实现 (26)5.1 键盘输入去抖电路的VHDL源程序 (26)5.2 密码锁输入电路的VHDL源程序 (29)5.3 密码锁控制电路的VHDL源程序 (34)5.4 密码锁显示电路的VHDL源程序 (38)第6章系统仿真分析及硬件验证 (40)6.1 系统仿真分析 (40)6.1.1 键盘输入去抖电路的仿真 (40)6.1.2 密码锁输入电路的仿真 (40)6.1.3 密码锁控制电路的仿真 (41)6.1.4 密码锁显示电路的仿真 (43)6.2 系统硬件验证 (44)第7章小结 (48)参考文献 (51)致谢 (52)第1章引言第1章引言1.1 课题背景自古以来,锁具都是人们心目中的“铁将军”,随着社会物质财富的日益增长和人们生活水平的不断提高,人们对它要求也越来越高,即要安全可靠,又要使用方便。

北京邮电大学数字电路与逻辑设计实验密码锁实验任务与要求设计并实现一个数字密码锁,密码锁有四位数字密码和一个确认开锁按键,密码输入正确,密码锁打开,密码输入错误进行警示。

基本要求:1、密码设置:通过键盘进行4位数字密码设定输入,在数码管上显示所输入数字。

通过密码设置确定键(BTN 键)进行锁定。

2、开锁:在闭锁状态下,可以输入密码开锁,且每输入一位密码,在数码管上显示“-”,提示已输入密码的位数。

输入四位核对密码后,按“开锁”键,若密码正确则系统开锁,若密码错误系统仍然处于闭锁状态,并用蜂鸣器或l ed 闪烁报警。

3、在开锁状态下,可以通过密码复位键(BTN 键)来清除密码,恢复初始密码“0000”。

闭锁状态下不能清除密码。

4、用点阵显示开锁和闭锁状态。

提高要求:1、输入密码数字由右向左依次显示,即:每输入一数字显示在最右边的数码管上,同时将先前输入的所有数字向左移动一位。

2、密码锁的密码位数(4~6 位)可调。

3、自拟其它功能。

二、系统设计设计思路本设计按照不同功能将具体实现分为不同模块,分别是时钟分频,防抖动,数码管扫描与显示,报警模块,密码验证模块,点阵显示模块,键盘输入模块以及功能键模块。

总体框图分块设计时钟模块:密码锁的工作时钟由外部晶振提供,时钟频率为50Mhz。

对CLK进行分频输出三路时钟CLK1Khz,CLK1,CLK2,频率分别为1Khz,5hz,1hz。

数码管显示与扫描七段数码管是电子开发过程中常用的输出显示设备。

当数码管的中的一个段被输入高电平,则相应的这一段被点亮。

反之则不亮。

四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。

八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起,8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭。

在键盘获取到行值和列值以后,组合成一个8位的数据,根据实现不同的编码在对每个按键进行匹配,找到键值后在7段码管显示。

大连理工大学本科实验报告题目:基于VHDL 4位电子密码锁的设计课程名称:数字电路课程设计学院(系):电子信息与电气工程专业:电子英强班级:学生姓名:学号:完成日期:2013.7.8成绩:2013 年7 月08 日题目:基于VHDL 4位电子密码锁的设计1 设计要求○1电子密码锁为4位8421BCD码,多于4位,密码只取前4位。

○2在输入密码错误,给出一个错误信号,有三次输入机会,若三次密码都输入错误,则给出一个报警信号,此后只能由密码管理员取消报警信号。

○3在输入密码正确的情况下,可以再次设定密码。

○4每次输入一个密码,将显示在7段数码管上,并依次左移。

○5每次输入密码的时候,按取消(cancel)键可以取消这次密码的输入,课重新输入4位密码。

2 设计分析及系统方案设计在实验室DE2开发板的条件下,考虑到key键只有4个,可以用switch开关来实现密码输入模块,用switch[9]~switch[0] 来实现数字9~0的输入,并通过译码模块将其转化为8421BCD码,由8421BCD码来驱动7段数码管作为密码锁的显示模块。

每按一个键,产生一个上升沿,给4个数码管做时钟,实现没输入一个数左移一位的效果。

为了实现密码输入多于4位,可以构造一个模为4的计数器来控制只取前4位密码。

共有三次输入密码的机会,可以构造一个模为3的计数器来控制。

密码比较模块:当按下确定键(yes)键,则将输入的密码和内置密码进行比较。

密码输入模块:当输入密码正确时,再输入密码,利用重置密码键(set_psw)直接将其赋值给内置的密码psw即可实现。

LED显示模块,用来显示密码输入的正确与否。

若输入密码与内置密码一致,则锁打开,输出一个高电平给LEDG,绿灯亮,密码错误则输出一个高电平给LEDR,红灯亮。

综合上述分析,本系统的硬件部分主要由密码锁输入译码模块、密码锁显示模块、密码锁控制模块、密码比较和重置模块和LED显示模块五个部分组成。

3系统以及模块硬件电路设计说明:1. 密码锁显示模块:段数码管是电子开发过程中常用的输出显示设备。

在本设计中使用的是4个四位一体、共阳极型七段数码管。

其单个静态数码管如右图所示。

2.密码输入和译码模块:用switch[9]~[0]实现数字9到0的输入。

clk Clk_in分频器密码锁输入和译码start resetNum[9]至Num[0]Out0Out1Out2Out3 q(4 downto 0)CancelOut_q(15 downto 0)Psw(15 downto 0)DE2开发板上使用的元件的管脚编号如下: 端口名 FPGA 管脚 说明alarm pin_af23 报警信号,红灯亮 cancel pin_v1 取消密码输入 clk pin_n2 50MHz 时钟 correct pin_ae22 密码正确,绿灯亮 num[0] pin_n25 输入数字0到9num[1] pin_n26 num[2] pin_p25 num[3] pin_ae14 num[4] pin_af14 num[5] pin_ad13 num[6] pin_ac13 num[7] pin_c13 num[8] pin_b13 num[9] pin_a13 out0[0] pin_af10 u0数码管 out0[1] pin_ab12 out0[2] pin_ac12 out0[3] pin_ad11 out0[4]pin_ae11CorrectOut_erroralarmyes密码比较和重置Set_psw4 系统的VHDL设计说明1.分频模块,即做一个模5000的计数器,从而将50MHz的时钟转化为10000Hz的时钟。

2.密码锁输入和译码,显示模块。

switch[9]~switch[0]模拟数字9~0的输入,例如switch[9]为高电平,而其他为低电平,则通过程序译码为9,同时产生一个clock时钟上升沿,由于人操作的时间必定大于0.00001s(即10000Hz 的时钟周期),所以在下次按键是,clock已经回到低电平,此后再按键clock 又产生一个上升沿。

由此构造的clock时钟可以为左移寄存器当时钟。

3.密码显示模块:switch改变一次,即每输入一个数,译码产生一个四位的BCD码,来驱动数码管。

并随着clock上升沿,依次左移显示。

4.密码比较和重置模块:在输入了4位密码后,16位BCD码已经保存在out_q里,通过与内置密码比较即可。

数码管的真值表(0代表亮,1代表不亮)VHDL源代码○1.主程序coded_lock代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity coded_lock isport(clk: in std_logic;start:in std_logic;reset:in std_logic;num:in std_logic_vector(9 downto 0);out3,out2,out1,out0:out std_logic_vector(6 downto 0);correct: buffer std_logic;yes:in std_logic;--admin:in std_logic;set_psw:std_logic;alarm: out std_logic;cancel: in std_logic;out_error: buffer std_logic);end;architecture behave of coded_lock is--******************************************************************* component decoder is --显示译码器的元件例化port(qq:in std_logic_vector(3 downto 0);result: out std_logic_vector(6 downto 0));end component;--******************************************************************* signal out_q: std_logic_vector(15 downto 0):="1111111111111111"; --out_q为4位密码锁的8421BCD码signal q:std_logic_vector(3 downto 0);--输入一个9~0的数字,q为其8421BCD码signal clock : std_logic:='0';--每按一次键,clock输出一个上升沿signal counter: integer range 0 to 2:=0;--模为3的计数器signal cnt4: integer range 0 to 4:=0;--模为5的计数器signal enable: std_logic:='1';--当输错3次密码,则此使能端为0,使无法译码signal psw:std_logic_vector(15 downto 0):="1001100001110110"; --默认密码为9876signal clk_in: std_logic;--5000分频之后的时钟begin--******************************************************************* process(clk_in,start,reset,enable)beginif reset='0' thenclock<='0';elsif rising_edge(clk_in) thenif start='1' and enable='1' thencase num is --按个键,clock来一个上升沿when "1000000000"=>q<="1001";clock<='1';when "010*******"=>q<="1000";clock<='1';when "0010000000"=>q<="0111";clock<='1';when "0001000000"=>q<="0110";clock<='1';when "0000100000"=>q<="0101";clock<='1';when "0000010000"=>q<="0100";clock<='1';when "0000001000"=>q<="0011";clock<='1';when "0000000100"=>q<="0010";clock<='1';when "0000000010"=>q<="0001";clock<='1';when "0000000001"=>q<="0000";clock<='1';when others =>q<="1111";clock<='0';end case;else null;end if;end if;end process;--***************************************************************** --左移进程,按下一个按键则clock输出一个高电平,显示译码器左移process(clock,yes,start,reset,cancel)beginif reset='0' thencorrect<='0';out_error<='0';counter<=0;enable<='1';alarm<='0';out_q<="1111111111111111";elsif cancel='1' thencorrect<='0';out_error<='0';out_q<="0000000000000000";cnt4<=0; --使计数器清零,重新开始译码elsif start='0' thencnt4<=0;out_q<="0000000000000000";elseif rising_edge(clock) thenif cnt4=4 thennull;elseout_q<=out_q(11 downto 0) & q;cnt4<=cnt4+1;end if;end if;if falling_edge(yes) thenif out_q=psw thencorrect<='1';out_error<='0';alarm<='0';elsif counter=2 thencorrect<='0';out_error<='1';alarm<='1';enable<='0';elsecorrect<='0';out_error<='1';alarm<='0';counter<=counter+1;end if;end if;end if;end process;--******************************************************************* process(correct,set_psw) --重新设置密码的进程beginif falling_edge(set_psw) thenif correct='1' then --输入密码正确才可以重新设置密码psw<=out_q;end if;end if;end process;--***************************************************************--分频模块:将50Mz 的时钟分频为10000Hzprocess(clk)variable tem:integer range 0 to 4999;beginif rising_edge(clk) thenif tem=4999 thenclk_in<='1';tem:=0;elsetem:=tem+1;clk_in<='0';end if;end if;end process;--******************************************************************* u3:component decoder port map(qq=>out_q(15 downto 12),result=>out3);u2:component decoder port map(qq=>out_q(11 downto 8),result=>out2);u1:component decoder port map(qq=>out_q(7 downto 4),result=>out1);u0:component decoder port map(qq=>out_q(3 downto 0),result=>out0); end behave;○2.decoder代码:library ieee;use ieee.std_logic_1164.all;entity decoder isport(qq:in std_logic_vector(3 downto 0);result: out std_logic_vector(6 downto 0));end;architecture reg of decoder isbeginprocess(qq)begincase qq iswhen "0000"=>result<="1000000";when "0001"=>result<="1111001";when "0010"=>result<="0100100";when "0011"=>result<="0110000";when "0100"=>result<="0011001";when "0101"=>result<="0010010";when "0110"=>result<="0000010";when "0111"=>result<="1111000";when "1000"=>result<="0000000";when "1001"=>result<="0010000";when others=>result<="1111111";end case;end process;end reg;5 结论以及结果说明计算机平台为window 7 64bit旗舰版,软件调试环境为QuartusⅡ6.0.使用的硬件芯片为EP2C35F672C6.下面试各个模块的仿真图:图1图1显示了密码输入和显示模块所实现的功能。