Recursive bipartitioning of signal flow graphs for programmable video signal processors

- 格式:pdf

- 大小:386.85 KB

- 文档页数:7

ACCUM (Accumulator) 积算模块ACCUM 积算模块用于计算模拟型输入信号(流量或脉冲数)的累计值,通常用作流量积算,用户可以清除、预设或保持模块的输出,积算模块可以串接起来使用。

AIN (Analog Input) 模拟信号输入模块AIN 模拟信号输入模块用于处理从模拟量输入类型的现场总线组件(FBM) 或(FBC) 来的单点输入信号,也可接受其它模块的信号。

它同时提供输入信号的修正、滤波、输出保持上次正常值、标度输出到所要求的工程单位、输入通道故障报警、超量程报警以及高、低绝对值报警。

AINR (Redundant Analog Input) 冗余的模拟信号输入模块AINR 模拟信号输入模块用于处理从冗余的模拟量输入类型的现场总线组件(FBMs)或(FBCs) 来的单点输入信号,也可接受二个其它模块的信号。

其它功能与AIN 模块相同。

ALMPRI (Alarm Priority Change) 报警优先级更改模块报警优先级更改模块可以动态地更改某个模块的报警点的优先级使得该报警点的报警优先级随过程的工况而改变。

它有5 个布尔输入PR_INj ( j=1~5 ) 第j 个为“1”时,就将第j 级优先级从PRIOUT 输出。

当PR_INi 与PR_INj (i<j)的输入同时为“1”时,PRIOUT=i 。

AOUT (Analog Output) 模拟信号输出模块模拟信号输出模块将一个单点模拟输出信号送往模拟量输出类型的现场总线组件的某个通道,它同时提供带偏置的手/自动功能,输出信号限制以及输出通道故障报警。

AOUTR (Redundant Analog Output) 冗余的模拟信号输出模块其功能与AOUT 模块基本相同。

BIAS (Bias) 偏置模块偏置模块的输出测量值(MEAS) 和偏置值(BIAS) 之和。

这两个输入可以分别进行标度。

同时,模块提供测量值报警。

但它不提供输出报警。

电子类公司笔试题精选一、模拟电路1基尔霍夫定理的内容是什么?〔仕兰微电子〕基尔霍夫电流定律是一个电荷守恒定律,即在一个电路中流入一个节点的电荷与流出同一个节点的电荷相等.基尔霍夫电压定律是一个能量守恒定律,即在一个回路中回路电压之和为零.2、平板电容公式(C=εS/4πkd)。

〔未知〕3、最基本的如三极管曲线特性。

〔未知〕4、描述反馈电路的概念,列举他们的应用。

〔仕兰微电子〕5、负反馈种类〔电压并联反馈,电流串联反馈,电压串联反馈和电流并联反馈〕;负反馈的优点〔降低放大器的增益灵敏度,改变输入电阻和输出电阻,改善放大器的线性和非线性失真,有效地扩展放大器的通频带,自动调节作用〕〔未知〕6、放大电路的频率补偿的目的是什么,有哪些方法?〔仕兰微电子〕7、频率响应,如:怎么才算是稳定的,如何改变频响曲线的几个方法。

〔未知〕8、给出一个查分运放,如何相位补偿,并画补偿后的波特图。

〔凹凸〕9、基本放大电路种类〔电压放大器,电流放大器,互导放大器和互阻放大器〕,优缺点,特别是广泛采用差分结构的原因。

〔未知〕10、给出一差分电路,告诉其输出电压Y 和Y-,求共模分量和差模分量。

〔未知〕11、画差放的两个输入管。

〔凹凸〕12、画出由运放构成加法、减法、微分、积分运算的电路原理图。

并画出一个晶体管级的运放电路。

〔仕兰微电子〕13、用运算放大器组成一个10倍的放大器。

〔未知〕14、给出一个简单电路,让你分析输出电压的特性〔就是个积分电路〕,并求输出端某点的rise/fall时间。

(Infineon笔试试题)15、电阻R和电容C串联,输入电压为R和C之间的电压,输出电压分别为C上电压和R 上电压,要求制这两种电路输入电压的频谱,判断这两种电路何为高通滤波器,何为低通滤波器。

当RC18、说说静态、动态时序模拟的优缺点。

〔威盛VIA 2003.11.06 上海笔试试题〕19、一个四级的Mux,其中第二级信号为关键信号如何改善timing。

基于ZYNQ的无线视频流发送设计尹雅君;李毅航;张宽;唐立军【摘要】随着我国高清电视的迅猛发展,4K高清视频的应用需要用到无线传输,视频的无线传输显得尤为重要.但现有的无线传输方案大都采用纯软件进行调制,而纯软件速度慢、代码多、调试难度高,对于高清视频的传输显得复杂.针对该问题,设计基于ZYNQ的无线视频流发送,通过ZYNQ的PS端进行数据发送控制,由集成调制芯片IT9517进行视频TS流的无线发送.该方案在保证处理速度和数据带宽的同时,还具有低功耗特点.测试结果表明,视频流能成功发送,具有一定的实用性.【期刊名称】《现代计算机(专业版)》【年(卷),期】2019(000)016【总页数】4页(P74-77)【关键词】ZYNQ-7000;TS流;视频传输;IT9517【作者】尹雅君;李毅航;张宽;唐立军【作者单位】长沙理工大学物理与电子科学学院,长沙 410114;长沙理工大学物理与电子科学学院,长沙 410114;长沙理工大学物理与电子科学学院,长沙 410114;长沙理工大学物理与电子科学学院,长沙 410114【正文语种】中文0 引言无线视频传输在工业和生活中有着极大的应用[1],随着视频分辨率的提高,在进行无线视频传输时,对处理视频数据流的嵌入式系统有了更高的要求。

Xilinx公司推出的可扩展性处理平台ZYNQ-7000系列产品,是双核ARM Cortex-A9处理器系统(PS)和FPGA可编程逻辑单元(PL)集成的SOC[2],在扩展嵌入式系统结构的同时,也提升了系统的性能和集成度,该平台实现了视频数据流传输的模块化、低功耗以及传输的高速稳定。

本文提出基于ZYNQ-7000平台和集成调制芯片的无线视频传输设计,可满足视频数据流的无线发送。

1 系统整体框架基于ZYNQ的无线视频流发送设计结构如上图1所示,发射端由ZYNQ视频处理平台、集成调制芯片IT9517、SD卡、DDR3存储器、VDMA组成。

高性能视频编码帧间预测的单元划分优化算法单娜娜;周巍;段哲民;魏恒璐【摘要】新一代的高性能视频编码(HEVC)通过应用各种先进技术来大幅提高视频编码的性能,然而,这些方法也大大增加了整个编码过程,尤其是预测编码阶段的计算复杂度.该文提出一种应用于高性能视频编码帧间预测的快速单元划分算法.该算法基于HEVC灵活的四叉树结构,根据被编码单元的运动特性来确定所编码信息的阈值,并以此作为单元划分的提前终止条件,从而减少了不必要的单元划分操作和率失真代价的相关计算,达到节省编码时间和降低编码复杂度的目的.实验结果表明,在峰值信噪比(PSNR)损失仅为0.0418 dB的情况下,所提算法可以平均降低46.1%的编码时间.【期刊名称】《电子与信息学报》【年(卷),期】2016(038)005【总页数】8页(P1194-1201)【关键词】高性能视频编码;编码单元;帧间预测;率失真代价【作者】单娜娜;周巍;段哲民;魏恒璐【作者单位】西北工业大学电子信息学院西安 710072;西北工业大学电子信息学院西安 710072;西北工业大学电子信息学院西安 710072;西北工业大学电子信息学院西安 710072【正文语种】中文【中图分类】TN919.811 引言新一代视频编码标准,即高性能视频编码(High Efficiency Video Coding, HEVC)标准,是由VCEG(Video Coding Experts Group)和MPEG(Moving Picture ExpertsGroup)联合成立的视频编码联合组(Joint Collaborative Team on Video Coding, JCT-VC)开发制定的[1]。

HEVC目前已经基本实现了在相同的质量下,压缩率比H.264/AVC提高一倍的目标,但是如何进一步提升编码效率和降低编码复杂度仍然是该领域内极具挑战性的热点问题。

在针对提高编码单元(CU)划分效率的有关问题上,人们进行了大量的研究,文献[2]提出了借助图像梯度信息提前选择CU深度范围的快速选择算法。

一、用P、V操作描述前趋关系。

P1、P2、P3、P4、P5、P6为一组合作进程,其前趋图如图2.3所示,试用P、V 操作描述这6个进程的同步。

p23图2.3说明任务启动后P1先执行,当它结束后P2、P3可以开始执行,P2完成后P4、P5可以开始执行,仅当P3、P4、P5都执行完后,P6才能开始执行。

为了确保这一执行顺序,设置5个同步信号量n、摄、f3、f4、g分别表示进程P1、P2、P3、P4、P5是否执行完成,其初值均为0。

这6个进程的同步描述如下:图2.3 描述进程执行先后次序的前趋图int f1=0; /*表示进程P1是否执行完成*/int f2=0; /*表示进程P2是否执行完成*/int f3=0; /*表示进程P3是否执行完成*/int f4=0; /*表示进程P4是否执行完成*/int f5=0; /*表示进程P5是否执行完成*/main(){cobeginP1( );P2( );P3( );P4( );P5( );P6( );coend}P1 ( ){┇v(f1);v(f1):}P2 ( ){p(f1);┇v(f2);v(f2);)P3 ( ){p(f1);┇v(f3);}P4( ){p(f2);┇v(f4);}P5 ( ){p(f2);┇v(f5);}P6( ){p(f3);p(f4);p(f5);┇}二、生产者-消费者问题p25生产者-消费者问题是最著名的进程同步问题。

它描述了一组生产者向一组消费者提供产品,它们共享一个有界缓冲区,生产者向其中投放产品,消费者从中取得产品。

生产者-消费者问题是许多相互合作进程的一种抽象。

例如,在输入时,输入进程是生产者,计算进程是消费者;在输出时,计算进程是生产者,打印进程是消费者。

因此,该问题具有很大实用价值。

我们把一个长度为n的有界缓冲区(n>0)与一群生产者进程P1、P2、…、Pm和一群消费者进程C1、C2、…、Ck 联系起来,如图2.4所示。

第一章:1、数字信号处理的实现方法一般有哪几种?答:数字信号处理的实现是用硬件软件或软硬结合的方法来实现各种算法。

(1) 在通用的计算机上用软件实现;(2) 在通用计算机系统中加上专用的加速处理机实现;(3) 用通用的单片机实现,这种方法可用于一些不太复杂的数字信号处理,如数字控制;(4)用通用的可编程 DSP 芯片实现。

与单片机相比,DSP 芯片具有更加适合于数字信号处理的软件和硬件资源,可用于复杂的数字信号处理算法;(5) 用专用的 DSP 芯片实现。

在一些特殊的场合,要求的信号处理速度极高,用通用 DSP 芯片很难实现( 6)用基于通用 dsp 核的asic 芯片实现。

2、简单的叙述一下 dsp 芯片的发展概况?答:第一阶段, DSP 的雏形阶段( 1980 年前后)。

代表产品: S2811。

主要用途:军事或航空航天部门。

第二阶段, DSP 的成熟阶段( 1990 年前后)。

代表产品: TI 公司的 TMS320C20主要用途:通信、计算机领域。

第三阶段, DSP 的完善阶段( 2000 年以后)。

代表产品:TI 公司的 TMS320C54 主要用途:各个行业领域。

3、可编程 dsp 芯片有哪些特点?答: 1、采用哈佛结构( 1)冯。

诺依曼结构,( 2)哈佛结构( 3)改进型哈佛结构2、采用多总线结构 3.采用流水线技术4、配有专用的硬件乘法-累加器5、具有特殊的 dsp 指令6、快速的指令周期7、硬件配置强8、支持多处理器结构9、省电管理和低功耗4、什么是哈佛结构和冯。

诺依曼结构?它们有什么区别?答:哈佛结构:该结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大地提高了数据处理能力和指令的执行速度,非常适合于实时的数字信号处理。

冯。

诺依曼结构:该结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行。

2024年3月第39卷第2期西安石油大学学报(自然科学版)JournalofXi’anShiyouUniversity(NaturalScienceEdition)Mar.2024Vol.39No.2收稿日期:2023 06 03基金项目:国家自然科学基金面上项目“基于频变信息的流体识别及流体可动性预测”(41774142);四川省重点研发项目“工业互联网安全与智能管理平台关键技术研究与应用”(2023YFG0112);四川省自然科学基金资助项目“基于超分辨感知方法的密集神经图像分割”(2022NSFSC0964)第一作者:曹凯奇(1998 ),男,硕士,研究方向:遥感图像标注。

E mail:819088338@qq.com通讯作者:文武(1979 ),男,博士,研究方向:人工智能在地球科学的应用、高性能计算。

E mail:wenwu@cuit.edu.cnDOI:10.3969/j.issn.1673 064X.2024.02.016中图分类号:TE19文章编号:1673 064X(2024)02 0128 15文献标识码:A基于改进DeepLabV3+的引导式道路提取方法及在震源点位优化中的应用曹凯奇1,张凌浩2,徐虹1,吴蔚3,文武1,周航1(1.成都信息工程大学计算机学院,四川成都610225;2.国网四川省电力公司电力科学研究院,四川成都610094;3.中国石油集团东方地球物理勘探有限责任公司采集技术中心,河北涿州072750)摘要:为解决自动识别方法在道路提取时存在漏提、错提现象,提出一种引导式道路提取方法提高修正效率。

在DeepLabV3+原有输入通道(3通道)的基础上添加额外输入通道(第4通道),将道路的4个极点转化为二维高斯热图后作为额外通道输入网络,网络以极点作为引导信号,使网络适用于引导式道路提取任务;设计并行多分支模块,提取上下文信息,增强网络特征提取能力;融合类均衡二值交叉熵和骰子系数组成新的复合损失函数进行训练缓解正负样本不均衡问题。

第27卷第4期计算机集成制造系统Vol.27No.4 2021年4月Computer Integrated Manufacturing Systems Apr.2021 DOI:10.13196/j.cims.2021.04.005基于FPGA的多源异构数据并行可配置采集方法李展鹏1,邹孝付",苏雍贺1,张长志彳,陶飞1(1.北京航空航天大学自动化科学与电气工程学院,北京100191;2.国网天津市电力公司电力科学研究院,天津300384)摘要:数据是支撑智能制造的关键要素,对生产各阶段数据的有效采集是实现“人一机一物一环境”制造全要素互联互通的基础。

随着制造升级发展,车间不断引入来自不同厂家,具有不同协议、不同接口的设备,使得待采集数据多源异构且采集需求不断变化。

传统数据采集设备难以并行采集多源异构数据、难以根据采集需求的动态变化对采集设备动态配置,因此提出一种基于现场可编程门阵列(FPGA)的多源异构数据并行可配置采集方法,基于FPGA硬件并行完成对多源异构数据的监测,保证数据采集实时性;研究FPGA动态重构技术并设计了数据采集可配置方法,提升数据采集灵活性;最后,设计了验证方案,验证了所提方法的有效性。

关键词:现场可编程门阵列;多源异构;数据采集;动态重构中图分类号:TP274.2文献标识码:AConfigurable acquisition method of multi-source heterogeneous data based on FPGALIZhanpeng1,ZOUXiaofu1+,SUYonghe1,ZHANG Changzhi2,TAO Fei1(1.School of Automation Science and Electrical Engineering,Beihang University,Beijing100191,China;2.State Grid Tianjin Electronic Power Research Institute,Tianjin300384,China)Abstract:Data is a key element supporting intelligent manufacturing.With the upgrading of manufacturing,the factory continuously introduces equipment from different manufacturers with different protocols and different interfaces.Data from that equipment collected has the characteristics of multi-source heterogeneity and constantly updated.Traditional data acquisition systems are customized for specific equipment,which is difficult to achieve parallel acquisition of multi-source heterogeneous data and real-time dynamic configuration.To solve these problems,a configurable acquisition method based on Field Programmable Gate Array(FPGA)was presented.Multi-source heterogeneous data were collected in parallel to ensure the real-time data acquisition.A configurable data acquisition scheme was designed to enhance the flexibility of data acquisition.A verification scheme was designed to verify the effectiveness of the proposed method.Keywords:field programmable gate array;multi-source heterogeneity;data acquisition;dynamic reconfiguration0引言随着云计算、大数据、物联网等新一代信息技术的发展以及信息化与工业化的“深度融合”,传统制造企业不断向智能制造的方向转型升级数据是智能制造的关键要素阂,只有在制造工厂底层实现对生产数据的有效感知,才能有效地完成工厂资源管理、车间计划与排产、生产过程监控等重要工收稿日期:2020-11-12;修灯日期:2020-11-25,,Received12Nov.2020;accepted25Nov.2020.基金项目:国家重点研发计划资助项目(2018YFB1500800);北京市科技重大专项资助项目(Z191100002719004);国家电网有限公司科技资助项目(SGTJDK00DYJS2000148)0Foundation items:Project supported by the National Key Research and Develapment Program,Chi-na(No.2018YFB1500800),the Beijing Municipal Science and Technology Major Project,China(No.Z191100002719004),and the Science and Technology Foundation of State Grid Corporation,China(No.SGTJDK00DYJS2000148).第4期李展鹏等:基于FPGA的多源异构数据并行可配置采集方法1009作闪。

ED&TC ’96

0-89791-821/96 $5.00 © 1996 IEEE

PPPP

outputs

inputs

ALEssiloswitchmatrixprogramBEsOEsMEs

ALEcoreME

core

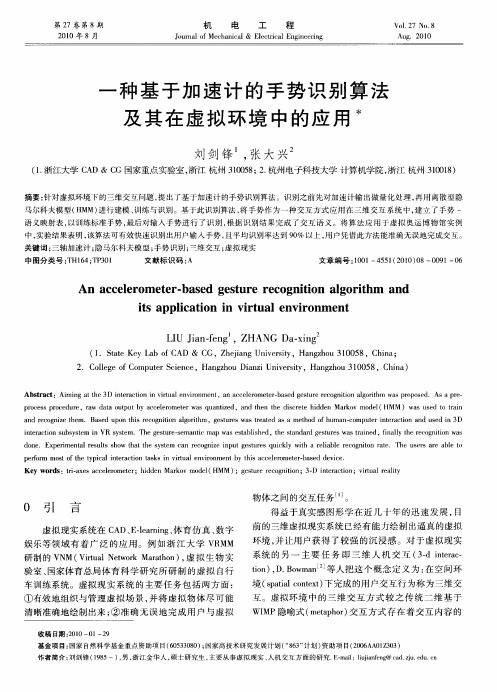

(3) Partial network covers

(1) SFG

(2) Partition VSP network

(4) Full network cover

i0

o0v0v1v0v1v1v1

OE

v1

OE

v0OEv0OEv0OEv0

ALE

v0v1o0i0

024681012costfeasible solution0

2

4

6

8

10

12

cost

feasible solution

Run 1Run 2Run 3Run 4Run 1Run 2Run 3

Try 2Try 1

Run 4Run 1Run 2Run 3

2.4

2.6

2.8

3.0

3.2

3.4

3.6

3.8

balance cost

feasible solution