计算机组成原理第四章

- 格式:ppt

- 大小:1.39 MB

- 文档页数:93

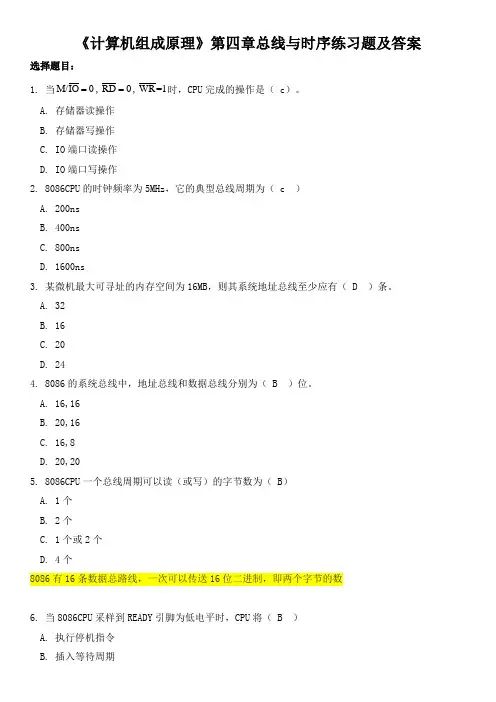

《计算机组成原理》第四章总线与时序练习题及答案选择题目:1. 当M/IO 0=,RD 0=,WR=1时,CPU 完成的操作是( c )。

A. 存储器读操作B. 存储器写操作C. IO 端口读操作D. IO 端口写操作2. 8086CPU 的时钟频率为5MHz ,它的典型总线周期为( c )A. 200nsB. 400nsC. 800nsD. 1600ns3. 某微机最大可寻址的内存空间为16MB ,则其系统地址总线至少应有( D)条。

A. 32B. 16C. 20D. 244. 8086的系统总线中,地址总线和数据总线分别为( B )位。

A. 16,16B. 20,16C. 16,8D. 20,205. 8086CPU 一个总线周期可以读(或写)的字节数为( B )A. 1个B. 2个C. 1个或2个D. 4个8086有16条数据总路线,一次可以传送16位二进制,即两个字节的数6. 当8086CPU 采样到READY 引脚为低电平时,CPU 将( B )A. 执行停机指令B. 插入等待周期C. 执行空操作D. 重新发送地址7. 当8086CPU读写内存的一个对准存放的字时,BHE和A0的状态为( A )。

A. 00B. 01C. 10D. 118. 当8086CPU采样到READY引脚为低电平时,CPU将( B )A. 执行停机指令B. 插入等待周期C. 执行空操作D. 重新发送地址9. 8086CPU的字数据可以存放在偶地址,也可以存放在奇地址。

下列说法正确的是( A )A. 堆栈指针最好指向偶地址B. 堆栈指针最好指向奇地址C. 堆栈指针只能指向偶地址D. 堆栈指针只能指向奇地址10. 8086CPU在进行对外设输出操作时,控制信号M/IO和DT/R状态必须是(D )A. 0,0B. 0,1C. 1,0D. 1,111. 8086CPU复位时,各内部寄存器复位成初值。

复位后重新启动时,计算机将从内存的( c )处开始执行指令。

第4章习题参考答案1.ASCII码是7位,如果设计主存单元字长为32位,指令字长为12位,是否合理?为什么?答:不合理。

指令最好半字长或单字长,设16位比较合适。

一个字符的ASCII 是7位,如果设计主存单元字长为32位,则一个单元可以放四个字符,这也是可以的,只是在存取单个字符时,要多花些时间而已,不过,一条指令至少占一个单元,但只占一个单元的12位,而另20位就浪费了,这样看来就不合理,因为通常单字长指令很多,浪费也就很大了。

2.假设某计算机指令长度为32位,具有双操作数、单操作数、无操作数三类指令形式,指令系统共有70条指令,请设计满足要求的指令格式。

答:字长32位,指令系统共有70条指令,所以其操作码至少需要7位。

双操作数指令3.指令格式结构如下所示,试分析指令格式及寻址方式特点。

答:该指令格式及寻址方式特点如下:(1) 单字长二XXX指令。

(2) 操作码字段OP可以指定26=64种操作。

(3) 源和目标都是通用寄存器(可分指向16个寄存器)所以是RR型指令,即两个操作数均在寄存器中。

(4) 这种指令结构常用于RR之间的数据传送及算术逻辑运算类指令。

4.指令格式结构如下所示,试分析指令格式及寻址方式特点。

15 10 9 8 7 4 3 0答:该指令格式及寻址方式特点如下:(1)双字长二XXX指令,用于访问存储器。

(2)操作码字段OP可以指定26=64种操作。

(3)RS型指令,一个操作数在通用寄存器(选择16个之一),另一个操作数在主存中。

有效XXX可通过变址寻址求得,即有效XXX等于变址寄存器(选择16个之一)内容加上位移量。

5.指令格式结构如下所示,试分析指令格式及寻址方式特点。

答:该指令格式及寻址方式特点如下:(1)该指令为单字长双操作数指令,源操作数和目的操作数均由寻址方式和寄存器构成,寄存器均有8个,寻址方式均有8种。

根据寻址方式的不同,指令可以是RR型、RS型、也可以是SS型;(2)因为OP为4位,所以最多可以有16种操作。

第四章存储系统4.1概述4.1.1技术指标4.1.2层次结构4.1.3存储器分类存储器是计算机系统中的记忆设备,用来存放程序和数据。

构成存储器的存储介质,目前主要采用半导体器件和磁性材料。

一个双稳态半导体电路或一个CMOS晶体管或磁性材料的存储元,均可以存储一位二进制代码。

这个二进制代码位是存储器中最小的存储单位,称为一个存储位或存储元。

由若干个存储元组成一个存储单元,然后再由许多存储单元组成一个存储器。

根据存储材料的性能及使用方法不同,存储器有各种不同的分类方法。

(1)按存储介质分作为存储介质的基本要求,必须有两个明显区别的物理状态,分别用来表示二进制的代码0和1。

另一方面,存储器的存取速度又取决于这种物理状态的改变速度。

目前使用的存储介质主要是半导体器件和磁性材料。

用半导体器件组成的存储器称为半导体存储器。

用磁性材料做成的存储器称为磁表面存储器,如磁盘存储器和磁带存储器。

(2)按存取方式分如果存储器中任何存储单元的内容都能被随机存取,且存取时间和存储单元的物理位置无关,这种存储器称为随机存储器。

半导体存储器是随机存储器。

如果存储器只能按某种顺序来存取,也就是说存取时间和存储单元的物理位置有关,这种存储器称为顺序存储器。

如磁带存储器就是顺序存储器,它的存取周期较长。

磁盘存储器是半顺序存储器。

(3)按存储器的读写功能分有些半导体存储器存储的内容是固定不变的,即只能读出而不能写入,因此这种半导体存储器称为只读存储器(ROM)。

既能读出又能写人的半导体存储器,称为随机读写存储器(RAM)。

(4)按信息的可保存性分断电后信息即消失的存储器,称为非永久记忆的存储器。

断电后仍能保存信息的存储器,称为永久性记忆的存储器。

磁性材料做成的存储器是永久性存储器,半导体读写4.2 半导体随机读写存储器主存储器由半导体存储芯片构成,容量较小时可采用SRAM芯片,容量较大时一般采用DRAM芯片。

主存中的固化区采用ROM芯片,包括PROM、EPROM、EEPROM、等。

第4章存储器1. 解释概念:主存、辅存、Cache、RAM、SRAM、DRAM、ROM、PROM、EPROM、EEPROM、CDROM、Flash Memory。

答:主存:主存储器,用于存放正在执行的程序和数据。

CPU可以直接进行随机读写,访问速度较高。

辅存:辅助存储器,用于存放当前暂不执行的程序和数据,以及一些需要永久保存的信息。

Cache:高速缓冲存储器,介于CPU和主存之间,用于解决CPU和主存之间速度不匹配问题。

RAM:半导体随机存取存储器,主要用作计算机中的主存。

SRAM:静态半导体随机存取存储器。

DRAM:动态半导体随机存取存储器。

ROM:掩膜式半导体只读存储器。

由芯片制造商在制造时写入内容,以后只能读出而不能写入。

PROM:可编程只读存储器,由用户根据需要确定写入内容,只能写入一次。

EPROM:紫外线擦写可编程只读存储器。

需要修改内容时,现将其全部内容擦除,然后再编程。

擦除依靠紫外线使浮动栅极上的电荷泄露而实现。

EEPROM:电擦写可编程只读存储器。

CDROM:只读型光盘。

Flash Memory:闪速存储器。

或称快擦型存储器。

2. 计算机中哪些部件可以用于存储信息?按速度、容量和价格/位排序说明。

答:计算机中寄存器、Cache、主存、硬盘可以用于存储信息。

按速度由高至低排序为:寄存器、Cache、主存、硬盘;按容量由小至大排序为:寄存器、Cache、主存、硬盘;按价格/位由高至低排序为:寄存器、Cache、主存、硬盘。

3. 存储器的层次结构主要体现在什么地方?为什么要分这些层次?计算机如何管理这些层次?答:存储器的层次结构主要体现在Cache-主存和主存-辅存这两个存储层次上。

Cache-主存层次在存储系统中主要对CPU访存起加速作用,即从整体运行的效果分析,CPU访存速度加快,接近于Cache的速度,而寻址空间和位价却接近于主存。

主存-辅存层次在存储系统中主要起扩容作用,即从程序员的角度看,他所使用的存储器其容量和位价接近于辅存,而速度接近于主存。