Mentor中测试点的自动添加

- 格式:pdf

- 大小:771.62 KB

- 文档页数:12

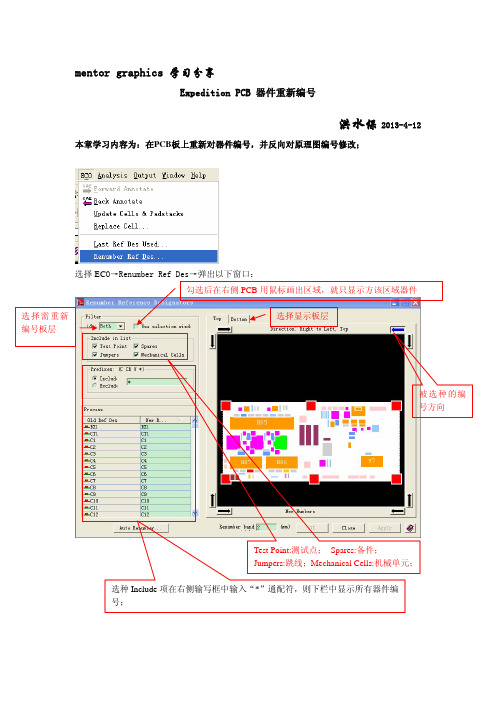

mentor graphics学习分享

Expedition PCB 器件重新编号

洪水保2013-4-12本章学习内容为:在PCB板上重新对器件编号,并反向对原理图编号修改;

选择EC O→Renumber Ref Des→弹出以下窗口:

选择需重新编号板层

勾选后在右侧PCB用鼠标画出区域,就只显示方该区域器件

选择显示板层

被选种的编

号方向

Test Point:测试点; Spares:备件;

Jumpers:跳线;Mechanical Cells:机械单元;

选种Include项在右侧输写框中输入“*”通配符,则下栏中显示所有器件编

号;

输写框中输入编号前缀,则下栏中仅显示相应前缀器件编号; 注:输入多个前缀时中间需加空格,输入完后直接Enter;

选种Exclude 项则是排除右侧输写框中输入的前缀,下栏中不显示相应前缀器件编号;注:Process 栏中不显示的编号,则不会进行重新编号;

完成筛选后,执行Auto Renumber 弹出窗口,输入相应参数后点OK ;

结语:重新编号后,编号是按照PCB 的方向顺序操作的,容易查找PCB 上的器件位置,并且美观; 编号起始号;

可以修改Process 栏中编号前缀;仅能一种类别操作;

可以在编号顺序号后面增加相同的后缀;

编号修改完成后进行确认,即完成重新编号;注:需保证原理图的数据连接正常;

运行该项,即可修改原理图中的编号;

本章完

2013-4-12。

库的建立1、名词说明。

1) 元件称为part.。

一个元件只有做好part,才能在原理图中放置device。

2)元件里面的符号称为symbol。

比如说一个元件分成几个部分来画的话,就可以说一个part里面含有几个symbol。

3)cell是元器件的PCB封装。

其他软件上称为PCBFOOTPRINT.。

4)padstacks 焊盘信息5)2、symbol的建立1)打开Library Manager2)file中的new和open是对应于库文件。

在此列中我们打开中心库,库文件后缀名为.lmc3)我们可以看到库文件里面包含的内容如下:该库文件包含有parts、cell、symbol和padstack。

4)首先我们建立一个symbol的partition。

在symbol这个分类里面,我们建立一个partition,作用跟文件夹差不多,可以用来区分不同类型的symbol。

5)建立symbol。

在partition上面右键点击出来,如下图:import symbols可以放入我们已经做好的symbol。

这里我们来做一个new symbol,出来一个new symbol 的对话框:填入symbol的名称。

6)这个时候调用了Design captures symbol editor这个程序。

7)先用rectangle和line画出symbol的框和引脚的引线,如下图:引脚的引线最低得隔开2个格子,以备后面的pin name和pin number的显示8)由于line不具备电气特性,因此我们加pin的时候得把pin加在line的外侧,双击pin,输入pin Number和pin name。

9)调整pin name和pin number的位置,如下图10)增加文字U,其属性为ref designator11)我们建立这样的两个symbol12)建立一个part ,在part里面的一个partition上面右键点击new part13)出现part editor14)选中需要编辑的part,如testpart,点击右下角的pin mapping15)出现pin mapping 对话框16)因为这个part分成2个框图,我们需要加入2个symbol17)点击左上角的import symbol,选择相应的symbol,把两个include勾选框勾选上,输入框里面填入1,这个slot就是说这个part里面含有几个这样的symbol18)插入第二个symbol,这个时候要把create勾选框勾上,其他的设置同上。

完整的PCB 设计系统解决方案Mentor Graphics 的Expedition 系列流程是专为大中型企业、研究院所,以及广泛使用高级PCB 设计技术或高速系统设计的团队量身定制的高度集成的系统设计平台,将业界最先进的设计和分析功能融合到包括设计数据管理和约束管理的单一环境中。

主要功能特点:完整的设计流程,包括库设计与管理、原理图设计、PCB 设计、生产数据的处理、SI 仿真、EMC/EMI 分析、热分析及数模混合仿真等,整个流程紧密结合,确保设计数据在整个流程中无缝传递;获得专利的并行设计技术,可以实现原理图和PCB 的多人协同设计;集成企业信息管理和供应链系统,实现优化的零部件挑选和采购,以及与生产的有效沟通;最先进的布局和布线技术,大幅度提高设计效率,缩短产品上市时间,提高产品质量;全面支持前沿的PCB 设计技术,比如高密度互联(HDI)/微过孔、埋入式元件、刚柔结合板,以及多引脚/高性能的IC 封装;紧密结合FPGA 设计流程,缩短设计周期,优化系统性能,减少产品成本;;与RF 分析工具Agilent ADS 无缝结合,消除RF 设计“黑盒子” 共享式约束编辑管理系统,方便流程中的所有工具使用;开放式的架构,为客户提供工业标准的开发语言及函数接口,如C、Java、VB 等,1 方便用户进行二次开发及定制个性化设置。

产品分类描述Expedition PCB Expedition PCB 作为最新一代的PCB 设计工具的代表,为当今高复杂度、高速PCB 设计、分析及生产制造提供了完整的、流畅的设计环境。

Expedition PCB 的核心是当今业界最受称誉的AutoActive 技术,该技术采用了实时45 度角无网格算法,将无网格交互布线和自动布线完美结合,将PCB 设计引入了一个新的高度。

最新器件工艺支持如Expedition PCB 支持当今最新的器件封装类型,BGA 类、CSOP 类、QSP 类、PLCC类等,支持所有器件封装的自动扇出,支持埋孔、盲孔的各种设计需求如引脚下、引脚边、引脚外不同位置放置过孔,支持微孔设计的各种工艺;性能极为优异的交互布线Expedition PCB 在交互布线的性能上远远领先其他工具,包括竞争对手都不得不折服。

PADS常见问题Pads layout中的一些操作问题1.Pad和Via有什么区别?PAD是焊盘,VIA是过孔,通孔焊盘和过孔都会打穿板子。

PCB 实物做出来焊盘那个孔周围是没有阻焊层的,可以焊锡在上面,而过孔则没有。

通孔焊盘和VIA都必须设置25 layer,且Drill Size(钻孔大小)与其他层一致,但Diameter(焊盘大小)要比其他层大20mil(0.5mm)以上。

焊盘外径D一般不小于(d+1.2)mm,高密度数字电路的D最小可到(d+1.0)mm,其中d 为钻孔直径。

1-1.请问PowerPCB如何设置才能在走线打孔的时候信号线自动用小孔,电源线用大孔?先在PAD STACKS中将你要用的VIA式样定制好,然后到Desing Ruels中先定义Default Routing Rules使用小的VIA,再到Net Ruels选中电源的Net,在Routing中定义成大的VIA。

如不行,可以敲入“VA”,将VIAMode设成Automatic,它就会按规则来了。

【不同网络设置线宽】在PowerPCB中是否有对不同网络分别进行线宽的设置吗?可以的!design rules->default-》Clearance-》Trace Width设置缺省值。

design rules->Class (或Net)中选中网络-》Clearance-》Trace Width 生成新的条件规则则实线不同网络不同走线宽度OK!1-2. 测点优先级:Ⅰ. 表贴焊盘(Test pad) Ⅱ. 零件脚(Component lead) Ⅲ. 贯穿孔(Via hole)1.如何添加和自定义过孔或盲孔?Setup ---> Design ---> Rules---> Default---> Routing 中Vias 的Availabe和Selected匀为空白,请问怎样设置过孔?那你就新建一个VIA类型SETUP->PAD STACKS->在PAD STACK TYPE中选VIA->ADD VIA……然后Setup --->Design --->Rules---> Default---> Routing 中,把新建的VIA 添加到SELECT VIA!1-3.怎么加测试点?【SCH上手动增加测试点】原理图中就增加测试点符号,并PCB库中做好对应测试点的封装(表贴封装、via封装),然后在layout中导入网表即可----------------------------------【PCB上直接手动加测试点】1) 连线时,点鼠标右键在end via mode 中选择end test point2) 选中一个网络的某段走线,右键-Add testpoint(只能加Via测试点)或Add Via,选中Via 或Pad修改属性为TestPoint3)将焊盘(表贴封装、via封装)做成一个部件,在ECO模式下用添加Component的方式增加进来,并修改属性为测试点--------------------------------【自动增加针床测试用的测试点】在PADS Layout中有专门加入测试点的方法。

Mentor Graphics企业PCB设计平台处理方案1.1 系统级PCB设计流程Mentor Graphics企业可以提供全线旳系统及PCB设计、仿真及原则化处理方案,如下图所示。

图2 PCB 设计、仿真及原则化处理方案1.2 模块阐明1.2.1 DxDesigner完备旳高性能原理图输入工具DxDesigner是原理图设计输入旳完整处理方案,包括设计创立、设计定义和设计复用。

提供强大旳原理图输入功能,实现PCB网表旳自动转换,支持LMS(Library ManagementSystem)库管理系统,保证迅速而以便地选择最理想、最廉价同步也是最轻易采购旳器件;DxDesigner支持层次化分页式模块化设计,以便实现设计复用缩短设计周期;集成旳仿真和高速电路分析环境保证概念设计阶段电路功能和性能满足设计指标,从而减少失误导致旳设计反复;设计数据集中管理保证企业内部从采购到生产各部门之间数据信息旳高度一致性,深入提高效率并且减少失误。

图3 DxDesigner设计界面DxDesigner是一种业界广泛使用旳、通用旳前端原理图设计工具,其兼容性可体现为三个方面:--兼容Protel/ Altium设计DxDesigner提供Protel/ Altium转换器,可与Protel/ Altium进行设计原理图和符号库进行双向数据转换。

--兼容Cadence(OrCAD)与PowerLogic设计DxDesigner提供OrCAD/ PADS Logic转换器,可直接导入OrCAD与PADS Logic环境下旳设计文献和符号库,转换过程中不丢失任何设计信息。

--兼容多种格式旳PCB网表与物理设计规则输出DxDesigner支持PADS Layout、Cadence Allegro、Expedition、BoardStation、Zuken等多种格式旳PCB网表输出与物理设计规则输出。

1.2.2 Expedition PCB 高速高密度PCB设计工具Expedition PCB为设计师提供了用于复杂PCB物理设计、分析和加工一整套可伸缩旳工具,它将交互设计和自动布线有机地整合到一种设计环境中。

Mentor PADS 快捷命令(无模指令) Modeless Commands目录全局设置(Global Settings) (1)栅格(Grids) (1)搜索(Search) (2)角度(Angles) (2)取消(Undo) (2)设计规则检查DRC (Design Rules Checking) (2)走线(Routing) (2)绘制对象(Drafting Objects) (3)替代鼠标单击(Mouse Click Substitutes) (3)其他方面(Various) (3)控制快捷键(Control Shortcuts) (3)功能快捷键(Function Key Shortcuts) (4)B lazeRouter中的快捷键 (4)全局设置(Global Settings)C 打开或关闭设计画面补充格式显示模式。

D 打开或关闭当前层拥有最高优先显示权。

DO 打开可关闭当前通孔显示模式。

ET 设置暂停走线时以测试点为结束方式。

I 进行数据库完整测试。

L<n> 改变当前层,如,则当前层为第二层N<s> 高亮某一网络O<r> 将焊盘和走线以其外框形式显示。

PO 将灌铜只显示其外框。

Q 打开快速测量器,以当前位置开始测量。

QL 对点亮网络、管脚对走线和某一选择范围进行快速测量共长度。

R<n> 设置最小显示线宽,小于此值的则只显示其中线,比如。

RV 保持建立重复性使用电路模式。

SPD 显示生成混合分割层的数据。

SPI 显示热焊盘标示符号“”在其热盘上。

SPO 只显示混合分割层的外框。

T 设置设计画面为透明显示模式。

X 打开或关闭文字外框显示。

W<n> 改变线宽,比如30。

栅格(Grids)G<xx> 过孔和设计栅格设置。

GD<xx> 显示栅格设置。

GP 打开或关闭极性栅格。

GP r a 移动到一个指定的极坐标点。

MENTOR中测试点的自动添加ZTE EDA 设计部匡胜林[摘要]随着EDA 设计的蓬勃发展,加之高速器件的大面积应用,单板的密度越来越大,提高PCB单板的设计效率,已经成为我们亟待解决的问题。

而PCB单机布线所花费的时间往往成为制约某一项目进度的瓶颈,为大幅度提高单板整体设计效率,使用MENTOR公司的ExpeditionPCB布线器进行多人协同设计能很好地解决这个问题。

而为了验证生产质量,需要在单板上添加在线测试点,如何应用Mentor布线工具来自动添加测试点提高工作效率显得尤为重要,本文就如何使用ExpeditionPCB布线器自动添加测试点给出一些基本方法。

[关键词]Mentor、测试点、提高效率一、前言本文就Mentor布线器从测试点的参数设置、库的调用、自动添加、间距规则检查等方面,来描述PCB协同设计中测试点的自动添加过程以及测试点自动添加和间距检查带来的方便。

虽然该工具对于密度相对较大的单板测试点的添加比例不能完全达到100%,但相对于手动添加测试点来说,减少的工作量还是相当大的。

(如果网络连线较短,所加的测试点Type有限,软件受间距规则限制,就会不予以自动添加。

因此,个别难加的测试点就需要我们对所布的Trace进行改善,手工添加来加以解决。

)二、测试点的参数设置我们在进行测试点的自动添加时,需要对我们所承担单板任务的测试点添加类型进行了解,即对测试点的Padstack有所熟悉,针对不同公司或者用户进行设置。

2.1 Mentor中测试点定义在Expedition PCB中测试点是作为虚拟器件放置的,因此测试点通常情况下可以放在相应网络的焊盘和过孔上。

但放在焊盘上,通常是不符合在线测试要求。

因此,多数时候,测试点是放在过孔上或单独放置的。

并且作为一个虚拟器件,我们就需要在Package Group里选择Test Point组,定义其Cell类型。

另外,关于Expedition中测试点阻焊的定义也是从同一个参考面去定义的,也就是说同一种类型的测试点,其TOP面和BOTTOM面的Padstacks参数是相同的。

因为它们的设置参数都是针对测试点这个虚拟器件,而非针对PCB单板的装配面或焊接面(或者A面还是B面),如图1。

图1 Mentor中测试点padstacks外形2.2 测试点参数设置打开Setup—Padstacks Editor选项,选择一个需要的过孔,复制作为测试孔,在properties中必须选择测试点属性:如Pin-Through.,在Hole Filter 中可选择测试点Hole的大小,如图2:(图中红色数据经过计算得到,为阻焊层)其中各Pads参数定义为:Mount side: 过孔的顶环(见上图中的红色层)Tnternal:过孔的内环Opposite side:过孔的底环Plane thermal:花焊盘Selected hole:过孔的大小Mount side: 测试点TOP面阻焊Opposite side:测试点BOTTOM面阻焊(以上均相对测试点自身而言)图2 Padstack Editor参数设置在生产可测试性要求中这些参数的设置至关重要,针对不同的设计要求,可对测试点参数进行各种不同的设置。

2.3 创建测试点虚拟器件由于Mentor布线器中测试点是虚拟器件,所以必须对所设置的Pastacks进行虚拟器件设置,我们打开Stup---Cell Editor,选择Package中的,出现下图3,在弹出框中按照要求设置好后,即可在ExpeditionPCB中Cell Editor 定义需要的测试点,创建虚拟测试点器件。

点击NEXT后在弹出的框中输入需要创建测试点所使用的Padstacks等各种设置,并画好所需要的Assembly outline或者placement outline(方便后续自动添加不致使其加在器件底下)图4。

图3 Cell Editor创建虚拟器件图4 测试点Padstack及外框设置三、测试点库的创建和调用通过上述测试点的各种参数已经设置好,那么根据不同公司和不同设计者要求,就可以设置各种不同的测试点,在今后的测试点添加中就可以直接调用,而不必重复操作。

那么,如何调用呢?我们在一个单板中设置好各种测试点,执行setup/LibrarySevices操作,将其导出到一个文件中(分别导出Padstacks和Cell),在新建的文件夹中生成*.hkp 文件,在今后的设计中就可以再次导入其中的数据,无需再设置,直接添加即可。

如下图5、6:图5 导入Padstacks 图6 导入cells其中,导出Padstacks、cells的操作只是需要创建一个新的文件,放置导出的*.hkp文件,把单板所设置的测试点参数导出即可,该单板中其他Padstacks、cells不必理会。

四、自动添加测试点4.1前期准备在自动添加测试点前,我们需要对刚布完线的PCB进行Batch DRC中的Hangers进行检查,并对Hanger s进行删除(自动删除),因为在自动添加测试点的时候很多的添加错误DRC报告都指出了由于Hangers的存在而导致自动添加失败。

为了满足测试点的间距问题,我们可以在Net Classes and Clearances(或者在CES中)等各项中设置所需要的测试点与各元素的间距要求,比如测试点与测试点中心距、测试点与表层线间距、测试点与同层器件间距、测试点与过孔间距等等。

(注意,因为测试点被认为是虚拟器件,所以其定义就为一个PAD)如图7,就是一个测试点与各元素的间距设置。

图7 测试点(Pad)与Trace、Via、Pad的间距设置4.2自动添加测试点对各种间距进行设置完毕后,我们就可以自动添加测试点了。

这里要加测试点,就包括了,需要添加测试点的个数、是否加在器件下等一些设置了。

4.2.1设置测试点添加个数执行Route\Testpoints\Aoute Assignment操作或者点击工具栏中图标,则出现下面的对话框(图8),在其中进行需要的设置即可。

图8 测试点添加个数设置一般我们在实际的PCB布线任务中,我们会做两个操作,先对单板中所有通孔器件进行测试点的自动添加,然后在对其他进行添加,依次类推,逐个添加。

4.2.2自动添加测试点一般而言,生产可测试性要求我们不把测试点添加在器件底下(插件式的器件除外),所以我们必须设置不允许加在器件底下的操作,点击上图中项,出现下面对话框(图9)。

在第一个可选框中,我们选需要添加的其中一种测试点Cell,并定义层面(TOP或 BOTTOM)以及测试点位号。

但是我们在加含Via的网络测试点的时候,就必须勾上“Use closed assembly outlines as test”项,就可以避免将测试点添加到器件底下,而且由于前面设置了各种间距要求,那么,自动添加的时候,它就会按照前面设置按“规则”添加了。

也就无须我们去手动控制添加的间距,大大地提高了工作效率。

图9 测试点位号设置完成上述步骤后,可以在不同层(TOP or BOTTOM)添加测试点,也可以加表贴测试点等等,总之,尽量将测试点加全。

当然,相对密度大的单板经常会有些测试点没有自动加上,如图10,需要手工添加。

图10 快速找到没有自动添加上的测试点点击Placed中显示为0的选项,即可较快的找到没有添加的网络(有阴影模式显示),并可手动的快速加上。

五、不规则测试点自动检查5.1测试点添加比例检查当测试点添加完后,在每种测试点添加完的时候(如加完表贴后加VIA型测试点)我们都过滤掉,以便设计者观察,所以最后的工作就是检查没有添加和加多的网络,我们就可以打开上图10来查看,如红色部分不符合设计者要求,就可以迅速找到所属网络来删除或添加。

5.2间距DRC检查打开Analysis—Batch DRC对话框或使用图标,Batch DRC对话框如图11,如图11 DRC检查项设置其中也可以将所设置的各相关项进行保存,下次单板任务就可以不用重复设置,可反复调用。

设置好后,再对要检查的各种间距分开设置,以便于找到各种不满足间距要求的测试点,也可以一次性设置全部不满足各种间距要求的测试点,只是现在错误时全部显示出来,不便于找到错误之处而已。

具体操作,点击上图红色部分,弹出图12,进行各种设置。

图12 各种间距要求检查图13 不满足要求的测试点显示DRC错误及Display设置DRC错误做好上述各种操作设置后,我们点击OK,就可以打开Display Control项,在Hazard项中勾上Proximity,定义好显示不满足要求的测试点错误提示的颜色后,就可以逐个找到不满足要求的测试点,进行修正。

当然,不论是出自自动布线还是自动添加测试点,没有人为因素的干预,是不会100%无误和满足的,所以,自动添加测试点也同样需要必要的人为干预,使软件做到最大程度的有效利用。

六、测试点自动添加注意事项通过实际运用,我们发现测试点的自动添加在Expedition PCB中会出现以下几种DRC错误报告:a、测试点加在器件底下b、测试点各类间距不够c、添加比例较低(50~60%)。

设计者就需要进注意以下事项:(1)测试点自动添加时,大多数设计者为了减少自动添加次数,往往将“Use closed polygon assembly outlines as test point obstructs”项不勾,导致大量DRC错误报告出现,因此我们必须勾上此项,否则就需要在操作完毕后对器件底下的Test point删除。

(2)添加前,要根据具体要求设置好各种间距要求,(注意不要遗漏一些区域规则)。

每一种测试点添加完后,最好随即进行DRC检查,以方便及时修正。

(3)测试点添加是软件自动操作,过程中会有推挤TRACE的状态,但不影响线的总体,所以设计者须将走线etch置于Unfixed Selected Items和Unlocked状态下,方便软件进行线的推挤。

七、结束语现代 设计行业的飞速发展,不能仅仅停留在手工作业上,随着MENTOR Expedition PCB布线器使用无网格布线及多人协同设计的发展,应用布线器中各种自动操作完成设计任务已成为一项提高效率的重要手段。

本文就如何使用MENTOR布线器中的自动添加测试点做了简单介绍,重要的还是实践。

只有积累大量的经验后,才可能对各种规则及参数设置灵活掌握和运用,从而提高单板的设计效率。

由于时间仓促,加之应用和理解水平有限,错误之处难免,欢迎探讨和斧正。

八、参考文献[1]俞延风·理解Expeditionpcb中测试点·中兴通讯EDA设计部,2006年8月。

[2]丁国兴等·印制电路板设计规范——生产可测试性要求·中兴通讯股份有限公司,2003年6月。