集成电路中的元器件及其寄生效应教学

- 格式:pptx

- 大小:1005.82 KB

- 文档页数:80

1.0 双极寄生在集成电路中,用反偏pn结隔离双极器件,存在一些潜在的寄生效应,同时,在一单外延区域集成一个以上器件也产生了更可能的寄生效应。

此寄生效应大多数是以不希望的pnp或npn晶体管出现。

所以,这个章节将不着重分析双极晶体管中寄生电容与寄生电阻的混合模式,但会着重关注由寄生pnp或npn管产生的电路工作中的变化。

因为结隔离的IC中,所有器件公用一个电衬底,电路同一性直接依赖于版图。

由于这些原因,设计工程师将会仔细观察IC的版图,约占设计工作的50%,可能的寄生以及它们对电路工作的影响将会用容易理解的电子/空穴注入理论完全的评价,连同IC的真正环境以及电路如何在那样的环境中工作一起完整的评价。

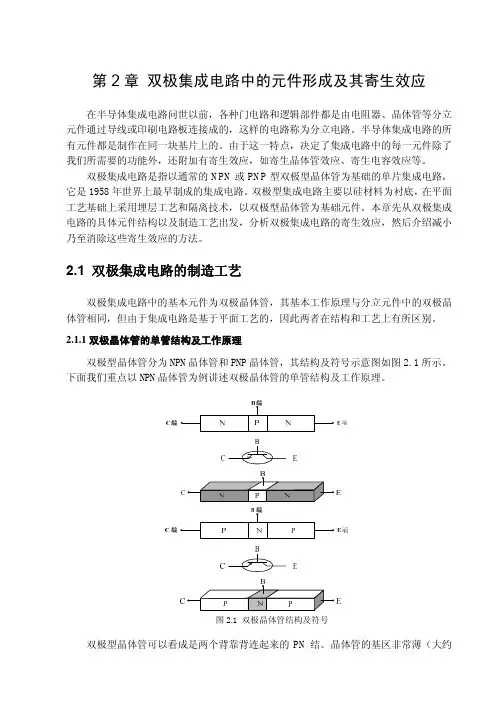

1.1 寄生pnp1.1.1 npn中的寄生pnp单块结隔离电路的npn管的剖面图如图1.1.1a所示,p隔离和p衬底区域通常相对于npn集电区n外延区域是反偏的。

不管怎样,这些隔离和衬底区域指出了在npn结构中可能的寄生pnp管,这个pnp是由npn的p型基区,连同npn的n型外延,以及p型隔离岛/衬底形成的。

npn的p型基区既可以是寄生pnp的发射极,也可以是集电极。

正常工作下,衬底相对于外延是偏置很负的,如果npn是正向导通,那么,寄生可以看作是一个对衬底的反偏二极管和衬底与外延电容并联。

npn的饱和将会允许寄生pnp管开始工作,当npn饱和,bc结正偏,这也会使两个可能的寄生pnp中的其中一个的be结正偏,如图1.1.1b。

npn的基区现在也是衬底pnp的发射极,npn的外延是pnp 的基极,衬底是pnp的集电极。

在这种工作模式下,npn基区向外延注入空穴,这个空穴电流的一部分将会在外延复合掉。

不管怎样,相当多的空穴将会被衬底/隔离收集。

这些空穴来源于npn的正向基极电流,这个结果在npn饱和区Ie<Ic+Ib。

这个能被看作是将基极电流的一部分直接分流到衬底。

如果npn被在基极的一个低阻源驱动进入饱和区,寄生pnp将会引导大量的空穴电流到衬底。

博士研究生入学考试《集成电路原理与设计》考试大纲①半导体集成电路张廷庆第一章集成电路的寄生效应集成电路的双极型工艺,典型PN结隔离工艺,集成电路元件结构和寄生效应;多结晶体管埃伯斯-莫尔模型,集成电路晶体管有源寄生效应的形成过程,集成电路中的寄生电容和效应。

第二章双极逻辑集成电路双极型逻辑集成电路的发展过程,简易TTL与非门的逻辑结构,六管单元TTL与非门的工作原理及功耗计算,TTL电路的温度特性,TTL门电路的逻辑是如何扩展。

第三章 TTL中大规模集成电路TTL芯片电路的简化逻辑门,单管逻辑门的功能,简化触发器结构,了解TTL中大规模集成电路的实际结构,双极型存储器结构,双极型门阵列结构与原理。

第四章 TTL电路版图设计结合集成电路工艺的确定,熟悉集成电路版图设计的一般程序,版图设计的基本尺寸确定,集成晶体管版图,二极管版图,肖特基势垒二极管版图,集成电阻的版图。

第五章 ECL和I2L电路ECL和I2L的电路结构,工作原理和特点,如何用这类型的电路实现逻辑运算。

第六章 nMOS逻辑集成电路电阻负载MOS倒相器,E/E MOS倒相器,E/D MOS倒相器,自举负载MOS倒相器的结构和原理;了解这些电路的速度,静态功耗等特点,弄清楚有比电路的定义;什么是静态MOS电路。

第七章 CMOS集成电路重点是CMOS倒相器和CMOS传输门的基本结构和工作原理,用这两类结构如何实现各种大规模逻辑电路,注意这类电路的转换特性和阈值损失原因;结合MOS工艺和版图结构,了解CMOS 电路中的栅锁效应。

第八章动态和准静态MOS电路理解栅电容的电荷存储效应,这种动态电路的输入阻抗,对信号的作用;动态倒相器和电路单元的基本结构和原理,各种动态和准静态MOS电路单元。

第九章 MOS集成电路的版图设计MOS集成电路的工艺设计和选择,MOS集成电路版图的设计规则,MOS集成电路各种单元电路的版图设计。

第十章 MOS大规模集成电路MOS大规模集成电路的特点,计算机辅助设计的流程,HMOS,MOS存储器,算术逻辑单元,半定制逻辑单元的设计实例。