verilog行为建模

- 格式:ppt

- 大小:1.06 MB

- 文档页数:61

SystemVerilog硬件设计及建模引言在硬件设计领域,SystemVerilog是一种广泛使用的硬件描述语言。

它结合了Verilog HDL和一些现代编程语言的特性,使得硬件设计和建模更加高效和灵活。

本文将介绍SystemVerilog的基本概念和语法,以及如何利用它进行硬件设计和建模。

SystemVerilog基础模块和端口在SystemVerilog中,设计被组织成一个个模块。

每个模块由一个或多个端口组成,其中包含输入端口、输出端口和双向端口。

端口是模块与外部世界之间通信的接口。

以下是一个简单的SystemVerilog模块的示例:module MyModule(input wire clk, input wire rst, input wire A, input wire B, output wire C);// 模块逻辑always @(posedge clk or posedge rst)if (rst)C <= 0;elseC <= A & B;endmodule数据类型SystemVerilog支持多种数据类型,包括基本数据类型(如整数和实数)和复杂数据类型(如数组和结构体)。

它还支持用户自定义数据类型。

以下是一些常用的数据类型示例:•整数类型:int, bit, logic•实数类型:real, time•数组类型:int my_array[8]•结构体类型:typedef struct packed {int x;int y;} my_struct;时序和复位在SystemVerilog中,时序和复位是设计中非常重要的概念。

时序表示硬件的时间顺序行为,比如时钟上升沿触发的操作。

复位用于将设计状态恢复到初始状态。

以下是一个简单的时序和复位示例:always @(posedge clk or posedge rst)if (rst)// 复位逻辑else// 时序逻辑仿真和验证SystemVerilog提供了丰富的仿真和验证功能,以验证设计的正确性。

verilog !用法-回复Verilog 是硬件描述语言(Hardware Description Language, HDL) 的一种,主要用于描述数字系统的行为和结构。

它是一种高级语言,可用于描述电子系统的硬件功能和电路行为。

Verilog 具有模块化和并行化的特性,能够快速且准确地描述电子系统及其各个组件之间的相互关系。

本文将以"Verilog 用法" 为主题,为读者逐步介绍Verilog 的基础知识和常见用法。

第一部分:Verilog 简介和基础知识(500 字)1. 什么是Verilog?Verilog 是一种硬件描述语言,用于描述数字系统的行为和结构。

它是一种高级语言,能够准确描述电子系统的硬件功能和电路行为。

2. Verilog 的起源和发展最早的Verilog 是在1984 年由Gateway Design Automation 公司的Philip Moorby 发明的。

之后,它被开放出来,并逐渐成为数字系统设计的行业标准。

3. Verilog 的基本元素Verilog 包含模块(module)、端口(port)、信号(signal)、寄存器(register)、线网(wire)、输入(input)、输出(output)、内部连接(assign)等基本元素,这些元素共同构成了一个完整的Verilog 描述。

4. Verilog 的行为建模Verilog 提供了多种行为建模的方式,包括组合逻辑(combinational)、时序逻辑(sequential)、有限状态机(finite state machine)等,使得设计者能够准确地描述电子系统的行为和时序。

第二部分:Verilog 模块和端口定义(500 字)1. Verilog 模块的定义Verilog 中的模块是一个独立的功能单元,它可以包含多个输入输出端口和内部信号,用于描述一个子系统的功能。

模块内部可以包含连接和互连逻辑,以及寄存器等具体的硬件描述。

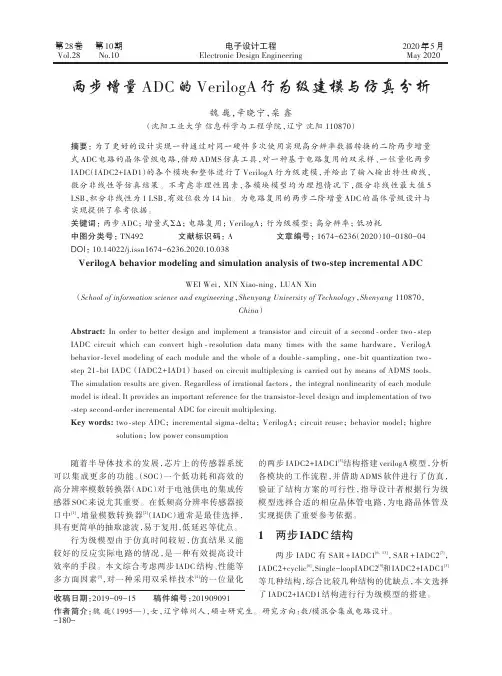

电子设计工程Electronic Design Engineering第28卷Vol.28第10期No.102020年5月May 2020收稿日期:2019-09-15稿件编号:201909091作者简介:魏巍(1995—),女,辽宁锦州人,硕士研究生。

研究方向:数/模混合集成电路设计。

随着半导体技术的发展,芯片上的传感器系统可以集成更多的功能。

(SOC )一个低功耗和高效的高分辨率模数转换器(ADC )对于电池供电的集成传感器SOC 来说尤其重要。

在低频高分辨率传感器接口中[1],增量模数转换器[2](IADC )通常是最佳选择,具有更简单的抽取滤波,易于复用,低延迟等优点。

行为级模型由于仿真时间较短,仿真结果又能较好的反应实际电路的情况,是一种有效提高设计效率的手段。

本文综合考虑两步IADC 结构、性能等多方面因素[3],对一种采用双采样技术[4]的一位量化的两步IADC2+IADC1[5]结构搭建verilogA 模型,分析各模块的工作流程,并借助ADMS 软件进行了仿真,验证了结构方案的可行性,指导设计者根据行为级模型选择合适的相应晶体管电路,为电路晶体管及实现提供了重要参考依据。

1两步IADC 结构两步IADC 有SAR +IADC1[6,13],SAR +IADC2[7],IADC2+cyclic [8],Single-loopIADC2[9]和IADC2+IADC1[3]等几种结构,综合比较几种结构的优缺点,本文选择了IADC2+IACD1结构进行行为级模型的搭建。

两步增量ADC 的VerilogA 行为级建模与仿真分析魏巍,辛晓宁,栾鑫(沈阳工业大学信息科学与工程学院,辽宁沈阳110870)摘要:为了更好的设计实现一种通过对同一硬件多次使用实现高分辨率数据转换的二阶两步增量式ADC 电路的晶体管级电路,借助ADMS 仿真工具,对一种基于电路复用的双采样、一位量化两步IADC (IADC2+IAD1)的各个模块和整体进行了VerilogA 行为级建模,并给出了输入输出特性曲线,微分非线性等仿真结果。

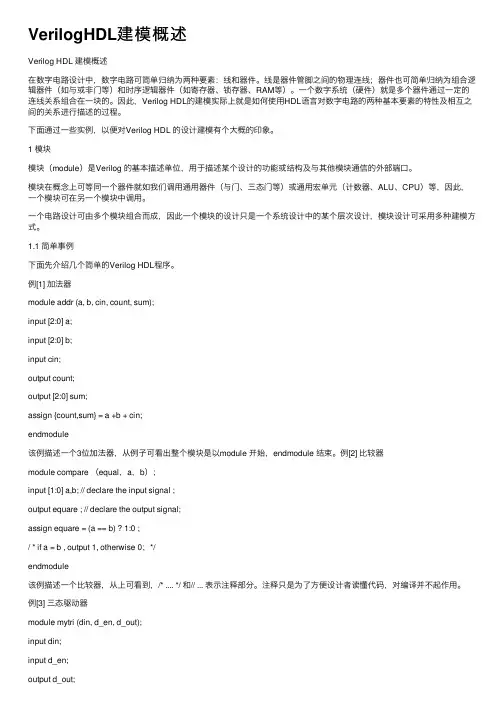

VerilogHDL建模概述Verilog HDL 建模概述在数字电路设计中,数字电路可简单归纳为两种要素:线和器件。

线是器件管脚之间的物理连线;器件也可简单归纳为组合逻辑器件(如与或⾮门等)和时序逻辑器件(如寄存器、锁存器、RAM等)。

⼀个数字系统(硬件)就是多个器件通过⼀定的连线关系组合在⼀块的。

因此,Verilog HDL的建模实际上就是如何使⽤HDL语⾔对数字电路的两种基本要素的特性及相互之间的关系进⾏描述的过程。

下⾯通过⼀些实例,以便对Verilog HDL 的设计建模有个⼤概的印象。

1 模块模块(module)是Verilog 的基本描述单位,⽤于描述某个设计的功能或结构及与其他模块通信的外部端⼝。

模块在概念上可等同⼀个器件就如我们调⽤通⽤器件(与门、三态门等)或通⽤宏单元(计数器、ALU、CPU)等,因此,⼀个模块可在另⼀个模块中调⽤。

⼀个电路设计可由多个模块组合⽽成,因此⼀个模块的设计只是⼀个系统设计中的某个层次设计,模块设计可采⽤多种建模⽅式。

1.1 简单事例下⾯先介绍⼏个简单的Verilog HDL程序。

例[1] 加法器module addr (a, b, cin, count, sum);input [2:0] a;input [2:0] b;input cin;output count;output [2:0] sum;assign {count,sum} = a +b + cin;endmodule该例描述⼀个3位加法器,从例⼦可看出整个模块是以module 开始,endmodule 结束。

例[2] ⽐较器module compare (equal,a,b);input [1:0] a,b; // declare the input signal ;output equare ; // declare the output signal;assign equare = (a == b) ? 1:0 ;/ * if a = b , output 1, otherwise 0;*/endmodule该例描述⼀个⽐较器,从上可看到,/* .... */ 和// ... 表⽰注释部分。

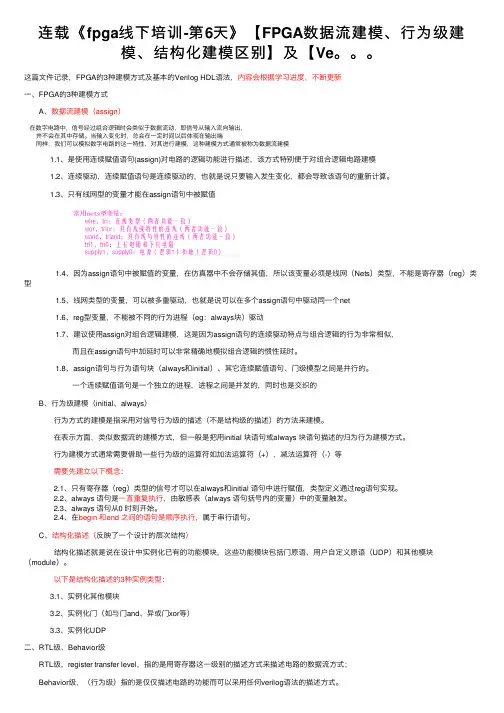

连载《fpga线下培训-第6天》【FPGA数据流建模、⾏为级建模、结构化建模区别】及【Ve。

这篇⽂件记录,FPGA的3种建模⽅式及基本的Verilog HDL语法,内容会根据学习进度,不断更新⼀、FPGA的3种建模⽅式 A、数据流建模(assign)在数字电路中,信号经过组合逻辑时会类似于数据流动,即信号从输⼊流向输出, 并不会在其中存储。

当输⼊变化时,总会在⼀定时间以后体现在输出端 同样,我们可以模拟数字电路的这⼀特性,对其进⾏建模,这种建模⽅式通常被称为数据流建模 1.1、是使⽤连续赋值语句(assign)对电路的逻辑功能进⾏描述,该⽅式特别便于对组合逻辑电路建模 1.2、连续驱动,连续赋值语句是连续驱动的,也就是说只要输⼊发⽣变化,都会导致该语句的重新计算。

1.3、只有线⽹型的变量才能在assign语句中被赋值 1.4、因为assign语句中被赋值的变量,在仿真器中不会存储其值,所以该变量必须是线⽹(Nets)类型,不能是寄存器(reg)类型 1.5、线⽹类型的变量,可以被多重驱动,也就是说可以在多个assign语句中驱动同⼀个net 1.6、reg型变量,不能被不同的⾏为进程(eg:always块)驱动 1.7、建议使⽤assign对组合逻辑建模,这是因为assign语句的连续驱动特点与组合逻辑的⾏为⾮常相似, ⽽且在assign语句中加延时可以⾮常精确地模拟组合逻辑的惯性延时。

1.8、assign语句与⾏为语句块(always和initial)、其它连续赋值语句、门级模型之间是并⾏的。

⼀个连续赋值语句是⼀个独⽴的进程,进程之间是并发的,同时也是交织的 B、⾏为级建模(initial、always) ⾏为⽅式的建模是指采⽤对信号⾏为级的描述(不是结构级的描述)的⽅法来建模。

在表⽰⽅⾯,类似数据流的建模⽅式,但⼀般是把⽤initial 块语句或always 块语句描述的归为⾏为建模⽅式。

verilog的三种描述方式

Verilog是一种硬件描述语言,用于描述和设计数字电路。

在Verilog中,有三种不同的描述方式:

1. 行为描述方式(Behavioral Modeling):行为描述方式是一

种基于事件的描述方法,用于描述数字电路的行为和功能。

在行为描述方式中,使用进程或函数来描述电路的操作和行为。

例如,使用if-else语句、for循环和并行块等来描述数字电路

的行为。

行为描述方式更接近于编程语言,可以方便地实现复杂的逻辑和算法。

2. 数据流描述方式(Dataflow Modeling):数据流描述方式是

一种基于信号流动的描述方法,用于描述数字电路的数据流和信号传递。

在数据流描述方式中,使用逻辑运算符(如AND、OR、NOT等)和信号赋值等来描述数字电路的数据流。

数据

流描述方式更接近于电路的物理结构,可以方便地实现组合逻辑。

3. 结构描述方式(Structural Modeling):结构描述方式是一

种基于模块和组件的描述方法,用于描述数字电路的结构和组成。

在结构描述方式中,使用模块实例化、端口连接和网表等来描述数字电路的结构。

结构描述方式更接近于电路的布局和连接,可以方便地进行模块化设计和层次化设计。

Verilog语言实现5分频电路的设计1.行为建模方法:使用行为建模方法,可以通过描述电路的功能行为来实现5分频电路。

以下是使用Verilog语言进行行为建模的代码示例:```verilogmodule DivideBy5input wire clk,output wire clk_outreg [2:0] counter;counter <= 0;clk_out <= ~clk_out;end else begincounter <= counter + 1;endendendmodule```在该示例中,定义了一个模块`DivideBy5`,包含一个输入端口`clk`和一个输出端口`clk_out`,分别用于输入时钟信号和输出分频后的时钟信号。

`reg [2:0] counter`是一个3位的寄存器,用于计数。

当计数达到5时,即计数器的值为5,会将`counter`复位为0,并将输出时钟信号`clk_out`取反。

否则,计数器的值会自增12.结构建模方法:使用结构建模方法,可以通过组合和顺序电路的连接方式来实现5分频电路。

以下是使用Verilog语言进行结构建模的代码示例:```verilogmodule DivideBy5input wire clk,output wire clk_outwire clk_out_2;wire clk_out_3;wire clk_out_4;DivideBy2 div_by_2 ( .clk(clk), .clk_out(clk_out_2) );DivideBy2 div_by_3 ( .clk(clk_out_2), .clk_out(clk_out_3) );DivideBy2 div_by_4 ( .clk(clk_out_3), .clk_out(clk_out_4) );DivideBy2 div_by_5 ( .clk(clk_out_4), .clk_out(clk_out) );endmodulemodule DivideBy2input wire clk,output wire clk_outreg clk_out;clk_out <= ~clk_out;endendmodule```在该示例中,定义了两个模块`DivideBy5`和`DivideBy2`。

1、VerilogHDL设计流程1、Verilog HDL 设计流程:1、文本编辑:文件保存为.v的文件;2、功能仿真:将.v文件调入HDL仿真软件,逻辑功能是否正确(前仿真);3、逻辑综合:将源文件调入逻辑综合软件进行综合,把语言综合成最简的布尔表达式,生成.edf的EDA工业标准文件;矚慫润厲钐瘗睞枥庑赖。

4、布局布线;5、时序仿真:验证电路的时序(后仿真)。

2、Verilog 程序包括四部分:1、端口定义2、I/O口说明3、内部信号声明4、功能定义3、逻辑功能定义:三种方法在模块中产生逻辑:(1)用assign 声明语句;如assign a = b & c;(描述组合逻辑)(2)用实例元件;如and #2 u1(q,a,b);(3)用always块;如(既可描述组合逻辑也可描述时序逻辑)always @ (posedge clk or posedge clr)beginif(clr) q <= 0;else if(en) q <= d;end4、网络类型变量两种:wire triWire型变量:用来表示单个门驱动或连续赋值语句驱动的网络类型数据。

Tri 型变量:用来表示多驱动器驱动的网络型数据。

线网类型两种:wire triTri 主要用于定义三态的线网;Wire型:代表的是物理连接,不存储逻辑值,要由器件驱动,通常用assign进行赋值Wire类型的信号没被驱动,缺省值为Z(高阻);信号没有定义数据类型时,缺省为wire 类型。

(缺省==默认)聞創沟燴鐺險爱氇谴净。

Reg型:默认初始值为x,通常用always模块内的指定信号,常代表触发器;always模块内被赋值的每一个信号都必须定义为reg型。

(寄存器类型)Verilog HDL 有5种寄存器类型:reg、integer、time、real、realtime5、运算符号所带操作数单目运算符:可带一个操作数,操作数放在运算符右边双目运算符:可带两个操作数,操作数放在运算符两边三目运算符:可带3个操作数,用三目运算符分隔开6、底层模块的调用:底层模块(被测试模块)可由测试模块调用如:(位置关联方式) :AND_G2 AND_G2(A,B,F);第一个AND_G2 为底层模块名,第二个为实例名,(A,B,F)为参数定义。

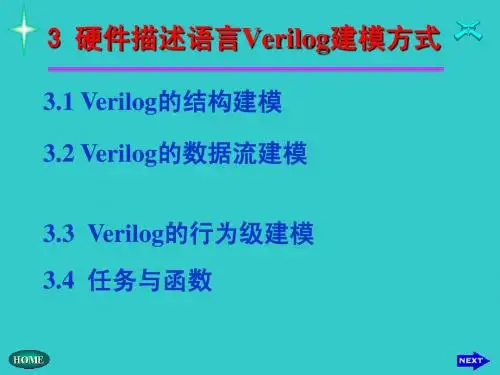

verilog HDL建模方式简单的归纳为三类:结构化描述方式、数据流描述方式、行为描述方式。

一个模块中往往是将三种建模方式混合起来使用,来描述一个完整的功能。

系统级、算法级、RTL级属于行为级,门级、开关级属于结构级。

系统级:用高级语言实现设计模块的外部性能的模型。

算法级:用高级语言结构实现设计算法的模型。

RTL级:描述数据在寄存器之间流动和如何树立这些数据的模型门级:描述逻辑门以及逻辑门之间的连线的模型开关级:描述器件中三极管和存储节点以及他们之间连线的模型1)结构化的建模方式是通过对电路的层次和组成结构进行描述来建模,即通过对器件的调用(HDL概念称为例化),并使用线网来连接各器件来描述一个模块的结构。

这里的器件包括Verilog HDL的内置门如与门and,异或门xor等,也可以是用户自定义的一个模块,还可以是FPGA厂商的提供的一个基本逻辑单元或者宏。

结构化的描述方式反映了一个设计的层次结构。

module FA_struct (A, B, Cin, Sum, Cout);input A;input B;input Cin;output Sum;output Cout;wire S1, T1, T2, T3;// -- statements -- //xor x1 (S1, A, B);xor x2 (Sum, S1, Cin);and A1 (T1, A, B );and A2 (T2, B, Cin);and A3 (T3, A, Cin);or O1 (Cout, T1, T2, T3 );endmodule该实例显示了一个全加器由两个异或门、三个与门、一个或门构成。

S1、T1、T2、T3则是门与门之间的连线。

代码显示了用纯结构的建模方式,其中xor 、and、or 是Verilog HDL 内置的门器件。

以 xor x1 (S1, A, B) 该例化语句为例:xor 表明调用一个内置的异或门,器件名称xor ,代码实例化名x1(类似原理图输入方式)。

system verilog语法总结以下是SystemVerilog语法的总结:1. 模块:SystemVerilog程序由一个或多个模块组成,模块是设计的构建块。

模块可以是分层的,可以包含其他模块或模块实例。

2. 端口:模块可以有输入、输出或双向端口。

端口声明指定传入或传出模块的信号的数据类型、方向和大小(如果适用)。

3. 数据类型:SystemVerilog支持各种数据类型,包括整数、实数、布尔值和字符串。

它还提供了数组和结构等复合类型。

4. 变量:在SystemVerilog中,可以使用"reg"或"logic"关键字声明变量。

它们可以是任何支持的数据类型,并且可以使用过程语句赋值。

5. 过程块:SystemVerilog提供了类似"always"、"initial"和"task/function"的过程块。

这些块允许您使用过程语句(如if-else、for循环、while循环等)来定义设计的行为。

6. 连续赋值:连续赋值用于描述模块内的组合逻辑。

它们使用assign关键字,并指定确定左侧信号值的右侧表达式。

7. 运算符:SystemVerilog支持各种运算符,包括算术、位、逻辑、比较和连接运算符。

这些运算符允许您对信号和变量进行操作。

8. 行为建模:SystemVerilog允许使用过程块、任务和函数进行行为建模。

这使您能够使用高级编程结构描述设计的功能。

9. 测试台:测试台是用于验证设计功能的单独模块或一组模块。

它生成输入刺激并监视输出,以确保正确操作。

10. 验证构造:SystemVerilog提供了各种验证构造,如断言、覆盖属性和带有随机刺激生成的测试台。

这些构造有助于验证设计的正确性。

请注意,这只是SystemVerilog语法的简要总结。

根据您的具体要求和用例,还有许多更多的功能和细节可以探索。