08 第八章 使用VHDL来设计时序电路 习题答案

- 格式:doc

- 大小:248.50 KB

- 文档页数:8

eda技术与vhdl设计答案eda技术与vhdl设计答案【篇一:eda技术与vhdl复习练习题】/p> 一、填空题1、pld的中文含义是:________。

2、asic的中文含义是:________。

3、“与-或”结构的可编程逻辑器件主要由四部分构成:________、________、____________和____________。

4、可编程逻辑器件结构图中一般用“x”表示此编程单元为________。

6、可编程逻辑器件结构图中无任何标记表示此编程单元为________。

7、可编程逻辑器件按规模的大小一般分为________和_________。

8、低密度可编程逻辑器件的主要有________和_________。

9、gal器件________取代全部pal器件。

10、pal器件只能________次编程。

11、gal器件能________次编程。

12、gal器件________取代ttl器件。

13、gal器件采用________擦除。

14、pal和gal器件________在系统编程。

15、pal和gal器件需要使用________编程。

二、选择题1、可编程逻辑器件pld的基本结构形式是_______:a:与——与b:与——或c:或——与d:或——或2、可以多次编程的器件是_______:a:prom b:plac:pal d:gal3、pld器件未编程时_______:a:有逻辑功能 b:没有逻辑功能c:pal器件有逻辑功能d:gal 器件有逻辑功能 4、gal器件可以用擦除:a:普通光 b:紫外线c:红外线 d:电5、gal16v8器件的输出引脚最多有______:a:16b:4 c:8 d:206、pal16v8器件的输入引脚最多有_______:a:16 b:4 c:8 d:207、gal16v8不能取代_________:a:pal16v b:74ls138c:74ls373 d:isplsi1032e-70plcc848、gal16v8的_______不可编程:a:与阵列b:或阵列c:输出逻辑宏单元olmc d:a、b都三、判断题1、gal器件的输出逻辑宏单元olmc不能实现pal器件的所有输出形式。

1、简述信号与变量的区别。

a.信号延时赋值,变量立即赋值b.信号的代入使用<=,变量的代入使用:=;c.信号在实际的硬件当中有对应的连线,变量没有2、简述可编程逻辑器件的优点。

a.集成度高,可以替代多至几千块通用IC芯片.极大减小电路的面积,降低功耗,提高可靠性b.具有完善先进的开发工具.提供语言、图形等设计方法,十分灵活.通过仿真工具来验证设计的正确性c.可以反复地擦除、编程,方便设计的修改和升级d.灵活地定义管脚功能,减轻设计工作量,缩短系统开发时间f.保密性好3、试比较moore状态机与mealy状态机的异同。

Moore输出只是状态机当前状态的函数. Mealy输出为有限状态机当前值和输入值的函数3、简述VHDL语言与计算机语言的差别。

a. 运行的基础。

计算机语言是在CPU+RAM构建的平台上运行。

VHDL设计的结果是由具体的逻辑、触发器组成的数字电路b.执行方式.计算机语言基本上以串行的方式执行.VHDL在总体上是以并行方式工作c.验证方式.计算机语言主要关注于变量值的变化.VHDL要实现严格的时序逻辑关系6、VHDL与计算机语言的区别?VHDL语言可以并行执行,计算机语言只能顺序执行。

3.1比较常用硬件描述语言VHDL、Verilog和ABEL语言的优劣。

1.VHDL:描述语言层次较高,不易控制底层电路,因而对综合器的性能要求较高。

有多种EDA工具选择,已成为IEEE标准。

应用VHDL进行工程设计的优点是多方面的,具体如下:(1) 与其他的硬件描述语言相比,VHDL具有更强的行为描述能力。

(2) VHDL具有丰富的仿真语句和库函数,使得在任何大系统的设计早期,就能查验设计系统的功能可行性,随时可对系统进行仿真模拟,使设计者对整个工程的结构和功能可行性做出判断。

(3) VHDL语句的行为描述能力和程序结构,决定了它具有支持大规模设计的分解和已有设计的再利用功能。

(4) 用VHDL完成一个确定的设计,可以利用EDA工具进行逻辑综合和优化,并自动把VHDL描述设计转变成门级网表(根据不同的实现芯片)。

时序逻辑电路课后习题答案时序逻辑电路课后习题答案时序逻辑电路是数字电路中的一种重要类型,它在数字系统中起到了关键的作用。

通过时序逻辑电路,我们可以实现各种复杂的功能,例如计数器、寄存器、状态机等。

然而,在学习过程中,我们常常会遇到一些难题,下面我将为大家提供一些常见时序逻辑电路习题的答案,希望能够对大家的学习有所帮助。

1. 设计一个4位二进制计数器,要求计数范围为0-9,采用时序逻辑电路实现。

答案:这是一个常见的计数器设计问题。

我们可以使用四个触发器构成一个4位二进制计数器。

每个触发器的输出作为下一个触发器的时钟输入,形成级联结构。

每当计数器的值达到9时,我们需要将其清零,即将四个触发器的输入端都置为0。

这样,当计数器的值达到9时,下一个时钟脉冲到来时,触发器的输出将变为0,实现了计数器的循环。

2. 设计一个状态机,实现一个简单的交通信号灯系统。

红灯亮20秒,绿灯亮30秒,黄灯亮5秒,然后再次循环。

答案:这是一个典型的状态机设计问题。

我们可以使用两个触发器来实现该状态机。

首先,我们需要定义三个状态:红灯状态、绿灯状态和黄灯状态。

然后,我们可以使用一个计数器来计时。

当计时达到20秒时,状态机切换到绿灯状态;当计时达到50秒时,状态机切换到黄灯状态;当计时达到55秒时,状态机切换到红灯状态。

然后,状态机重新开始计时,循环执行上述过程。

3. 设计一个电梯控制系统,实现电梯的上升和下降功能,并能够响应乘客的楼层请求。

答案:电梯控制系统是一个较为复杂的时序逻辑电路设计问题。

我们可以使用一个状态机来实现该系统。

首先,我们需要定义电梯的各个状态,例如静止状态、上升状态和下降状态。

然后,我们可以使用一个计时器来计时,以确定电梯的运行时间。

当电梯处于静止状态时,它可以响应乘客的楼层请求,并根据请求的楼层决定是上升还是下降。

当电梯到达目标楼层时,它会停止运行并等待下一个请求。

当电梯处于上升或下降状态时,它会根据当前楼层和目标楼层的差值来确定运行方向,并在到达目标楼层后停止运行。

EDA技术与VHDL程序设计基础教程习题答案第1章EDA习题答案1.8.1填空1.EDA的英文全称是Electronic Design Automation2.EDA技术经历了计算机辅助设计CAD阶段、计算机辅助工程设计CAE阶段、现代电子系统设计自动化EDA阶段三个发展阶段3. EDA技术的应用可概括为PCB设计、ASIC设计、CPLD/FPGA设计三个方向4.目前比较流行的主流厂家的EDA软件有Quartus II、ISE、ModelSim、ispLEVER5.常用的设计输入方式有原理图输入、文本输入、状态机输入6.常用的硬件描述语言有VHDL、Verilog7.逻辑综合后生成的网表文件为EDIF8.布局布线主要完成将综合器生成的网表文件转换成所需的下载文件9.时序仿真较功能仿真多考虑了器件的物理模型参数10.常用的第三方EDA工具软件有Synplify/Synplify Pro、Leonardo Spectrum1.8.2选择1.EDA技术发展历程的正确描述为(A)A CAD->CAE->EDAB EDA->CAD->CAEC EDA->CAE->CADD CAE->CAD->EDA2.Altera的第四代EDA集成开发环境为(C)A ModelsimB MUX+Plus IIC Quartus IID ISE3.下列EDA工具中,支持状态图输入方式的是(B)A Quartus IIB ISEC ispDesignEXPERTD Syplify Pro4.下列几种仿真中考虑了物理模型参数的仿真是(A)A 时序仿真B 功能仿真C 行为仿真D 逻辑仿真5.下列描述EDA工程设计流程正确的是(C)A输入->综合->布线->下载->仿真B布线->仿真->下载->输入->综合C输入->综合->布线->仿真->下载D输入->仿真->综合->布线->下载6.下列编程语言中不属于硬件描述语言的是(D)A VHDLB VerilogC ABELD PHP1.8.3问答1.结合本章学习的知识,简述什么是EDA技术?谈谈自己对EDA技术的认识?答:EDA(Electronic Design Automation)工程是现代电子信息工程领域中一门发展迅速的新技术。

一、选择题( A )1.一个项目的输入输出端口是定义在:A. 实体中B. 结构体中C. 任何位置D. 进程体( B)2.描述项目具有逻辑功能的是:A. 实体B. 结构体C. 配置D. 进程( A )3.关键字ARCHITECTURE定义的是:A. 结构体B. 进程C. 实体D. 配置( D )4.VHDL语言中变量定义的位置是:A. 实体中中任何位置B. 实体中特定位置C. 结构体中任何位置D. 结构体中特定位置( D )5.VHDL语言中信号定义的位置是:A. 实体中任何位置B. 实体中特定位置C. 结构体中任何位置D. 结构体中特定位置( B )6.变量是局部量可以写在:A. 实体中B. 进程中C. 线粒体D. 种子体中( A )7.变量和信号的描述正确的是:A. 变量赋值号是:=B. 信号赋值号是:=C. 变量赋值号是<=D. 二者没有区别( B )8. 变量和信号的描述正确的是:A. 变量可以带出进程B. 信号可以带出进程C. 信号不能带出进程D. 二者没有区别( )9.对于信号和变量的说法,哪一个是不正确的:A. 信号用于作为进程中局部数据存储单元B. 变量的赋值是立即完成的C. 信号在整个结构体内的任何地方都能适用D. 变量和信号的赋值符号不一样( A )10.下列关于变量的说法正确的是:A.变量是一个局部量,它只能在进程和子程序中使用B.B. 变量的赋值不是立即发生的,它需要有一个δ延时C. 在进程的敏感信号表中,既可以使用信号,也可以使用变量D. 变量赋值的一般表达式为:目标变量名<= 表达式( C )11.可以不必声明而直接引用的数据类型是:A. STD_LOGICB. STD_LOGIC_VECTORC. BITD. 前面三个答案都是错误的( C )12.STD_LOGIG_1164中定义高阻的字符是:A. XB. xC. zD. Z( A )13.STD_LOGIG_1164中字符H定义的是:A. 弱信号1B. 弱信号0C. 没有这个定义D. 初始值( B )14.使用STD_LOGIG_1164中的数据类型时:A. 可以直接调用B. 必须在库和包集合中声明C. 必须在实体中声明D. 必须在结构体中声明( B )15.关于转化函数说法正确的是:A. 任何数据类型都可以通过转化函数相互转化B. 只有特定类型的数据类型可以转化C. 任何数据类型都不能转化D. 前面说法都是错误的( C )16.VHDL运算符优先级说法正确的是:A. 逻辑运算的优先级最高B. 关系运算的优先级最高C. 逻辑运算的优先级最低D. 关系运算的优先级最低( D )17.VHDL运算符优先级说法正确的是:A. NOT的优先级最高B. AND和NOT属于同一个优先级C. NOT的优先级最低D. 前面的说法都是错误的( D )18.VHDL运算符优先级说法正确的是:A. 括号不能改变优先级B. 不能使用括号C. 括号的优先级最低D. 括号可以改变优先级( B )19.如果a=1,b=0,则逻辑表达式(a AND b)OR(NOT b AND a)的值是:A. 0B. 1C. 2D. 不确定( B )20.正确给变量X赋值的语句是:A. X<=A+B;B. X:=A+b;C. X=A+B;D. 前面的都不正确( )21.VHDL文本编辑中编译时出现如下的报错信息,其错误原因是:Error: VHDL syntax error: choice value length must match selector expression value lengthA. 表达式宽度不匹配B. 错将设计文件存入了根目录,并将其设定成工程C. 设计文件的文件名与实体名不一致D. 程序中缺少关键词( D )22.在VHDL语言中,下列对时钟边沿检测描述中,错误的是:A. if clk’event and clk = ‘1’ thenB. if falling_edge(clk) thenC. if clk’event and clk = ‘0’ thenD. if clk’stable and not clk = ‘1’ then( D )23.在VHDL中,可以用以下哪条语句表示检测clock下降沿:A. clock’ eventB. clock’ event and clock=’1’(上升沿)C. clock=’0’D. clock’ event and clock=’0’( D )24.VHDL语言共支持四种常用库,其中哪种库是用户的VHDL设计现行工作库:A. IEEE库B. VITAL库C. STD库D. WORK工作库( A )25.VHDL常用的库是:A. IEEEB. STDC. WORKD. PACKAGE( B )26.下列语句中,不属于并行语句的是:A. 进程语句B. CASE语句C. 元件例化语句D. WHEN…ELSE…语句( D )27.下面哪一个可以用作VHDL中的合法的实体名:A. ORB. V ARIABLEC. SIGNALD. OUT1( B )28.下列关于CASE语句的说法不正确的是:A. 条件句中的选择值或标识符所代表的值必须在表达式的取值范围内B. CASE语句中必须要有WHEN OTHERS=>NULLC. CASE语句中的选择值只能出现一次,且不允许有相同的选择值的条件语句出现D. CASE语句执行必须选中,且只能选中所列条件语句中的一条( D )29.VHDL中,为目标变量赋值符号是:A. =:B. =C. <=D. :=( B )30.VHDL语言是一种结构化设计语言,一个设计实体(电路模块)包括实体与结构体两部分,结构体描述:A. 器件外部特性B. 器件的内部功能C. 器件的综合约束D. 器件外部特性与内部功能。

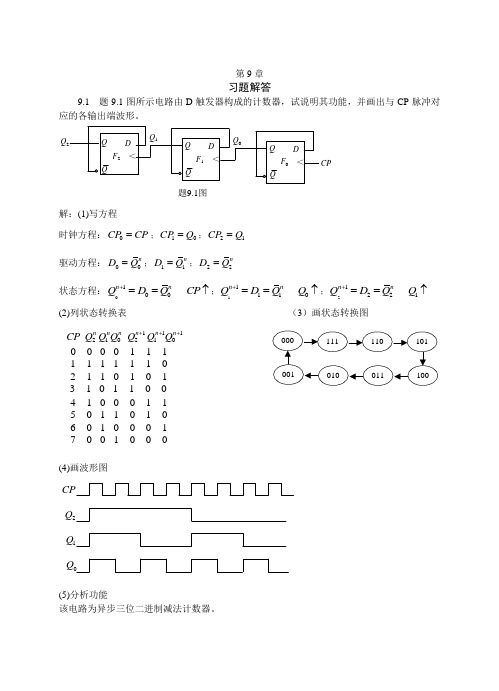

第9章习题解答9.1 题9.1图所示电路由D 触发器构成的计数器,试说明其功能,并画出与CP 脉冲对应的各输出端波形。

Q CP题9.1图解:(1)写方程时钟方程:0CP CP =;10CPQ =;21CP Q = 驱动方程:00n D Q =;11n D Q =;22n D Q =状态方程:0100n n Q D Q CP +==↑;11110n n Q D Q Q +==↑;21221n nQ D Q Q +==↑(2)列状态转换表 (3)画状态转换图111210210n n n n n n CP Q Q Q Q Q Q +++0 0 0 0 1 1 11 1 1 1 1 1 02 1 1 0 1 0 13 1 0 1 1 0 04 1 0 0 0 1 15 0 1 1 0 1 06 0 1 0 0 0 17 0 0 1 0 0 0(4)画波形图CP 2Q 1Q 0Q(5)分析功能该电路为异步三位二进制减法计数器。

9.6 已知题9.6图电路中时钟脉冲CP 的频率为1MHz 。

假设触发器初状态均为0,试分析电路的逻辑功能,画出Q 1、Q 2、Q 3的波形图,输出端Z 波形的频率是多少?CP题9.6图解:(1)写方程时钟方程:123CP CP CP CP ===驱动方程:113n n D Q Q =;212n n D Q Q =⊕;312n n D Q Q =状态方程:11113n n n Q D Q Q CP +==↑;12212n n n Q D Q Q CP +==⊕↑;13312n n n Q D Q Q CP +==↑ 输出方程:3n Z Q =(2)列状态转换表 (3)画状态转换图111321321n n n n n n CP Q Q Q QQ Q Z+++0 0 0 0 0 0 1 01 0 0 1 0 1 0 02 0 1 0 0 1 1 03 0 1 1 1 0 0 04 1 0 0 0 0 0 1 1 0 1 0 1 0 1 1 1 0 0 1 0 1 1 1 0 0 1 0 1(4)画波形图(5)分析功能该电路为能够自启动的同步5进制加法计数器。

VHDL程序填空题(一) 在下面横线上填上合适的VHDL关键词,完成2选1多路选择器的设计。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;1 MUX21 ISPORT(SEL:IN STD_LOGIC;A,B:IN STD_LOGIC;Q: OUT STD_LOGIC );END MUX21;2 BHV OF MUX21 ISBEGINQ<=A WHEN SEL=’1’ EL SE B;END BHV;(二) 在下面横线上填上合适的语句,完成BCD-7段LED显示译码器的设计。

LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL;ENTITY BCD_7SEG ISPORT( BCD_LED : IN STD_LOGIC_VECTOR(3 DOWNTO 0);LEDSEG : OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END BCD_7SEG;ARCHITECTURE BEHAVIOR OF BCD_7SEG ISBEGINPROCESS(BCD_LED)3IF BCD_LED="0000" THEN LEDSEG<="0111111";ELSIF BCD_LED="0001" THEN LEDSEG<="0000110";ELSIF BCD_LED="0010" THEN LEDSEG<= 4 ;ELSIF BCD_LED="0011" THEN LEDSEG<="1001111";ELSIF BCD_LED="0100" THEN LEDSEG<="1100110";ELSIF BCD_LED="0101" THEN LEDSEG<="1101101";ELSIF BCD_LED="0110" THEN LEDSEG<="1111101";ELSIF BCD_LED="0111" THEN LEDSEG<="0000111";ELSIF BCD_LED="1000" THEN LEDSEG<="1111111";ELSIF BCD_LED="1001" THENLEDSEG<="1101111";ELSE LEDSEG<= 5 ;END IF;END PROCESS;END BEHAVIOR;(三) 在下面横线上填上合适的语句,完成数据选择器的设计。

vhdl课后习题答案VHDL课后习题答案在学习VHDL(VHSIC Hardware Description Language)这门课程时,课后习题是巩固知识、提高能力的重要方式。

通过认真完成课后习题并查看答案,我们可以更好地理解和掌握VHDL的相关知识,提高自己的编程能力。

下面我们将通过几个典型的VHDL课后习题答案来展示VHDL的魅力和应用。

1. 课后习题一题目:使用VHDL编写一个简单的门电路,包括AND门、OR门和NOT门,并进行仿真验证。

答案:首先,我们定义AND门、OR门和NOT门的输入输出信号。

然后,使用VHDL语言编写各个门电路的逻辑实现,并进行仿真验证。

最后,我们可以观察仿真波形图,验证门电路的功能是否符合预期。

2. 课后习题二题目:使用VHDL编写一个4位全加器,并进行综合、布线和时序分析。

答案:首先,我们定义全加器的输入输出信号。

然后,使用VHDL语言编写4位全加器的逻辑实现,并进行综合、布线和时序分析。

最后,我们可以观察综合和布线报告,分析全加器的资源利用情况和时序性能。

3. 课后习题三题目:使用VHDL编写一个有限状态机(FSM),实现一个简单的计数器,并进行状态转移图和状态转移表的分析。

答案:首先,我们定义有限状态机的状态和状态转移条件。

然后,使用VHDL 语言编写有限状态机的逻辑实现,并进行状态转移图和状态转移表的分析。

最后,我们可以观察状态转移图和状态转移表,验证有限状态机的状态转移是否符合预期。

通过以上几个VHDL课后习题答案的展示,我们可以看到VHDL在数字电路设计和硬件描述方面的强大应用。

通过学习VHDL并完成课后习题,我们可以提高自己的编程能力,掌握数字电路设计的基本原理和方法。

希望大家在学习VHDL的过程中能够认真完成课后习题,并不断提高自己的编程水平。

vhdl_参考答案_上机练习三:时序逻辑电路设计2VHDL与复杂数字系统设计上机实验3:时序逻辑电路的VHDL程序设计⼀、实验⽬的:1.掌握在Max+plus II开发平台上,使⽤硬件描述语⾔设计电路的基本操作步骤;2.运⽤所学VHDL的描述语句完成⼀种时序逻辑电路的设计。

⼆、要点:时序逻辑电路在电路结构上有两个显著特点:第⼀,时序电路通常包含组合电路和存储电路两个组成部分,⽽且存储电路是必不可少的。

第⼆,存储电路的输出状态必须反馈到组合电路的输⼊端,与输⼊信号⼀起,共同决定组合逻辑电路的输出。

时序电路的信号变化特点:时序电路以时钟信号为驱动;电路内部信号的变化(或输出信号的变化)只发⽣在特定的时钟边沿;其他时刻输⼊信号的变化对电路不产⽣影响;要点:执⾏条件的控制;时钟边沿的检测;1、执⾏条件的控制采⽤进程描述可以有效控制执⾏条件,若进程以时钟信号(clk)为唯⼀敏感信号,则只有当时钟信号变化时,进程才执⾏;在其他时刻,任何输⼊信号的变化对电路(进程)不起作⽤;模版1:process(clock) --敏感信号表中只有时钟beginif rising_edge(clock) then--监测时钟上升沿,若⽤falling_edge(clock) ……--则监测时钟下升沿。

end if;end process;例:时钟上升沿动作的D触发器library ieee;use ieee.std_logic_1164.all;entity dff1 isport(clk, d: in std_logic;q: out std_logic);end dff1;architecture rtl of dff1 isbeginprocess(clk)beginif (clk'event and clk='1') thenq<=d;end if;end process;end rtl;时序逻辑电路的初始状态应由复位(或清零)信号来设置,根据复位信号对时序逻辑电路复位操作的不同,可分为同步复位和异步复位。

填空题1、所有的时序电路从理论上都可以表示为有限状态机。

2、数字系统一般可分为控制单元和数据通道,数据通道通常由组合逻辑电路构成,而控制单元通常由时序逻辑电路构成。

3、输出信号只和当前状态有关的状态机称为Moore型状态机。

4、在状态机的设计中,需要对状态机的各个状态设定唯一对应的状态编码。

5、状态机的每一个状态在实际电路中都是以一组触发器的当前状态组合来表示的。

6、直接状态编码有顺序编码、状态位直接输岀编码和一位有效的热码状态编码这三种常用的编码方式。

7、在状态机的正常运行中是不需要出现或者未被定义的状态,通常称为非法状态。

8、状态机设计的关键是如何把一个实际的时序逻辑关系抽象成一个时序逻辑函数。

综述题1、请简述使用VHDL语言设计有限状态机的步骤。

答案:根据系统功能描述,建立有限状态机状态转换图或状态转换表。

根据状态转换图采用VHDL语言定义可枚举的数据类型,枚举值即状态机的各个状态,并利用可枚举的数据类型定义状态变量。

建立状态机进程,并在进程中定义状态的转移。

2、请简述使用VHDL语言描述有限状态机的编码原则。

答案:两个状态变量,分别指定有限状态机的现态和次态。

有限状态机的状态变量要求是信号或者变量名,用于定义有限状态机的状态,也可以是设计者自己定义的枚举型变量。

但是,状态变量不能是接口或者端口。

系统至少有一个时钟信号。

每个状态应该有状态转移指定,而且有相应的输出信号指定。

系统有同步或者异步复位信号或者有隐含的复位状态。

3、在设计状态机的状态编码的时候,如果采用直接状态编码,有哪三种常用的编码方式??2 ?答案:顺序编码就是将有限状态机的状态用一个STD_LOGIC_VECTOR 型向量来表示,同样对于向量的位数 n ,要求2n>m (有效状态数),而且这些向量是顺序 递增的编码方式。

状态位直接输出编码可以缩短输出延时,其在对状态进行编码时,使其中某一位或某几位正好等于状态机处于每一个状态时的输出信号,这样将状态编码和输出信号有机的结合起来,使之既能区分信号,又能表示该状态下的输出信号。

第1章绪论1.1电子设计自动化1.2EDA技术,是以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统逻辑描述的主要表达方式,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具,通过有关的开发软件,自动完成用软件的方式设计的电子系统到硬件系统的逻辑编译、逻辑化简、逻辑分割、逻辑综合及优化、逻辑布局布线、逻辑仿真,直至完成对于特定目标芯片的适配编译、逻辑映射、编程下载等工作,最终形成集成电子系统或专用集成芯片的一门新技术。

1.31、用软件的方式设计硬件。

2、用软件方式设计的系统到硬件系统的转换是由有关的开发软件自动完成的。

3、设计过程中可用有关软件进行各种仿真。

4、系统可现场编程,在线升级。

5、整个系统可集成在一个芯片上,体积小、功耗低、可靠性高。

因此,EDA技术是现代电子设计的发展趋势。

1.4可编程逻辑器件(Programmable Logic Device,PLD)是一种由用户编程以实现某种逻辑功能的新型逻辑器件。

FPGA和CPLD分别是现场可编程门阵列和复杂可编程逻辑器件的简称。

1.51、自顶向下设计方法是一种模块化设计方法。

它对设计的描述从上到下,逐步由粗略到详细,符合常规的逻辑思维习惯。

由于高层设计与器件无关,设计易于在各种集成电路工艺或可编程器件之间移植。

2、适合多个设计者同时进行设计。

随着技术的不断进步,许多设计由一个设计者已无法完成,而必须经过多个设计者分工协作来完成。

在这种情况下,应用自顶向下的设计方法便于多个设计者同时进行设计,对设计任务进行合理分配,并用系统工程的方法对设计进行管理。

第2章可编程逻辑器件2.1按结构的复杂程度分类、按互连结构分类、按可编程特性分类、按可编程器件的编程元件分类2.2主动串行配置式、主动并行配置模式、外设配置模式、从动串行配置模式、菊花链配置模式2.31、编程单元。

查找表型FPGA的编程单元为SRAM结构,可以无限次编程,但它属于易失性元件,掉电后芯片内的信息会丢失;而CPLD则采用EEPROM编程单元,不仅可无限次编程,且掉电后片内的信息不会丢失。

V H D L习题解答(共15页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--VHDL 程序设计教程习题参考解答第一章习题参考答案1.什么是VHDLVHDL的实现有哪几种形态硬件描述语言(Hardware Description Language,HDL),顾名思义,是电子系统硬件行为描述、结构描述、数据流描述的语言。

VHDL语言的英文全名是Very High Speed Integrated Circuit Hardware Description Language,即超高速集成电路硬件描述语言。

2.简述VHDL的发展史。

1981年6月VHDL工作小组成立,提出了一个满足电子设计各种要求的能够作为工业标准的硬件描述语言。

1983年第三季度,由IBM公司、TI公司、Inter metrics公司签约,组成开发小组,工作任务是提出语言版本和开发软件环境。

1986年IEEE标准化组织开始工作,讨论VHDL语言标准,历时一年有余,于1987年12月通过标准审查,版本宣布实施,即IEEE STD 1076-1987。

1993年经过重新修订,发布版本,从而形成新的标准即IEEE STD 1076-1993。

2006年VHDL发布版本;2008年8月,VHDL 版本发布,解决了版本中发现的多个问题。

2009年1月,IEEE公布了VHDL 的标准版本,最新VHDL标准IEEE 1076-2008在2009年1月实施。

3. 详述VHDL设计IP模块的流程。

第1种设计形态,VHDL程序以IP模块的形态存在,VHDL-IP设计流程如图所示。

IP模块是与集成电路工艺无关的芯片设计方案,可以移植到不同的设计环境。

IP产品形态有规范,有IP包装规则和复用规则,是原生态的芯片硬件设计产品。

图 VHDL-IP设计流程4. 简答VHDL设计用FPGA实现的意义。

可编程器件FPGA具有容量大、密度高等特点,是科学实验、小批量生产、样机研制的载体。

第六章时序逻辑电路【题】 分析图时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方 程,画出电路的状态转换图,说明电路能否自启动。

电路能自启动。

状态转换图如图【题】分析图时序电路的逻辑功能,写出电路的驱动方程、 状态方程和输出方程,画出电路的状态转换图。

A 为输入逻辑变量。

【解】驱动 J i 二K i 二Q 3J 方程:J 2=K 3=Q1J 3= Q 1Q 2;K 3= Q3输出方程: Y Q 3将驱动方程带入 状态方程为:JK 触发器的特性方程后得到—n+1——Q iQ 3Q 1 Q 3Q 1Q 3 e Q i Q ; 1 Q 1Q 2 Q i Q 2Q 2Q i—n+1—Q 3 Q 3Q 2Q i图 A6.3Y图 P6.3图P6.5【解】D i AQ2驱动方程:一一D? AQ1Q2 A(Q i Q2)输出方程:Y AQ2Q1将驱动方程带入JK触发器的特性方程后得到状态方程为n+1Q i n 1 AQ2Q;+1 A(Q i Q2)电路的状态转换图如图图A6.5【题】分析图时序电路的逻辑功能,画出电路的状态转换图,检查电路能否自启动,说明电路能否自启动。

说明电路实现的功能。

A为输入变量。

输出方程:Y AQ 1Q 2 AQ 1Q 2将驱动方程带入JK 触发器的特性方程后得到状态方程为 :Q n+1 Q 1 Q 211 A Q 1 Q 2电路状态转换图如图。

A = 0时作二进制加法计数, A = 1时作二进制减法计数。

【题】 分析图时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方 程,画出电路的状态转换图,说明电路能否自启动。

【解】驱动方程J i K i 1J 2 K 2 AQ 1YCLK输出方程:Y Q o QQ z Q s将驱动方程带入JK触发器的特性方程后得到状态方程为Q o Q oQ1 Q0Q1 (Q2 Q3) Q0Q1Q;Q0Q2Q3 (Q0 Q1 )Q2Q3 Q0Q Q2Q3 Q0Q3 Y图P6.7【解】驱动方程J1 Q0 ? Q2Q3 ; K1 Q0Q0Q3;K2Q0Q1 Q0Q1Q2;KQ oCLK设初态QQQQ Q o=OOOO,由状态方程可得:状态转换表初态次态输出*** * * *Q3 Q Q Q Q Q Q Q Y0 0 0 0 10 0 1 10 0 0 1 0 0 0 0 00 0 10 0 0 0 1 00 0 11 0 0 10 00 10 0 0 0 11 00 10 1 0 10 0 00 110 0 10 1 00 111 0 110 010 0 0 0 111 010 0 1 10 0 0 010 10 0 10 1 010 11 10 10 0110 0 0 0 11 0110 1 110 0 01110 0 10 1 01111 1110 0状态转换图如图。

《EDA技术实用教程(第五版)》习题1 习题1-1EDA技术与ASIC设计和FPGA开发有什么关系?FPGA在ASIC设计中有什么用途?P3~4EDA技术与ASIC设计和FPGA开发有什么关系?答:利用EDA技术进行电子系统设计的最后目标是完成专用集成电路ASIC的设计和实现;FPGA和CPLD是实现这一途径的主流器件。

FPGA和CPLD的应用是EDA技术有机融合软硬件电子设计技术、SoC(片上系统)和ASIC设计,以及对自动设计与自动实现最典型的诠释。

FPGA在ASIC设计中有什么用途?答:FPGA和CPLD通常也被称为可编程专用IC,或可编程ASIC。

FPGA实现ASIC设计的现场可编程器件。

1-2 与软件描述语言相比,VHDL有什么特点? P4~6答:编译器将软件程序翻译成基于某种特定CPU的机器代码,这种代码仅限于这种CPU 而不能移植,并且机器代码不代表硬件结构,更不能改变CPU的硬件结构,只能被动地为其特定的硬件电路结构所利用。

综合器将VHDL程序转化的目标是底层的电路结构网表文件,这种满足VHDL设计程序功能描述的电路结构,不依赖于任何特定硬件环境;具有相对独立性。

综合器在将VHDL(硬件描述语言)表达的电路功能转化成具体的电路结构网表过程中,具有明显的能动性和创造性,它不是机械的一一对应式的“翻译”,而是根据设计库、工艺库以及预先设置的各类约束条件,选择最优的方式完成电路结构的设计。

l-3什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么?P6什么是综合? 答:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

有哪些类型?答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。

(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。

VHDL程序设计教程习题参考解答第1章思考题解答1.什么是VHDL?简述VHDL的发展史。

答:VHDL是美国国防部为电子项目设计承包商提供的,签定合同使用的,电子系统硬件描述语言。

1983年成立VHDL语言开发组,1987年推广实施,1993年扩充改版。

VHDL 是IEEE标准语言,广泛用于数字集成电路逻辑设计。

2.简述VHDL设计实体的结构。

答:实体由实体名、类型表、端口表、实体说明部分和实体语句部分组成。

根据IEEE标准,实体组织的一般格式为:ENTITY 实体名 IS[GENERIC(类型表);] --可选项[PORT(端口表);] --必需项实体说明部分; --可选项[BEGIN实体语句部分;]END [ENTITY] [实体名];3.分别用结构体的3种描述法设计一个4位计数器。

答:用行为描述方法设计一个4位计数器如下,其它描述方法,读者可自行设计。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;use ieee.std_logic_unsigned.all;ENTITY countA ISPORT (clk,clr,en:IN STD_LOGIC;Qa,qb,qc,qd:OUT STD_LOGIC);END countA;ARCHITECTURE example OF countA ISSIGNAL count_4:STD_LOGIC_vector (3 DOWNTO 0);BEGINQa <= count_4(0);Qb <= count_4(1);Qc <= count_4(2);Qd <= count_4(3);PROCESS (clk,clr)BEGINIF (clr = '1' ) THENCount_4 <= "0000";ELSIF (clk'EVENT AND clk = '1' ) THENIF (en = '1' ) THENIF (count_4 = "1111") THENcount_4 <= "0000";ELSEcount_4 <= count_4+ '1';END IF;END IF;END IF;END PROCESS;END example;第2章思考题解答1.什么叫对象?对象有哪几个类型?答:在VHDL语言中,凡是可以赋于一个值的客体叫对象(object)。

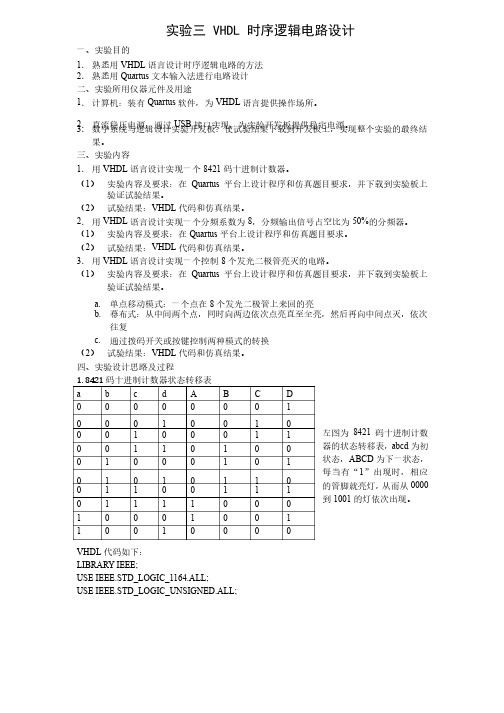

实验三实验三 VHDL VHDL VHDL 时序逻辑电路设计时序逻辑电路设计 一、实验目的一、实验目的1. 熟悉用VHDL 语言设计时序逻辑电路的方法语言设计时序逻辑电路的方法 2. 熟悉用Quartus 文本输入法进行电路设计文本输入法进行电路设计 二、实验所用仪器元件及用途二、实验所用仪器元件及用途 1. 计算机:装有Quartus 软件,为VHDL 语言提供操作场所。

语言提供操作场所。

2. 直流稳压电源:通过USB 接口实现,为实验开发板提供稳定电源。

接口实现,为实验开发板提供稳定电源。

3. 数字系统与逻辑设计实验开发板:使试验结果下载到开发板上,实现整个实验的最终结果。

果。

三、实验内容三、实验内容 1. 用VHDL 语言设计实现一个8421码十进制计数器。

码十进制计数器。

(1) 实验内容及要求:在Quartus 平台上设计程序和仿真题目要求,并下载到实验板上验证试验结果。

验证试验结果。

(2) 试验结果:VHDL 代码和仿真结果。

代码和仿真结果。

2. 用VHDL 语言设计实现一个分频系数为8,分频输出信号占空比为50%的分频器。

的分频器。

(1) 实验内容及要求:在Quartus 平台上设计程序和仿真题目要求。

平台上设计程序和仿真题目要求。

(2) 试验结果:VHDL 代码和仿真结果。

代码和仿真结果。

3. 用VHDL 语言设计实现一个控制8个发光二极管亮灭的电路。

个发光二极管亮灭的电路。

(1) 实验内容及要求:在Quartus 平台上设计程序和仿真题目要求,并下载到实验板上验证试验结果。

验证试验结果。

a. 单点移动模式:一个点在8个发光二极管上来回的亮个发光二极管上来回的亮b. 幕布式:从中间两个点,同时向两边依次点亮直至全亮,然后再向中间点灭,依次往复往复c. 通过拨码开关或按键控制两种模式的转换通过拨码开关或按键控制两种模式的转换 (2) 试验结果:VHDL 代码和仿真结果。

填空题1、而时序电路的输出不仅仅和电路当前输入相关,还和电路过去输入相关。

2、由于时序电路的输出和其过去的状态也相关,所以时序电路中必然有记忆元件,用于记忆和过去输入信号相关的信息。

3、时序电路可以分为同步时序电路和异步时序电路两大类。

4、任何时序逻辑电路都是以时钟为驱动信号的。

5、时序逻辑电路的时钟信号边沿分为上升沿和下降沿。

6、显式表示时钟敏感信号是指时钟信号显式地出现在进程语句PROCESS 后面的敏感信号列表中。

7、在隐式表示时钟敏感信号的时候,使用WAIT语句来控制进程的执行。

8、时钟信号是一个系统稳定工作的关键,它是一个系统的最小的时间刻度。

9、根据复位信号对时序逻辑电路的复位方式的不同,可以分为同步复位方式和异步复位方式。

10、在VHDL程序中描述时序电路的同步复位时,会采用IF 语句来描述复位条件。

11、构成时序逻辑电路的基本单元是触发器。

12、移位寄存器从数据输入方式上可以分为并行输入和串行输入两种。

综述题1、请简述同步时序电路和异步时序电路的区别。

答案:●同步时序电路:其所有电路都是用一个公共的时钟信号,电路中所有的记忆都受到这个时钟信号的同一控制,只有在该信号来到的时候记忆元件的状态发生变化,从而使时序电路的输入发生变化;而且每次时钟信号到来的时候忆元件的状态和电路的输出状态才会发生改变。

●异步时序电路:其电路中没有一个统一的时钟信号,各个记忆元件也不受到个时钟控制,电路状态的改变是因为输入信号引起的。

记2、请简述时序逻辑电路在电路结构上的两个显著特点。

●时序逻辑电路通常包含组合电路和存储电路两个组成部分,而存储电路是必少的。

●时序逻辑电路的存储电路的输出状态必须反馈到电路的输入端,与输入信号一起共同决定电路的输出。

?2 ?3 、请画出时序逻辑电路中时钟上升沿和下降沿的波形并且写出其在VHDL语言中的描述方法。

答案:上升沿:VHDL语言描述时钟的上升沿clk= ‘1'AND clk'LAST_V ALUE=‘0' AND clk'EVENclk =‘11电平上升沿clk0电平clk'LAST_V ALUE=‘clk'EVENT下降沿:VHDL语言描述时钟的下降沿clk= ‘0'AND clk'LAST_V ALUE=‘1' AND clk 'EVENTclk'LAST_V ALUE =‘1'1电平下降沿0电平clkclk =‘0' clk'EVENT4、在使用时钟作为敏感信号的时候,需要注意哪三点?答案:●无论是用PROCESS 语句还是WAIT语句,在对时钟边沿说明时,一定要说明是上升沿还是下降沿(前沿还是后沿),仅仅说明边沿是不够的。

填空题1、而时序电路的输出不仅仅和电路当前输入相关,还和电路过去输入相关。

2、由于时序电路的输出和其过去的状态也相关,所以时序电路中必然有记忆元件,用于记忆和过去输入信号相关的信息。

3、时序电路可以分为同步时序电路和异步时序电路两大类。

4、任何时序逻辑电路都是以时钟为驱动信号的。

5、时序逻辑电路的时钟信号边沿分为上升沿和下降沿。

6、显式表示时钟敏感信号是指时钟信号显式地出现在进程语句PROCESS后面的敏感信号列表中。

7、在隐式表示时钟敏感信号的时候,使用WAIT语句来控制进程的执行。

8、时钟信号是一个系统稳定工作的关键,它是一个系统的最小的时间刻度。

9、根据复位信号对时序逻辑电路的复位方式的不同,可以分为同步复位方式和异步复位方式。

10、在VHDL程序中描述时序电路的同步复位时,会采用IF语句来描述复位条件。

11、构成时序逻辑电路的基本单元是触发器。

12、移位寄存器从数据输入方式上可以分为并行输入和串行输入两种。

综述题1、请简述同步时序电路和异步时序电路的区别。

答案:●同步时序电路:其所有电路都是用一个公共的时钟信号,电路中所有的记忆元件都受到这个时钟信号的同一控制,只有在该信号来到的时候记忆元件的状态才能发生变化,从而使时序电路的输入发生变化;而且每次时钟信号到来的时候,记忆元件的状态和电路的输出状态才会发生改变。

●异步时序电路:其电路中没有一个统一的时钟信号,各个记忆元件也不受到同一个时钟控制,电路状态的改变是因为输入信号引起的。

2、请简述时序逻辑电路在电路结构上的两个显著特点。

●时序逻辑电路通常包含组合电路和存储电路两个组成部分,而存储电路是必不可少的。

●时序逻辑电路的存储电路的输出状态必须反馈到电路的输入端,与输入信号一起共同决定电路的输出。

•2 •3、请画出时序逻辑电路中时钟上升沿和下降沿的波形并且写出其在VHDL语言中的描述方法。

答案:上升沿:VHDL语言描述时钟的上升沿clk=‘1’AND clk’LAST_VALUE=‘0’ AND clk’EVENT下降沿:VHDL语言描述时钟的下降沿clk=‘0’AND clk’LAST_VALUE=‘1’ AND clk’EVENTclk'EVENT4、在使用时钟作为敏感信号的时候,需要注意哪三点?答案:●无论是用PROCESS语句还是WAIT语句,在对时钟边沿说明时,一定要说明是上升沿还是下降沿(前沿还是后沿),仅仅说明边沿是不够的。

●当时钟信号作为进程的敏感信号时,在敏感信号列表中不能同时出现多个时钟信号,但是其他信号量可以和时钟信号并列地放在敏感信号列表中。

●采用隐式表示时钟信号时,由于它是进程的同步点,它要么放在进程的最前面,要么放在进程的最后面。

5、请简述同步计数器和异步计数器的差别。

答案:●异步计数器:高触发位的时钟信号往往是由低一位触发器的输出提供的,高触发器的翻转有待低一位触发器的翻转之后才能进行,其缺点是计数速度比较慢,而且位数越多,计数速度越慢。

●同步计数器:各个触发器的时钟脉冲是由同一个脉冲供给的,各个触发器是同时• 3 •翻转的,其最高工作频率只和一个触发器的始终到输出的传输延迟以及有关控制门的传输延迟之和有关,所以其工作频率比异步计数器高。

实验题实验【一】8位寄存器的设计实验目的:学习8位寄存器的设计原理和VHDL实现方法,熟悉VHDL时序逻辑电路的设计流程、仿真和硬件测试。

实验任务:参考8.5.1中关于寄存器的介绍和例8.10的6位寄存器/D触发器设计方法,使用VHDL语言实现一个8位带清除端的寄存器。

答案:library IEEE;use IEEE.Std_logic_1164.all; --库文件entity VHDLREG is --实体port(D : in std_logic_vector(8 downto 0);Q : out std_logic_vector(8 downto 0);CLRBAR, CLK : in std_logic); --引脚定义,带时钟和清除端end VHDLREG;architecture RT of VHDLREG isbeginQ <= (others => '0') when (CLRBAR = '0') --清除信号有效else D when rising_edge(CLK) --在时钟激励下工作else unaffected;end RT;实验【二】十进制计数器的设计实验目的:学习计数器的设计原理和VHDL实现方法,熟悉VHDL时序逻辑电路的设计流程、仿真和硬件测试。

实验任务:参考8.7.1中关于计数器的介绍和例8.15的十六进制计数器设计方法,使用VHDL语言实现一个十进制计数器。

答案:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; --库文件ENTITY VHDLCOUNTER IS --实体PORT(CLK: IN BIT;OE: OUT BIT;•4 •Y: OUT INTEGER RANGE 0 to 9); --16位输出END VHDLCOUNTER;ARCHITECTURE RT OF VHDLCOUNTER ISSIGNAL Q: INTEGER RANGE 0 TO 15;BEGINP1: PROCESS(clk) --时钟作为敏感信号beginif(CLK' EVENT AND CLK = '1') THEN --时钟上升沿Q <= Q+1;END IF;if Q = 9 THEN --如果计数器到15则翻转OE <= '0';ELSE --计数输出OE <= '1';END IF;Y <= Q;END PROCESS P1;END RT;实验【三】正弦波发生器的设计实验目的:学习计数器的设计原理和VHDL实现方法,熟悉VHDL时序逻辑电路的设计流程、仿真和硬件测试。

实验任务:用VHDL语言设计一个正弦波发生器。

答案:正弦波发生器的输出其实就是一个个点对应的二进制编码,将这些点在时钟激励下输出,通过数字-模拟转化器即可得到对应的正弦波形,通常来说点越多,所描述的正弦波形也就越准确。

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity sin is --实体port(clk,clr:in std_logic;d:out integer range 0 to 255); --定义一个输出end sin;architecture RL of sin is --结构体beginprocess(clk,clr)variable tmp:integer range 0 to 63;beginif clr='0' then d<=0;elsif clk'event and clk='1' then• 5 •if tmp=63 thentmp:=0;elsetmp:=tmp+1; --将循环计数器增加end if;case tmp is --根据循环计数器的值使用CASE控制输出when 00=>d<=255; when 01=>d<=254; when 02=>d<=252;when 03=>d<=249; when 04=>d<=245; when 05=>d<=239;when 06=>d<=233; when 07=>d<=225; when 08=>d<=217;when 09=>d<=207; when 10=>d<=197; when 11=>d<=186;when 12=>d<=174; when 13=>d<=162; when 14=>d<=150;when 15=>d<=137; when 16=>d<=124; when 17=>d<=112;when 18=>d<=99; when 19=>d<=87; when 20=>d<=75;when 21=>d<=64; when 22=>d<=53; when 23=>d<=43;when 24=>d<=34; when 25=>d<=26; when 26=>d<=19;when 27=>d<=13; when 28=>d<=8; when 29=>d<=4;when 30=>d<=1; when 31=>d<=0; when 32=>d<=0;when 33=>d<=1; when 34=>d<=4; when 35=>d<=8;when 36=>d<=13; when 37=>d<=19; when 38=>d<=26;when 39=>d<=34; when 40=>d<=43; when 41=>d<=53;when 42=>d<=64; when 43=>d<=75; when 44=>d<=87;when 45=>d<=99; when 46=>d<=112; when 47=>d<=124;when 48=>d<=137; when 49=>d<=150; when 50=>d<=162;when 51=>d<=174; when 52=>d<=186; when 53=>d<=197;when 54=>d<=207; when 55=>d<=217; when 56=>d<=225;when 57=>d<=233; when 58=>d<=239; when 59=>d<=245;when 60=>d<=249; when 61=>d<=252; when 62=>d<=254;when 63=>d<=255;when others=>null;end case;end if;end process;end RL;实验【四】发光二极管控制器的设计实验目的:学习计数器的设计原理和VHDL实现方法,熟悉VHDL时序逻辑电路的设计流程、仿真和硬件测试。