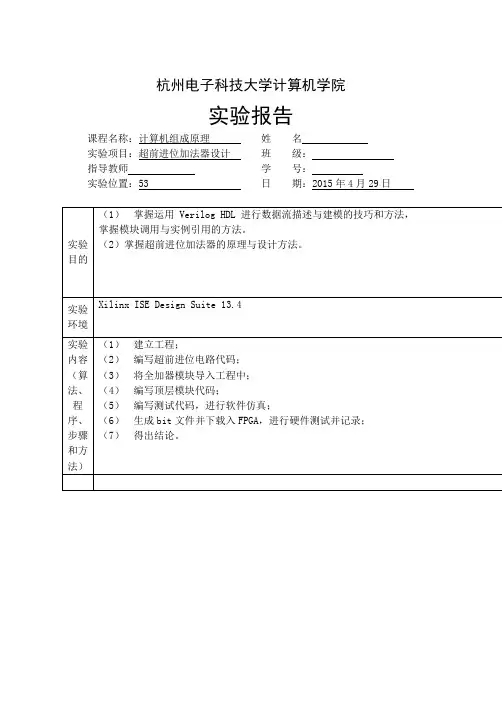

试验心得与小结

本次试验的超前进位加法器,更好的体现了,我们对于效率地的要求,对于以有些的地方我们可以采取一些手段改进自身的不足,超前进位的思想就是率先计算出我们的需要的进位

的值,然后在处理,解决了不同步的问题,真的很值得我们思考,这种类似的问题

指导教师

评议

成绩评定:指导教师签名:

实验环境

Xilinx ISE Design Suite 13.4

实验内容(算法、程序、步骤和方法)

(1)建立工程;

(2)编写超前进位电路代码;

(3)将全加器模块导入工程中;

(4)编写顶层模块代码;

(5)编写测试代码,进行软件仿真;

(6)生成bit文件并下载入FPGA,进行硬件测试并记录;

(7)得出结论。

O1(P[1],A[1],B[1]),

O2(P[2],A[2],B[2]),

O3(P[3],A[3],B[3]);

MainSection M(Co,G,P,Ci);

Add FA0(A[0],B[0],Ci,F[0]),

FA1(A[1],B[1],Co[1],F[1]),

FA2(A[2],B[2],Co[2],F[2]),

FA3(A[3],B[3],Co[3],F[3]);

Endmodule

4、测试代码:

module test;

// Inputs

reg [3:0] A;

reg [3:0] B;

reg Ci;

// Outputs

wire [3:0] F;

wire [4:1]Co;

// Instantiate the Unit Under Test (UUT)

assign C[2]=G[1]|(P[1]&G[0])|(P[1]&P[0]&Ci);