21.JK触发器练习

- 格式:doc

- 大小:23.50 KB

- 文档页数:2

电子技术基础练习题库及答案一、单选题(共70题,每题1分,共70分)1、本征半导体温度升高后,两种载流子浓度仍然相等。

A、✔B、×正确答案:A2、单相半波整流电路,负载电阻RL=750W,变压器次级电压有效值,U2=20V,则输出电压平均值U0为。

A、18VB、20VC、9V正确答案:C3、PN结两端加正向电压时,那么参加导电的是()A、少数载流子。

B、既有多数载流子又有少数载流子。

C、多数载流子。

正确答案:C4、符号IB表示三极管基极电流的()A、直流分量。

B、交流分量。

C、直流分量和交流分量之和。

正确答案:A5、在晶体三极管放大电路中,当输入电流一定时,若静态工作点设置太低,将产生()A、截止失真。

B、放大失真。

C、饱和失真。

正确答案:A6、三端集成稳压器cw7812的输出电压是()A、5VB、9VC、12V正确答案:C7、测得在放大状态的三极管的三个管角电位分别是15.5v,6v,6.7v,则该三极管类型是()A、npn型硅管。

B、npn型锗管C、PnP型锗管正确答案:A8、稳压管的稳压区是指其工作在()的区域。

A、正向导通。

B、反向击穿。

C、反向截止。

正确答案:B9、在由运放组成的电路中运放工作在非线性状态的电路是。

()A、差值放大器。

B、反相放大器。

C、电压比较器。

正确答案:C10、组合逻辑电路的输出与电路的原状态()A、无关B、有关C、不一定正确答案:B11、组合电路的特点是任意时刻的输出与电路的原状态有关。

A、×B、✔正确答案:A12、下列三种电路中,输入电阻最大的电路是()A、共集放大电路。

B、共射放大电路。

C、共基放大电路。

正确答案:A13、最常用的显示器件是()数码显示器。

A、七段B、五段C、九段正确答案:A14、逻辑代数运算于普通代数运算结果()A、相同B、不想同C、有的相同,有的不相同。

正确答案:C15、非门的逻辑功能是()A、有0出0。

全1出1。

B、有1出1。

数电触发器习题触发器是数字电路中常用的重要元件,用于存储和处理信息。

在数字电路的设计与实现中,经常需要使用触发器来完成不同的任务。

以下是一些关于数电触发器的习题,旨在帮助读者加深对触发器的理解和应用。

问题一:D触发器的真值表和特性方程D触发器是最简单的触发器之一,其输入信号为D(数据输入)和Clk(时钟输入),输出信号为Q(输出)和Q’(输出的补)。

请完成以下任务:1.给出D触发器的真值表。

D Clk Q Q’0 0 Q(n) Q’(n)0 1 0 11 0 Q(n) Q’(n)1 1 1 02.根据真值表,写出D触发器的特性方程。

Q(n+1) = D + Q(n) * Clk’Q’(n+1) = D’ + Q’ * Clk’问题二:JK触发器的真值表和特性方程JK触发器是一种可以实现各种功能的多功能触发器,其输入信号为J(置位输入)、K(复位输入)和Clk(时钟输入),输出信号为Q(输出)和Q’(输出的补)。

请完成以下任务:1.给出JK触发器的真值表。

J K Clk Q Q’0 0 0 Q(n) Q’(n)0 0 1 Q(n) Q’(n)0 1 0 0 10 1 1 0 11 0 0 1 01 0 1 1 01 1 0 \* \*1 1 1 \* \*注:*代表不确定状态。

2.根据真值表,写出JK触发器的特性方程。

Q(n+1) = (J * Q’(n)’)’ * (K’ * Q(n))’Q’(n+1) = (J’ * Q(n))’ * (K * Q’(n)’)’问题三:T触发器的状态转换图和特性方程T触发器是一种特殊的JK触发器,其输入信号为T(切换输入)和Clk(时钟输入),输出信号为Q(输出)和Q’(输出的补)。

请完成以下任务:1.绘制T触发器的状态转换图。

T触发器状态转换图注:图中S0、S1、S2、S3分别表示T触发器的四种状态。

2.根据状态转换图,写出T触发器的特性方程。

Q(n+1) = T * Q’(n)’ + T’ * Q(n)Q’(n+1) = T’ * Q’(n)’ + T * Q(n)问题四:D触发器与JK触发器的状态表达式转换已知D触发器和JK触发器的状态表达式分别为:D触发器:Q(n+1) = D + Q(n) * Clk’JK触发器:Q(n+1) = (J * Q’(n)’)’ * (K’ *Q(n))’请完成以下任务:将D触发器的状态表达式转换为JK触发器的状态表达式。

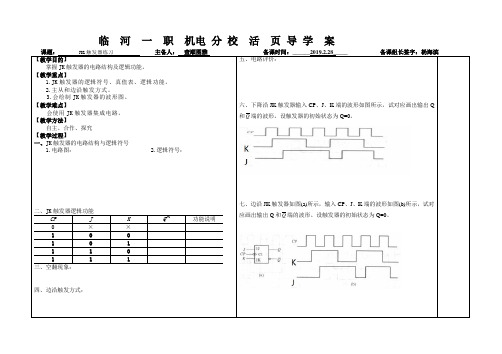

临河一职机电分校活页导学案课题:JK触发器练习主备人:查顺图雅备课时间:______2019.2.28_____ 备课组长签字:杨海滨【教学目的】掌握JK触发器的电路结构及逻辑功能。

【教学重点】1.JK触发器的逻辑符号、真值表、逻辑功能。

2.主从和边沿触发方式。

3.会绘制JK触发器的波形图。

【教学难点】会使用JK触发器集成电路。

【教学方法】自主、合作、探究【教学过程】一、JK触发器的电路结构与逻辑符号1.电路图:2.逻辑符号:二、JK触发器逻辑功能CP J K Q n+1功能说明0 ××1 0 01 0 11 1 01 1 1三、空翻现象:四、边沿触发方式:五、电路评价:六、下降沿JK触发器输入CP、J、K端的波形如图所示,试对应画出输出Q 和Q端的波形。

设触发器的初始状态为Q=0。

七、边沿JK触发器如图(a)所示,输入CP、J、K端的波形如图(b)所示,试对应画出输出Q和Q端的波形。

设触发器的初始状态为Q=0。

八、下降沿JK触发器输入CP、J、K端的波形如图所示,试对应画出输出Q和Q端的波形。

设触发器的初始状态为Q=0。

九、下降沿JK触发器输入CP、J、K端的波形如图所示,试对应画出输出Q和Q端的波形。

设触发器的初始状态为Q=0。

十、下降沿JK触发器输入CP、J、K端的波形如图所示,试对应画出输出Q 和Q端的波形。

设触发器的初始状态为Q=0。

十一、下降沿JK触发器输入CP、J、K端的波形如图所示,试对应画出输出Q和Q端的波形。

设触发器的初始状态为Q=0。

一、判断题1、用逻辑门构成的各种触发器均属于电平异步时序逻辑电路()2、RS、JK、D和T四种触发器中,唯有RS触发器存在输入信号的约束条件()3、与非门的输入端加有低电平时,其输出端恒为高电平。

()4、数字电路可以分为组合逻辑电路和时序逻辑电路两大类。

()5、时序逻辑电路中存在反馈,其输出不仅取决于当时的输入,还与电路的上一个状态有关。

()6、组合逻辑电路的输出只与当时的输入有关,与电路的上一个状态无关,没有记忆功能。

()7、触发器是时序逻辑电路的基本单元。

()8、时序逻辑电路由组合逻辑电路和存储电路构成。

()9、触发器的反转条件是由触发输入与时钟脉冲共同决定的。

()10、组合逻辑电路任何时刻的输出不仅与该时刻的输入状态有关,还与先前的输出状态有关。

()11、译码器、比较器属于组合逻辑电路。

12、数字电路可分为组合逻辑电路和时序逻辑电路。

13、全加器是实现两个1位二进制数相加并考虑低位进位的逻辑电路。

14、实现同一逻辑功能的逻辑电路可以不同15、译码是编码的逆过程。

16、寻找组合逻辑电路输入输出关系表达式的过程和方法,是组合逻辑电路的设计过程.17、公式化简法有时不容易判断结果是否最简.18、实现同一逻辑功能的电路是唯一的.19、加法器可以有并行进位加法器.20、七段显示译码器有共阳极和共阴极显示器两种接法.21、一个班级有80个学生,现采用二进制编码器对每位学生进行编码,则编码器输出至少5位二进制数才能满足要求22、高电平有效的显示译码器可驱动共阴极接法的数码管23、低电平有效的显示译码器可驱动共阳极接法的数码管24、高电平有效的显示译码器可驱动共阳极接法的数码管25、低电平有效的显示译码器可驱动共阴极接法的数码管26、同一CP控制各触发器的计数器称为异步计数器()27、各触发器的信号来源不同的计数器称为同步计数器()28、1个触发器可以存放2个二进制数()29、D触发器只有时钟脉冲上升沿有效的品种。

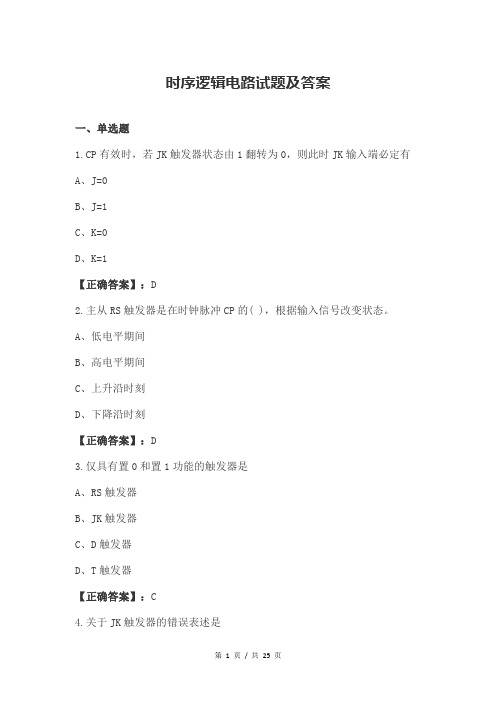

时序逻辑电路试题及答案一、单选题1.CP有效时,若JK触发器状态由1翻转为0,则此时JK输入端必定有A、J=0B、J=1C、K=0D、K=1【正确答案】:D2.主从RS触发器是在时钟脉冲CP的( ),根据输入信号改变状态。

A、低电平期间B、高电平期间C、上升沿时刻D、下降沿时刻【正确答案】:D3.仅具有置0和置1功能的触发器是A、RS触发器B、JK触发器C、D触发器D、T触发器【正确答案】:C4.关于JK触发器的错误表述是A、对于输入信号没有制约条件B、不允许JK同时为1C、允许JK同时为1D、允许JK同时为0【正确答案】:B5.D触发器当D=Q时,实现的逻辑功能是A、置0B、置1C、保持D、翻转【正确答案】:C6.JK触发器有( )触发信号输入端。

A、一个B、二个C、三个D、四个【正确答案】:B7.下列哪项表示基本RS触发器的符号A、B、C、D、【正确答案】:A8.D触发器在CP脉冲有效的情况下能实现的功能是A、置0和置1B、置1和保持C、置0和保持D、保持和翻转【正确答案】:A9.基本RS触发器是( )。

A、组合逻辑电路B、单稳态触发器C、双稳态触发器D、无稳态触发器10.双D集成触发器CD4013的时钟脉冲CP的引脚是A、14脚B、7脚C、3脚与11脚D、5脚与11脚【正确答案】:C11.与非型同步RS触发器,CP=1期间,( ),触发器维持原态。

A、R=0,S=0B、R=0,S=1C、R=1,S=0D、R=1,S=1【正确答案】:A12.主从JK触发器的初态为0,JK=01时,经过2021个触发脉冲后,其状态变化及输出状态为A、一直为0B、由0变为1,然后一直为1C、在01间翻转,最后为1D、在01间翻转,最后为013.对双JK集成触发器74LS112引脚功能叙述错误的是A、16脚是VccB、8脚是GNDC、1脚是CP1D、16脚是GND【正确答案】:D14.D触发器用作计数型触发器时,输入端D的正确接法是A、D=0B、D=1C、D=D=Q【正确答案】:C15.JK触发器中,当JK取值相同时,则Q等于A、J⊕QB、QC、1D、016.在RS触发器的逻辑符号中表示A、低电平时置1B、高电平时置1C、低电平时置0D、高电平时置0【正确答案】:C17.JK触发器,若J=,K= Q,则可实现的逻辑功能是A、置0B、置1C、保持D、翻转【正确答案】:D18.D触发器有( )触发信号输入端。

§8 JK 触发器、D 触发器和T 触发器一、JK 触发器JK 触发器的符号如图所示,CP 输入端有小圆圈,表示触发器改变状态的时间是CP 脉冲的下降沿(由1变0),称“下降沿触发”或“负边沿触发”;没有的表示“上升沿触发”。

JK 触发器的逻辑功能(真值表)如下:功能描述:“00不翻11翻,互补输入, J 为打入端”。

特征方程: Q n+1=n n Q K Q J例:下降沿触发的JK 触发器,已知CP 、J 、K 的波形,画Q 的波形。

在各类集成触发器中,JK 触发器的功能最为齐全。

在实际应用J K Q n Q n+1 功能描述 0 0 0 0 保持0 0 1 1 0 1 0 0 置0 0 1 1 0 1 0 0 1 置1 1 0 1 1 1 1 0 1 翻转 1 1 1CP J K Q123456J Cp KQ QRJ Cp K SQ Q带异步清零、置1功能、 上升沿触发的的JK 触发器CLK 1J 14K3Q13Q12T下降沿触发的JK 触发器中,它不仅有很强的通用性,而且能灵活地转换成其他类型的触发器。

二、D 触发器 1.电路组成:用JK 触发器能很方便地构成D 触发器:a )用JK 触发器构成D 触发器 b) D 触发器的逻辑符号2.逻辑功能: 1) 真值表:描述:每来一个CP 脉冲,就把D 端的数据送到Q 端。

因此D 触发器又称“数据锁存器”,D (Data )端是数据输入端。

2) 特征方程:Q n+1=D例题:下降沿触发的D 触发器,初态为0态。

根据图示的CP 和D 的波形,画Q 和Q 反的波形。

QQCP D Q Q三、T 触发器 1.电路组成把JK 触发器的两个输入端J 、K 连在一起,作为一个输入端T ,就构成T 触发器。

如下图:2.逻辑功能:因为T=J=K ,所以当T=0,CP 脉冲来后触发器维持原状太不变;当T=1,每来一个CP 脉冲触发器状态翻转一次。

特征方程:Q n+1=n n n QT Q T Q T ⊕=+ 例:根据T 触发器的CP 、T信号画Q 和Q 反:常用集成触发器介绍74LS74 (Dual D-type FF (pre, clr)) 74LS112(Dual JK FF(-edge, pre, clr))CP T Q Q51234Q Q74LS379 (Quad D-type FF w/en)CC4027(CD4027)(Dual JK FF (+edge, pre, clr))触发器应用举例(演示)1.触发器构成的数据锁存器2.触发器构成的移位寄存器 3 .触发器构成的计数器。

触发器练习题一、填空题1、触发器具有 个稳定状态,在输入信号消失后,它能保持 。

2、在基本RS 触发器中,输入端D R 或D R 能使触发器处于 状态,输入端D S 或D S 能使触发器处于 状态。

3、同步RS 触发器状态的改变是与 信号同步的。

4、在CP 脉冲和输入信号作用下,JK 触发器能够具有 、 、 、和 的逻辑功能。

5、对于JK 触发器,当CP 脉冲有效期间,若J=K=0时,触发器状态 ;若K J =时,触发器 或 ;若J=K=1时,触发器状态 。

6、与主从触发器相比, 触发器的抗干扰能力较强。

7、对于JK 触发器,若J=K ,则可完成 触发器的逻辑功能。

8、对于JK 触发器,若K J =,则可完成 触发器的逻辑功能。

二、判断题1、触发器有两个稳定状态,一个是现态,一个是次态。

( )2、触发器有两个稳定状态,在外界输入信号的作用下,可以从一个稳定状态转变为另一个稳定状态。

( )4、同步D 触发器的Q 端和D 端的状态在任何时刻都是相同的。

( )5、同一逻辑功能的触发器,其电路结构一定相同。

( )6、仅具有反正功能的触发器是T 触发器。

( )三、选择题1、对于触发器和组合逻辑电路,以下( )的说法是正确的。

A 、两者都有记忆能力B 、两者都无记忆能力C 、只有组合逻辑电路有记忆能力D 、只有触发器有记忆能力2、对于JK 触发器,输入J=0、K=1,CP 脉冲作用后,触发器的1+n Q 应为( )。

A 、0B 、1C 、可能是0,也可能是1D 、与n Q 有关3、JK 触发器在CP 脉冲作用下,若使n n Q Q =+1,则输入信号应为( )。

A 、1==K JB 、Q K Q J ==,C 、Q K Q J ==,D 、0==K J4、具有“置0” “置1” “保持” “翻转”功能的触发器叫( )。

A 、JK 触发器B 、基本RS 触发器C 、同步D 触发器 D 、同步RS 触发器5、边沿控制触发的触发器的触发方式为( )。

1.一位十六进制数可以用 C 位二进制数来表示。

2.十进制数25用8421BCD 码表示为 B 。

3. 以下表达式中符合逻辑运算法则的是 D 。

A . 1B . 2C . 4D . 16 A .10 101 B .0010 0101 C .100101 D .10101 A .C ·C =C 2 B .1+1=10 C .0<1 D .A +1=14. 当逻辑函数有n 个变量时,共有 D 个变量取值组合? 5.A+BC= C 。

6.在何种输入情况下,“与非”运算的结果是逻辑0。

DA. nB. 2nC. n 2D. 2n A .A +B B.A +C C.(A +B )(A +C ) D.B +C A .全部输入是0 B.任一输入是0 C.仅一输入是0 D.全部输入是17. 以下电路中可以实现“线与”功能的有 C 。

8.以下电路中常用于总线应用的有 A 。

A .与非门B .三态输出门C .集电极开路门D . C M O S 与非门 A .T S L 门 B .O C 门 C . 漏极开路门D .C M O S 与非门9.若在编码器中有50个编码对象,则要求输出二进制代码位数为 B 位。

10.一个16选一的数据选择器,其地址输入(选择控制输入)端有 C 个。

A .5B .6C .10D .50 A .1 B .2 C .4 D .1611.四选一数据选择器的数据输出Y 与数据输入X i 和地址码A i 之间的逻辑表达式为Y = A 。

A .3X A A X A A X A A X A A 01201101001+++B .001X A AC .101X A AD .3X A A 0112.一个8选一数据选择器的数据输入端有 E 个。

A .1B .2C .3D .4E .813.在下列逻辑电路中,不是组合逻辑电路的有 D 。

A .译码器B .编码器C .全加器D .寄存器14.八路数据分配器,其地址输入端有 c 个。

第21章 触发器和时序逻辑电路一、填空题1、JK 触发器的特性方程为:=+1n Q ________________________。

2、时钟触发器按照结构和触发方式不同可分为:_________、__________、_________和主从式触发器四种。

3、T 触发器的特性方程为=+1n Q _________________。

4、4个触发器组成的寄存器可以存储__________位二进制数。

5、将JK 触发器的J 端连在Q 端上,K 端接高电平。

假设)(t Q =0,则经过50个CP 脉冲作用后,它的状态)50(+t Q =_____。

6、对于时钟RS 触发器,若要求其输出“0”状态保持不变,则输入的RS 信号应为________。

7、组成计数器的各个触发器的状态能在时钟信号到达时同时翻转,它属于__________ 计数器。

(填“同步”或“异步”)8、当JK 触发器的输入J=1,K=0时,触发器的次态Q n+1=____________。

9、若要构成十二进制计数器,最少要用__________个触发器。

10、构成一个模6的同步计数器最少要________个触发器。

11、一个 JK 触发器有____个稳态,它可存储____位二进制数。

二、选择题1、下列触发器中有空翻现象的是_________。

A 、同步式触发器B 、维持阻塞式触发器C 、主从式触发器D 、边沿式触发器 2、在以下各种电路中,属于时序电路的有__________。

A 、译码器B 、计数器C 、数据选择器D 、编码器 3、JK 触发器当J=K=1时,Q n+1=__________。

A 、0B 、1C 、Q nD 、 Q n4、下列触发器中逻辑功能最多是_______。

A 、J-K 触发器B 、D 触发器C 、T 触发器D 、T ′触发器 5、在CP 有效的情况下,当输入端D=0时,则D 触发器的输出端=+1n Q ________。

一、判断题

1.主从型JK触发器的从触发器开启时刻在CP下降沿到来时。

()

2.将JK触发器的J、K端连接在一起作为输入端,就构成D触发器。

()

3.主从JK触发器能够避免触发器空翻现象。

()

4.当J=0,K=1时,Q n+1=JQ n+KQ n,置“0”。

()

5.时钟脉冲为下降沿触发。

()

6.JK触发器处于翻转时输入信号的条件是J=1,K=0。

()

7.JK触发器在CP作用下,要使Q n+1=Q n,则输入信号必为J=K=0。

()

二、选择题

1.JK触发器在J、K端同时输入高电平,则处于()。

A.保持

B.置0

C.翻转

D.置1

2.欲使JK触发器按Q n+1=Q n工作,可使JK触发器的输入端()。

A.J=K=0

B.J=Q ,K=Q

C.J=1 ,K=Q

D.J=Q ,K=0

3.下列触发器中,没有约束条件的是()。

A.基本RS触发器

B.主从JK触发器

C.钟控RS触发器

D.以上都不是

4.对于JK触发器,若J=K,则可完成()触发器的逻辑功能。

A.RS

B.D

C.T

D.T′

5.触发器与组合逻辑门电路比较()。

A.两者都有记忆能力

B.只有组合逻辑门电路有记忆能力

C.只有触发器有记忆能力

D.都没有记忆能力

6.一个触发器可记录一位二进制代码,它有()个稳态。

A.0

B.1

C.2

D.3

7.J=K=1时,边沿JK触发器的时钟输入频率为120Hz。

Q输出为()。

A.保持为高电平

B.保持为低电平

C.频率为60Hz波形

D.频率为240Hz波形

三、填空题

1.在时钟脉冲控制下,根据输入信号及J、K的不同情况,能够具有功能的电路,称为JK触发器。

2.触发器是一种。

3.当现态Q n=0时,具备时钟条件后JK触发器的次态为Q n+1=。

4.通常把一个CP脉冲引起触发器多次翻转的现象称为空翻,有这种现象的触发器是。

5.把JK触发器的两个输入端连在一起就构成了T触发器,T触发器具有的逻辑功能是。

6.触发器有互非的输出端。

7.组合逻辑电路的基本单元是。

8.主从JK触发器是在采样。

9.主从JK触发器是在输出。