附录2常用数字集成电路引脚图

- 格式:doc

- 大小:3.20 MB

- 文档页数:4

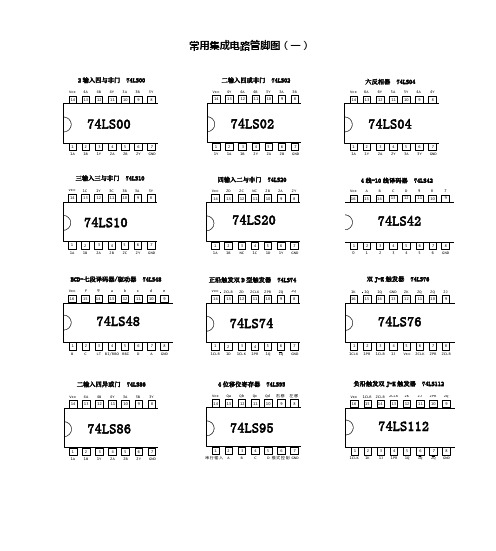

123456789101112131474LS001A1B1Y2A2B 2YGND3Y 3A 4Y 4B 4A Vcc 3B 2输入四与非门 74LS00123456789101112131474LS021A1B 1Y 2A2B2YGND3Y 3A 4Y 4B 4A Vcc 3B 二输入四或非门 74LS02六反相器 74LS04123456789101112131474LS101B1Y 1A 2A 3B 2BGND2Y2C3Y 3C 3A Vcc 1C 三输入三与非门 74LS10123456789101112131474LS201B2C 1A NC 2B 1CGND1Y1D2Y NC 2A Vcc 2D 四输入二与非门 74LS204线-10线译码器 74LS421234567891011121314151674LS48BCLTBI/RBO RBIDAGNDe d c b a gf Vcc BCD-七段译码器/驱动器 74LS48123456789101112131474LS741CLR1D1CLK1PR1QGND2Q 2PR 2CLK 2D 2CLR Vcc 2Q 正沿触发双D 型触发器 74LS74双J-K 触发器 74LS76二输入四异或门 74LS86 常用集成电路管脚图(一)4位移位寄存器 74LS95负沿触发双J-K 触发器 74LS1121234567891011121314151674LS138ABCG2AG2BG1Y7GNDY6Y5Y4Y3Y2Y1Y0Vcc 3-8线译码器/多路转换器 74LS1381234567891011121314151674LS1391G1A1B1Y01Y11Y21Y3GND2Y32Y22Y12Y02B 2A 2G Vcc 双2-4线译码器/多路转换器 74LS1391234567891011121314151674LS151321YW 读取脉冲GNDC B A 7654Vcc 8选1数据选择器 74LS1511234567891011121314151674LS1531GB1C31C21C11C0 1YGND2Y 2C02C12C22C3A 2G Vcc 双4-1线数据选择器 74LS1531234567891011121314151674LS160CLKABCDA1GNDA00123CS EO Vcc 选择同步位计数器 74LS1601234567891011121314151674LS161CLKABCDPGNDLD T QD QC QB QA C0Vcc CLR同步集成十六进制计数器 74LS1611234567891011121314151674LS3901A1清除1QA1B1QB1QCGND2QD 2QC 2QB 2B 2QA 2清除2A Vcc 1QD双十进制计数器 74LS390NE55512345678GND触发OUT复位Vcc 放电阀值控制电压定时器 NE555DAC08321234567891011121314151617181920WR1CSAGNDDI3DI2DI1DI0VrefRfbDGNDIout1Iout2DI7DI6DI5DI4XFER WR2ILE Vcc 8位D/A 转换器 DAC083212345678910111213142827262524232221201918171615ADC0809IN3IN4IN5IN6IN7IN2IN1IN0ADDA ADDB ADDC ALE D7D6D5D4D0Vref(-)D2START EOCD3OECLOCK Vcc Vref(+)GNDD18位8通道逐次逼近型A/D 转换器 ADC08098线-3线八进制优先编码器 74LS1481234567891011121314151674LS1484567E1A2A1GNDA00123CS EO Vcc 常用集成电路管脚图(二)。

附录B 常用集成电路外部引脚图Z^LSOO 料丽 Wc 聘 t* » ia JI 而冋网KH 丽R1 m74LS(52 z 吃Xkn 4V 4fl 4A n JQ U冋冋丽冋冋〒面和畀1 Wi r?ibL I Q L TT 阡LU I2J L2J LU LU lAJ LZJ 1 1A -Ifl tV 詁 aflJVI“1 21 ® Ml 4J Jj |引IVIB 2Y lA 2B GhO四2输入正“或非”门⑵ 74LS02⑴74LS00四2输入正“与非”门 ⑶74LS04六反相器⑷ 74LS08 四2输入正“与”门74LS04Mtoc fl* S T SArniiiai nil iVJi4A回 rri堆 Pl Pl2 b 1 ALU lU LU Ld 国回 LUUIf JAivikiY&泌⑸74LS10三3输入正“与非”门⑹ 74LS14六反相施密特触发器 丫 A74LS10 T.sec1C IT- K JB W 3T 而 丽 [iJI liil 岡面IT IMOf回 PlUl |Z|口 .4 丨国□ |T.g IB ZAK 2V SMT⑺74LS20双4输入正“与非”门(8) 74LS3274LS20杠呢 )L- T1 M區」LJ LzJ LiJ N lAl bJIT 2a !1fSAav四2输入或门4 lA IT Ifi M冋冋 rni n^i m <30!R1 74LS08 VEADVbr d臼 M 廿 9 H 押 而河豆同而jj .3| J. 1*1 hl in W IB EM *zv cw» K NC a 2A 丹 而57ny 丽両 回 m2 I 」.Jj 丨列回巴316 MC 1C 1O IV G*®wc ri iiLiJ LU Ld LUu u lY u zb A dU2AB CDE FGH IJFl 帀LL UJ _U [± L£J LJTAIB lY2A3fl7T fiNt(9) 74LS47 BCD 到七段译码器/驱动器(有效低、0C 门、15V )(10) 74LS48 BCD (内有上拉电阻)到七段码译码/驱动器7^LS47 ULr.ljfflWHWc I f 0• c d H1门二3IJGur ;) .忙七V :-..----------- w -----------.F yf r n n Pl ' 1(11) 74LS51 2-3 输入“与或非”门(12) 74LS54与或非门(13) 74LS74 双 D 型触发器(带预置和清除、正沿触(14) 74LS76Vae 2Qfl » ICX Jl*B Xi »[i? 哩 iil 卫呼 IT74LS74 ■h -Jri ?訂 g*B7415716J 匸. 5 1 £1(15) 74LS86四2输入异或门四总线缓冲门Y A(16) 74LS125 (带三态输出、C 高时输出关断,即禁VHD阪74LSe646 4Y R A 砂曲3a u avJig. [VI74LS125 v~AVtc < 4A J* X 3* Jlf冋冋.同而帀瓦風引 ⑺ |叫6 C LT HmSCWII & A <ihDLJ LJ LJ kJ kJ LJ LJ LiJ ci.f HbVHt ml b JI atafiJ JJ H. IN .'I I^J .^J 10( IH lOA ij心K PA XLR双JK 触发器(带预置和清除、负沿触发)1* 1Q 1O GhP » M 203」(17) 74LS138 3 线-8线译码器(多路转换器)(18) 74LS148 8线-3线八进制编码器阿T S7冋T1 TJ M 面洞[i?rfi IQ rftH.J5J■J ij :J.■74LS13e)■1n"1*S l<Jl >. [«.T■T■c OZA ^ZB Gl tT□TOVB eo C5 3 7 \ 0 M叵西I有回匝问74LS14S出a -込.序”q-F ,咅许S0丨引1= Ml ElH At 0X3(19) 74LS151 8 选1数据选择器(多路转换器)(20) 74LS153 4(多路转换器)选1数据选择器(21) 74LS160 同步4位计数器(十进制,直接清除)(22) 74LS161 4位计数器(二进制,直接清除)同步ViJU co OA « oc flO FTJwlFS [171 ;ia [ijl (1? [wlID叵、74LS160/ 卫乍KfhF臨K I 亠Tib, . i 'S rFJf ]LIJ PfOJ? cutLil lU' LU ir LU LtA & c a Efr(23) 74LS194 4 位双向通用移位寄存器(24) CD4060B 二进制计数器和振荡器(分频器,14级进位)oc CD cu< £1 別両冋阪同而冋m«:« QI Qt KSFT er nu fBT冋岡冋向冋冋冋R174LSW4H.理 3 Ltl ⑸ LU 回aR SR A B C 0 a ONO oil QU 414 qe 05 (F CK I»(11VP ■»Y£ U) lA d « V iri IStIf 同同冋同冋rmnnrri(29)七段显示数码管(示意图)(25) NE555多谐振荡器(26)A741运算放大器TED HR mr cn冋m n R]H ; ™ (JtT HL2 Rirn Ri R]NE555TH Uf kJ L JtMl CLI tttLJ U U bJULl 止-祐i(27) ADC0804 八位模/数转换器 (28) DAC0832八位数/模转换器m CLU nm w bu n nn* ns同冋PI 冋岡同冋両IU 回na丽 u pa u pT rnmi T *诣 何同冋丽 网网网 mLJbJkJHkJtdliJkJkJH ?! E Iff cuiiK TH! uiEt IHL tana itnf/a HHLJLiJUJLiJUIIiJLJLLfMl^ 縣 Wi 4ew n K n »He "xm附录C常用门逻辑符号对照表。

常用数字集成电路管脚排列及逻辑符号图 D-1 74LS00 四 2 输入与非门图 D-2 74LS01 四 2 输入与非门(OC)图 D-3 74LS02 四 2 输入或非门图 D-4 74LS04 六反相器图 D-5 74LS08 四 2 输入与门图 D-6 74LS10 三 3 输入与非门图 D-7 74LS20 双 4 输入与非门图 D-8R74LS32 四 2 输入或门SQS R QR Q SRSQ图 D-9 74LS54 4 路 2-2-2-2 输入与或非门图 D-10 74LS74 双上升沿 D 型触发器图 D-11 74LS86 四 2 输入异或门图 D-1274LS112 双下降沿 J-K 触发器图 D-13 74LS126 四总线缓冲器图 D-1474LS138 3 线-8 线译码器图 D-15 74LS148 8 线-3 线优先编码器图 D-16 74LS151 8 选 1 数据选择器图 D-17 74LS153 双 4 选 1 数据选择器图 D-18 74LS161 4 位二进制同步计数器图 D-19 74LS194 4 位双向移位寄存器图 D-20 74LS196 二-五-十进制计数器图 D-21 74LS283 4 位二进制超前进位全加器图 D-2274LS290 二-五-十进制计数器图 D-23CD4011B 四 2 输入与非门图 D-24 CD4081 四 2 输入与门图 D-25555 定时器图 D-26DAC0832 8 位数模转换器图 D-27ADC0809 8 位模数转换器。

常用电子器件管脚排列图附录1 逻辑符号对照示例附录表1.1 逻辑非、逻辑极性符号对照示例(以反相器为例)附录表1.2 几种常用逻辑门的逻辑符号比较示例附录表1.3 逻辑符号、框图、管脚排列比较示列(以74HC390为例)附录2 集成电路1. 集成电路命名方法集成电路命名方法见附录表2.1附录表2.1 国产半导体集成电路型号命名法(GB3430-82)2.集成电路介绍集成电路IC 是封在单个封装件中的一组互连电路。

装在陶瓷衬底上的分立元件或电路有时还和单个集成电路连在一起,称为混合集成电路。

把全部元件和电路成型在单片晶体硅材料上称单片集成电路。

单片集成电路现在已成为最普及的集成电路形式,它可以封装成各种类型的固态器件,也可以封装成特殊的集成电路。

通用集成电路分为模拟(线性)和数字两大类。

模拟电路根据输入的各种电平,在输出端产生各种相应的电平;而数字电路是开关器件,以规定的电平响应导通和截止。

有时候集成电路标有LM (线性类型) 或DM(数字类型)符号。

集成电路都有二或三个电源接线端:用CC V 、DD V 、SS V 、V +、V -或GND 来表示。

这是一般应用所需要的。

双列直插式是集成电路最通用的封装形式。

其引脚标记有半圆形豁口、标志线、标志圆点 等,一般由半圆形豁口就可以确定各引脚的位置。

双列直插式的引脚排列图如附录图2.1所示。

3.使用TFL 集成电路与CMOS 集成电路的注意事项(1) 使用TYL 集成电路注意事项① TYL 集成电路的电源电压不能高于V 5.5+。

使用时,不能将电源与地颠倒错接,否则将会因为过大电流而造成器件损坏。

附录图 2.1双列直插式集成电路的引脚排列②电路的各输入端不能直接与高于V 5.5+和低于V 5.0-的低内阻电源连接,因为低内阻电源能提供较大的电流,导致器件过热而烧坏。

③除三态和集电极开路的电路外,输出端不允许并联使用。

如果将集电极开路的门电路输出端并联使用而使电路具有线与功能时,应在其输出端加一个预先计算好的上拉负载电阻到CC V 端。

计算机硬件基础实验指导书(2014级数计软工)每组2人;每个实验完成后,必须于下个实验前提交实验报告(纸质版)。

附录一数字电路实验箱的使用说明附录二数字电路实验器件引脚排列图实验仪器及实验器件需求每台实验箱需配备:1个示波器,1个面包板,1个万用表,1个电位器(可能实验箱上本身就有),若干导线。

所需芯片如下:(每台)74LS00 与非门1片74LS86 异或门1片74LS125 三态门1片74LS08 与门1片74LS04 非门1片74LS20 与非门3片74LS283 全加器1片74LS138 译码器1片74LS151 数据选择器1片74LS74 D触发器1片74LS112 JK触发器1片74LS161 计数器2片1、电子技术测量仪器的使用及门电路逻辑功能测试熟悉示波器和数字电路实验箱的使用方法,掌握脉冲信号参数的测试方法。

了解集成电路的外引线排列及其使用方法,测试各种逻辑门电路的逻辑功能。

一、实验目的了解数字实验箱的原理,掌握其使用方法了解TTL器件和CMOS器件的使用特点掌握基本门电路逻辑功能的测试方法二、实验仪器及实验器件器件:YB3262实验箱,YB4325示波器,1片74LS00与非门,1个万用表,1片74LS86异或门,1片74LS125三态缓冲器,1片74LS08与门,导线若干。

三、实验内容(1)数字实验箱的使用(参考附录一)用万用表测出固定直流稳压源的出去电压值。

用万用表分别测出十六路高低电平信号源和单次脉冲信号源的高低电平值,并观察单次脉冲前后沿(即输出波形的上升和下降时间)的变化。

分别用十六路高低电平信号源和单次脉冲信号源检查十二路高低电平指示灯的好坏。

用十六路高低电平信号源测试七段数码管的工作情况,观察是否正确显示0-9十个数码。

(2)分别写出74LS00,74LS86,74LS08,74LS125的逻辑表达式,列出其真值表,并分别对其逻辑功能进行静态测试。

74LS125三态缓冲器的逻辑功能为:E’为使能端,低电平有效。

附录B 常用集成电路外部引脚图(1) 74LS00四2输入正“与非”门74LS00 皿VCC484A4Y383A3Y[1] LU12J LU 111IZJ1A1B 1Y2A2B 2YCWD(3) 74LS04六反相器74LS04 gLU I2J LU LU L1J 回 LU1A 1Y 2A 2Y 3A SY GND(2) 74LS02四2输入正“或非”门74LS02 Y “.BVcc 4Y 48 4A SY 3B 3A(4) 74LS08四2输入正“与”门74LS08 Y ,ASV<X 4B 4A 4Y 38 5A 3Y而冋耳冋冋回ITd 自3 4 ©⑼31A IB 1Y 2A 28 2Y GhO(5) 74LS10三3输入正“与非”门74LS10 Y-A8C(6) 74LS14六反相施密特触发器Y = AVO : 6A 6Y 5A 5Y 4A 4Y质」 申?护卩 山山山山山山Ld1A l¥ 2A 2Y M 3Y GKD(7) 74LS20双4输入正“与非"门74LS20 Y =ABCOVbc 2D X NC 28 2A 2Y1.1A IB NC 1C 10 IV GHD(8) 74LS32 四 2^A^nY = A + Bva 4B 4A 4Y 3B M 3T(9) 74LS47 BCD到七段译码器/驱动器 (有效低、0C门、15V)74LS47Vcc f g a b c d e冋冋向冋/LLJ'・~ -*15枪入tA tAji LU ill i< 1^1 Ld iejB C LT BI RBO RW D A GHC(10) 74LS48 BCD到七段码译码/驱动器(有上拉电阻)I.T REO/R】IR1 D A GXDY = AB + CDE + FGH + IJ(13) 74LS74双D型触发器(带预置和清除、正沿触发)Vco XLR 20 2OK 2PR 20 2Q而回丽0回目国74LS74丄[£J向21㈢空也1CLR 10 1CK 1PR 1O 1O GKO(15) 74LS86四2输入异或门74LS86 Y=A«$6=AS=ABVcc 4B 4A 4Y 38 3A 3Y[iT fol 12] (Til Ro] [¥] [Tl(14) 74LS76双JK触发器(带预置和清除、负沿触发)IK IQ 1Q GNO 2K 2Q 2Q 2J74LS76Ji >: <:■n [:. <:■E L II1J3L L L£J⑥山直1CK 1PR 1CLR 1J Vcc 2CK 2PR 2CLR(16) 74LS125四总线缓冲门Y = A(带三态输出、C高时输出关断,即禁止)74LS125 zVcc 4C 4A <r X 3A 3Y 而冋冋而同回国m^n^rHTWKPT1C 1A 1Y 2C 2A 2Y GN0(11) 74LS51 2-3输入“与或非"门(12) 74LS54与或非门2丫• :2A・26)■ :2C・2D)74LS511Y- 1A- 16 - 1C' ♦r1D- im(17) 74LS138 3线-8线译码器 (多路转换器)驱 YO Y1 Y2 Y3 Y4 Y$ Yfl 応屁而冋叼而応冋74LS1383发・8纯话哥寥,$0转萩耳L L LL12JU J 1JL 6J I 11S JABC O2A G2B G1 Y7 GNOVoc eO GS 32 1 0 AO丽:[ii] 冋卑厄 M 冋叵]74LS148 8ft-3^ A 进创优先廉垮比4567 El A2 A1 ONC(19) 74LS151 8选1数据选择器 (多路转换器)497 A U C[?& 同而而壬]而同可(20) 74LS153 4选1数据选择器(多路转换器)ra a A 2C32C2 XI 2(» 2Y冋冋冋冋冈冋而[7]74LS151 LU LU 2J Li ±l 1 IzJ ±J3 210 Y W S GHD74LS153UlLdUJLiJlAJLLlLJLiJTc B ICS IC2 IC) ICO IT CKD(21) 74LSI60同步4位计数器(十进制,直接清除)(22) 74LS161同步4位计数器(二进制,直接清除)74LS160E 步凶使计fts ・i (柚斤陰》I1J l±] UJ L 4' HJ l± L1J l£CLR CLK AB C 0 EP CND(23) 74LS194 4位双向通用移位寄存器(24) CD4060B 二进制计数器和振荡器(分频器,14级进位)CLR $R A 8 C 0 SI GNDQ】2 Q13 QM Q6Q7 Q4 VSS(18) 74LS148 8线-3线八进制编码器VCC CO QA 06 QC QD ET 1031 CU A B C D »? ©©(25) NE555多谐振荡器(26) "741运算放大器(27) ADC0804八位模/数转换器(28) DAC0832八位数/模转换器吃CLKI DM DB1 D© 063 DM D65 DB6 C67ADC0804LdLjLJLiJLJLdLJLBJLdkJ誌药55 cum T5TTI um U1&- MKD Ur©f/2 DO©(29)七段显示数码管(示意图)DP G COM F EHill£... 、a af JA B COMC D岡冋冋回冋网冋冋网冋VCC (IE WW2 OTR M 05 «07 Uttll I<»t2网冋冋冋冋网冋冋冋冋MC0832L2JS 丽I 临D D3 D2 01 BO Uref Rfb MMD附录C常用门逻辑符号对照表。

常用集成电路型号及引脚图

电路名称及符号 引脚图 注释

六反向器

TTL 74LS04 CMOS MC14069 A:输入 Y:输出

四两输入与非门

TTL 74LS00 CMOS MC14069 7401(OC) A、B:输入 Y:输出

双四输入与非门 TTL 74LS20 CMOS MC14012 NC 为空脚

A、B、C、D 输入 Y 输出

双进位保留全加器

74LS183

NC 为空脚

四两输入异或门 74LS86 A、B:输入 Y 输出

与门输入主从

单 JK 触发器

74H72

上升沿触发

二—五—十进制

异步计数器

74LS290

双 D 型触发器

74LS74

上升沿触发

错误!文档中没有指定样式的文字。

221

556

双 JK 触发器 74LS112

负沿触发

四总线缓冲器 74125(三态低有效) 74126(三态高有效)

555

四线—十线译码器 74LS42

十线—四线优先 编码器 74LS147

双四选一数据 选择器 74LS153

同步可逆十进制 计数器 74LS192

CP+=1 CP =↑减法 CP+=↓CP =1 加法

ADC 0809。

附录1 集成电路外引线图3四2输入异或门74LS86Y=A ⊕B1A 1B 1Y 2A 2B 2Y GNDVcc 4A 4B 4Y 3A 3B 3Y4六反向器74LS04Y=A1A 1Y 2A 2Y 3A 3Y GNDVcc 6A 6Y 5A 5Y 4A4Y1四2输入与非门74LS00Y=A •B1A 1B 1Y 2A 2B 2Y GNDVcc 4A 4B 4Y 3A 3B 3Y2四2输入或门74LS32Y=A +B1A 1B 1Y 2A 2B 2Y GNDVcc 4A 4B 4Y 3A 3B3Y7双4输入与非门74LS20Y=A •B •C •D1A 1B NC 1C 1D 1Y GNDVcc 2D 2C NC 2B 2A 2Y82路3—3输入、2路2—2输入与或非门Y=(A •B •D)+(E •F •G)1A 2A 2B 2C 2D 2Y GNDVcc 1C 1B 1F 1E 1D1Y5四2输入与门74LS08Y=A •B1A 1B 1Y 2A 2B 2Y GNDVcc 4A 4B 4Y 3A 3B 3Y6三3输入与非门74LS10Y=A •B •C1A 1B 2A 2B 2C 2Y GNDVcc 1C 1Y 3C 3B 3A 3YY=(A •B)+(C •D)74LS5111四2输入与非门CD4011Y=A •B1A 1B 1Y 2A 2B 2Y V SSV DD 4A 4B 4Y 3A3B 3Y 12六反向器CD4069Y=A1A 1Y 2A 2Y 3A 3Y V SSV DD 6A 6Y 5A 5Y 4A4Y9四2输入或非门74LS02Y=A +B1A 1B 1Y 2A 2B 2Y GNDVcc 4A 4B 4Y 3A3B 3Y 108输入与非门74LS30Y=A •B •C •D •E •F •G •H A B C D E F GNDVcc NC H G NC NC Y151613141A 1B NC 1C 1D 1Y GNDV CC 2D 2C NC 2B 2A 2Y双4输入与门74LS211A 1B 2A 2B 2C 2Y GNDV CC 1C 1Y 3C 3B 3A 3Y三3输入或非门74LS27Y=A+B+C Y=A •B •C •D1A 1B 2A 2B 2C 2Y GNDV CC 1C 1Y 3C 3B 3A 3Y三3输入与门74LS11Y=A •B •C 双上升沿D 型触发器1CLR 1D 1CLK 1PRE 1Q 1Q V SSV DD CD40132CLR 2D 2CLK 2PRE2Q 2Q27B C LT BI LE DV SSV DD 28254线—七段译码器/驱动器(BCD B C LT BI/RBORBI D A V CC Y f Y g Ya Y b Y d Ye26GNDV CC 3129304线—16线译码器 74LS15445678910A B C D G215G1A GND输入,有限流电阻 ) 74LS48Yc Y f Y g Ya Y b Y d YeYc 4线—七段译码器/驱动器(BCD 输入,无限流电阻 ) CD45114线—七段译码器/驱动器(OC)B C LT BI/RBORBI D A V CC Y f Y g Ya Y b Y d YeGND74LS247Yc GNDV CC 3线—8线译码器 74LS138A B C OE2A OE2B OE1Y7Y0Y1Y2Y3Y4Y6Y5123141312011双上升沿D 型触发器74LS741CLR 1D 1CLK 1PRE 1Q 1Q GNDVcc 双下降沿JK 型触发器74LS112GND Vcc 2CLR 2D 2CLK 2PRE 2Q 2Q1CLR 1K 1CLK 1PRE 1Q 1Q 1J 2CLR 2K 2CLK 2PRE 2Q2Q 2J3435323338四位十进制同步计数器(异步清零)CLR CLK A B C D GNDVccRCO Q A Q B Q C Q D ET 39十进制同步加/减计数器(双时钟)B Q B Q A DOWNUP Q C Q D Vcc A CLR BO CO LOAD C 364位二进制全加器372B2A2A1B1GNDV CC C0LOAD74LS160EP 74LS192 CD40192GNDDGNDV CC 10线—4线优先编码器 74LS14745678C B NC D 321A9四位二进制同步计数器74LS161CLR CLK A B C D GNDV CC RCO Q A Q B Q C Q D ET LOADEP 74LS1484567E1A2GNDV CC E0GS 3210A1A08线—3线优先编码器GNDV CC 4线—10线译码器 74LS42Y0Y1Y2Y3Y4Y5Y6A B C D Y9Y7Y84位二进制同步加/减计数器(双时钟)B Q B Q A UP Q C Q D Vcc A CLR BO CO LOAD C 74LS193 CD40193GNDDDOWN74LS28313B3A3A4B4C4442456D 触发器(有清除端)CLR 1Q 1D 2D 2Q 3D GNDV CC 6Q 6D 5D 5Q 4D 4Q 404346444774LS1743Q CLK14位同步二进制计数/分配,振荡器Q12Q13Q14Q6Q5Q7V SSV DD Q10Q8Q9CLR CKI CKO CD4060Q4CKO4上升沿D型触发器CLR 1Q 1Q 1D 2D 2Q GNDV CC 74LS1752Q CLK4Q 4Q 4D 3D 3Q 3Q 十进制计数/分频器CD4017Y5Y1Y0Y2Y6Y7V SSV DD CLR CLK CLKEN CO Y9Y4Y3Y8414位双向通用移位寄存器SR SERA CLRBCD GNDV CC QA QB QC QD CLK S1SL SER S074LS194R9(1)NC R9(2)Q C Q B NC V CC GNDR0(2)CKB CKA Q D Q A 十进制计数器74LS290R0(1)8位移位寄存器Q A A CLR B Q C Q D GNDV CC Q H Q G Q F Q E CLKQ B 74LS164四位二进制同步加/减计数器B Q B Q A CTEN D/U Q C Q D Vcc A CLK RCO CO/BO LOAD C 74LS191GNDD50488段LED 数码显示器(共阴)a bcde g 51fG N DG N D8段LED 数码显示器(共阳)a bcde gf V C CV C C555时基电路GND TI OUT Vcc D TH VCRD49E6E5E4E3E2E1GNDV CC E8E9E10E11E12E13D W E7G E0E14E15A B C16选1数据选择器74LS15052534双向模拟开关1IN/OUT V SSV DD 1V C CD40668选1数据选择器(原,反码输出)D3D2D1D0Y W GNDV CC D4D5D6D7A B 74LS151G C1IN/OUT 2IN/OUT 2IN/OUT2V C 3V C 4V C4IN/OUT 4IN/OUT 3IN/OUT 3IN/OUT附录2 TTL集成电路分类、推荐工作条件1.TTL集成电路分类54系列:军用产品74系列:民用产品2.推荐工作条件。

附录三常用集成电路芯片引脚排列图印刷电路板贴片封装芯片双列直插式封装74LS00 74LS03Y=AB四2输入正与非门Y=AB集电极开路输出的四2输入正与非门74LS0474LS08Y=A六反相器Y=AB 四2输入正与门74LS10 74LS11Y=ABC三3输入正与非门Y=ABC 三3输入正与门74LS2074LS21Y=ABCD双4输入正与非门Y=ABCD双4输入正与门74LS32 74LS48测试Y=A+B 四2输入正或门BCD-七段译码器74LS48是具有内部上拉电阻的BCD-七段译码器/驱动器。

输出高电平有效,其中,A、B、C、D是输入端,a、b、c、d、e、f是输出。

74LS51 74LS74Y=CDAB+与或非门双D型正边沿触发器74LS8674LS90CP2Y=A⊕B 四2输入异或门十进制计数器(2、5分频)74LS90是四位十进制计数器。

各有两个置“0”(R01、R02)和置“9”(R91、R92)输入端,有两个计数输入端A和B,Q A-Q D为输出。

若从A端输入计数脉冲,将Q A与B短接,则组成十进制计数器(分频器);若从B端输入计数脉冲,把Q D与A短接,则组成二~五混合进制计数器(或五分频器)74LS112 74LS125双J -K 负边沿触发器(带预置和清除端) Y=A 三态输出的四总线缓冲门 EN 为高时禁止74LS13874LS153输出选择允许输出数据输入选通选择输出3-8线译码器/分配器 双4-1线数据选择器/多路开关 74LS138为3-8线译码器,包含三个允许输入端S 1、2S 、3S ,可对8条线中任意一条进行译码,这取决于三个二进制选择输入端A 0、A 1、A 2和三个允许输入端S 1、2S 、3S 的状态。

74LS160 74LS180数据输入输出4位同步计数器(十进制,直接清除) 9位奇/偶校验器/发生器74LS175 74LS183输入输入输出四D 型触发器(互补输出,共直接清除) 双保留进位全加器74LS183全加器每一位有一个单独的进位输出,它可在多输入保留进位方法中使用,能在不大于两级门的延时内产生真和、真进位输出。