STM32中断列表

- 格式:doc

- 大小:28.00 KB

- 文档页数:2

CM3 内核支持256 个中断,其中包含了16 个内核中断和240 个外部中断,并且具有256级的可编程中断设置。

但STM32 并没有使用CM3 内核的全部东西,而是只用了它的一部分。

STM32 有84 个中断,包括16 个内核中断和68 个可屏蔽中断,具有16 级可编程的中断优先级。

而我们常用的就是这68 个可屏蔽中断,但是STM32 的68 个可屏蔽中断,在STM32F103 系列上面,又只有60 个(在107 系列才有68 个)。

在MDK 内,与NVIC 相关的寄存器,MDK 为其定义了如下的结构体:点击(此处)折叠或打开1.typedef struct2.{3.vu32 ISER[2];4.u32 RESERVED0[30];5.vu32 ICER[2];6.u32 RSERVED1[30];7.vu32 ISPR[2];8.u32 RESERVED2[30];9.vu32 ICPR[2];10.u32 RESERVED3[30];11.vu32 IABR[2];12.u32 RESERVED4[62];13.vu32 IPR[15];14.} NVIC_TypeDef;STM32 的中断在这些寄存器的控制下有序的执行的。

只有了解这些中断寄存器,才能了解STM32 的中断。

下面简要介绍这几个寄存器:ISER[2]:I SER 全称是:Interrupt Set-Enable Registers,这是一个中断使能寄存器组。

上面说了STM32F103 的可屏蔽中断只有60 个,这里用了 2 个32 位的寄存器,总共可以表示64 个中断。

而STM32F103 只用了其中的前60 位。

ISER[0]的bit0~bit31 分别对应中断0~31。

ISER[1]的bit0~27 对应中断32~59;这样总共60 个中断就分别对应上了。

你要使能某个中断,必须设置相应的ISER 位为1,使该中断被使能(这里仅仅是使能,还要配合中断分组、屏蔽、IO 口映射等设置才算是一个完整的中断设置)。

stm32adc中断函数例程在STM32的ADC中,配置中断可以通过HAL库或标准库来完成。

以下是一个使用HAL库的例程,用于配置并启用ADC的中断功能。

首先,需要初始化ADC并配置中断:#include"stm32f4xx_hal.h"ADC_HandleTypeDef hadc1;void HAL_ADC_MspInit(ADC_HandleTypeDef*hadc){GPIO_InitTypeDef GPIO_InitStruct={0};__HAL_RCC_GPIOA_CLK_ENABLE();__HAL_RCC_ADC1_CLK_ENABLE();GPIO_InitStruct.Pin=GPIO_PIN_0;GPIO_InitStruct.Mode=GPIO_MODE_ANALOG;GPIO_InitStruct.Pull=GPIO_NOPULL;HAL_GPIO_Init(GPIOA,&GPIO_InitStruct);HAL_NVIC_SetPriority(ADC_IRQn,0,0);HAL_NVIC_EnableIRQ(ADC_IRQn);}void HAL_ADC_MspDeInit(ADC_HandleTypeDef*hadc){__HAL_RCC_ADC1_CLK_DISABLE();}void MX_ADC1_Init(void){ADC_ChannelConfTypeDef sConfig={0};hadc1.Instance=ADC1;hadc1.Init.ClockPrescaler=ADC_CLOCK_SYNC_PCLK_DIV4;hadc1.Init.Resolution=ADC_RESOLUTION_12B;hadc1.Init.ScanConvMode=DISABLE;hadc1.Init.ContinuousConvMode=DISABLE;hadc1.Init.DiscontinuousConvMode=DISABLE;hadc1.Init.DataAlign=ADC_DATAALIGN_RIGHT;hadc1.Init.NbrOfConversion=1;hadc1.Init.DMAContinuousRequests=DISABLE;hadc1.Init.EOCSelection=ADC_EOC_SINGLE_CONV;HAL_ADC_Init(&hadc1);sConfig.Channel=ADC_CHANNEL_0;sConfig.Rank=1;sConfig.SamplingTime=ADC_SAMPLETIME_3CYCLES;HAL_ADC_ConfigChannel(&hadc1,&sConfig);}接下来,启动ADC并在中断服务函数中处理中断:void HAL_ADC_ConvCpltCallback(ADC_HandleTypeDef*hadc){if(hadc->Instance==ADC1){uint32_t adc_value=HAL_ADC_GetValue(hadc);//在这里处理ADC转换完成中断}}void ADC_IRQHandler(void){HAL_ADC_IRQHandler(&hadc1);}这是一个简单的例程,用于配置和使用STM32的ADC中断功能。

STM32103系列中断NVIC 中断构成10个系统异常(系统中断)60个外部中断NVIC寄存器NVIC简介全称:嵌套向量中断控制器来源:cortex-M3 内核里的NVIC减去不需要的部分构成STM32的NVIC寄存器1.ISER中断使能寄存器2.ICER中断清除寄存器(也就是失能中断)3.ISPR中断使能悬起寄存器4.ICPR中断清除悬起寄存器5.IABR中断有效位寄存器6.IP中断优先级寄存器7.STIR软件触发中断寄存器黄色部分是常用的中断优先级优先级的定义优先级设定寄存器:NVIC->IPRx复位,NMI 和硬 fault是特殊的、不可设置的、优先级最高的,无论什么时候出现都会抢占最高级别作用:用来配置外部中断优先级寄存器说明寄存器宽度:8bit(如图所示:STM32系列有效的只有4bit)支持16级优先级别:0~15数值意义:数值越小,优先级就越高优先级分组优先级分组:SCB->AIRCR:PRIGROUP[10:8]优先级分组定义用于表达优先级的4bit,如果有中断发生,抢占式优先级高的先执行,如果抢占式优先级相同,就比较子优先级。

如果2者都相同,那就比较它们的硬件编号(编号小的优先级高)优先级分组的来源优先级分组抢占式优先级子优先级固件库中断配置需要用到的定义所在文件misc.c、misc.h、stm32f10x.h、st32f10x_it.c中断配置步骤使能外设某个中断11.开启比如定时器中断、串口中断,外部中断等相应外设中断的寄存器位2.使能NVIC寄存器中的使能寄存器设置中断优先级分组2对应的固件库函数:NVIC_PriorityGroupConfig(),在misc.c的文件中配置NVIC寄存器3初始化NVIC_InitTypeDef结构体将初始化后的NVIC_InitTypeDef结构体放入NVIC_Init()中,在misc.c的文件中4编写中断服务函数51.中断服务函数名称都在startup_stm32f10x_hd.s的汇编文件中已经设置好了2.在st32f10x_it.c文件中编写。

STM32中断优先级彻底讲解stm32目前支持的中断共为84个(16个内核+68个外部),16级可编程中断优先级的设置(仅使用中断优先级设置8bit中的高4位)和16个抢占优先级(因为抢占优先级最多可以有四位数)。

二:优先级推论stm32(cortex-m3)中有两个优先级的概念——抢占式优先级和响应优先级,有人把响应优先级称作'亚优先级'或'副优先级',每个中断源都需要被指定这两种优先级。

具备低抢占市场式优先级的中断可以在具备高抢占市场式优先级的中断处理过程中被积极响应,即为中断嵌套,或者说低抢占市场式优先级的中断可以嵌套高抢占市场式优先级的中断。

当两个中断源的抢占式优先级相同时,这两个中断将没有嵌套关系,当一个中断到来后,如果正在处理另一个中断,这个后到来的中断就要等到前一个中断处理完之后才能被处理。

如果这两个中断同时到达,则中断控制器根据他们的响应优先级高低来决定先处理哪一个;如果他们的抢占式优先级和响应优先级都相等,则根据他们在中断表中的排位顺序同意先处置哪一个。

三:优先级分组既然每个中断源都须要被选定这两种优先级,就须要存有适当的寄存器位记录每个中断的优先级;在cortex-m3中定义了8个比特位用作设置中断源的优先级,这8个比特位在nvic应用领域中断与登位掌控递丛器(aircr)的中断优先级分组域中,可以存有8种分配方式,如下:所有8位用于指定响应优先级最低1十一位用作选定抢占市场式优先级,最高7十一位用作选定积极响应优先级最低2十一位用作选定抢占市场式优先级,最高6十一位用作选定积极响应优先级最低3十一位用作选定抢占市场式优先级,最高5十一位用作选定积极响应优先级最低4十一位用作选定抢占市场式优先级,最高4十一位用作选定积极响应优先级最低5十一位用作选定抢占市场式优先级,最高3十一位用作选定积极响应优先级最低6十一位用作选定抢占市场式优先级,最高2十一位用作选定积极响应优先级最低7十一位用作选定抢占市场式优先级,最高1十一位用作选定积极响应优先级这就是优先级分组的概念。

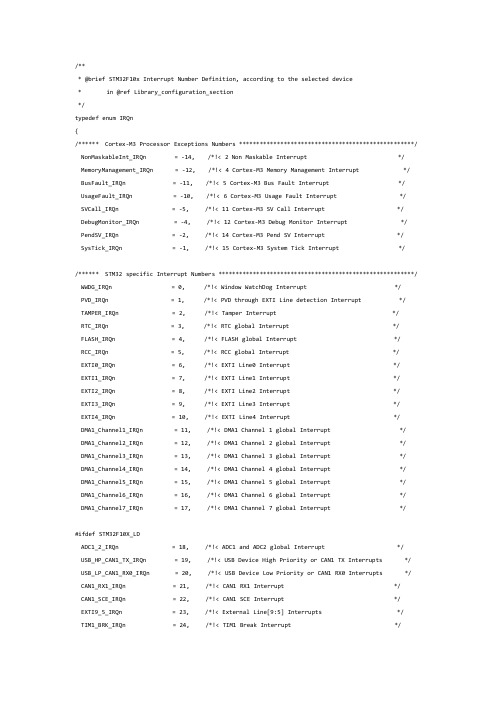

/***@brief STM32F10x Interrupt Number Definition,according to the selected device*in@ref Library_configuration_section*/typedef enum IRQn{/******Cortex-M3Processor Exceptions Numbers***************************************************/ NonMaskableInt_IRQn=-14,/*!<2Non Maskable Interrupt*/ MemoryManagement_IRQn=-12,/*!<4Cortex-M3Memory Management Interrupt*/ BusFault_IRQn=-11,/*!<5Cortex-M3Bus Fault Interrupt*/ UsageFault_IRQn=-10,/*!<6Cortex-M3Usage Fault Interrupt*/ SVCall_IRQn=-5,/*!<11Cortex-M3SV Call Interrupt*/ DebugMonitor_IRQn=-4,/*!<12Cortex-M3Debug Monitor Interrupt*/ PendSV_IRQn=-2,/*!<14Cortex-M3Pend SV Interrupt*/ SysTick_IRQn=-1,/*!<15Cortex-M3System Tick Interrupt*//******STM32specific Interrupt Numbers*********************************************************/ WWDG_IRQn=0,/*!<Window WatchDog Interrupt*/ PVD_IRQn=1,/*!<PVD through EXTI Line detection Interrupt*/ TAMPER_IRQn=2,/*!<Tamper Interrupt*/ RTC_IRQn=3,/*!<RTC global Interrupt*/ FLASH_IRQn=4,/*!<FLASH global Interrupt*/ RCC_IRQn=5,/*!<RCC global Interrupt*/ EXTI0_IRQn=6,/*!<EXTI Line0Interrupt*/ EXTI1_IRQn=7,/*!<EXTI Line1Interrupt*/ EXTI2_IRQn=8,/*!<EXTI Line2Interrupt*/ EXTI3_IRQn=9,/*!<EXTI Line3Interrupt*/ EXTI4_IRQn=10,/*!<EXTI Line4Interrupt*/ DMA1_Channel1_IRQn=11,/*!<DMA1Channel1global Interrupt*/ DMA1_Channel2_IRQn=12,/*!<DMA1Channel2global Interrupt*/ DMA1_Channel3_IRQn=13,/*!<DMA1Channel3global Interrupt*/ DMA1_Channel4_IRQn=14,/*!<DMA1Channel4global Interrupt*/ DMA1_Channel5_IRQn=15,/*!<DMA1Channel5global Interrupt*/ DMA1_Channel6_IRQn=16,/*!<DMA1Channel6global Interrupt*/ DMA1_Channel7_IRQn=17,/*!<DMA1Channel7global Interrupt*/#ifdef STM32F10X_LDADC1_2_IRQn=18,/*!<ADC1and ADC2global Interrupt*/ USB_HP_CAN1_TX_IRQn=19,/*!<USB Device High Priority or CAN1TX Interrupts*/ USB_LP_CAN1_RX0_IRQn=20,/*!<USB Device Low Priority or CAN1RX0Interrupts*/ CAN1_RX1_IRQn=21,/*!<CAN1RX1Interrupt*/ CAN1_SCE_IRQn=22,/*!<CAN1SCE Interrupt*/ EXTI9_5_IRQn=23,/*!<External Line[9:5]Interrupts*/ TIM1_BRK_IRQn=24,/*!<TIM1Break Interrupt*/TIM1_TRG_COM_IRQn=26,/*!<TIM1Trigger and Commutation Interrupt*/ TIM1_CC_IRQn=27,/*!<TIM1Capture Compare Interrupt*/TIM2_IRQn=28,/*!<TIM2global Interrupt*/TIM3_IRQn=29,/*!<TIM3global Interrupt*/I2C1_EV_IRQn=31,/*!<I2C1Event Interrupt*/I2C1_ER_IRQn=32,/*!<I2C1Error Interrupt*/SPI1_IRQn=35,/*!<SPI1global Interrupt*/ USART1_IRQn=37,/*!<USART1global Interrupt*/ USART2_IRQn=38,/*!<USART2global Interrupt*/ EXTI15_10_IRQn=40,/*!<External Line[15:10]Interrupts*/ RTCAlarm_IRQn=41,/*!<RTC Alarm through EXTI Line Interrupt*/ USBWakeUp_IRQn=42/*!<USB Device WakeUp from suspend through EXTI Line Interrupt */#endif/*STM32F10X_LD*/#ifdef STM32F10X_LD_VLADC1_IRQn=18,/*!<ADC1global Interrupt*/EXTI9_5_IRQn=23,/*!<External Line[9:5]Interrupts*/TIM1_BRK_TIM15_IRQn=24,/*!<TIM1Break and TIM15Interrupts*/ TIM1_UP_TIM16_IRQn=25,/*!<TIM1Update and TIM16Interrupts*/ TIM1_TRG_COM_TIM17_IRQn=26,/*!<TIM1Trigger and Commutation and TIM17Interrupt*/ TIM1_CC_IRQn=27,/*!<TIM1Capture Compare Interrupt*/TIM2_IRQn=28,/*!<TIM2global Interrupt*/TIM3_IRQn=29,/*!<TIM3global Interrupt*/I2C1_EV_IRQn=31,/*!<I2C1Event Interrupt*/I2C1_ER_IRQn=32,/*!<I2C1Error Interrupt*/SPI1_IRQn=35,/*!<SPI1global Interrupt*/ USART1_IRQn=37,/*!<USART1global Interrupt*/ USART2_IRQn=38,/*!<USART2global Interrupt*/ EXTI15_10_IRQn=40,/*!<External Line[15:10]Interrupts*/ RTCAlarm_IRQn=41,/*!<RTC Alarm through EXTI Line Interrupt*/ CEC_IRQn=42,/*!<HDMI-CEC Interrupt*/TIM6_DAC_IRQn=54,/*!<TIM6and DAC underrun Interrupt*/TIM7_IRQn=55/*!<TIM7Interrupt*/#endif/*STM32F10X_LD_VL*/#ifdef STM32F10X_MDADC1_2_IRQn=18,/*!<ADC1and ADC2global Interrupt*/ USB_HP_CAN1_TX_IRQn=19,/*!<USB Device High Priority or CAN1TX Interrupts*/ USB_LP_CAN1_RX0_IRQn=20,/*!<USB Device Low Priority or CAN1RX0Interrupts*/ CAN1_RX1_IRQn=21,/*!<CAN1RX1Interrupt*/CAN1_SCE_IRQn=22,/*!<CAN1SCE Interrupt*/EXTI9_5_IRQn=23,/*!<External Line[9:5]Interrupts*/TIM1_UP_IRQn=25,/*!<TIM1Update Interrupt*/TIM1_TRG_COM_IRQn=26,/*!<TIM1Trigger and Commutation Interrupt*/ TIM1_CC_IRQn=27,/*!<TIM1Capture Compare Interrupt*/TIM2_IRQn=28,/*!<TIM2global Interrupt*/TIM3_IRQn=29,/*!<TIM3global Interrupt*/TIM4_IRQn=30,/*!<TIM4global Interrupt*/I2C1_EV_IRQn=31,/*!<I2C1Event Interrupt*/I2C1_ER_IRQn=32,/*!<I2C1Error Interrupt*/I2C2_EV_IRQn=33,/*!<I2C2Event Interrupt*/I2C2_ER_IRQn=34,/*!<I2C2Error Interrupt*/SPI1_IRQn=35,/*!<SPI1global Interrupt*/SPI2_IRQn=36,/*!<SPI2global Interrupt*/ USART1_IRQn=37,/*!<USART1global Interrupt*/ USART2_IRQn=38,/*!<USART2global Interrupt*/ USART3_IRQn=39,/*!<USART3global Interrupt*/ EXTI15_10_IRQn=40,/*!<External Line[15:10]Interrupts*/ RTCAlarm_IRQn=41,/*!<RTC Alarm through EXTI Line Interrupt*/ USBWakeUp_IRQn=42/*!<USB Device WakeUp from suspend through EXTI Line Interrupt */#endif/*STM32F10X_MD*/#ifdef STM32F10X_MD_VLADC1_IRQn=18,/*!<ADC1global Interrupt*/EXTI9_5_IRQn=23,/*!<External Line[9:5]Interrupts*/TIM1_BRK_TIM15_IRQn=24,/*!<TIM1Break and TIM15Interrupts*/ TIM1_UP_TIM16_IRQn=25,/*!<TIM1Update and TIM16Interrupts*/ TIM1_TRG_COM_TIM17_IRQn=26,/*!<TIM1Trigger and Commutation and TIM17Interrupt*/ TIM1_CC_IRQn=27,/*!<TIM1Capture Compare Interrupt*/TIM2_IRQn=28,/*!<TIM2global Interrupt*/TIM3_IRQn=29,/*!<TIM3global Interrupt*/TIM4_IRQn=30,/*!<TIM4global Interrupt*/I2C1_EV_IRQn=31,/*!<I2C1Event Interrupt*/I2C1_ER_IRQn=32,/*!<I2C1Error Interrupt*/I2C2_EV_IRQn=33,/*!<I2C2Event Interrupt*/I2C2_ER_IRQn=34,/*!<I2C2Error Interrupt*/SPI1_IRQn=35,/*!<SPI1global Interrupt*/SPI2_IRQn=36,/*!<SPI2global Interrupt*/ USART1_IRQn=37,/*!<USART1global Interrupt*/ USART2_IRQn=38,/*!<USART2global Interrupt*/ USART3_IRQn=39,/*!<USART3global Interrupt*/ EXTI15_10_IRQn=40,/*!<External Line[15:10]Interrupts*/ RTCAlarm_IRQn=41,/*!<RTC Alarm through EXTI Line Interrupt*/ CEC_IRQn=42,/*!<HDMI-CEC Interrupt*/TIM6_DAC_IRQn=54,/*!<TIM6and DAC underrun Interrupt*/TIM7_IRQn=55/*!<TIM7Interrupt*/#endif/*STM32F10X_MD_VL*/#ifdef STM32F10X_HDADC1_2_IRQn=18,/*!<ADC1and ADC2global Interrupt*/ USB_HP_CAN1_TX_IRQn=19,/*!<USB Device High Priority or CAN1TX Interrupts*/ USB_LP_CAN1_RX0_IRQn=20,/*!<USB Device Low Priority or CAN1RX0Interrupts*/ CAN1_RX1_IRQn=21,/*!<CAN1RX1Interrupt*/CAN1_SCE_IRQn=22,/*!<CAN1SCE Interrupt*/EXTI9_5_IRQn=23,/*!<External Line[9:5]Interrupts*/TIM1_BRK_IRQn=24,/*!<TIM1Break Interrupt*/TIM1_UP_IRQn=25,/*!<TIM1Update Interrupt*/TIM1_TRG_COM_IRQn=26,/*!<TIM1Trigger and Commutation Interrupt*/ TIM1_CC_IRQn=27,/*!<TIM1Capture Compare Interrupt*/TIM2_IRQn=28,/*!<TIM2global Interrupt*/TIM3_IRQn=29,/*!<TIM3global Interrupt*/TIM4_IRQn=30,/*!<TIM4global Interrupt*/I2C1_EV_IRQn=31,/*!<I2C1Event Interrupt*/I2C1_ER_IRQn=32,/*!<I2C1Error Interrupt*/I2C2_EV_IRQn=33,/*!<I2C2Event Interrupt*/I2C2_ER_IRQn=34,/*!<I2C2Error Interrupt*/SPI1_IRQn=35,/*!<SPI1global Interrupt*/SPI2_IRQn=36,/*!<SPI2global Interrupt*/ USART1_IRQn=37,/*!<USART1global Interrupt*/ USART2_IRQn=38,/*!<USART2global Interrupt*/ USART3_IRQn=39,/*!<USART3global Interrupt*/ EXTI15_10_IRQn=40,/*!<External Line[15:10]Interrupts*/ RTCAlarm_IRQn=41,/*!<RTC Alarm through EXTI Line Interrupt*/ USBWakeUp_IRQn=42,/*!<USB Device WakeUp from suspend through EXTI Line Interrupt */TIM8_BRK_IRQn=43,/*!<TIM8Break Interrupt*/TIM8_UP_IRQn=44,/*!<TIM8Update Interrupt*/TIM8_TRG_COM_IRQn=45,/*!<TIM8Trigger and Commutation Interrupt*/ TIM8_CC_IRQn=46,/*!<TIM8Capture Compare Interrupt*/ ADC3_IRQn=47,/*!<ADC3global Interrupt*/ FSMC_IRQn=48,/*!<FSMC global Interrupt*/ SDIO_IRQn=49,/*!<SDIO global Interrupt*/TIM5_IRQn=50,/*!<TIM5global Interrupt*/SPI3_IRQn=51,/*!<SPI3global Interrupt*/ UART4_IRQn=52,/*!<UART4global Interrupt*/ UART5_IRQn=53,/*!<UART5global Interrupt*/TIM6_IRQn=54,/*!<TIM6global Interrupt*/TIM7_IRQn=55,/*!<TIM7global Interrupt*/DMA2_Channel1_IRQn=56,/*!<DMA2Channel1global Interrupt*/ DMA2_Channel2_IRQn=57,/*!<DMA2Channel2global Interrupt*/ DMA2_Channel3_IRQn=58,/*!<DMA2Channel3global Interrupt*/ DMA2_Channel4_5_IRQn=59/*!<DMA2Channel4and Channel5global Interrupt*/ #endif/*STM32F10X_HD*/#ifdef STM32F10X_HD_VLADC1_IRQn=18,/*!<ADC1global Interrupt*/ EXTI9_5_IRQn=23,/*!<External Line[9:5]Interrupts*/ TIM1_BRK_TIM15_IRQn=24,/*!<TIM1Break and TIM15Interrupts*/ TIM1_UP_TIM16_IRQn=25,/*!<TIM1Update and TIM16Interrupts*/ TIM1_TRG_COM_TIM17_IRQn=26,/*!<TIM1Trigger and Commutation and TIM17Interrupt*/ TIM1_CC_IRQn=27,/*!<TIM1Capture Compare Interrupt*/ TIM2_IRQn=28,/*!<TIM2global Interrupt*/ TIM3_IRQn=29,/*!<TIM3global Interrupt*/ TIM4_IRQn=30,/*!<TIM4global Interrupt*/I2C1_EV_IRQn=31,/*!<I2C1Event Interrupt*/I2C1_ER_IRQn=32,/*!<I2C1Error Interrupt*/I2C2_EV_IRQn=33,/*!<I2C2Event Interrupt*/I2C2_ER_IRQn=34,/*!<I2C2Error Interrupt*/ SPI1_IRQn=35,/*!<SPI1global Interrupt*/ SPI2_IRQn=36,/*!<SPI2global Interrupt*/ USART1_IRQn=37,/*!<USART1global Interrupt*/ USART2_IRQn=38,/*!<USART2global Interrupt*/ USART3_IRQn=39,/*!<USART3global Interrupt*/ EXTI15_10_IRQn=40,/*!<External Line[15:10]Interrupts*/ RTCAlarm_IRQn=41,/*!<RTC Alarm through EXTI Line Interrupt*/ CEC_IRQn=42,/*!<HDMI-CEC Interrupt*/ TIM12_IRQn=43,/*!<TIM12global Interrupt*/ TIM13_IRQn=44,/*!<TIM13global Interrupt*/ TIM14_IRQn=45,/*!<TIM14global Interrupt*/ TIM5_IRQn=50,/*!<TIM5global Interrupt*/ SPI3_IRQn=51,/*!<SPI3global Interrupt*/ UART4_IRQn=52,/*!<UART4global Interrupt*/ UART5_IRQn=53,/*!<UART5global Interrupt*/ TIM6_DAC_IRQn=54,/*!<TIM6and DAC underrun Interrupt*/ TIM7_IRQn=55,/*!<TIM7Interrupt*/ DMA2_Channel1_IRQn=56,/*!<DMA2Channel1global Interrupt*/ DMA2_Channel2_IRQn=57,/*!<DMA2Channel2global Interrupt*/ DMA2_Channel3_IRQn=58,/*!<DMA2Channel3global Interrupt*/ DMA2_Channel4_5_IRQn=59,/*!<DMA2Channel4and Channel5global Interrupt*/ DMA2_Channel5_IRQn=60/*!<DMA2Channel5global Interrupt(DMA2Channel5ismapped at position60only if the MISC_REMAP bit inthe AFIO_MAPR2register is set)*/#endif/*STM32F10X_HD_VL*/#ifdef STM32F10X_XLADC1_2_IRQn=18,/*!<ADC1and ADC2global Interrupt*/ USB_HP_CAN1_TX_IRQn=19,/*!<USB Device High Priority or CAN1TX Interrupts*/ USB_LP_CAN1_RX0_IRQn=20,/*!<USB Device Low Priority or CAN1RX0Interrupts*/ CAN1_RX1_IRQn=21,/*!<CAN1RX1Interrupt*/CAN1_SCE_IRQn=22,/*!<CAN1SCE Interrupt*/EXTI9_5_IRQn=23,/*!<External Line[9:5]Interrupts*/TIM1_BRK_TIM9_IRQn=24,/*!<TIM1Break Interrupt and TIM9global Interrupt*/ TIM1_UP_TIM10_IRQn=25,/*!<TIM1Update Interrupt and TIM10global Interrupt*/ TIM1_TRG_COM_TIM11_IRQn=26,/*!<TIM1Trigger and Commutation Interrupt and TIM11global interrupt*/TIM1_CC_IRQn=27,/*!<TIM1Capture Compare Interrupt*/TIM2_IRQn=28,/*!<TIM2global Interrupt*/TIM3_IRQn=29,/*!<TIM3global Interrupt*/TIM4_IRQn=30,/*!<TIM4global Interrupt*/I2C1_EV_IRQn=31,/*!<I2C1Event Interrupt*/I2C1_ER_IRQn=32,/*!<I2C1Error Interrupt*/I2C2_EV_IRQn=33,/*!<I2C2Event Interrupt*/I2C2_ER_IRQn=34,/*!<I2C2Error Interrupt*/SPI1_IRQn=35,/*!<SPI1global Interrupt*/SPI2_IRQn=36,/*!<SPI2global Interrupt*/ USART1_IRQn=37,/*!<USART1global Interrupt*/ USART2_IRQn=38,/*!<USART2global Interrupt*/ USART3_IRQn=39,/*!<USART3global Interrupt*/ EXTI15_10_IRQn=40,/*!<External Line[15:10]Interrupts*/ RTCAlarm_IRQn=41,/*!<RTC Alarm through EXTI Line Interrupt*/ USBWakeUp_IRQn=42,/*!<USB Device WakeUp from suspend through EXTI Line Interrupt */TIM8_BRK_TIM12_IRQn=43,/*!<TIM8Break Interrupt and TIM12global Interrupt*/ TIM8_UP_TIM13_IRQn=44,/*!<TIM8Update Interrupt and TIM13global Interrupt*/ TIM8_TRG_COM_TIM14_IRQn=45,/*!<TIM8Trigger and Commutation Interrupt and TIM14global interrupt*/TIM8_CC_IRQn=46,/*!<TIM8Capture Compare Interrupt*/ ADC3_IRQn=47,/*!<ADC3global Interrupt*/ FSMC_IRQn=48,/*!<FSMC global Interrupt*/ SDIO_IRQn=49,/*!<SDIO global Interrupt*/TIM5_IRQn=50,/*!<TIM5global Interrupt*/SPI3_IRQn=51,/*!<SPI3global Interrupt*/ UART4_IRQn=52,/*!<UART4global Interrupt*/ UART5_IRQn=53,/*!<UART5global Interrupt*/TIM6_IRQn=54,/*!<TIM6global Interrupt*/TIM7_IRQn=55,/*!<TIM7global Interrupt*/DMA2_Channel1_IRQn=56,/*!<DMA2Channel1global Interrupt*/ DMA2_Channel2_IRQn=57,/*!<DMA2Channel2global Interrupt*/ DMA2_Channel3_IRQn=58,/*!<DMA2Channel3global Interrupt*/ DMA2_Channel4_5_IRQn=59/*!<DMA2Channel4and Channel5global Interrupt*/#endif/*STM32F10X_XL*/#ifdef STM32F10X_CLADC1_2_IRQn=18,/*!<ADC1and ADC2global Interrupt*/ CAN1_TX_IRQn=19,/*!<USB Device High Priority or CAN1TX Interrupts*/ CAN1_RX0_IRQn=20,/*!<USB Device Low Priority or CAN1RX0Interrupts*/ CAN1_RX1_IRQn=21,/*!<CAN1RX1Interrupt*/CAN1_SCE_IRQn=22,/*!<CAN1SCE Interrupt*/EXTI9_5_IRQn=23,/*!<External Line[9:5]Interrupts*/TIM1_BRK_IRQn=24,/*!<TIM1Break Interrupt*/TIM1_UP_IRQn=25,/*!<TIM1Update Interrupt*/TIM1_TRG_COM_IRQn=26,/*!<TIM1Trigger and Commutation Interrupt*/ TIM1_CC_IRQn=27,/*!<TIM1Capture Compare Interrupt*/TIM2_IRQn=28,/*!<TIM2global Interrupt*/TIM3_IRQn=29,/*!<TIM3global Interrupt*/TIM4_IRQn=30,/*!<TIM4global Interrupt*/I2C1_EV_IRQn=31,/*!<I2C1Event Interrupt*/I2C1_ER_IRQn=32,/*!<I2C1Error Interrupt*/I2C2_EV_IRQn=33,/*!<I2C2Event Interrupt*/I2C2_ER_IRQn=34,/*!<I2C2Error Interrupt*/SPI1_IRQn=35,/*!<SPI1global Interrupt*/SPI2_IRQn=36,/*!<SPI2global Interrupt*/ USART1_IRQn=37,/*!<USART1global Interrupt*/ USART2_IRQn=38,/*!<USART2global Interrupt*/ USART3_IRQn=39,/*!<USART3global Interrupt*/ EXTI15_10_IRQn=40,/*!<External Line[15:10]Interrupts*/ RTCAlarm_IRQn=41,/*!<RTC Alarm through EXTI Line Interrupt*/ OTG_FS_WKUP_IRQn=42,/*!<USB OTG FS WakeUp from suspend through EXTI Line Interrupt */TIM5_IRQn=50,/*!<TIM5global Interrupt*/SPI3_IRQn=51,/*!<SPI3global Interrupt*/ UART4_IRQn=52,/*!<UART4global Interrupt*/ UART5_IRQn=53,/*!<UART5global Interrupt*/TIM6_IRQn=54,/*!<TIM6global Interrupt*/TIM7_IRQn=55,/*!<TIM7global Interrupt*/DMA2_Channel1_IRQn=56,/*!<DMA2Channel1global Interrupt*/ DMA2_Channel2_IRQn=57,/*!<DMA2Channel2global Interrupt*/ DMA2_Channel3_IRQn=58,/*!<DMA2Channel3global Interrupt*/ DMA2_Channel4_IRQn=59,/*!<DMA2Channel4global Interrupt*/ DMA2_Channel5_IRQn=60,/*!<DMA2Channel5global Interrupt*/ETH_IRQn=61,/*!<Ethernet global Interrupt*/ ETH_WKUP_IRQn=62,/*!<Ethernet Wakeup through EXTI line Interrupt*/ CAN2_TX_IRQn=63,/*!<CAN2TX Interrupt*/ CAN2_RX0_IRQn=64,/*!<CAN2RX0Interrupt*/ CAN2_RX1_IRQn=65,/*!<CAN2RX1Interrupt*/ CAN2_SCE_IRQn=66,/*!<CAN2SCE Interrupt*/ OTG_FS_IRQn=67/*!<USB OTG FS global Interrupt*/ #endif/*STM32F10X_CL*/}IRQn_Type;。

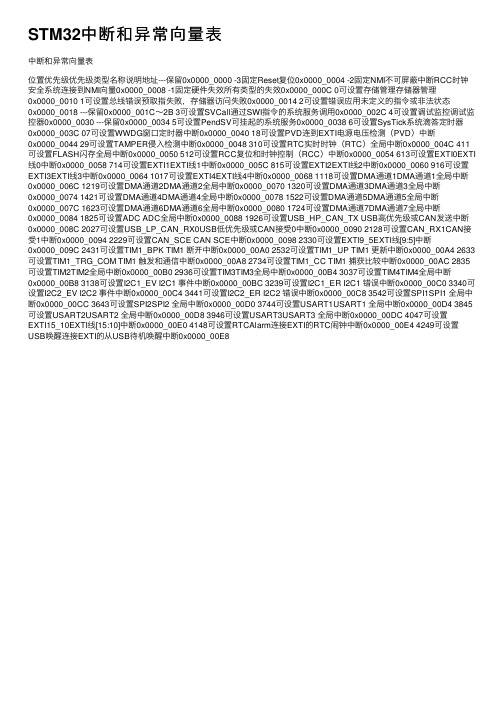

STM32中断和异常向量表中断和异常向量表位置优先级优先级类型名称说明地址---保留0x0000_0000 -3固定Reset复位0x0000_0004 -2固定NMI不可屏蔽中断RCC时钟安全系统连接到NMI向量0x0000_0008 -1固定硬件失效所有类型的失效0x0000_000C 0可设置存储管理存储器管理0x0000_0010 1可设置总线错误预取指失败,存储器访问失败0x0000_0014 2可设置错误应⽤未定义的指令或⾮法状态0x0000_0018 ---保留0x0000_001C~2B 3可设置SVCall通过SWI指令的系统服务调⽤0x0000_002C 4可设置调试监控调试监控器0x0000_0030 ---保留0x0000_0034 5可设置PendSV可挂起的系统服务0x0000_0038 6可设置SysTick系统滴答定时器0x0000_003C 07可设置WWDG窗⼝定时器中断0x0000_0040 18可设置PVD连到EXTI电源电压检测(PVD)中断0x0000_0044 29可设置TAMPER侵⼊检测中断0x0000_0048 310可设置RTC实时时钟(RTC)全局中断0x0000_004C 411可设置FLASH闪存全局中断0x0000_0050 512可设置RCC复位和时钟控制(RCC)中断0x0000_0054 613可设置EXTI0EXTI 线0中断0x0000_0058 714可设置EXTI1EXTI线1中断0x0000_005C 815可设置EXTI2EXTI线2中断0x0000_0060 916可设置EXTI3EXTI线3中断0x0000_0064 1017可设置EXTI4EXTI线4中断0x0000_0068 1118可设置DMA通道1DMA通道1全局中断0x0000_006C 1219可设置DMA通道2DMA通道2全局中断0x0000_0070 1320可设置DMA通道3DMA通道3全局中断0x0000_0074 1421可设置DMA通道4DMA通道4全局中断0x0000_0078 1522可设置DMA通道5DMA通道5全局中断0x0000_007C 1623可设置DMA通道6DMA通道6全局中断0x0000_0080 1724可设置DMA通道7DMA通道7全局中断0x0000_0084 1825可设置ADC ADC全局中断0x0000_0088 1926可设置USB_HP_CAN_TX USB⾼优先级或CAN发送中断0x0000_008C 2027可设置USB_LP_CAN_RX0USB低优先级或CAN接受0中断0x0000_0090 2128可设置CAN_RX1CAN接受1中断0x0000_0094 2229可设置CAN_SCE CAN SCE中断0x0000_0098 2330可设置EXTI9_5EXTI线[9:5]中断0x0000_009C 2431可设置TIM1_BPK TIM1 断开中断0x0000_00A0 2532可设置TIM1_UP TIM1 更新中断0x0000_00A4 2633可设置TIM1_TRG_COM TIM1 触发和通信中断0x0000_00A8 2734可设置TIM1_CC TIM1 捕获⽐较中断0x0000_00AC 2835可设置TIM2TIM2全局中断0x0000_00B0 2936可设置TIM3TIM3全局中断0x0000_00B4 3037可设置TIM4TIM4全局中断0x0000_00B8 3138可设置I2C1_EV I2C1 事件中断0x0000_00BC 3239可设置I2C1_ER I2C1 错误中断0x0000_00C0 3340可设置I2C2_EV I2C2 事件中断0x0000_00C4 3441可设置I2C2_ER I2C2 错误中断0x0000_00C8 3542可设置SPI1SPI1 全局中断0x0000_00CC 3643可设置SPI2SPI2 全局中断0x0000_00D0 3744可设置USART1USART1 全局中断0x0000_00D4 3845可设置USART2USART2 全局中断0x0000_00D8 3946可设置USART3USART3 全局中断0x0000_00DC 4047可设置EXTI15_10EXTI线[15:10]中断0x0000_00E0 4148可设置RTCAlarm连接EXTI的RTC闹钟中断0x0000_00E4 4249可设置USB唤醒连接EXTI的从USB待机唤醒中断0x0000_00E8。

外部中断(zhōngduàn)的初始化过程:1.初始化IO为输入(shūrù)(可以设置上拉,下拉,浮空)2.开启(kāiqǐ)IO复用(fù yònɡ)时钟3.开启(kāiqǐ)与该IO相对的线上(详解下)4.配置NVIC,使能中断5.编写中断服务函数外部中断:Stm32中总共有19个外部中断包括:线0-15:IO输入中断(每条线上最多有7个IO,如GPIOA~GPIOG,但是每一条线每次只允许同时连接到一个IO)线16:PVD线17:RTC线18:USB关于(guānyú)优先级:CM3中内核(nèi hé)支持256个中断(zhōngduàn)(16个内核(nèi hé)+240外部(wàibù))和可编程256级中断优先级的设置Stm32目前(mùqián)支持84个中断(zhōngduàn)(16个内核(nèi hé)+68个外部(wàibù),注:不是(bù shi)指68个外部中断),16级可编程优先级(优先级设置寄存器中使用了4位)注意:其中(qízhōng)外部中断5-9和中断(zhōngduàn)10-15向量存放(cúnfàng)在一起优先级:数值(shùzí)低的优先级要高于数值高的!!!!!!上电复位后,系统默认(mòrèn)使用的是组0;一个系统只能使用一组优先级组,不可使用多个,优先级的设置不能超过组的范围,否则会产生不可预计的错误1.高抢先级的中断可以打断低优先级的中断响应,构成中断嵌套2.相同抢先级的中断不可以构成嵌套,系统会优先响应子优先级高的3.当2(n)个相同抢先优先级和相同子优先级的中断(zhōngduàn)出现,STM32首先响应中断通道所对应的中断向量地址(dìzhǐ)低的那个中断4.0号抢先优先级的中断,可以(kěyǐ)打断任何中断抢先优先级为非0号的中断(zhōngduàn);1号抢先优先级的中断(zhōngduàn),可以打断任何中断抢先优先级为2、3、4号的中断;……;构成中断嵌套。

STM32 中断向量表的位置、重定向我们也知道怎么跳到main 函数了,那么,中断发生后,又是怎么跑到中断入口地址的呢?从stm32f10x.s 可以看到,已经定义好了一大堆的中断响应函数,这就是中断向量表,标号__Vectors,表示中断向量表入口地址,例如:AREA RESET, DATA, READONLY ;定义只读数据段,实际上是在CODE区(假设STM32 从FLASH 启动,则此中断向量表起始地址即为0x8000000)EXPORT __VectorsIMPORT OS_CPU_SysTickHandler IMPORTOS_CPU_PendSVHandler__Vectors DCD __initial_sp ; Top of Stack DCD Reset_Handler ; Reset Handler DCD NMI_Handler ; NMI Handler DCD HardFault_Handler ; Hard Fault Handler DCD MemManage_Handler ; MPU Fault Handler DCD BusFault_Handler ; Bus Fault Handler DCD UsageFault_Handler ; Usage Fault Handler这个向量表的编写是有讲究的,跟硬件一一对应不能乱写的,CPU 找入口地址就靠它了,bin 文件开头就是他们的地址,参考手册RM0008 的10.1.2 节可以看到排列。

我们再结合CORTEX-M3 的特性,他上电后根据boot 引脚来决定PC 位置,比如boot 设置为flash 启动,则启动后PC 跳到0x08000000。

此时CPU 会先取2 个地址,第一个是栈顶地址,第二个是复位异常地址,故有了上面的写法,这样就跳到reset_handler。

那么这个reset_handler 的实际地址是多少.?下面的一堆例如Nmi_handler 地址又是多少呢?发生中断是怎么跑到这个地址的呢?下面挨个讲解。

STM32 学习记录12 中断向量表从stm32f10x.s 可以看到,已经定义好了一大堆的中断响应函数,这就是中断向量表,标号__Vectors,表示中断向量表入口地址,例如:AREA RESET, DATA, READONLY ;定义只读数据段,实际上是在CODE 区(假设STM32 从FLASH 启动,则此中断向量表起始地址即为0x8000000)EXPORT__VectorsIMPORT OS_CPU_SysTickHandler IMPORTOS_CPU_PendSVHandler__Vectors DCD __initial_sp ; Top of Stack DCD Reset_Handler ; Reset Handler DCD NMI_Handler ; NMI Handler DCD HardFault_Handler ; Hard Fault Handler DCD MemManage_Handler ; MPU Fault Handler DCD BusFault_Handler ; Bus Fault Handler DCD UsageFault_Handler ; Usage Fault Handler这个向量表的编写是有讲究的,跟硬件一一对应不能乱写的,CPU 找入口地址就靠它了,bin 文件开头就是他们的地址,参考手册RM0008 的10.1.2 节可以看到排列。

我们再结合CORTEX-M3 的特性,他上电后根据boot 引脚来决定PC 位置,比如boot 设置为flash 启动,则启动后PC 跳到0x08000000。

此时CPU 会先取2 个地址,第一个是栈顶地址,第二个是复位异常地址,故有了上面的写法,这样就跳到reset_handler。

那么这个reset_handler 的实际地址是多少.?下面的一堆例如Nmi_handler 地址又是多少呢?发生中断是怎么跑到这个地址的呢?下面挨个讲解。

在STM32微控制器上使用FreeRTOS实时操作系统时,中断服务例程(ISR)的写法需要遵循一定的规范,以确保中断处理能够在不同的任务之间正确地进行。

以下是一些基本步骤和注意事项,用于在FreeRTOS中实现中断服务例程:1. **中断向量表初始化**:在系统启动时,需要初始化中断向量表,将中断处理函数的地址映射到相应的中断号上。

2. **中断优先级设置**:在FreeRTOS中,可以通过NVIC(嵌套向量中断控制器)设置中断的优先级。

在中断服务例程中,可以使用`HAL_NVIC_SetPriority`函数设置优先级。

3. **中断使能**:在中断服务例程编写完成后,需要使用`HAL_NVIC_EnableIRQ`或`HAL_NVIC_Enable`函数使能中断。

4. **中断服务例程的原型**:中断服务例程应该有一个原型,其中包含了中断号和中断服务例程的函数指针。

5. **在中断服务例程中保护现场**:在进入中断服务例程之前,应该保存CPU的状态,包括程序计数器和其他必要的寄存器,以防止中断服务例程被其他中断打断。

6. **中断服务例程的退出**:在中断服务例程结束时,应该恢复之前保存的状态,并使用`HAL_NVIC_DisableIRQ`或`HAL_NVIC_Disable`函数禁用中断。

7. **使用FreeRTOS的API**:如果需要在中断服务例程中使用FreeRTOS的API,比如创建任务、等待消息等,应该确保这些操作不会导致中断被禁止的时间过长,以免影响系统的响应性。

以下是一个简单的STM32中断服务例程的示例代码:```cvoid EXTI0_IRQHandler(void) {// 保存状态HAL_NVIC_DisableIRQ(EXTI0_IRQn); // 禁用中断// 中断处理逻辑// ...// 恢复状态HAL_NVIC_EnableIRQ(EXTI0_IRQn); // 使能中断} ```。

#define WWDG_IRQChannel ((u8)0x00) /* Window WatchDog Interrupt */#define PVD_IRQChannel ((u8)0x01) /* PVD through EXTI Line detection Interrupt */#define TAMPER_IRQChannel ((u8)0x02) /* Tamper Interrupt */#define RTC_IRQChannel ((u8)0x03) /* RTC global Interrupt */#define FLASH_IRQChannel ((u8)0x04) /* FLASH global Interrupt */#define RCC_IRQChannel ((u8)0x05) /* RCC global Interrupt */#define EXTI0_IRQChannel ((u8)0x06) /* EXTI Line0 Interrupt */#define EXTI1_IRQChannel ((u8)0x07) /* EXTI Line1 Interrupt */#define EXTI2_IRQChannel ((u8)0x08) /* EXTI Line2 Interrupt */#define EXTI3_IRQChannel ((u8)0x09) /* EXTI Line3 Interrupt */#define EXTI4_IRQChannel ((u8)0x0A) /* EXTI Line4 Interrupt */#define DMA1_Channel1_IRQChannel ((u8)0x0B) /* DMA1 Channel 1 global Interrupt */#define DMA1_Channel2_IRQChannel ((u8)0x0C) /* DMA1 Channel 2 global Interrupt */#define DMA1_Channel3_IRQChannel ((u8)0x0D) /* DMA1 Channel 3 global Interrupt */#define DMA1_Channel4_IRQChannel ((u8)0x0E) /* DMA1 Channel 4 global Interrupt */#define DMA1_Channel5_IRQChannel ((u8)0x0F) /* DMA1 Channel 5 global Interrupt */#define DMA1_Channel6_IRQChannel ((u8)0x10) /* DMA1 Channel 6 global Interrupt */#define DMA1_Channel7_IRQChannel ((u8)0x11) /* DMA1 Channel 7 global Interrupt */#define ADC1_2_IRQChannel ((u8)0x12) /* ADC1 et ADC2 global Interrupt */#define USB_HP_CAN_TX_IRQChannel ((u8)0x13) /* USB High Priority or CAN TX Interrupts */#define USB_LP_CAN_RX0_IRQChannel ((u8)0x14) /* USB Low Priority or CAN RX0 Interrupts */#define CAN_RX1_IRQChannel ((u8)0x15) /* CAN RX1 Interrupt */#define CAN_SCE_IRQChannel ((u8)0x16) /* CAN SCE Interrupt */#define EXTI9_5_IRQChannel ((u8)0x17) /* External Line[9:5] Interrupts */#define TIM1_BRK_IRQChannel ((u8)0x18) /* TIM1 Break Interrupt */#define TIM1_UP_IRQChannel ((u8)0x19) /* TIM1 Update Interrupt */#define TIM1_TRG_COM_IRQChannel ((u8)0x1A) /* TIM1 Trigger and Commutation Interrupt */#define TIM1_CC_IRQChannel ((u8)0x1B) /* TIM1 Capture Compare Interrupt */#define TIM2_IRQChannel ((u8)0x1C) /* TIM2 global Interrupt */#define TIM3_IRQChannel ((u8)0x1D) /* TIM3 global Interrupt */#define TIM4_IRQChannel ((u8)0x1E) /* TIM4 global Interrupt */#define I2C1_EV_IRQChannel ((u8)0x1F) /* I2C1 Event Interrupt */#define I2C1_ER_IRQChannel ((u8)0x20) /* I2C1 Error Interrupt */#define I2C2_EV_IRQChannel ((u8)0x21) /* I2C2 Event Interrupt */#define I2C2_ER_IRQChannel ((u8)0x22) /* I2C2 Error Interrupt */#define SPI1_IRQChannel ((u8)0x23) /* SPI1 global Interrupt */#define SPI2_IRQChannel ((u8)0x24) /* SPI2 global Interrupt */#define USART1_IRQChannel ((u8)0x25) /* USART1 global Interrupt */#define USART2_IRQChannel ((u8)0x26) /* USART2 global Interrupt */#define USART3_IRQChannel ((u8)0x27) /* USART3 global Interrupt */#define EXTI15_10_IRQChannel ((u8)0x28) /* External Line[15:10] Interrupts */#define RTCAlarm_IRQChannel ((u8)0x29) /* RTC Alarm through EXTI Line Interrupt */#define USBWakeUp_IRQChannel ((u8)0x2A) /* USB WakeUp from suspend through EXTI Line Interrupt */#define TIM8_BRK_IRQChannel ((u8)0x2B) /* TIM8 Break Interrupt */#define TIM8_UP_IRQChannel ((u8)0x2C) /* TIM8 Update Interrupt */#define TIM8_TRG_COM_IRQChannel ((u8)0x2D) /* TIM8 Trigger and Commutation Interrupt */#define TIM8_CC_IRQChannel ((u8)0x2E) /* TIM8 Capture Compare Interrupt */#define ADC3_IRQChannel ((u8)0x2F) /* ADC3 global Interrupt */#define FSMC_IRQChannel ((u8)0x30) /* FSMC global Interrupt */#define SDIO_IRQChannel ((u8)0x31) /* SDIO global Interrupt */#define TIM5_IRQChannel ((u8)0x32) /* TIM5 global Interrupt */#define SPI3_IRQChannel ((u8)0x33) /* SPI3 global Interrupt */#define UART4_IRQChannel ((u8)0x34) /* UART4 global Interrupt */#define UART5_IRQChannel ((u8)0x35) /* UART5 global Interrupt */#define TIM6_IRQChannel ((u8)0x36) /* TIM6 global Interrupt */#define TIM7_IRQChannel ((u8)0x37) /* TIM7 global Interrupt */#define DMA2_Channel1_IRQChannel ((u8)0x38) /* DMA2 Channel 1 global Interrupt */#define DMA2_Channel2_IRQChannel ((u8)0x39) /* DMA2 Channel 2 global Interrupt */#define DMA2_Channel3_IRQChannel ((u8)0x3A) /* DMA2 Channel 3 global Interrupt */#define DMA2_Channel4_5_IRQChannel ((u8)0x3B) /* DMA2 Channel 4 and DMA2 Channel 5 global Interrupt */。