基于DSP2407的单相软件锁相环的实现

- 格式:pdf

- 大小:211.40 KB

- 文档页数:3

一种基于DSP的软件锁相环模型与实现随着大规模集成电路及高速数字信号处理器的发展,通信领域的信号处理越来越多地在数字域付诸实现。

软件锁相技术是随着软件无线电的发展和高速DSP的出现而开展起来的一个研究课题。

在软件无线电接收机中采用的锁相技术是基于数字信号处理技术在DSP等通用可编程器件上的实现形式,由于这一类型锁相环的功能主要通过软件编程实现,因此可将其称为软件锁相环(software PLL)[1]。

尽管软件锁相环采用的基本算法思想与模拟锁相环和数字锁相环相比并没有太大变化,然而其实现方式却完全不同。

本文将建立软件锁相环的Z 域模型,分析软件锁相环中的延时估计、捕获速度及多速率条件下的软件锁相环模型问题[1]。

1软件锁相环的基本模型在模拟锁相环的基础上,利用数字、模拟系统彼此之间的联系,以二阶二型锁相环为例建立软件锁相环的Z 域模型。

文献[2]详细给出了锁相环的基本模型和原理。

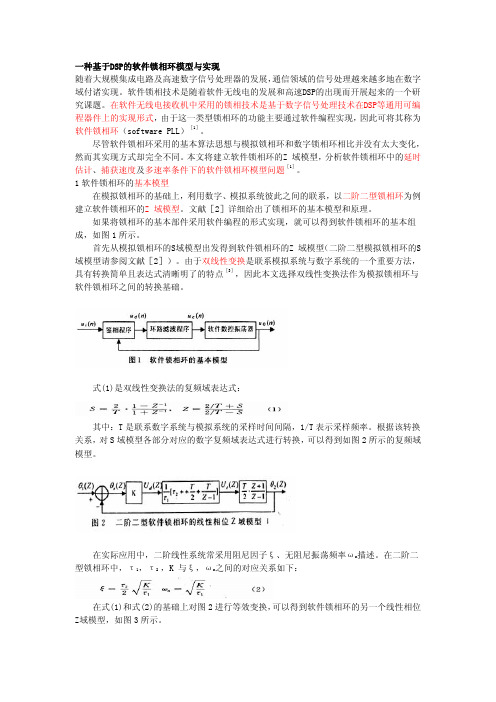

如果将锁相环的基本部件采用软件编程的形式实现,就可以得到软件锁相环的基本组成,如图1所示。

首先从模拟锁相环的S域模型出发得到软件锁相环的Z 域模型(二阶二型模拟锁相环的S 域模型请参阅文献[2])。

由于双线性变换是联系模拟系统与数字系统的一个重要方法,具有转换简单且表达式清晰明了的特点[3],因此本文选择双线性变换法作为模拟锁相环与软件锁相环之间的转换基础。

式(1)是双线性变换法的复频域表达式:其中:T是联系数字系统与模拟系统的采样时间间隔,1/T表示采样频率。

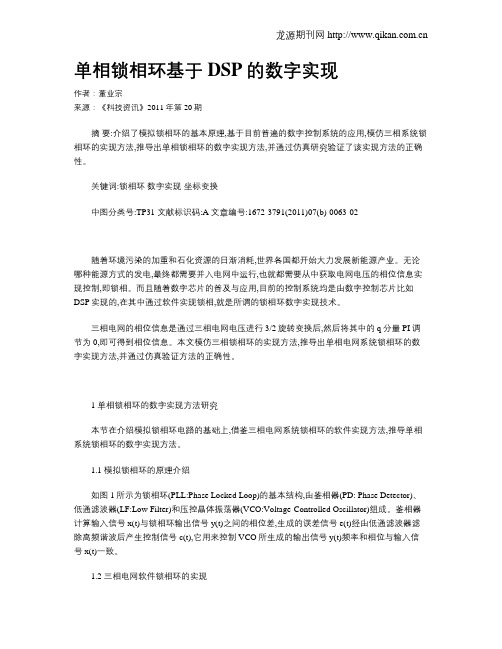

根据该转换关系,对S域模型各部分对应的数字复频域表达式进行转换,可以得到如图2所示的复频域模型。

在实际应用中,二阶线性系统常采用阻尼因子ξ、无阻尼振荡频率ωn描述。

在二阶二型锁相环中,τ1,τ2 ,K 与ξ,ωn之间的对应关系如下:在式(1)和式(2)的基础上对图2进行等效变换,可以得到软件锁相环的另一个线性相位Z域模型,如图3所示。

在模型Ⅰ中,参数τ1,τ2和K与实现电路功能的电阻、电容、压控振荡器密切相关。

单相锁相环基于DSP的数字实现作者:董业宗来源:《科技资讯》2011年第20期摘要:介绍了模拟锁相环的基本原理,基于目前普遍的数字控制系统的应用,模仿三相系统锁相环的实现方法,推导出单相锁相环的数字实现方法,并通过仿真研究验证了该实现方法的正确性。

关键词:锁相环数字实现坐标变换中图分类号:TP31 文献标识码:A 文章编号:1672-3791(2011)07(b)-0063-02随着环境污染的加重和石化资源的日渐消耗,世界各国都开始大力发展新能源产业。

无论哪种能源方式的发电,最终都需要并入电网中运行,也就都需要从中获取电网电压的相位信息实现控制,即锁相。

而且随着数字芯片的普及与应用,目前的控制系统均是由数字控制芯片比如DSP实现的,在其中通过软件实现锁相,就是所谓的锁相环数字实现技术。

三相电网的相位信息是通过三相电网电压进行3/2旋转变换后,然后将其中的q分量PI调节为0,即可得到相位信息。

本文模仿三相锁相环的实现方法,推导出单相电网系统锁相环的数字实现方法,并通过仿真验证方法的正确性。

1 单相锁相环的数字实现方法研究本节在介绍模拟锁相环电路的基础上,借鉴三相电网系统锁相环的软件实现方法,推导单相系统锁相环的数字实现方法。

1.1 模拟锁相环的原理介绍如图1所示为锁相环(PLL:Phase Locked Loop)的基本结构,由鉴相器(PD: Phase Detector)、低通滤波器(LF:Low Filter)和压控晶体振荡器(VCO:Voltage-Controlled Oscillator)组成。

鉴相器计算输入信号x(t)与锁相环输出信号y(t)之间的相位差,生成的误差信号e(t)经由低通滤波器滤除高频谐波后产生控制信号c(t),它用来控制VCO所生成的输出信号y(t)频率和相位与输入信号x(t)一致。

1.2 三相电网软件锁相环的实现如图1所示的模拟锁相环电路能够实现输出信号对输入信号频率和相位的追踪。

基于DSP2407的单相软件锁相环的实现

徐耀

【期刊名称】《通信电源技术》

【年(卷),期】2010(027)006

【摘要】软件锁相环(SPLL)是用软件来实现模拟锁相环的功能,已广泛地运用到光伏并网逆变器和电机的控制中,在数字信号处理器(DSP)时代,用DSP实现软件锁相环比较容易.文中介绍了一种基于DSP2407的单相软件锁相环的实现方法,使相位差控制在0~1℃范围内.

【总页数】3页(P36-38)

【作者】徐耀

【作者单位】上海海事大学,上海,200135

【正文语种】中文

【中图分类】TM461.5

【相关文献】

1.基于DSP2407变频调速控制系统的设计与实现 [J], 张文婷

2.基于DSP的高精度单相软件锁相环的实现 [J], 张启亮;刘倩影

3.新型单相软件锁相环的研究 [J], 董祖毅;陈国栋

4.一种基于软件锁相环实现位同步的设计 [J], 张素琴

5.一种单相光伏并网逆变器软件锁相环的设计与实现 [J], 尧永;方宇;葛亚华;王明南;张继勇;

因版权原因,仅展示原文概要,查看原文内容请购买。

一、设计要求要求设计的最小系统包括TMS320LF2407A基本电路、电源电路、扩展RAM、指示灯等部分,需要用protel软件完成原理图和PCB的设计,并编写验证程序,在实验箱上进行调试。

二、设计原理及框图对于DSP2407,加上电源、复位和晶振,就构成了DSP最小系统。

为使这一最小系统能工作在开发状态下,应配以锁相环、JTAG接口、扩展片外程序存储器、FLASH烧写、指示灯、引脚扩展以及对其他引脚的处理等电路。

DSP2407最小系统框图如下图所示:三、主要芯片说明3.1 TMS320LF2407ATMS320LF2407A的常用资源见下表:3.2 TPS7333QTPS7333Q是TI公司生产的一款电压转换芯片,能将5V电压转换成3.3V,其特点如下:1.TPS7333Q克服了常规LDO稳压器的弊端,它具有非常低的静态电流,即使对于变化较大的负载,静态电流可以保持稳定2.具有关断特性3.具有输入和输出电容的选择3.3 CY7C1021选用的RAM型号为CY7C1021,64k*16位大小。

其高速转换时间:8、10、12、15ns,CMOS低功耗管理,TTL可共存界面,由3.3V供电,完全静态管理:无时钟或刷新要求,三种输出状态,高位、低位数据控制3.4 MAX811MAX811是一款四管脚微处理器复位芯片,用于监控微控制器和其他逻辑系统的电源电压,带有手动复位输入低电平复位芯片,支持手动复位功能,当MR引脚持续存在180ms的低电平,芯片的复位输出即会产生复位信号。

3.5 74HC0874HC08是4-2输入与门,相当于四个两输入与门。

其逻辑图如下:引脚图为四、设计过程4.1 电源电路电源电路的选择是系统设计的一个重要的部分,设计好坏对系统的影响最大。

这里使用TI公司的TPS7333Q来设计电源供电电路。

电源插孔J1 标识为内正外负,5V 稳压直流电源输入。

FUSE 为自恢复保险;7333 电源转换芯片作为5V 转3.3V 的高性能稳压芯片。

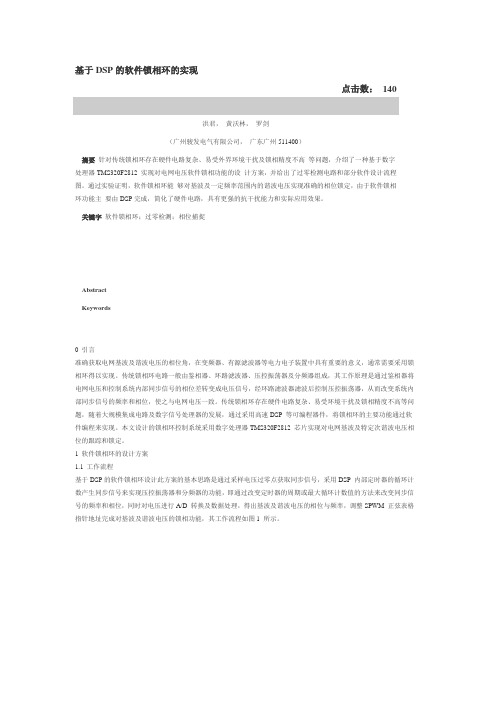

基于DSP的软件锁相环的实现点击数:140洪君,黄沃林,罗剑(广州骏发电气有限公司,广东广州511400)摘要针对传统锁相环存在硬件电路复杂、易受外界环境干扰及锁相精度不高等问题,介绍了一种基于数字处理器TMS320F2812 实现对电网电压软件锁相功能的设计方案,并给出了过零检测电路和部分软件设计流程图。

通过实验证明,软件锁相环能够对基波及一定频率范围内的谐波电压实现准确的相位锁定,由于软件锁相环功能主要由DSP完成,简化了硬件电路,具有更强的抗干扰能力和实际应用效果。

关键字软件锁相环;过零检测;相位捕捉AbstractKeywords0 引言准确获取电网基波及谐波电压的相位角,在变频器、有源滤波器等电力电子装置中具有重要的意义,通常需要采用锁相环得以实现。

传统锁相环电路一般由鉴相器、环路滤波器、压控振荡器及分频器组成,其工作原理是通过鉴相器将电网电压和控制系统内部同步信号的相位差转变成电压信号,经环路滤波器滤波后控制压控振荡器,从而改变系统内部同步信号的频率和相位,使之与电网电压一致。

传统锁相环存在硬件电路复杂、易受环境干扰及锁相精度不高等问题,随着大规模集成电路及数字信号处理器的发展,通过采用高速DSP 等可编程器件,将锁相环的主要功能通过软件编程来实现。

本文设计的锁相环控制系统采用数字处理器TMS320F2812 芯片实现对电网基波及特定次谐波电压相位的跟踪和锁定。

1 软件锁相环的设计方案1.1 工作流程基于DSP的软件锁相环设计此方案的基本思路是通过采样电压过零点获取同步信号,采用DSP 内部定时器的循环计数产生同步信号来实现压控振荡器和分频器的功能,即通过改变定时器的周期或最大循环计数值的方法来改变同步信号的频率和相位,同时对电压进行A/D 转换及数据处理,得出基波及谐波电压的相位与频率,调整SPWM 正弦表格指针地址完成对基波及谐波电压的锁相功能,其工作流程如图1 所示。

通常,过零信号可以通过检测电网三相电压中任一相的过零点获取。

基于定点DSP的软件锁相环的设计和实现摘要软件锁相环是软件接收机中执行载波恢复功能的关键部分。

提出了一种48位定点扩展精度的算法,可以有效地实现软件锁相环。

与浮点算法比较,能极大地降低的运算量,降低功耗,同时保证动态范围运算精度。

关键词低轨道卫星软件接收机软件锁相环定点扩展精度算法低轨小卫星通信是近年来卫星通信应用中一个方兴未艾的重要领域,"创新一号"小卫星是我国研制的具有完全自主知识产权的存储与转发通信小卫星,手持终端是专门为这颗小卫星研制的低功耗地面手持通信终端,支持调制数据速率达76.8的窄带信道。

基于公司的低功耗16位定点数字信号处理器3205510最高运算能力为200,完全用软件实现低中频数字接收机,其中包括执行载波恢复功能的软件锁相环--。

在用浮点算法实现软件锁相环时,由于3205510是一个定点处理器;没有浮点处理单元,只能用编译器产生模拟浮点运算的指令,运算量需要67.2,效率很低,因此需要一种能在3205510上执行的定点算法,有效地降低运算量。

本文提出了一种48位定点扩展精度算法实现,提高了效率,减少了运算量,同时保证了环路计算的精度和动态范围。

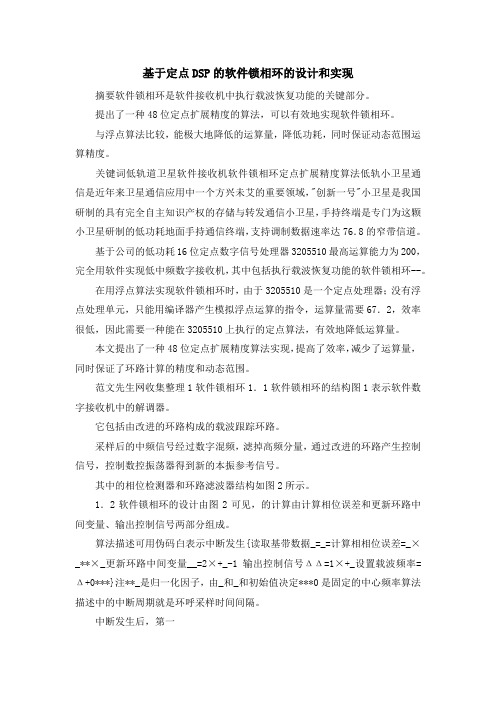

范文先生网收集整理1软件锁相环1.1软件锁相环的结构图1表示软件数字接收机中的解调器。

它包括由改进的环路构成的载波跟踪环路。

采样后的中频信号经过数字混频,滤掉高频分量,通过改进的环路产生控制信号,控制数控振荡器得到新的本振参考信号。

其中的相位检测器和环路滤波器结构如图2所示。

1.2软件锁相环的设计由图2可见,的计算由计算相位误差和更新环路中间变量、输出控制信号两部分组成。

算法描述可用伪码白表示中断发生{读取基带数据_=_=计算相相位误差=_×_**×_更新环路中间变量__=2×+_-1输出控制信号ΔΔ=1×+_设置载波频率=Δ+0***}注**_是归一化因子,由_和_和初始值决定***0是固定的中心频率算法描述中的中断周期就是环呼采样时间间隔。

锁相环的研究与设计——用于DSP芯片时钟发生器

的开题报告

一、研究背景

随着现代数字信号处理技术的日益成熟,数字信号处理(DSP)芯片在通信、音视频处理、图像处理等领域得到了广泛应用。

因为DSP芯片需要精确的时钟信号来同步各个模块之间的数据传输,常用的时钟发生器是基于晶振的,然而晶振的频率稳定性和精度难以满足高精度时钟信号的要求。

锁相环(PLL)是一种常用的时钟发生器,用于将一个参考时钟信号锁定到设定频率的输出时钟信号。

锁相环可以提供相对于晶振更高的频率稳定性和精度,适用于DSP芯片的时钟信号发生器。

二、研究内容

本论文将重点研究锁相环的理论原理与设计方法,并将其应用于DSP芯片的时钟发生器中。

主要研究内容包括:

1. 锁相环的基本结构和原理。

重点分析锁相环中的相位检测器、环路滤波器和控制电路等核心组成部分,并探讨其作用和影响因素。

2. 锁相环的设计方法。

基于理论分析和电路实现,设计一种高性能的锁相环,包括参数选取、电路布局和仿真验证等环节。

3. DSP芯片时钟发生器的整体设计。

将锁相环与其他电路模块相结合,构建一个完整的DSP芯片时钟发生器,并对其进行整体性能测试与验证。

三、研究意义

本论文的研究结果可以为DSP芯片时钟发生器的设计与制造提供参考,并为相关领域的进一步研究提供理论基础和实践经验。

同时,本研究探讨的锁相环设计方法可适用于其他电子设备中时钟发生器的设计与制造,具有一定的普适性和推广价值。

基于DSP的软件锁相环的设计李进兵荣雅君董杰安刚虎燕山大学电气工程学院河北秦皇岛066004摘要文中分析了锁相环的工作原理和锁相环软件设计流程,设计了基于数字信号处理器TMS320LF2407A的数字锁相环,给出了锁相环程序流程图和部分程序,并给出了实验结果。

关键词锁相环,DSP,逆变电源1.引言在逆变器并网控制系统中,为了保证逆变器输出电流和电网电压同相,一般要采用锁相环(PLL—Phase Locked Loop)技术。

常用的模拟锁相环主要由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VC0)组成,如图1所示。

鉴相器比较输入信号Vi和压控振荡器的输出信号Vo之间的相位差,完成相位差--电压变换。

环路滤波器的作用是滤除鉴相器输出信号Vd中的高频分量和其它干扰分量。

压控振荡器的振荡频率受环路滤波器输出电压Vc的控制,实现电压--频率的变换。

从而完成锁相的功能。

图1 锁相环原理图传统的锁相方法电路复杂且精度不高,以高速DSP芯片实现的数字方法与模拟方法相比有如下优点:智能化程度更高,性能更加完美:控制灵活,甚至可以在线修改控制算法,而不必对硬件电路做改动;可靠性高;维护方便,一旦出现故障,可以很方便地进行在线调试。

因此,本文设计的锁相控制系统采用TI公司TMS320LF2407A芯片来实现对市电的跟踪。

2.锁相控制的设计与实现一般软件锁相环的程序流程图如2图所示图2 软件锁相环国家自然科学基金项目(资助号:50237020)2.1 市电频率信号波形整形电路由于DSPLF2407A的参考电压为3.3伏需要通过硬件电路将220伏电压转化成3.3伏的方波。

本文利用一个迟滞比较器把输入整形为一个和输入同频同相的矩形波,然后利用该波形在软件上进行频率和相位跟踪。

具体实现电路如图3所示。

整定电路的输出波形如图4所示。

图3 市电频率信号波形整定电路图4 整定电路输出波形2.2 SPWM波的发生逆变器输出电压基准正弦信号需要由DSP给出。