正交信号发生器的设计与实现

- 格式:docx

- 大小:36.82 KB

- 文档页数:2

课程设计报告课程设计题目:双路正交IQ信号发生器学院:专业:通信工程班级:姓名:学号:指导老师:2011年07月08日摘要电子线路中,在无需外加激励信号的情况下,能将直流电能转换成具有一定波形、一定频率和一定幅度的交变能量的电子电路称为信号发生器。

本课程设计中要求实现一频率为10Mhz的信号源,故为高频信号发生器。

高频信号发生器主要是产生高频正弦震荡波,电路主要由高频振荡电路构成。

振荡器是一种能自动地将直流电源能量转换为一定波形的交变振荡信号能量的转换电路。

它无需外加激励信号。

常用正弦波振荡器主要由决定振荡频率的选频网络和维持振荡的正反馈放大器组成,这就是反馈振荡器。

按照选频网络所采用元件的不同,正弦波振荡器可分为LC振荡器、RC振荡器和晶体振荡器等类型。

其中LC振荡器和晶体振荡器用于产生高频正弦波。

正反馈放大器既可以由晶体管、场效应管等分立器件组成,也可以由集成电路组成。

根据所产生的波形不同,可将振荡器分成正弦波振荡器和非正弦波振荡器两大类。

前者能产生正弦波,后者能产生矩形波、三角波、锯齿波等。

使用运算放大器组成的微分电路可实现正弦波相移90度,产生余弦波,两路信号形成双路正交信号。

在本课程设计中,着眼于无线电通信的基础电路——LC正弦振荡器的分析和研究。

通过对电容反馈式三端振荡器以及改进型电容反馈式振荡器(西勒电路)的分析、对比和讨论。

以求得到一些对实际应用电路有帮助的结论。

在课程设计中,使用的仿真软件为protel99se。

该软件提供了功能强大的电子仿真设计界面和方便的电路图和文件管理功能。

能够让使用者全面的收集电路的相关数据,进而有助于对电路进行改进。

总体来说,课程设计中所涉及的仿真电路是比较简单的。

但通过仿真得到的结论在实际的类似电路中有很普遍的意义。

本设计最终选用西勒振荡器。

目录第一章设计要求与总体框图1.1 设计目的 (3)1.2 题目要求 (3)1.3 设计总体框图 (3)第二章各部分设计方案及工作原理2.1 LC正弦波振荡部分 (4)2.1.1 LC三点式振荡器相位平衡条件的判断准则 (4)2.1.2 电容三点式振荡器 (4)2.1.3西勒振荡器 (5)2.2 相位调整网路部分 (8)2.3总体设计及仿真 (10)第三章结论 (11)第四章展望 (12)第五章致谢 (12)第六章参考文献 (12)第一章设计要求与总体框图1.1 设计目的(1)了解通信系统功能模块电路的工作原理(2)熟悉通信系统功能电路的设计方法(3)掌握利用仿真软件对电路功能进行分析(4)学会通信电路的器件选型,参数调节,功能测试1.2 题目要求1 基于LC振荡器设计一频率为10Mhz的信号源,并利用相位调整网络获得双路正交信号。

基于延时移相正交信号发生器的锁相环建模方法及系统锁相环(PLL)是一种常见的电路,用于将输入信号与本地参考信号同步。

其中,延时移相正交信号发生器(DDS)是一种常用的数字信号发生器,可以产生高精度的正弦波信号。

本文将介绍一种基于DDS的PLL建模方法及系统。

一、建模方法1. PLL的基本原理PLL的基本原理是将输入信号与本地参考信号进行比较,然后根据比较结果调整本地参考信号的相位和频率,使其与输入信号同步。

PLL通常由相位检测器(PD)、环路滤波器(LPF)、控制电压发生器(VCO)和反馈电路组成。

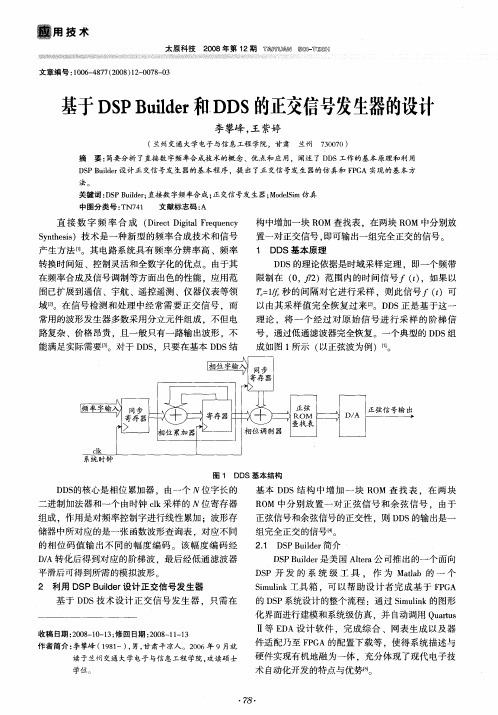

2. DDS的基本原理DDS是一种数字信号发生器,可以通过数字控制产生高精度的正弦波信号。

DDS的基本原理是将一个参考时钟信号与一个数字控制字相乘,得到一个数字信号,再通过数字滤波器和DAC转换成模拟信号输出。

DDS的优点是精度高、频率稳定,可以实现高速、高精度的信号产生。

3. 基于DDS的PLL建模方法基于DDS的PLL建模方法是将DDS作为VCO的替代品,将输入信号与DDS产生的正弦波信号进行比较,然后通过相位检测器和环路滤波器控制DDS的数字控制字,使其产生与输入信号同步的正弦波信号。

二、系统实现基于DDS的PLL系统实现主要包括DDS模块、相位检测器模块、环路滤波器模块和反馈电路模块。

1. DDS模块DDS模块主要包括数字控制字生成器、数字滤波器和DAC模块。

数字控制字生成器根据输入的频率和相位信息产生相应的数字控制字,数字滤波器对数字控制字进行滤波,DAC模块将滤波后的数字信号转换成模拟信号输出。

2. 相位检测器模块相位检测器模块将输入信号和DDS产生的正弦波信号进行比较,得到相位误差信号。

常用的相位检测器有边沿触发型、环路型和乘法型等。

3. 环路滤波器模块环路滤波器模块对相位误差信号进行滤波,得到控制电压信号。

常用的环路滤波器有积分型、比例积分型和低通滤波器等。

4. 反馈电路模块反馈电路模块将控制电压信号送回DDS模块,控制DDS的数字控制字,实现DDS的频率和相位的调整,使其与输入信号同步。

正交信号发生器的FPGA设计与仿真雷能芳【期刊名称】《价值工程》【年(卷),期】2011(030)024【摘要】The common approach to implement orthogonal signal generator on FPGA is based on look-up tables, which require a huge volume of ROM to achieve high resolution. This paper proposes a pipelined architecture for implementation of orthogonal signal generator on FPGA, which, based on CORDIC algorithm, can save considerable hardware resources and improve the speed performance as well. According to advantages of DSP Builder, the system is designed by utilizing VHDL and Simulink module. The correctness and feasibility of this design is verified by simulation result.%正交信号发生器的FPGA实现通常都是基于查找表的方法,为了达到高精度要求,需要耗费大量的ROM资源去建立庞大的查找表.文中提出了一种基于流水线CORDIC 算法的实现方案,可有效地节省FPGA的硬件资源.并根据DSP开发工具DSP Builder的优点,采用VHDL文本与Simulink模型图相结合的方法进行了FPGA设计,仿真结果验证了设计的正确性及可行性.【总页数】2页(P140-141)【作者】雷能芳【作者单位】渭南师范学院,渭南714000【正文语种】中文【中图分类】TP391.9【相关文献】1.基于FPGA的正交信号发生器设计 [J], 杨峰;文枰2.正交幅度调制解调器的FPGA设计与仿真 [J], 雷能芳3.基于FPGA的正交信号发生器 [J], 郝小江4.多模态信号发生器设计与仿真 [J], 雷红;黄懿赟;潘圣民;陆伟5.一种频率占空比独立可调的PWM信号发生器的设计与仿真 [J], 盛奋华因版权原因,仅展示原文概要,查看原文内容请购买。

正弦信号发生器是信号中最常见的一种,它能输出一个幅度可调、频率可调的正弦信号,在这些信号发生器中,又以低频正弦信号发生器最为常用,在科学研究及生产实践中均有着广泛应用。

引言引言正弦信号发生器是信号中最常见的一种,它能输出一个幅度可调、频率可调的正弦信号,在这些信号发生器中,又以低频正弦信号发生器最为常用,在科学研究及生产实践中均有着广泛应用。

广泛应用。

目前,常用的信号发生器绝大部分是由模拟电路构成的,当这种模拟信号发生器用于低频信号输出往往需要的RC 值很大,这样不但参数准确度难以保证,而且体积大和功耗都很大,而由数字电路构成的低频信号发生器,虽然其低频性能好但体积较大,大,而由数字电路构成的低频信号发生器,虽然其低频性能好但体积较大,价格较贵,价格较贵,价格较贵,而本而本文借助DSP 运算速度高,系统集成度强的优势设计的这种信号发生器,比以前的数字式信号发生器具有速度更快,且实现更加简便。

号发生器具有速度更快,且实现更加简便。

系统原理系统原理一般的采样型SPWM 法分自然采样法和规则采样法,自然采样法是将基准正弦波与一个载波三角波相比较,由两者的交点决定开关模式的方法。

由于自然采样法得到的数学模型需要解超越方程,因而并不适合微控制器进行实时控制,又因为实践检验对称波形比非对称波形在三相电的相电流中引起的谐波失真小,所以我们使用对称规则采样法作为本系统的数学模型。

学模型。

这里说明一下使用TI 公司的DSP 芯片TMS320LF2407(以下简称2407)来产生PWM 信号的原理:由于产生一个PWM 信号需要有一个适合的定时器来重复产生一个与PWM 周期相同的计数周期,并用一个比较寄存器来保持调制值,并用一个比较寄存器来保持调制值,因此,因此,比较寄存器的值应不断与定时寄存器的值相比较,这样,当两个值相匹配时,时寄存器的值相比较,这样,当两个值相匹配时,就会在响应的输出上产生一个转换(从低就会在响应的输出上产生一个转换(从低到高或从高到低),从而产生输出脉冲,输出的开启,从而产生输出脉冲,输出的开启(或关闭)(或关闭)(或关闭)时间与被调制的数值成正比,时间与被调制的数值成正比,因此,改变调制数值,相关引脚上输出的脉冲信号的宽度也将随之改变。

第42卷2006年第6期 西 北 师 范 大 学 学 报(自然科学版) Vol 142 2006 No 16 Journal of Northwest Normal University (Natural Science ) 收稿日期:2006Ο01Ο04;修改稿收到日期:2006Ο09Ο14基金项目:甘肃省科技攻关资助项目(2GS047ΟA52Ο002Ο07)作者简介:马胜前(1954—),男,甘肃甘谷人,教授,硕士研究生导师.主要研究方向为计算机测量与控制技术和信号处理.E Οmail :s.q.ma @tom 1com正交信号发生器的设计与实现马胜前(西北师范大学物理与电子工程学院,甘肃兰州 730070)摘 要:描述了基于A T89C52单片机、锁相环和开关电容滤波器的正交信号发生器的设计和实现方法.单片机产生方波,通过数字接口实现相位差为90°的方波,再通过两个8阶BU T TERWOR T H 低通开关电容滤波器MAX295对双路方波进行滤波,从而产生正交的正弦波.MAX295的时钟由锁相环倍频产生.采用连续时间滤波器抑制采样时钟的影响.频率覆盖范围011~20k Hz.频率和相位误差小于1%.关键词:相位差;正交波形;单片机;开关电容滤波器中图分类号:TN 713;TP 36811 文献标识码:A 文章编号:10012988Ⅹ(2006)0620031203Design and implementation of t he quadrat ure waveform generatorMA Sheng Οqian(College of Physics and Electronic Engineering ,Northwest Normal University ,Lanzhou 730070,G ansu ,China )Abstract :The design and implementation of quadrat ure waveform generator are described based on t he A T89C52,p hase Οlocked loop (PLL )and switched Οcapacitor filter (SCF ).The square wave is generated by single Οchip micro Οcont roller.It is shifted 90degree by a digital circuit.In order to obtain quadrat ure sinusoidal waves ,t he dual Οchannel square waves are filtered by two 8Οorder Butterwort h lowpass SCF MAX295.The clock of MAX295comes f rom PLL.For supp ressed t he affect of t he sampling clock ,t he second order continue time filters are used.It covers f requency range 011~20k Hz.The errors of f requency and p hase are less t han 1%.K ey w ords :p hase difference ;quadrat ure waveform ;single Οchip micro Οcont roller ;switched Οcapacitor filter 在信号检测和处理中经常需要正交信号,而常用的波形发生器多数采用分立元件组成,不但电路复杂、价格昂贵,且一般只有一路输出波形,不能满足实际需要[1].文献[2]采用MAX038实现一组正交信号,但电路较复杂,而且相位误差较大.用单片机和D/A 转换器可以产生双路波形,但由于每个周期需要输出多个值,所以信号频率难以提高[3].笔者结合单片机和开关电容滤波器的优点,用锁相环的倍频功能[4],确保开关电容滤波器的信号与时钟比精确,提高了信号的频率,改善了输出波形.该波形发生器能方便地产生正交信号,其频率和相位精度高.1 硬件设计图1所示为正交信号发生器的原理框图.单片机根据键盘给定的频率产生一路方波CL K 0,锁相环倍频电路由MC14046和固定的模为N /2的计数器等构成,实现N /2倍频功能.N 为钟控开关电容滤波器所要求的时钟信号比,本设计中N =50.设CL K0的频率为f X ,则锁相环的输出频率为f CL K 1=N f X /2.(1) 数字接口产生相位差90°的双路方波,图2为13西 北 师 范 大 学 学 报(自然科学版) 第42卷 Journal of Northwest Normal University (Natural Science ) Vol 142 90°移相电路.CL K 0通过异或门产生周期相同相位相反的信号,再经过上升边沿触发的D 触发器二分频后产生相位差为90°的双路方波V O S1,V O S2.设双路方波的频率为f 1,则有f 1=f X /2.(2)该信号由低通滤波器滤除高次谐波,就可得到相位差为90°的正弦信号.图1 正交信号发生器框图Fig 1Diagram of quadrature waveformgenerator图2 90°移相电路Fig 290°phase shifter circuit为了输出正弦信号,要求从方波信号V O S1,V O S2中分别提取基波,即必须滤除谐波成分.从傅立叶级数可知,方波信号包含基波、3次谐波以上的奇次谐波,为了较好地滤除谐波成分,要求滤波器在通带内波动小,阻带内衰减足够大.为此选用了时钟控制的8阶BU TERWOR T H 开关电容滤波器MAX295.MAX295要求时钟信号频率比固定为50,即要求f CL K 1/f 1的比值为50.由(1)式和(2)式可以得到f CL K 1/f 1=N.(3) 因为已经设定N 为50,所以满足滤波器要求.MAX295对三次谐波的衰减大于70dB ,故产生的波形较为理想[5].从方波信号V O S1,V O S2中提取基波需要2个低通滤波器来实现.图3所示为一个信道的低通滤波器实现电路.V O S1加到8阶BU TERWOR T H 低通滤波器的输入,CL K 1作为时钟输入,从MAX295第5脚输出低通滤波信号.为减小采样时钟对输出信号的影响,利用MAX295内部的运算放大器A 1和外接电容C 1、C 2,电阻R 1、R 2、R 3组成一个二阶连续时间滤波器.图4为幅值调节电路,其中V E 为辅助直流电源.由于图3中低通滤波器输出信号V M1含直流分量,通过调节R W2可以去除直流分量或改变直流分量大小.调节R W1可以改变输出交流分量的峰值.V O1是正交信号中的一路信号,另外一个信道的低通滤波器及其幅值调节电路结构及参数完全相同.图3 低通滤波器实现Fig 3Implementation of low Οpass filter图4 输出幅值调节Fig 4Adjustment of output amplitude2 软件设计单片机采用A T89C52,显示芯片采用MAX7219管理,键盘采用中断方式.由键盘输入欲产生信号的频率f X ,单片机通过调用计算程序算出定时器T 2的时间常数.当频率较低时,定时器T 2工作在16位自动重装初值的加法计数模式.以中断方式实现时间控制,就可以按照设定的频率从P110输出方波.设T 2定时初值为Y 1,因为需要定时为输出信号周期的一半,所以有Y 1=65536-f O S C /(2×12×f X ),(4)其中f O S C 是单片机的外接晶体振荡频率.当频率较高时,T 2工作在波形产生方式,其频率关系为fX=f O S C /[4×(65536-Y 2)].(5)Y 2为定时初值,由(5)式得Y 2=65536-f O S C /(4×f X ).(6)这时T 2不采用中断方式,它可以自动从P110输出占空比为50%的方波.波形产生方式的输出可以避免单片机中断而导致的误差.图5为主程序流程图.设置定时器T 2的优先级最高,显示采用6位数码管.图6为键盘和定时23 2006年第6期 马胜前:正交信号发生器的设计与实现 2006 No 16 Design and implementation of the quadrature waveform generator 器中断服务的流程图.当频率f X 小于20Hz ,T 2工作为定时中断方式,时间常数按(4)式计算,需要定时大于T 2的最大定时时,需要一个软件计数器和T 2的中断协同工作.当频率f X ≥20Hz ,时间常数按照(6)式计算,T 2的工作方式相应切换为波形产生方式.为了减小误差,采用浮点计算,计算结果还需转换为16进制,将计数初值装载到RCA P2H 和RCA P2L 两个寄存器中.图5 主程序流程图Fig 5Flow diargram of mainprogram图6 中断服务程序流程图Fig 6Flow diargram of interrupt service program3 实验结果单片机的f O S C 为4M Hz ,PLL 使用的计数器模为25,CL K 0为单片机从P110输出的信号,图7为移相电路产生的信号波形,V O S1,V O S2分别为二分频后相位差为90°的双路方波.图8是示波器记录的频率为1k Hz ,幅值为1V ,经过低通滤波器和幅值调节电路后产生的正交信号V O1,V O 2.对于图3中的二阶连续时间滤波器的截止频率f C 要求不严格,只要f C 大于信号频率f X 的3倍即可.在整个频段内分段改变电容C 1、C 2,电阻R 1、R 2、R 3的值即可,具体取值参见文献[6].本实验用手动开关选择,但也可以由单片机控制模拟开关来选择,由于篇幅,这里不再详述.输出频率范围为011~20k Hz ,相位误差在整个频段内小于1%.产生误差的主要原因是2个信道的元器件不完全匹配.因为要求时间常数Y 1和Y 2为整数,所以频率的误差主要来自计算后的舍入误差,选择合适的f X 可以大大减小频率误差.实验说明,在整个频率范围,频率误差不大于1%.图7 移相电路波形Fig 7Waveform of phaseshifter图8 输出正交信号波形Fig 8Output waveforms of guadrature signal4 结束语基于单片机、锁相环和开关电容滤波器,设计并实现了正交信号发生器.利用单片机可以方便地设置频率,利用定时器T 2精确的定时功能和灵活的输出方式生产频率信号.数字移相电路保证了90°的相位移.利用锁相环的倍频功能,确保了开关电容滤波器的信号与时钟比精确,并采用连续时间滤波器来抑制开关电容滤波器的时钟噪声.该波形发生器的频率和相位精度高,能满足一般实验和科研的要求.参考文献:[1] 冯 杰.任意波形发生器[J ].电子世界,2004(7):55.[2] 张 屺,杨 波,冯旭哲,等.程控宽带正交信号发生仪[J ].电子工程师,2000(4):26Ο27.[3] 张李勇,陈 朗,张飞舟.基于8051单片机的双通道波形发生器的设计与实现[J ].计算机工程与应用,2004(8):100Ο103.[4] 马胜前.用PSCF 设计自适应带通滤波器[J ].兰州大学学报:自然科学版,1999,35(4):48Ο53.[5] MAXIM.N EWREL EASEDA TABOO K.VOL UM E I ,1993.[6] 钱建立.8阶开关电容滤波器MAX29X 系列的应用设计[J ].国外电子元器件,1995(1):5Ο9.(责任编辑 孙晓玲)33。

基于FPGA的正交信号发生器设计

杨峰;文枰

【期刊名称】《四川文理学院学报》

【年(卷),期】2015(25)5

【摘要】根据直接数字频率合成(DDS)技术,设计了基于FPGA的正交信号发生器,以用于双通道微弱信号相关检测电路中.首先介绍了DDS技术的基本原理;其次采用硬件描述语言编写各个模块的代码,并对其进行功能仿真和验证;然后对各个模块进行硬件电路设计;最后对设计的正交信号发生器进行了实验测试.测试结果表明:正交信号发生器的输出信号的频率特性和相位特性具有很高的稳定性,能够满足相关检测电路的要求.

【总页数】3页(P47-49)

【作者】杨峰;文枰

【作者单位】四川文理学院国有资产管理处,四川达州635000;重庆大学光电工程学院,重庆沙坪坝400030

【正文语种】中文

【中图分类】TN911

【相关文献】

1.基于PIC单片机的正交正弦信号发生器的设计 [J], 宋进红;张晓丽;张芳芳

2.基于DDS的可变频多路正交信号发生器的设计 [J], 范圆圆;王晓升;刘伟

3.基于MATLAB的可控DDS正交信号发生器的设计与实现 [J], 杨军

4.基于FPGA的正交信号发生器 [J], 郝小江

5.正交信号发生器的FPGA设计与仿真 [J], 雷能芳

因版权原因,仅展示原文概要,查看原文内容请购买。

正交信号发生器的设计与实现

马胜前

【期刊名称】《西北师范大学学报(自然科学版)》

【年(卷),期】2006(042)006

【摘要】描述了基于AT89C52单片机、锁相环和开关电容滤波器的正交信号发生器的设计和实现方法.单片机产生方波,通过数字接口实现相位差为90°的方波,再通过两个8阶BUTTERWORTH低通开关电容滤波器MAX295对双路方波进行滤波,从而产生正交的正弦波.MAX295的时钟由锁相环倍频产生.采用连续时间滤波器抑制采样时钟的影响.频率覆盖范围0.1~20 kHz.频率和相位误差小于1%.【总页数】3页(P31-33)

【作者】马胜前

【作者单位】西北师范大学,物理与电子工程学院,甘肃,兰州,730070

【正文语种】中文

【中图分类】TN713;TP368.1

【相关文献】

1.基于正交信号发生器的单相锁相环的研究 [J], 陈红兵;闵晶妍

2.单相αβPLL方案中正交信号发生器的性能比较 [J], 贝太周;王萍;张博文

3.基于FPGA的正交信号发生器设计 [J], 杨峰;文枰

4.基于MATLAB的可控DDS正交信号发生器的设计与实现 [J], 杨军

5.具有精确幅值积分特性的正交信号发生器 [J], 孙于;李雪;耿嘉一;吴尚

因版权原因,仅展示原文概要,查看原文内容请购买。