基于PCI总线视频信号发生器的实现

- 格式:pdf

- 大小:204.90 KB

- 文档页数:4

基于PCI总线的DSP视频采集驱动设计

李晨阳;续志军

【期刊名称】《制造业自动化》

【年(卷),期】2010(032)009

【摘要】针对当前市场上主流视频DSP系统在数据处理的灵活性和实时性上不能兼顾的不足,文中提出了基于FPGA及PCI总线的实时视频DSP平台设计方案,并重点介绍利用PCI接口芯片PCI9054搭建高速数据传输接口的具体实现方法.利用PCI接口芯片的强大功能,详细介绍了PCI9054的工作方式以及调用厂商提供的API函数编写平台驱动程序.本平台可灵活的添加图像处理功能,对于一些需要经常进行特殊图像处理的研究型单位(如学校、科研机构等)进行教学、研究具有一定的意义.

【总页数】4页(P3-6)

【作者】李晨阳;续志军

【作者单位】中国科学院长春光学精密机械与物理研究所,长春,130033;中国科学院长春光学精密机械与物理研究所,长春,130033

【正文语种】中文

【中图分类】TP391

【相关文献】

1.基于PCIE总线的视频采集系统驱动设计 [J], 肖忠炳;于乐

2.基于PCI总线的视频采集系统设计 [J], 陈东旭;席泽敏;盛成明;李汉钊

3.基于DSP与PCI的视频采集卡设计与实现 [J], 黄洁

4.基于PCI总线的视频采集卡及其WDM驱动程序设计 [J], 刘慧英;王军;夏天琪

5.一种基于CPLD和PCI总线的视频采集卡的设计 [J], 赵明卓;李亚兰

因版权原因,仅展示原文概要,查看原文内容请购买。

基于PCI总线的任意波形信号发生器设计的开题报告一、选题的背景和意义波形信号的生成是电路研究和实验的基础,因此波形信号发生器是非常重要的一种电子实验仪器。

随着科技的发展,数字信号处理技术得到广泛应用,数字波形信号发生器逐渐取代了传统的模拟波形信号发生器成为主流。

PCI总线作为计算机与外围设备交互的通信接口,在数字信号处理领域也具有广泛的应用。

因此,基于PCI总线的任意波形信号发生器设计具有重要的现实意义。

二、文献综述1.任意波形信号发生器任意波形信号发生器是一种能输出任意波形信号的设备,它可以通过预设各种信号的幅值、相位、频率和脉宽等参数,输出各类信号。

传统的任意波形信号发生器主要基于数字信号处理器(DSP)或场效应管(FPGA)实现,输出的信号精度高、波形多样化。

任意波形信号发生器被广泛应用于精密仪器仪表测试、学校科研院所、工业场合等。

2.PCI总线PCI总线是一种能够实现高速数据传输和通信的计算机外围设备接口,是目前主流的内部计算机扩展总线。

PCI总线数据传输速度快、稳定性高、带宽大、地址空间广,适合于大数据传输、高速采集和实现高性能计算等场合。

3.基于PCI总线的任意波形信号发生器设计目前,基于PCI总线的任意波形信号发生器设计已成为研究热点。

设计人员主要围绕如何利用PCI总线实现高速传输和控制、如何设计高精度的模拟电路、如何实现稳定的时钟同步等方面进行探索和研究。

同时,为了提高系统的可编程性和使用灵活度,研究者还将系统设计进行了模块化和结构化。

三、研究内容和方案本文拟设计一种基于PCI总线的任意波形信号发生器,实现以下功能:1.支持多种波形的发生,包括正弦波、方波、三角波、锯齿波等。

2.支持各种波形的控制参数调节,包括幅值、频率、相位等。

3.借助PCI总线的高速传输特点,实现高速数据传输和稳定性控制。

4.采用模块化设计和参数配置方式,实现系统的可编程和灵活度。

设计方案如下:1.使用DSP实现波形信号的计算和生成,通过PCI总线与计算机进行通信数据传输。

第5卷 第10期 中 国 水 运 Vol.5 No.10 2007年 10月 China Water Transport October 2007收稿日期:2007-8-4作者简介:周敏均 (1983-) 杭州电子科技大学 自动化学院 研究生 (310012) 研究方向:检测技术与自动化装置基于PCI 总线的视频采集卡驱动程序的设计与实现周敏均 杨成忠 江加加摘 要:本文介绍了基于PCI 总线的视频采集卡驱动程序的设计和实现。

视频采集卡基于PCI 总线的设计更好地满足了高速大容量的数据传输需求;针对视频设备的内核流驱动的设计更方便了上层应用软件的开发。

该视频采集卡驱动已经成功应用于视频监控系统中,有效地提高了视频监控系统的功效。

关键词:PCI 总线 视频采集卡 内核流驱动中图分类号:TP311.131 文献标识码:A 文章编号:1006-7973(2007)10-0149-03一、引言随着计算机、网络、多媒体技术以及全球安防事业的迅猛发展,数字视频技术得到了长足地发展,视频采集卡的应用也越来越广泛。

但是由于视频数据传输高速、大量的特点,传统的使用基于串口、并口或ISA 总线传输数据的方式已经不能满足其传输的需求。

同时,由于其复杂性,现在各厂商都是自己提供采集卡的SDK,没有统一的界面,使得上层应用的开发和设备的使用非常不便,而基于内核流的驱动程序能够很好的解决这个问题,上层应用程序能够通过系统提供的统一接口访问底层硬件。

当前,基于PCI 总线的视频采集卡以其强大而灵活的功能、高度的集成性成为主流产品。

为此,本文设计了基于PCI 总线的视频采集卡,并开发了相应的基于内核流的驱动程序。

二、视频采集卡硬件系统PCI 总线是近年来出现的一种高性能的局部总线,它理论上提供133MB/s 的传输速率,支持猝发式读写,具备完整的多总线主控能力,支持即插即用,很适合网络适配器、硬盘驱动器、全动态数字视频卡、图形卡及各类高速外设应用。

基于PCI总线的雷达视频采集方案摘要:分析了雷达视频采集的必要性和意义,介绍了通过PCI实现高速雷达视频信号的采集实现方案,并分析了方案中的各个模块的功能。

关键词:雷达视频数据采集 PCI PC机在传统的雷达显示终端中所涉及到的视频信号是模拟的,随着计算机技术和IC技术的不断发展,使这种模拟信号的数字化成为可能,使得雷达视频的存储和远距离传输成为可能,并在实际中得到越来越多的应用。

在基于这种技术背景下开展了相应的研究。

(文库114收集整理)1 视频采集方案可行性分析方案的设计主要考虑雷达视频带宽,即距离分辨率。

在采集卡部分影响带宽的数据瓶颈在于三方面:AD采样量化、FIFO读写速度和PCI的DMA速度。

硬件方案中采用TLC5540,最高采样率可以达到40MHz,采样深度为8bits;FIFO采用IDT72V36100,最高读写速度可以达到133MHz;计算机PCI总线的数据带宽可达到532Mbps,在实际中,由于受硬件环境,如主机板和CPU的影响,采用133Mbps的PCI卡。

在PC机部分数据瓶颈主要在于磁盘数据访问速度,普通磁盘的数据访问速度为40Mbps。

若数字化雷达视频带宽达到30Mbps、量化深度为8bits,则数据采样率为30MHz,距离分辨率为300,000,000/2/30,000,000=5m,这样的分辨率能够满足一般的导航和警戒雷达。

若量化深度降低,则距离分辨率将进一步提高。

由以上分析可见所采用方案能够满足视频的带宽要求。

2 系统实现的关键点2.1 方案中的雷达视频数据流程和结构对于30MHz带宽的数字化雷达视频信号要求实时传输,合理地安排数据的流程非常重要。

其流程如图1所示。

由底层到应用程序,雷达数据主要经过三个数据传输过程。

(1)由数据采集卡至设备驱动,在数据采集卡中采用了双FIFO技术,通过DMA单个FIFO一次传输一帧雷达数据,即一个主脉冲正程的雷达回波信号。

这里双FIFO的作用在于信号的实时传送,采集卡对FIF01写入时,驱动程序通过DMA将FIFO2的数据传入BLK2中,此为数据通道CH2,CHl为FIFO1与BLK2之间的通道。

总第173期2008年第11期舰船电子工程Ship Electronic Enginee ring Vol.28No.11158 基于PCI 总线的视频采集系统设计3陈东旭1) 席泽敏1) 盛成明2) 李汉钊1)(海军工程大学1) 武汉 430033)(海军702厂2) 上海 210000)摘 要 主要介绍了基于P CI 总线的视频采集系统的硬件实现;通过VFW 软件开发包,探讨了视频采集及用MP EG 4压缩编码中的编程设置。

关键词 PCI 总线;视频采集系统;V FW;MP EG 4中图分类号 TP368.1Desi gn of Video Cap tu re Syst em Based on PCI BusC he nD ongxu 1) Xi Ze min 1) Sheng C he ngmi ng 2) L i Ha nzhao 1)(Naval Unive rsity of Engineering 1),Wuha n 430033)(702Factor y of Navy 2),Sha nghai 210000)Abs tra ct The paper introduces hardwa re realization of video capture syste m on PCI bus.Progra mming of the video capture and M P EG 4compr ession code is discussed by using VFW s oft ware development tools.Ke y w ords PC I Bus ,video capt ur e system ,V FW ,M P EG 4Class N umber TP368.11 引言为了采集记录雷达情报,以便脱离雷达装备和本系统在通用计算机上检索回放,设计了一种同步实时记录综合显示器画面的高速视频采集系统。

基于PCI总线的视频数据采集板的研究张诚;孙列鹏;杨化路;肖薇;张东升【摘要】介绍了PCI接口的基本功能和特点;利用PLX9054接口芯片,结合FPGA逻辑设计芯片和大容量FIFO,实现了对双路视频的AD采集和多路串口报文的打包高速实时数据传输.【期刊名称】《电脑与信息技术》【年(卷),期】2019(027)001【总页数】3页(P76-78)【关键词】PCI总线;数据采集;FPGA【作者】张诚;孙列鹏;杨化路;肖薇;张东升【作者单位】北广科技股份有限公司,北京 101312;北京航空航天大学,北京100082;北广科技股份有限公司,北京 101312;北广科技股份有限公司,北京101312;北广科技股份有限公司,北京 101312【正文语种】中文【中图分类】TN73PCI接口从1993年提出至今,得到了众多计算机设备厂商的支持,已经在PC机、工业控制等相关领域得到了广泛的应用。

现在我们也可以把这个使用广泛的PCI接口标准运用到我们的视频数据采集板上,来解决视频采集传输速度问题。

1 视频数据采集板的结构设计1.1 视频数据采集板的硬件结构视频数据采集板的硬件结构分为视频数据采集和与PCI总线连接两部分,下面分别进行介绍。

1.1.1 视频采集部分结构视频数据采集板的主要功能是对信号(其中信号包括:两路视频信号和几路串口信号)进行采样,数字化,并进行一些预处理,然后把实时接收的数据通过FPGA进行一些预处理和打包。

将打包的帧结构数据以16位的形式进行输出(此过程的结构图如图1所示)。

从图中我们可以看到,我们的视频数据采集板可以对输入的两路视频分别进行增益的调节,然后将调节了增益后的视频送到两路模-数转化芯片同时进行采样,转化为数字量,这样可以保证我们两路的视频均可以以比较理想的增益来进行记录。

这样也提高了我们以后的可扩展的能力。

图1 视频数据采集板采集结构图1.1.2 视频采集和PCI总线连接结构从FPGA输出的帧结构数据为16位的,而PCI总线的数据长度为32位,而且两者工作在不同时钟的异步状态下,为解决两者长度不统一和时钟不同步的问题我们在两者中加入了一个FIFO芯片,这样就能有效的解决内部总线长度和PCI总线长度不统一以及两个总线工作时钟不同步的两大问题。

基于PCI总线和CPLD的任意信号发生器设计2 系统主要硬件设计2.1 PCI 总线接口部分设计PCI 总线作为计算机与外部设备的一个重要连接总线,数据传输稳定、灵活、传输速度快,还具有即插即用和良好的扩展性等优点,被广泛应用在各种与计算机互联的设备中。

考虑到PCI 总线的协议比较复杂,所以本设计采用了PLX 公司生产的PCI 接口专用芯片PCI9052 用于PCI 总线的控制。

图2 是PCI9052 芯片的主要接口电路图。

主要包括9052 与PCI 插槽间的连接信号线、与E2PROM 之间的连接线和与局部总线之间的连接线。

与PCI 插槽的信号包括地址数据复用信号AD[31:O].总线命令信号C/BE[3:0]#和PCI 协议控制信号PAR,FRAME#,IRDY#,TRDY#,STOP#,IDSEL,DEVSEL#,PERR#,SE RR#。

与串行E2PROM 的连线有4 根信号线:EESK,EEDO,EEDI 和EECS。

本设计中需要传输的数据量比较少,同时考虑到对早期的ISA 设备的兼容性,所以采用了9052 中的ISA 模式。

在ISA 模式下,9052 与ISA 总线的连接有数据线LAD[7:0],地址线ISAA[1:O],LA[23:2],I/O 读写信号线IOWR#,IORD#,地址锁存BALE。

9052 的工作方式及配置信息主要由E2PROM 加载,这里采用了Motorola 公司的93LC46B,E2PROM 的数据可以提前用烧写器烧好,也可以在线烧写。

配置信息包括:设备号DID、制造商号VID、子设备号SDID、子制造商号SVID、中断号、设备类型号、局部空间基地址、局部空间描述符、工作模式、LOCAL 端数据线的宽度、片选以及局部响应控制CNTRL 等信号。

根据需要配置好这些信息,写入E2PROM 中。

本设计中E2PROM 的配置信息如表1 所示。

基于PCI总线的塔康视频信号产生电路设计PCI 总线具有支持多种外围设备、独立于处理器、数据传输快等优点,已经应用于PC 机,工控机等多种场合,如数据采集卡,IO 控制卡、总线卡等都采用了PCI 总线结构。

在某综合测试系统设计时,为提高系统集成化、模块化的要求,设计研制了基于PCI9054 的塔康(TACAN)视频信号产生板卡。

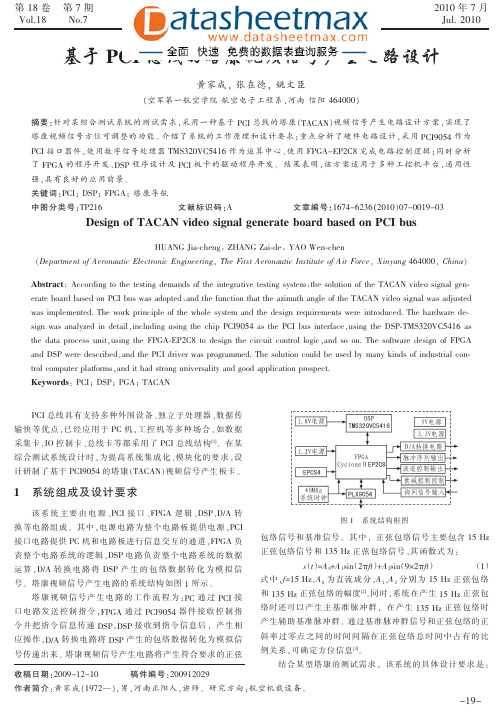

1 系统组成及设计要求该系统主要由电源、PCI 接口、FPGA 逻辑、DSP、D/A 转换等电路组成。

其中,电源电路为整个电路板提供电源,PCI 接口电路提供PC 机和电路板进行信息交互的通道,FPGA 负责整个电路系统的逻辑,DSP 电路负责整个电路系统的数据运算,D/A 转换电路将DSP 产生的包络数据转化为模拟信号。

塔康视频信号产生电路的系统结构如图1 所示。

塔康视频信号产生电路的工作流程为:PC 通过PCI 接口电路发送控制指令,FPGA 通过PCI9054 器件接收控制指令并把指令信息传递DSP,DSP 接收到指令信息后,产生相应操作,D/A 转换电路将DSP 产生的包络数据转化为模拟信号传递出来。

塔康视频信号产生电路将产生符合要求的正弦包络信号和基准信号。

其中,正弦包络信号主要包含15 Hz 正弦包络信号和135 Hz 正弦包络信号,其函数式为:式中,f=15 Hz,A0 为直流成分,A1、A2 分别为15 Hz 正弦包络和135 Hz 正弦包络的幅度。

同时,系统在产生15 Hz 正弦包络时还可以产生主基准脉冲群,在产生135 Hz 正弦包络时产生辅助基准脉冲群。

通过基准脉冲群信号和正弦包络的正斜率过零点之间的时间间隔在正弦包络总时间中占有的比例关系,可确定方位信息。

结合某型塔康的测试需求,该系统的具体设计要求是:15 Hz 和135 Hz 正弦包络的信号深度均可调,幅度调整的范围都是O~40%,最小调整间隔为1%:15 Hz 正弦包络和135Hz 正弦包络的幅度。