宽带锁相频率源设计

- 格式:pdf

- 大小:204.90 KB

- 文档页数:3

题目10M锁100MHz锁相频率源一、设计任务与要求1、理解锁相环相关概念,熟悉ADF4002锁相环芯片;2、应用ADF4002锁相环芯片,设计100MHz锁相频率源,单片机写入ADF4002的控制字;3、应用ADIsimPLL软件进行环路滤波器仿真;4、输入信号10MHz,输出100MHz,环路带宽在10Hz~100Hz之间;5、熟悉ADF4002硬件电路设计;二、方案设计1.微处理器最小系统电路方案1:STM32F103C8T6方案2:STC51方案3:FPGASTM与FPGA的优缺点一个属于单片机STM32 ,一个属于可编程阵列FPGA。

STM32由于有各种外设操作起来简单,可以处理模拟以及数字信号,适用于设计的控制电路FPGA应用也比较广泛,只能处理数字信号,但是能同时运行多条指令,也就是并行执行,这是单片机、ARM等比不了的,主要用于处理各种逻辑。

STM32代表ARM Cortex-M内核的32位微控制器,具有高性能,实时性强,低功耗,便于低电压操作等优点,同时还易于开发。

我们选择方案2,因为STC51是STC公司推出的以MCS-51为内核的单片机的。

和AT89C51基本一致,但是可以通过串口直接烧写所以被广泛使用。

MCS-51是入门级一款很经典的MCU,特点就是简单,所以在教学时大量采用。

而FPGA耗财贵,上手难度大,所以选择了方案2。

2.ADF4002模块电路方案一:TIDA-01346设计结合使用两个LMX2594合成器,与使用一个合成器相比,产生的噪声更低。

通过结合相位中两个合成器的输出,理论3dB相位噪声优势可能是由于输出功率高6dB,而噪声功率仅高3dB。

LMX2594是这种应用的理想合成器,因为它具有SYNC功能,该功能使其具有确定性的可重复相位以及可编程相位,可以用来校正由于线迹失配或任何其他因素导致的任何相位误差。

方案二:该ADF4002频率合成器用于在无线接收器和发射器的上变频和下变频部分中实现本地振荡器。

60MHz~12GHz宽带频率源研究的开题报告一、选题背景及意义广泛的频率范围和宽广的应用场景都对高质量的宽带频率源提出了极高的要求。

目前市场上的大多数频率源多只覆盖部分频段而缺乏较宽的带宽。

因此需要一种能够满足高频率和广泛应用的宽带频率源,用于雷达通信、航空导航、卫星通讯等领域。

二、研究内容该研究的主要内容涉及以下几个方面:1. 设计高性能宽带LC振荡器。

利用高品质因子(Q值)的电感器、电容器和晶体管组成的振荡器,实现高频段范围的信号发放。

2. 设计并实现扩频器。

利用扩频器实现原始基带信号到高带宽信号的转换。

3. 设计频率锁定电路。

开发一种锁定电路,实现不同时间和条件下宽带频率源的稳定性,对抗外部干扰影响。

4. 数据分析和计算。

分析各前行的测试数据,对振荡器、扩频器和频率锁定电路进行计算和仿真,提高频率源的精确度和稳定性。

三、研究方案和技术路线1. 选用高品质因子(Q值)的电感器、电容器、晶体管等元器件,设计高性能LC振荡器。

通过调节元器件参数,使得振荡器的共振频率覆盖60MHz至12GHz的范围,并保证输出信号的幅度和谐波较小。

2. 利用平衡调制扩频技术,实现高带宽信号的产生。

具体思路是,原始基带信号经过平衡调制转换为高宽带信号,并通过RC滤波器对高带宽进行筛选,以产生所需的频率宽带信号。

3. 设计频率锁定电路,采用Phase-Locked Loop(PLL)技术。

这种技术通过负反馈来迫使自由运动跟随着一个来自外界的参考信号。

通过对锁相环参数、滤波器参数等进行优化,使其能够适应不同环境和频率。

4. 分析和计算各元器件精度、温度导致的漂移、非线性等因素,保证频率源的精确即可靠性。

如果实验结果与计算相比有误差,采取适当手段进行修正。

四、预期成果和意义1. 成功实现覆盖60MHz至12GHz的宽带频率源,开创了新的研究领域,具有广泛的应用前景。

2. 通过锁相环技术和特殊的设计,有效地提高了频率源的稳定性,保证了输出信号的准确度和可靠性。

基于MB1504的锁相频率源电路设计(2)

MB1504 锁相频率

中的预置数A。

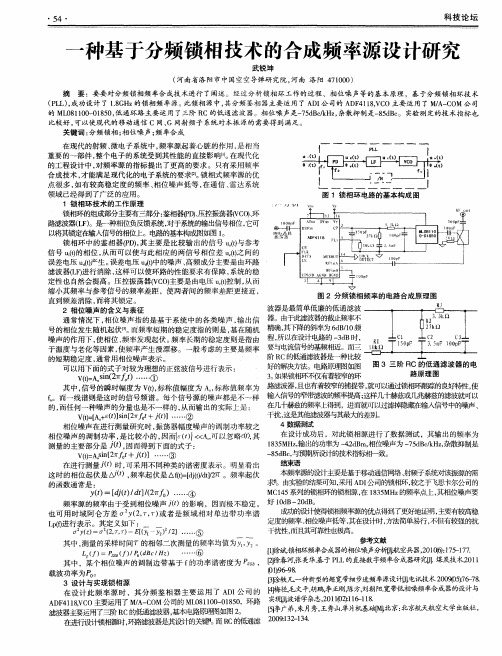

图6所示为MB1504的数据输入格式。

根据MB1504的工作原理,锁相环的输出频率fvco的计算公式为:

式中,fosc为外接晶体振荡器输人参考频率;P为前置分频器的分频比(由位SW决定),当SW为高时,P为32;当SW为低时,P为64;N为11位可编程计数器中的预置数(范围从16~2047);A为7位吞脉冲计数器中的预置数(范围从0~63);R为14位可编程参考分频器中的预置数(范围从8~16383)。

本设计中,频率合成器的频率范围fout为80~88 MHz,频率间隔△f为2 kHz。

参考振荡器的振荡频率fosc为4.096 MHz,参考频率fr等于合成器频率间隔△f(2 kHz),所以参考分频比R为:R=fosc/fr=2048,中心频率为84 MHz的分频比(PN+A=fout/△f)为42000。

这里采用的前置分频比模式为÷32/33,即P=32,

并由此可得:N=1312,A=16。

这样,改变N和A,即可改变输出频率,而改变N、R,则可改变输出频率和频率间隔。

小型化低成本频率源设计李宝新(中国电子科技集团公司第二十研究所,西安 710068)摘 要:本文采用集成式锁相环(Phase-Locked Loop,PLL)ADF5355实现一款超宽带、小尺寸、低成本的频率源,锁相环利用单片机C8051F340控制。

首先锁相环芯片ADF5355可以实现54 MHz~13600 MHz的频率输出,可以满足较大频率范围固定点频源的要求;另外,选择的锁相环芯片ADF5355和单片机C8051F340,再加一个稳压器芯片就可以实现低成本频率源的设计;通过合理的空间布局,可以实现小尺寸频率源的设计,具有较大的工程应用价值。

关键词:锁相环;单片机;稳压器中图分类号:TN74 文献标识码:A 文章编号:1674-7976-(2020)-06-438-04 Design Miniaturized and Low Cost Fixed Frequency SourceLI BaoxinAbstract:This paper design a fixed frequency source with the phase-locked loop chip ADF5355. Controlled by MCU C8051F340, the source realized the goal of miniaturized, low cost and ultra wideband. First, the phase-locked loop chip ADF5355 can realize frequency range from 54 MHz to 13600 MHz, so it can fulfill the request of the frequency range of the fixed frequency source. In addition, this source is formed by the PLL chip ADF5355, MCU C8051F340 and a LDO (Low dropout regulator) chip. Through reasonable PCB design, the size of this source is 30mm×30mm, with great practical value in engineering.Key words:PLL; MCU; LDO0 引言频率源是雷达、通信等系统实现高性能指标的关键技术之一,很多现代电子系统的功能实现都直接与频率源的性能有关,因此频率源被誉为无线电系统的心脏,其性能的优劣直接影响到整机的性能。