晶体管设计

- 格式:docx

- 大小:484.65 KB

- 文档页数:17

第四章晶体管规则阵列设计技术VLSIC 是高度复杂的集成系统,为保证设计的正确性和简化设计,避免由 于在版图设计过程中采用复杂结构而引入不可靠因素,因此,在 VLSI 的设计技术中大量地采用规则结构,晶体管规则阵列设计技术就是其中之一。

在这个结构 中的基本单元就是MOS 晶体管或MOS 晶体管对(CMOS )。

4.1晶体管阵列及其逻辑设计应用唯读存储器ROM 是最常用的晶体管规则阵列。

它以晶体管的有无来确定存 储的信号是“ 0”或“ 1”。

在人们通常的概念中,ROM 仅仅是存储器,实际上, 它还是一个可以用于组合逻辑设计的技术,显然,在 ROM 中的基本信息单元是 晶体管。

MOS 结构的ROM 以其低功耗,结构简单,单元占用面积小等优点, 已成为目前ROM 结构的主流实现技术。

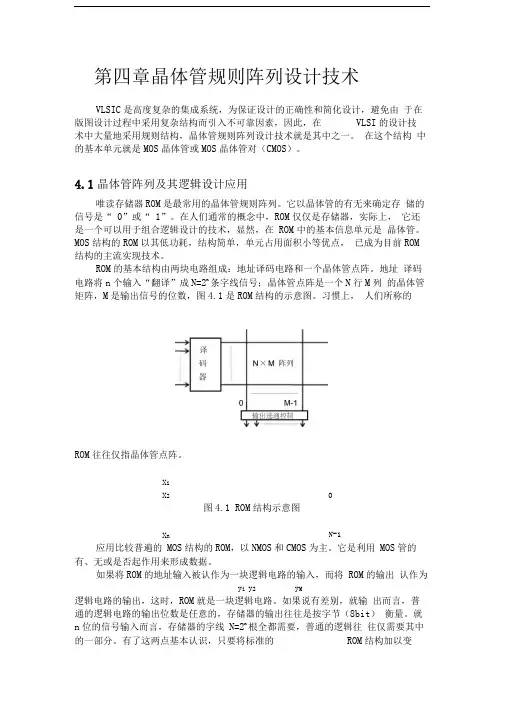

ROM 的基本结构由两块电路组成:地址译码电路和一个晶体管点阵。

地址 译码电路将n 个输入“翻译”成N=2n条字线信号;晶体管点阵是一个N 行M 列 的晶体管矩阵,M 是输出信号的位数,图4.1是ROM 结构的示意图。

习惯上, 人们所称的ROM 往往仅指晶体管点阵。

图4.1 ROM 结构示意图应用比较普遍的 MOS 结构的ROM ,以NMOS 和CMOS 为主。

它是利用 MOS 管的有、无或是否起作用来形成数据。

如果将ROM 的地址输入被认作为一块逻辑电路的输入,而将 ROM 的输出 认作为逻辑电路的输出,这时,ROM 就是一块逻辑电路。

如果说有差别,就输 出而言,普通的逻辑电路的输出位数是任意的,存储器的输出往往是按字节(8bit ) 衡量。

就n 位的信号输入而言,存储器的字线 N=2n根全都需要,普通的逻辑往 往仅需要其中的一部分。

有了这两点基本认识,只要将标准的 ROM 结构加以变X i X 2X nN-1y i y 2y M化,就可以实现我们所需的逻辑。

当然,基本的ROM结构仅适用于组合逻辑电路,如果在ROM的输出加上记忆单元和信息反馈,它同样可以满足时序逻辑的需要,实际上,人们也是这样做的。

VDMOS功率晶体管的版图设计系专业姓名班级学号指导教师职称指导教师职称设计时间摘要VDMOS 是微电子技术和电力电子技术融和起来的新一代功率半导体器件。

因具有开关速度快、输入阻抗高、负温度系数、低驱动功率、制造工艺简单等一系列优点,在电力电子领域得到了广泛的应用。

目前,国际上已形成规模化生产,而我国在 VDMOS 设计领域则处于起步阶段。

本文首先阐述了 VDMOS 器件的基本结构和工作原理,描述和分析了器件设计中各种电性能参数和结构参数之间的关系。

通过理论上的经典公式来确定 VDMOS 的外延参数、单胞尺寸和单胞数量、终端等纵向和横向结构参数的理想值。

根据结构参数,利用L-edit版图绘制软件分别完成了能够用于实际生产的60V、100V、500V VDMOS 器件的版图设计。

在此基础之上确定了器件的制作工艺流程,并对工艺流水中出现的问题进行了分析。

最后,总结全文,提出下一步研究工作的方向。

关键词:,功率半导体器件,版图设计,原胞,击穿电压目录第1章绪论电力电子系统是空间电子系统和核电子系统的心脏,功率电子技术是所有电力电子系统的基础。

VDMOSFET 是功率电子系统的重要元器件,它为电子设备提供所需形式的电源以及为电机设备提供驱动。

几乎大部分电子设备和电机设备都需用到功率 VDMOS 器件。

VDMOS 器件具有不能被横向导电器件所替代的优良性能,包括高耐压、低导通电阻、大功率和可靠性等。

半导体功率器件是电力电子系统进行能量控制和转换的基本电子元器件,也称为电力电子开关器件。

它是用来进行高效电能形态变换、功率控制与处理,以及实现能量调节的新技术核心器件。

电力电子技术的不断发展为半导体功率器件开拓了广泛的应用领域,而半导体功率器件的可控制特性决定了电力电子系统的效率、体积和重量。

实践证明,半导体功率器件的发展是电力电子系统技术更新的关键。

通常,半导体功率器件是一种三端子器件,通过施加于控制端子上的控制信号,控制另两个端子处于电压阻断(器件截至)或电流导通(器件导通)状态。

晶体管原理与设计一、引言在现代电子技术中,晶体管是一种至关重要的元件。

它是现代计算机和各种电子设备的基础构建单元,广泛应用于通信系统、嵌入式系统、数字电路和模拟电路等领域。

本文将深入探讨晶体管的原理和设计,以及其在电子技术领域的重要性。

二、晶体管的工作原理晶体管是一种半导体器件,能够实现信号放大、开关控制和电流放大等功能。

其内部结构由P型半导体、N型半导体和PN结构组成,通过对电压的控制实现信号放大与开关控制。

2.1 PN结PN结是晶体管的核心组成部分,在P型半导体与N型半导体之间形成一个结。

当施加适当正向偏置电压时,P型区域中的空穴和N型区域中的电子会向结区域扩散,形成扩散电流。

当施加适当反向偏置电压时,会形成势垒,电流通过受阻。

2.2 三极管结构三极管是一种常见的晶体管结构,由发射极、基极和集电极组成。

当在基极输入一个小电流时,发射极和集电极之间的电流会得到放大,并可以控制集电极输出电流的大小。

三极管通过对输入信号的调制,实现了放大功能。

三、晶体管的设计考虑因素在设计晶体管电路时,需要考虑一系列因素以确保其性能和可靠性。

3.1 尺寸和材料选择晶体管的尺寸和材料选择对其工作特性产生重要影响。

材料的选择应考虑导电性和热传导性能,如硅、锗等。

而晶体管的尺寸会影响其电流倍增和速度。

3.2 偏置设置晶体管的偏置设置可以通过外加电压或电流实现。

适当的偏置可以确保晶体管正常工作,并且在不同工作状态下具有合理的响应。

3.3 散热设计晶体管在工作过程中会产生热量,如果不能及时有效散热,会导致温度升高,甚至损坏晶体管。

因此,在设计中需要考虑散热问题,采取散热措施,如散热片、散热底座等。

3.4 噪声和干扰抑制在电子设备中,噪声和干扰是晶体管设计中需要面对的问题。

采用合适的抑制措施,如差分信号处理、屏蔽等,可以有效减少噪声和干扰对晶体管性能的影响。

四、晶体管的应用领域晶体管广泛应用于各种电子设备和系统中,为现代科技的发展提供了重要支持。

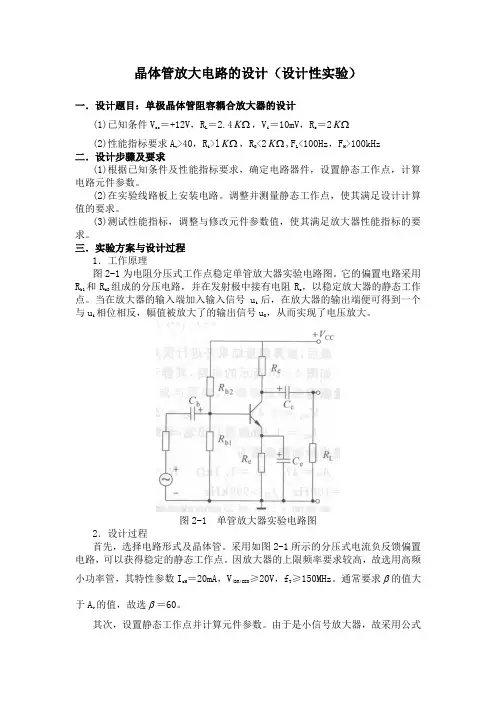

晶体管放大电路的设计(设计性实验)一•设计题目:单极晶体管阻容耦合放大器的设计(1) 已知条件V Cc= +12V, F L= 2.4 K0 , V = 10mV R = 2K Q⑵性能指标要求A v>40, R>l , R O<2K「,F L<100H Z R>100kHz二•设计步骤及要求(1) 根据已知条件及性能指标要求,确定电路器件,设置静态工作点,计算电路元件参数。

(2) 在实验线路板上安装电路。

调整并测量静态工作点,使其满足设计计算值的要求。

(3) 测试性能指标,调整与修改元件参数值,使其满足放大器性能指标的要求。

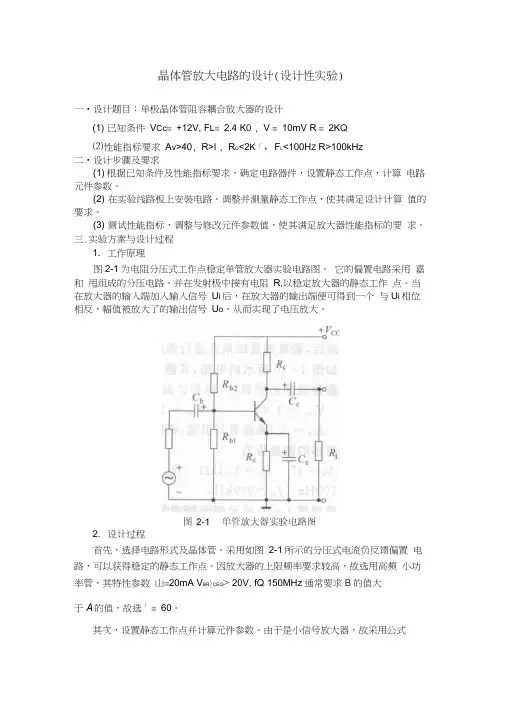

三.实验方案与设计过程1. 工作原理图2-1为电阻分压式工作点稳定单管放大器实验电路图。

它的偏置电路采用嘉和甩组成的分压电路,并在发射极中接有电阻R,以稳定放大器的静态工作点。

当在放大器的输入端加入输入信号U i后,在放大器的输出端便可得到一个与U i相位相反,幅值被放大了的输出信号U o,从而实现了电压放大。

2. 设计过程首先,选择电路形式及晶体管。

采用如图2-1所示的分压式电流负反馈偏置电路,可以获得稳定的静态工作点。

因放大器的上限频率要求较高,故选用高频小功率管,其特性参数山=20mA V BR)CEQ> 20V, fQ 150MHz通常要求B的值大于A的值,故选1 = 60。

其次,设置静态工作点并计算元件参数。

由于是小信号放大器,故采用公式法设置静态工作点Q,计算如下: 要求R>l (Rr 5),根据公式“r b (1「)嗨七00「皿I eQ (mA) I CQ (mA)I C Q 26mA = 2.2mA 1000 -300取 I CQ =2mA若取V bQ =3V,由 Re : V bQ -Vbe1 CQ由"誌―曲为使静态工作点调整方便, 尺2由20k 」固定电阻和100k 」电位器串联而 成。

由于(R S r be ) :: (R C R L ),比较「(3~10)25貝 %)Q -(3~ 10)2二 f L (R c R L )由Cwef^er 8.2^取标称值10汀取C C =C b =10l F ,=1.15k 1,取标称值1k-1V CC V bQR b2 :R b1 =57kOV bQ20罟黑I CQ (mA)=1.08k 1由心二得V i__ L 妲r ber be A VR L R L'=1k 「, R L - R L综合考虑,取标称值2.4 k-R b1 ' R b22 、函数信号发生器 4 、交流毫伏表6、直流毫安表 8 、万用电表9、晶体三极管3DG6< 1( 50〜100)或9011X 1、电阻器、电容器若干 五、实验内容实验电路如图2— 2所示。

晶体管规则阵列设计技术介绍晶体管规则阵列(Transistor-Transistor Logic,TTL)是一种数字集成电路(IC)设计技术,广泛应用于计算机、通信、工业控制等领域。

TTL电路使用晶体管作为主要元件,并通过特定的布局规则和逻辑门设计,实现各种逻辑功能。

本文将介绍晶体管规则阵列设计技术的基本原理、特点和应用。

基本原理晶体管规则阵列设计技术基于晶体管的开关能力和逻辑门的组合。

每个晶体管都可以作为一个开关,用于控制电流通断。

逻辑门由多个晶体管组成,通过它们之间的连接方式和工作状态,实现特定的逻辑功能。

常见的逻辑门包括与门(AND)、与非门(NAND)、或门(OR)、或非门(NOR)、非门(NOT)等。

这些逻辑门可以通过组合和级联,构建出更复杂的逻辑电路,实现各种数字逻辑功能。

晶体管规则阵列设计技术的基本原理是通过优化晶体管的连接方式和逻辑门的布局,以实现电路功能的快速、高效和稳定。

通过合理的设计,可以减少功耗、提高速度,并提供更高的集成度和可靠性。

特点晶体管规则阵列设计技术具有以下特点:1.高速度:由于TTL电路基于晶体管的开关能力,工作速度较快,通常可达数百兆赫兹,满足多数应用的需求。

2.低功耗:晶体管规则阵列设计技术可以通过优化电路结构和电流传输路径,减少功耗。

相较于其他数字逻辑技术,TTL电路的功耗较低。

3.可靠性:TTL电路采用晶体管作为主要元件,具有较高的可靠性和稳定性。

它能适应更宽的温度范围和供电条件,并具有较强的抗干扰能力。

4.灵活性:晶体管规则阵列设计技术允许设计师根据需求选择适当的逻辑门和电路结构,以满足不同应用的要求。

它支持多种逻辑功能的组合和级联,能够实现复杂的数字电路设计。

应用晶体管规则阵列设计技术在各个领域都有广泛的应用,包括但不限于以下几个方面:1.计算机:TTL电路广泛用于计算机的中央处理器(CPU)、内存和接口电路。

它们被用于实现各种算术逻辑运算、控制信号的产生和传输等功能。

电子器件课程设计中功率开关晶体管设计班级:姓名:学号:指导老师:中功率开关晶体管设计一、设计指标说明1、设计要求体管设计的任务就是根据使用的要求,确定主要电学参数及指标,设计出满足参数指标要求的纵向结构参数、横向结构参数和热学参数。

晶体管对纵向结构的要求是确定芯片结构和制造工艺的重要依据。

设计一个中功率开关晶体管,重点考虑其开关特性和频率特性,具体的设计指标说明如下:CC V =25V, BB V =1.5V , L R =50Ω;B R =100Ω, 脉冲幅度7.5V, 脉冲宽度1.5s μ;脉冲重复频率 1.5Z kH , on t =50ns , off t =100ns , cm I =800mA , cm P =700mW , T f ≥100M Z H , V BV CBO 60≥,SUS V =45V(集电极维持电压) DC β>20(CE V =1V, C I =500mA )2、设计思想总述1.根据使用要求选定主要电学参数,确定主要电学参数的设计指标。

2 根据设计指标的要求,了解同类产品的现有水平和工艺条件,结合设计指标 和 生 产经验进行初步设计。

3.根据初步设计方案,对晶体管的电学参数进行验算,在此基础上,对设计方 案 进 行综合调整和修改。

4 根据初步设计方案进行小批童试制。

通过边设计,边试制,暴露问题解决矛盾,修改和完善设计方案。

二、器件主要参数决定因素的分析当晶体管工作于饱和与截止状态时,在共射甲类运用条件下,较小的基极电流可以控制很大的集电极电流,从而可作为电子开关使用。

如图一所示为典型的开关电路,在放大状态时,B I 增加使C I 增加,当C I 上升到使CE L C CC V R I V +==BE V 时,集电结从反偏上升到零偏,进入临界饱和态。

L CC CS R V I ≈,此时L CC CS BS R V I I ββ==,此时晶体管的C 、E 间近似短路,相当于C 、E 间的开关闭合;当输入脉冲为负或零,发射结反偏,晶体管进入截止状态时,晶体管相当于开关断开。

晶体管电路设计精讲第八贴学习内容:1、三极管的基本特性2、通过参数挑选三极管知己知彼,百战百胜前面几贴,我们已经对晶体管放大电路有了一定的认识,现在我们就要开始进入我们的电路设计过程了。

就象我们平时做一件事一样,在做之前先要有一个目标或者说是目的。

但是仅有目标就行了吗?还要有实现目标的方法,可利用的资源,和实现手段的限制等等。

用一个很简单的例子来说明这个过程:现在,老板通知你明天到北京开会。

你应该怎样做呢?马上买车票直奔北京么?如果你真的是这样想的而且这样做了,相信用不到明天你的老板就会通知你不用来上班了。

看起来是一个很简单的问题,但是它涉及到的内容绝对不简单,我们可以把它当做一个系统的工程来分析下。

最简单的办法是问自己几个问题:1、明天要开什么会?2、在哪里开?3、几点报道?4、需要做哪些准备?这是一些最基本的必须知道的条件。

也是我们做好这件事情所要必须了解的东西。

例子很简单,让我们切换回来,当我们设计一个电路时是不是也要有一些条件和要求摆在我们面前呢?我在QQ里经常会遇到一些朋友提出类似的问题:“我要做一个功放,求图纸”,“我要做个稳压电源该怎么做”等等诸如此类的问题。

那么这时候,一般我会反问他们,“你要做一个多大的功放,是用电脑做音源还是用话筒?”,“你要做的稳压电源输出多少电压,电流,输入多少”。

而现在我们设计一个放大器,同样要有一定的条件要求,按着这个要求去投计选材,做出来的才是一个合格的作品。

下面就是我们这次要设计的放大器的基本要求了:让我们来分析一下这个要求。

首先第一条,电压增益也就是电压放大倍数是5倍,这一点很明确,不用多说。

第二条,最大输出电压5Vp-p,这个要求里面的意思就很多了。

先解释下Vp-p的概念,翻译成中文是“电压峰峰值”的意思,从字面上就可以理解了,就是指一个交流信号在某一时间段内波峰和波谷(正向峰值和负向峰值)的电压差。

这个值代表了信号的幅度信息。

还有以后我们要经常用到的有Vrms(有效值),Vp(峰值),它们之间的关系如下图它们之间的关系式如下,这几个公式希望大家能记住并理解:Vp-p = 2VpVp = √2 Vrms = 1.414 VrmsVrms = 1/√2 Vp = 0.707 VpVp-p = 2 x √2 Vrms = 2.828 VmrsVrms的物理意义在于,某个信号在一个完整周期内在负载上所做的功与相同的直流电压在同一时间段同一个负载上所做的功相同。

晶体管放大电路的设计(设计性实验)一.设计题目:单极晶体管阻容耦合放大器的设计(1)已知条件Vcc =+12V,RL=2.4KΩ,V i=10mV,R s=2KΩ(2)性能指标要求Av >40,Ri>l KΩ,R O<2KΩ,F L<100Hz,F H>100kHz二.设计步骤及要求(1)根据已知条件及性能指标要求,确定电路器件,设置静态工作点,计算电路元件参数。

(2)在实验线路板上安装电路。

调整并测量静态工作点,使其满足设计计算值的要求。

(3)测试性能指标,调整与修改元件参数值,使其满足放大器性能指标的要求。

三.实验方案与设计过程1.工作原理图2-1为电阻分压式工作点稳定单管放大器实验电路图。

它的偏置电路采用R b1和Rb2组成的分压电路,并在发射极中接有电阻Re,以稳定放大器的静态工作点。

当在放大器的输入端加入输入信号ui后,在放大器的输出端便可得到一个与ui 相位相反,幅值被放大了的输出信号u,从而实现了电压放大。

图2-1 单管放大器实验电路图2.设计过程首先,选择电路形式及晶体管。

采用如图2-1所示的分压式电流负反馈偏置电路,可以获得稳定的静态工作点。

因放大器的上限频率要求较高,故选用高频小功率管,其特性参数IcM =20mA,V(BR)CEO≥20V,fT≥150MHz。

通常要求β的值大于Av的值,故选β=60。

其次,设置静态工作点并计算元件参数。

由于是小信号放大器,故采用公式法设置静态工作点Q ,计算如下:要求R i >l K Ω(R i ≈r be ),根据公式26()26()(1)300()()be b eQ cQ mV mV r r I mA I mA ββ=++≈+26 2.21000300cQ I mA mA β<=-取2cQ I mA = 若取3bQ V V =,由 1.15bQ bee cQV V R k I -≈=Ω,取标称值1k Ω由120(5~10)bQ b V R k β==Ω2157CC bQ b b bQV V R R k V -≈=Ω为使静态工作点调整方便,2b R 由20k Ω固定电阻和100k Ω电位器串联而成。

《晶体管电路设计(上)》一、晶体管基础知识1. 晶体管的分类与结构晶体管是一种半导体器件,按照结构和工作原理的不同,可分为两大类:双极型晶体管(BJT)和场效应晶体管(FET)。

双极型晶体管包括NPN型和PNP型,而场效应晶体管主要包括增强型MOS管和结型场效应管。

2. 晶体管的工作原理(1)双极型晶体管(BJT)工作原理:当在基极与发射极之间施加适当的正向电压,基区内的少数载流子会增多,导致集电极与发射极之间的电流增大,从而实现放大作用。

(2)场效应晶体管(FET)工作原理:通过改变栅极电压,控制源极与漏极之间的导电通道,实现电流的放大。

3. 晶体管的特性参数(1)直流参数:包括饱和压降、截止电流、放大系数等。

(2)交流参数:包括截止频率、增益带宽积、输入输出阻抗等。

二、晶体管放大电路设计1. 放大电路的基本类型(1)反相放大电路:输入信号与输出信号相位相反。

(2)同相放大电路:输入信号与输出信号相位相同。

(3)电压跟随器:输出电压与输入电压基本相等。

2. 放大电路的设计步骤(1)确定电路类型:根据实际需求选择合适的放大电路类型。

(2)选择晶体管:根据电路要求,选取合适的晶体管型号。

(3)计算电路参数:包括偏置电阻、负载电阻、耦合电容等。

(4)电路仿真与调试:利用电路仿真软件进行仿真,并根据实际效果调整电路参数。

三、晶体管开关电路设计1. 开关电路的基本原理晶体管开关电路利用晶体管的截止和饱和状态,实现电路的通断控制。

当晶体管处于截止状态时,开关断开;当晶体管处于饱和状态时,开关闭合。

2. 开关电路的设计要点(1)选择合适的晶体管:确保晶体管在截止和饱和状态下都能满足电路要求。

(2)优化电路参数:合理设置驱动电流、开关速度等参数,以提高开关电路的性能。

(3)考虑开关损耗:在设计过程中,尽量降低开关过程中的能量损耗,提高电路效率。

《晶体管电路设计(上)》四、晶体管稳压电路设计1. 稳压电路的作用与分类稳压电路的主要作用是保证输出电压在一定范围内稳定不变,不受输入电压和负载变化的影响。

功率晶体管课程设计一、教学目标本节课的教学目标是让学生掌握功率晶体管的基本原理、结构和应用,培养学生分析问题和解决问题的能力。

具体目标如下:1.知识目标:(1)了解功率晶体管的结构和原理;(2)掌握功率晶体管的工作特性;(3)熟悉功率晶体管的应用领域。

2.技能目标:(1)能够分析功率晶体管的工作原理;(2)能够运用功率晶体管解决实际问题;(3)能够进行功率晶体管的简单设计和优化。

3.情感态度价值观目标:(1)培养学生对功率晶体管技术的兴趣和好奇心;(2)使学生认识到功率晶体管在现代科技中的重要性;(3)培养学生勇于探索、创新的精神。

二、教学内容根据课程目标,本节课的教学内容如下:1.功率晶体管的基本原理:介绍功率晶体管的工作原理,包括PN结的形成、载流子的运动和导电特性等。

2.功率晶体管的结构:讲解功率晶体管的常见结构类型,如NPN型、PNP型等,并分析各种结构的特点和应用。

3.功率晶体管的工作特性:阐述功率晶体管的导通和截止条件,分析其输出特性、输入特性和开关特性等。

4.功率晶体管的应用:介绍功率晶体管在电子设备中的应用领域,如放大器、开关电路、稳压器等,并分析实际应用中的关键参数。

三、教学方法为了提高教学效果,本节课采用以下教学方法:1.讲授法:讲解功率晶体管的基本原理、结构和应用,使学生掌握基础知识。

2.案例分析法:分析实际应用中的功率晶体管电路,让学生学会运用所学知识解决实际问题。

3.实验法:安排课后实验,让学生亲自动手操作,加深对功率晶体管的理解和掌握。

4.讨论法:学生分组讨论,培养学生的团队协作能力和口头表达能力。

四、教学资源为了支持教学内容和教学方法的实施,本节课准备以下教学资源:1.教材:选用权威、实用的教材,如《功率晶体管原理与应用》。

2.参考书:提供相关领域的参考书籍,如《晶体管电路原理》。

3.多媒体资料:制作精美的PPT,生动展示功率晶体管的结构和原理。

4.实验设备:准备功率晶体管实验套件,让学生动手实践。

晶体管放⼤电路设计晶体管放⼤电路设计丁炳亮⼀、基础理论具体⼀个晶体管电路的计算其实并不困难,真正困难的是根据要求设计出合乎要求且实际性能优良的电路。

晶体管电路的计算主要是静态⼯作点和动态参数的估算。

⾸先需要准备⼀些基础知识⽤于理论计算。

1、晶体管计算中⽤到的⼏个重要公式:第⼀个公式是PN节伏安特性公式,公式中电流电压为直流。

第⼆个公式是共射接法时,BE的输⼊的动态电阻,经常⽤到的⼀个公式。

其中rbb⽐较⼩,当电流很⼩时可以忽略,或者认为是200欧,⼀些晶体管规格书会给出。

需要注意是计算交流等效电路时才有⽤到这个公式。

第三个公式只要记住26mV即可。

第四公式为转移电导,也就是把晶体管等效为电压控制电流源(h模型等效为CCCS,Pi模型等效为VCCS)。

第五、六个公式为考虑厄利电压时的共射直流放⼤倍数和CE间电阻,看作CCCS时CE间电阻应该是⽆穷,但是厄利电压的存在使得该值变⼩。

2、h等效和Pi等效(微变模型)⼀般⼯程计算使⽤简化的等效模型就能满⾜要求了。

简化的h等效模型简化的Pi等效模型3、共射电压增益h等效模型计算有Pi等效模型计算有,注意这个公式忽略了rbb,实际上在电流较⼤时是不能忽略的,例如β=200,ICQ=26mA,则(26mV/ICQ)*β=200欧,与rbb相近,因此BE结的电压约等于Ube/2。

利⽤上个公式在不考虑负载时有。

⼆、最简单的放⼤电路1、设计需求信号源最⼤幅度为50mV,三极管为9013,h=250,电源电压5V。

这⾥的h值是⽤万⽤表测量出来的,实际的电路设计中h值有⼀个较⼤的范围,所以需要考虑对静态⼯作点的影响。

2、静态⼯作点估算⼀般情况UCQ=Vcc/2,R3是为了减⼩失真,应该远⼤于rbe,但取的过⼤则实际输⼊到晶体管的电流就很⼩,这⾥取3.3K较为合适。

ICQ的确定是关键,需要先计算出最⼤的输⼊电流幅度,这⾥估计rbe=1K,则IBQ=50mV/4.3K=11.6uA,为了避免失真,另外考虑⼿头上现有的电阻值,所以IBQ设置为17.4uA,即R2=250K,R1=2.5V/(IBQ*h)=575欧,⼿头上只有510欧电阻,所以实际的UCQ=2.8V 左右。

晶体管电路设计引言晶体管电路设计是电子电路设计中的一个重要方面。

晶体管作为一种半导体器件,广泛应用于各种电子设备中,如计算机、手机、电视等。

本文将介绍晶体管电路设计的基本概念、原理和实践方法。

晶体管基础知识什么是晶体管晶体管,全称为晶体管三极管,是一种用于放大和开关电信号的半导体器件。

它由三个区域构成,分别为发射区、基区和集电区。

晶体管的工作原理是通过控制基极电流来控制集电区电流。

根据晶体管的PN结类型可以分为NPN型和PNP型。

晶体管的应用晶体管广泛应用于电子设备中的各种电路中,如放大电路、开关电路、数字电路等。

晶体管可以放大电信号,实现信号放大,同时也可以作为开关控制电流的通断。

晶体管电路设计的步骤晶体管电路设计涉及多个步骤,下面将逐一介绍。

确定电路需求在进行晶体管电路设计之前,首先需要明确电路的需求。

包括电路的功能、输入输出要求、工作条件等。

根据电路需求确定晶体管的工作模式和参数。

选择合适的晶体管型号根据电路需求和工作模式,选择适合的晶体管型号。

根据晶体管的参数表,比较不同型号的晶体管的特性,如电流增益、最大功率、频率响应等,选择合适的晶体管型号。

绘制电路图根据电路需求和选择的晶体管型号,绘制电路图。

电路图应包括晶体管的引脚连接、元器件连接、电源连接等。

电路图绘制要符合电路设计规范,清晰明了。

计算电路参数根据电路需求和电路图,进行电路参数的计算。

包括电阻、电容、电感等元器件的选取和计算。

同时还需要计算晶体管的偏置电流、工作点等参数。

仿真和调试在进行实际的电路实现之前,可以通过软件仿真工具对电路进行仿真。

通过仿真可以评估电路的性能、稳定性等。

如果发现问题,可以进行调试和优化。

PCB设计和制造完成电路参数计算、仿真和调试后,需要进行PCB (Printed Circuit Board)的设计。

PCB设计是将电子元器件进行布局并进行连线的过程。

完成PCB设计后,可以进行PCB的制造。

实际设计和测试根据PCB设计进行实际的电路制作和组装。

VDMOS功率晶体管版图设计VDMOS功率晶体管的版图设计系专业姓名班级学号指导教师职称指导教师职称设计时间2012.9.15-2013.1.4摘要VDMOS 是微电子技术和电力电子技术融和起来的新一代功率半导体器件。

因具有开关速度快、输入阻抗高、负温度系数、低驱动功率、制造工艺简单等一系列优点,在电力电子领域得到了广泛的应用。

目前,国际上已形成规模化生产,而我国在VDMOS 设计领域则处于起步阶段。

本文首先阐述了VDMOS 器件的基本结构和工作原理,描述和分析了器件设计中各种电性能参数和结构参数之间的关系。

通过理论上的经典公式来确定VDMOS 的外延参数、单胞尺寸和单胞数量、终端等纵向和横向结构参数的理想值。

根据结构参数,利用L-edit版图绘制软件分别完成了能够用于实际生产的60V、100V、500V VDMOS 器件的版图设计。

在此基础之上确定了器件的制作工艺流程,并对工艺流水中出现的问题进行了分析。

最后,总结全文,提出下一步研究工作的方向。

关键词:,功率半导体器件,版图设计,原胞,击穿电压目录第1章绪论电力电子系统是空间电子系统和核电子系统的心脏,功率电子技术是所有电力电子系统的基础。

VDMOSFET 是功率电子系统的重要元器件,它为电子设备提供所需形式的电源以及为电机设备提供驱动。

几乎大部分电子设备和电机设备都需用到功率VDMOS 器件。

VDMOS 器件具有不能被横向导电器件所替代的优良性能,包括高耐压、低导通电阻、大功率和可靠性等。

半导体功率器件是电力电子系统进行能量控制和转换的基本电子元器件,也称为电力电子开关器件。

它是用来进行高效电能形态变换、功率控制与处理,以及实现能量调节的新技术核心器件。

电力电子技术的不断发展为半导体功率器件开拓了广泛的应用领域,而半导体功率器件的可控制特性决定了电力电子系统的效率、体积和重量。

实践证明,半导体功率器件的发展是电力电子系统技术更新的关键。

通常,半导体功率器件是一种三端子器件,通过施加于控制端子上的控制信号,控制另两个端子处于电压阻断(器件截至)或电流导通(器件导通)状态。

晶体管设计大功率晶体管是功率驱动电路的核心元件。

大功率晶体管通常工作在极限参数状态下,其主要参数是击穿电压和电流容量。

分析了大功率晶体管的工作原理和设计原则,并针对一个具体的大功率晶体管的参数要求,设计了晶体管的纵向和横向结构尺寸,并确定了材料参数和工艺参数。

大功率品体管以其电压高,电流大,功率大的独特优势随着社会的进步得到了不断的拓展。

在五十年代,锗合金工艺相对硅成熟,因此锗管成为大功率品体管的先声,在大功率晶体管中占据着主流地位。

硅大功率晶体管在1956年问世。

从此品种繁多的各种硅功率管大量应用到通讯和雷达设备、发射电路中的功率放大器、倍频器和振荡器等。

由于硅材料容易获得且能工作在较高温度具有小的反向电流和高的耐压特性等优点,因而在后期硅的发展速度远远超过锗管。

功率开关管作为各种类型开关电源的主功率开关器件,随着开关电源的日益发展,其应用范围更加广泛。

目前,硅大功率晶体管已广泛地应用于:(1)电源开关、反相器、电机速度控制:(2)汽车的点火电路,制动电路;(3)用于广播、电视的高频放大和电子计算机,通信设备的电源装置和各类开关电源等方面。

(4)军事工业和航空航天工业大功率设备。

大功率晶体管以其电压高、电流大、功率大的独特优势在自动化控制系统、计算机电源系统、交通电气设备、不停电电源装置及各类开关电源、各种变流系统、军事工业及航空航夭工业部门的大功率设备中占有非常重要的地位。

即使在集成电路技术和新型电力电子器件迅速发展的今天,普通型大功率晶体管在半导体产业这个大家族中仍占有一席之地,特别是在集成电路所不能胜任的领域(诸如低噪声,高耐压,大电流,大功率和微波性能等方面)发挥愈来愈大的作用。

因此,进一步研究、设计、制造大功率晶体管具有重要意义。

大功率晶体管区别于小功率晶体管的最大工作特点就是在大的耗散功率或输出功率条件下工作(即在大电流或高电压)。

因此,大功率品体管除了在大电流一下保证足够的放大能力和承受较高的集电极电压外,还必须有良好的散热能力。

2. 1大功率晶体管的大电流效应从晶体管原理可知,当晶体管在大电流或则高压下工作时,会发生一些不同于小电流工作的效应和现象:基区电导调制效应,基区增宽效应,基极电阻自偏压效应和发射极电流集中现象等。

基区电导调制效应:从晶体管的工作机理可知,晶体管的工作电流越大,则注入到基区的少数载流子就越多。

为了保持基区电中性的要求,在基区内需要引入同等数量的多数载流子。

这样一来,就会使基区内导电的载流子浓度增加,增大了基区的电导率,也就是说,基区的电导率受到了工作电流的调制。

山于基区电导率的增加,将使少子在基区内被复合的几率增加,导致电流放大系数下降。

基区增宽效应:在大的电流密度时,晶体管集电结空间电荷区域内的运动载流一子浓度将大大增加。

当集电极电流密度达到或超过某一定值时,由于运动载流子浓度的急剧增加,致使集电结附近的空间电荷出现重新分布的现象一基区一边集电结的电荷密度将大大增加,而集电区一边的集电结空间电荷密度将下降。

由于基区和集电区结附近要求电荷平衡,空间电荷的边界将向运动载流子的迁移方向移动,在发射结位置不变时,集电结的移动将相应的导致晶体管基区宽度增加,从而使电流放大系数下降。

2. 2大功率晶体管的饱和压降由晶体管的原理可知,饱和压降Uces的表达式:(2.1)式中为晶体管反向运用的电流增益(一般为0. 1),式右边第一项为0. 1 V-0. 3V左右,第二项对饱和压降起主要贡献。

从式2. 1可知,要想降低Uces就必须从减小集电极串联电阻rcs着手。

图2-2是集电极串联电阻示意图,从图中可以看出:rcs =rc1+rc2+rc3 (2. 2) 要精确地计算rcs是很困难的,下面只是通过大量的近似来粗略估算下,以便从中找出减小rcs的办法。

由于在饱和工作区时,Vbc>0,有空穴注入到发射区下面的外延层中,产生电导调制效应,使rc1下降,在深饱和、大注入时,可使rc1下降很多,以致rc1可以忽略不计,即饱和时的集电极串联电阻rcs近似为:(2.3)C 1) rc2.的计算因为电流由集电结垂直下来后转角流入埋层,所以取拐角的电阻为1/2的薄层电阻值,因而在计算rc2长度时,可以从发射区接触孔中心到集电极接触孔中心的长度L,:_。

即可,饥.为埋层宽度,Rs一瓜为埋层的方块电阻。

(2.4)(2) rc3的计算在进行rc3的计算时,假定其图形是一个上下底为矩形且相互平行的锥体,且作以下的近似:上底、下底各为等位面;锥体内的电流只在垂直方向流动:在上、下面上的电流分布是均匀的。

这样结构的电阻可用下式求得:(2.5)式中:P为材料的电阻率;T为锥体的高度:W, L为顶面矩形的宽和长;b为底面矩形与顶面矩形相应的宽和长的比值,平行锥体的厚度T可用下式来近似估算: (2.6)式中:Tepi为外延层的厚度:X jc为集电极结深.2. 3大功率晶体管的击穿分析大功率晶体管击穿包括晶体管的热击穿,雪崩击穿,表面击穿.晶体管的热击穿就是由于管子局部或全部过热而使器件突然损坏的一种现象,这往往是山于晶体管工作温度—参数不稳定性引起的。

热击穿通常先在晶体片的局部区域发生的,其原因是晶体管结构和材料的不均匀性。

在平行于P-N结方向产生电场梯度,导致电流的局部集中和在晶体片产生温度梯度。

由于局部温度增加和散热面积缩小,从而更促使管子温度增加。

最后导致管子完全损坏。

为了避免热击穿,则需要改善晶体管的结构,提高晶体管材料的均匀性,摒除易熔金属或合金,尽量提高结面积上的电流分部的不均匀性,而减少管子内部过热现象的出现。

大功率晶体管的设计,即要达到功率容量的要求,又要使管子的温度限制在最高结温以下,则需增强晶体管向外界散发热量的能力。

在晶体管中产生的热量可以通过下述三个方式散发出去:(I)在集电结产生的热量首先传递至晶片表面,再由晶片表面经电极传至管壳。

(2)通过管壳内部气体的对流,或者通过辐射的方式将热量传递至管壳。

(3)管壳通过辐射或与周围空气的传导,将热量散发至周围空气中。

雪崩击穿即内场击穿,它是由于结的空间电荷内,当运动的载流子大量地通过此空间的电荷区域并碰撞点阵原子,使点阵原子剧烈地电离而产生电子空穴对。

他随着空间电场的加大而加剧。

杂质浓度梯度a愈大,缓变结的雪崩击穿电压Vb越低,Vb正比于,杂质浓度梯度a不仅与结附近的杂质分布形式有关,且与扩散结的结深Xj:、衬底晶片的杂质浓度N0,分布形式有关,扩散层表面浓度Ns 、有关。

表面效应引起的电击穿,归根到底,都是因为晶体表面的不完善性,致使表面电场集中,以致电击穿先于体内发生,或者结表面有沾污现象,引起结的反向电流显著增大和不稳定现象。

表面效应引起的电击穿,归根到底,都是因为晶体表面的不完善性,致使表面电场集中,以致电击穿先于体内发生,或者结表面有沾污现象,引起结的反向电流显著增大和不稳定现象。

表面击穿现象归为以下几点:(1)在结的表面存在污物或杂质点,直接构成了漏电通道,致使结的耐压降低。

(2)由于管壳内存在有害气体的影响,或晶片周围气体介质发生改变,在晶体表面引起附加的电荷,使靠近表面层的载流子浓度提高,等效于晶体材料电阻率的下降,因而击穿电压值下降。

(3)由于结构和材料存在着缺陷,在表面出现局部的强龟场,并由此引起晶体表面状态的改变和反向漏电流的不稳定。

(4)对有Sio2膜保护的器件来说,由于Si02膜中难免掺入金属正离子或氧离子.这种离子的迁移造成结击穿电压的不稳定性。

因此我们应尽量减小晶片缺陷。

在满足性能要求下,尽量加宽处延层厚度和掺杂的均匀性;同时选取合适的发射极图形。

2. 4大功率晶体管的二次击穿(1)二次击穿现象从广义上讲,二次击穿是指器件承受的电压突然降低,电流急剧增大,器件由高压小电流状态突然跃入低压大电流状态的一种现象。

典型的二次击穿电流一电压特性曲线如图2-4所示。

当电压增加到雪崩击穿电压V,、时,电流急剧上升,AB段可称之为发生一次击穿。

当电流增加到B点,并在B点经过短暂停留之后,器件将由高压状态跃变到低压C点。

这时,如果电路无限流措施,电流将急剧增加,进入低压大电流区域CD段,直至最后烧毁。

(2)产生原因二次击穿主要是由于器件体内局部温度过高造成。

温度升高的原因是当正向偏置时由热不均衡性引起,反向偏置时由雪崩击穿引起。

因为晶体管的热阻在管子内部各处分布是不均匀的,在一些薄弱的区域,温度升高比其它部分高,形成所谓“热斑”,局部温度升高引起局部电流增加,电流增加又使温度升高,如此循环直至一个临界温度,造成管子的击穿。

雪崩击穿引起的二次击穿是由于发生一次雪崩击穿后,在某些点上因为电流密度过大,改变了结的电场分布,产生负阻效应从而使局部温度过高的一种现象。

鉴于上述分析,大功率管设计必须着重考虑两点:(1)大功率晶体管的饱和压降。

对大功率晶体管来一说,饱和压降是一个非常重要的参数,若饱和压降过大,将会限制它的工作电流的提高。

(2)击穿问题。

大功率晶体管工作在较大的耗散功率下,电流电压都具有相当大的数值,因而存在二次击穿问题。

3.大功率晶体管纵向结构设计大功率晶体管参数指标如下表所示:表3. 1大功率晶体管主要技术指标本文设计的大功率晶体管为具有外延层的N'-N -PN型平面晶体管,其结构模型如图3-1所示。

首先在低阻衬底N'型Si片上,先制作薄的N一型高阻外延层,外延层的电阻率ρc和厚度Wc.主要由管子所要求的集电极的击穿电压决定。

然后应用标准平面工艺,在Si表面生长氧化层,通过光刻和扩散等工艺,在外延层上先后制作所要求的电极图形的P型扩散基区和高浓度N‘扩散型发射区。

并在其上制作欧姆接触电极,形成了N"-N--P-N‘结构的外延平面工艺结构。

基区扩散层厚度(集电结深度Xjc)发射区扩散层厚度(发射结结深Xje. ),将由晶体管所要求的设计参数来决定。

基区宽度Wb是Xjc和Xje;。

二者之差:Wb=Xjc-Xje (3.1)为了达到集电极要求的工作电压,则须增大外延层厚度Wc.和提高其电阻率ρ,但外延层厚度Wc 提高后,集电极串联电阻也随之增大,而使管子的截止频率下降和输出特性恶化。

3. 1. 1集电结结深设计制造过浅或过深的P-N结都是有困难的。

由于晶片表面难免有破坏点和损伤存在,过浅的P-N结不易达到良好的反向耐压特性。

而过深的P-N结,不但需要长时间的扩一散时间,而且长时间的高温过程会引起晶体材料性能上的恶化。

由表1可知,本文设计功率晶体管的发射极和集电极之间的击穿电压为60V,山BVceo与Bcbo经验公式:其中n是常数,其值与晶体材料有关,对于硅N-P-N型硅平面管,n一般取4.由击穿电压与杂质浓度梯度的关系:式中aj是杂质浓度梯度,在上面的式子中,己算出BV cbo=151.83(V) ,结合实际,BVcbo与Eg和Nc有如下近似关系式中Nc是外延层杂质浓度,Eg是硅的禁带宽度,将Bvcbo=151.83 V代入上式,可得出:又由集电结杂质浓度梯度的表达式:式中Xje为集电结结深,Nbo为基区扩散表面杂质浓度(一般取Nbo=8x),将ajc = 2.36 x ,Nc= 5.09 x 代入上式,可求出:3. 1.2大功率晶体管的特征频率基区渡越时间。