可配置片上系统设计流程

- 格式:doc

- 大小:64.50 KB

- 文档页数:20

∙SoPC即片上可编程系统(SoPC-System on a Programmable Chip),是一种灵活、高效的SoC解决方案。

它将处理器、存储器、I/O口、LVDS等系统需要的作用模块集成到一个PLD器件上,构成一个可编程的片上系统。

它是PLD和SOC技术融合的结果。

目录∙构成sopc的三种方案∙sopc三种方案的比较∙sopc的特点∙sopc的开发流程∙sopc的解决方案构成sopc的三种方案∙ 1 基于FPGA嵌入IP硬核的SOPC系统:该方案是指在FPGA中预先植入处理器.最常用的是含有ARM32位知识产权处理器核的器件。

为了到达通用性,必须为常规的嵌入式处理器集成诸多通用和专用的接口,但增加了成本和功耗.如果将ARM或其它处理器核以硬核方式植入FPGA中,利用FPGA中的可编程逻辑资源,按照系统作用需求来添加接口作用模块,既能实现目标系统作用,又能降低系统的成本和功耗. 这样就能使得FPGA灵活的硬件设计和处理器的强大软件作用有机地结合在一起,高效地实现SOPC系统。

IP硬核直接植入FPGA存在以下不足: IP硬核多来自第三方公司,FPGA厂商无法控制费用,从而导致FPGA器件价格相对偏高. IP硬核预先植入,使用者无法根据实际需要改变处理器结构.更不能嵌入硬件加速模块(DSP). 无法根据实际设计需要在同一FPGA中集成多个处理器. 无法根据实际设计需要裁减处理器硬件资源以降低FPGA成本. 只能在特定的FPGA中使用硬核嵌入式处理器2 基于FPGA嵌入IP软核的SOPC系统:IP软核处理器能有效克服上述不足: 目前最有代表性的软核处理器分别是Altera公司的Nios II核,以及Xilinx公司的MicroBlaze核.特别是Nios II核,能很好的解决上述五方面的问题. Altera的Nios II核是用户可随意配置核构建的32位嵌入式处理器IP核,采用Avalon总线结构通信接口;包含由FS2开发的基于JTAG的片内设备内核. 在费用方面,由于Nios II是由Alter公司直接提供而非第三方厂商产品,故用户通常无需支付知识产权费用,Nios II的使用费用仅仅是其瞻仰的FPGA逻辑资源的费用3 基于HardCopy技术的SOPC系统:HardCopy就是利用原有的FPGA开发工具, 将成功实现于FPGA器件上的SOPC系统通过特定的技术直接向ASIC转化,从而克服传统ASIC设计中普遍存在的问题. ASIC (SOC)开发中难于克服的问题包括:开发周期长,产品上市慢,一次性成功率低,有最少投片量要求,设计软件工具繁多且昂贵, 开发流程复杂等.利用HardCopy技术设计ASIC,开发软件费用少,SOC级规模的设计周期不超过20周,转化的ASIC和用户设计习惯的掩模层只有两层,且一次性投片的成功率近乎100%,即所谓的FPGA 向ASIC的无缝转化用ASIC实现后的系统性能将必原来在HardCopy FPGA上验证的模型提高近50%,而功耗则降低40%.HardCopy技术是一种全新的SOC级ASIC设计解决方案,即将专用的硅片设计和F PGA至HardCopy自动迁移过程结合在一起的技术,首先利用Quartus II将系统模型成功实现于HardCopy FPGA上,然后帮助设计者把可编程解决方案无缝地迁移到低成本的ASIC上.这样, HardCopy器件就把大容量FPGA的灵活性和ASIC 的市场优势结合起来,实现对于有较大批量要求并对成本敏感的电子产品上,从而避开了直接设计ASIC的困难.sopc三种方案的比较∙sopc的特点∙SOPC结合了SOC和PLD、FPGA各自的优点,一般具备以下基本特征:至少包含一个嵌入式处理器内核;具有小容量片内高速RAM资源;丰富的IP Core资源可供选择;足够的片上可编程逻辑资源;处理器调试接口和FPGA编程接口;可能包含部分可编程模拟电路;单芯片、低功耗、微封装。

基于超大规模集成电路的片上系统设计与优化随着科技的不断进步和社会的快速发展,信息技术在各个领域中起到了至关重要的作用。

超大规模集成电路(Very Large Scale Integration,简称VLSI)作为信息技术发展的重要基石,已成为现代电子设备的核心组件之一。

而片上系统(System-on-Chip,简称SoC)作为VLSI技术的应用,更加强调了系统级整合的需求。

片上系统的设计和优化是一个极其关键且复杂的工作。

首先,设计一款功能强大、高性能的SoC需要深入了解应用场景和需求,确定所需硬件资源以及系统架构。

其次,在硬件设计阶段,需要对芯片的电路、布局、时序等方面进行细致的优化。

最后,软件设计和硬件设计需要有效地进行协同,以确保整个片上系统的稳定性和性能。

在片上系统设计中,硬件方面的优化包括以下几个方面。

首先是电路设计优化。

通过使用低功耗、高速度、可靠性更高的电路设计技术,可以降低功耗、提高频率和可靠性,使芯片具备更好的性能。

其次是布局优化。

通过优化不同电路元件之间的布局,可以减少电路之间的互相干扰,提高电路的稳定性。

此外,时序优化也是非常重要的,通过合理地优化时序,可以减少延迟,提高系统的响应速度。

在片上系统设计中,软件方面的优化也是不可忽视的。

首先是操作系统的优化。

合理地选择和配置操作系统,可以优化系统的资源利用率,并实现快速的任务调度。

其次是算法的优化。

针对特定的应用场景,通过设计高效的算法,可以减少计算时间和资源消耗,提高系统的性能。

此外,软件和硬件之间的协同设计也非常关键,在系统级别上合理地分配任务,充分发挥硬件和软件的优势,进一步提高系统的整体性能。

除了上述的设计优化,还有一些其他的方面需要考虑。

首先是能源管理。

在移动设备和嵌入式系统中,能源管理是一项非常重要的任务。

通过合理地设计和优化功耗管理方案,可以延长设备的续航时间,提高系统的能效。

其次是系统的测试和验证。

在设计完成后,需要对芯片进行全面的测试和验证,以确保系统的稳定性和可靠性。

• 152•定了整车机械系统的设计安装和改进方案。

硬件系统布置如图3所示,仿真结果如图4道路图像所示。

图3 整车布局图 图4 道路图像图5 实物图4 结语利用摄像头和电感对道路图像和电磁的检测来实现自动寻迹,能够有效解决智能小车自动寻迹以及模拟现实生活中汽车在遇到的一些特殊路况下小车自动寻迹的问题。

本文所设计和制作的智能小车在第十四届全国大学生智能汽车竞赛中得到实际应用,实现了在赛道上的自动寻迹。

参考:第十四届“恩智浦”杯全国大学生智能汽车竞赛细则[EB/OL].https:///index/;宋雪丽,王虎林等.基于单片机的寻迹机器人的系统设计,仪表技术[J].2016(4):102-105;高中正,赵丽娜等.基于摄像头的智能车控制系统设计,自动化与仪表[J].2015(6):1-5;李全福,万彦辉,郭华.模糊PID 控制算法在电动舵机控制中的应用[J].微电机,2008(12):28-30;李全利.单片机原理及应用技术[M].高等教育出版社,2010;刘乐善.微型计算机接口技术及应用[M].武汉:华中科技大学出版社,2004。

作者简介:范作鑫(1997—),山东潍坊人,大学本科,现就读于山东协和学院。

在文中介绍了可编程片上系统PSoC ,及PSoC 的开发环境、设计流程等,对PSoC 的优点与可编程门阵列FPGA 和可编程模拟器件ispPAC 进行总结对比。

1 PSoC简介可编程片上系统PSoC ,是美国Cypress 半导体公司在2000年推出的一种独特的系统架构。

它内部包含CPU 内核(M8C)、多种模拟和数字器件阵列集、微型处理器及外围单元和外围接口电路等系统,无需外接芯片及晶振,集成度非常高,实现了在线“系统单片化可编程”(张志文,胡志洁.PSoC 的多路陀螺输出脉冲计数系统设计[J].西安工业大学学报,2011年第6期),成为第一种真正具有混合信号处理能力的SOC 。

在PSoC 中,所有的模块都可以根据设计者设计需求的不同,进行动态重构,在芯片内部即可调用不同的模块来完成功能设计(胡志浩.基于PSoC 的陀螺组合测试技术的研究[D].西安工业大学,2011)。

片上系统(SOC)技术题集一、选择题1. 片上系统(SOC)中的微处理器通常不包括以下哪种类型?()A. 精简指令集(RISC)处理器B. 复杂指令集(CISC)处理器C. 超长指令字(VLIW)处理器D. 数字信号处理器(DSP)答案:D2. 以下关于片上系统(SOC)中存储器的描述,错误的是()A. 片上存储器通常包括静态随机存储器(SRAM)B. 动态随机存储器(DRAM)常用于片上系统的高速缓存C. 片上存储器还可能包含只读存储器(ROM)D. 闪存(Flash Memory)可用于片上系统的非易失性存储答案:B3. 在片上系统(SOC)的总线架构中,以下哪种总线主要用于连接高速设备?()A. 先进高性能总线(AHB)B. 先进系统总线(ASB)C. 外围设备总线(APB)D. 片上互联总线(OCB)答案:A4. 片上系统(SOC)设计中的硬件描述语言,以下不属于的是()A. Verilog HDLB. VHDLC. SystemVerilogD. C++答案:D5. 关于片上系统(SOC)中的时钟管理单元,以下说法正确的是()A. 负责产生不同频率的时钟信号B. 只用于同步数字电路C. 对系统性能没有影响D. 不需要考虑功耗问题答案:A6. 以下哪种不是片上系统(SOC)中的常见接口标准?()A. USBB. PCI ExpressC. SATAD. AGP答案:D7. 片上系统(SOC)中的电源管理模块的主要功能不包括()A. 降低系统功耗B. 提供稳定的电源电压C. 实现电源的动态调整D. 进行数据处理运算答案:D8. 在片上系统(SOC)的验证方法中,以下不属于功能验证的是()A. 模拟验证B. 形式验证C. 硬件加速验证D. 可靠性验证答案:D9. 片上系统(SOC)的可测试性设计(DFT)技术不包括()A. 边界扫描测试B. 内建自测试C. 逻辑模拟测试D. 扫描链测试答案:C10. 以下关于片上系统(SOC)中的模拟/混合信号模块的描述,不正确的是()A. 包括模数转换器(ADC)和数模转换器(DAC)B. 对噪声不敏感C. 可能需要特殊的工艺和设计技术D. 性能会受到工艺偏差的影响答案:B11. 片上系统(SOC)的封装技术中,以下不是关键考虑因素的是()A. 散热性能B. 引脚数量C. 成本D. 软件开发难度答案:D12. 关于片上系统(SOC)中的知识产权(IP)核,以下说法错误的是()A. 可以是软核、硬核或固核B. 一定是由芯片制造商自主研发C. 可以提高设计效率D. 需要进行集成和验证答案:B13. 片上系统(SOC)的低功耗设计技术不包括()A. 动态电压频率调整(DVFS)B. 门控时钟技术C. 增加晶体管尺寸D. 多阈值电压技术答案:C14. 以下不是片上系统(SOC)中的安全机制的是()A. 加密引擎B. 身份认证模块C. 图形处理单元(GPU)D. 访问控制逻辑答案:C15. 片上系统(SOC)中的通信协议不包括()A. I2CB. SPIC. HDMID. OpenGL答案:D16. 关于片上系统(SOC)中的实时操作系统(RTOS),以下描述错误的是()A. 具有高实时性B. 资源占用少C. 不支持多任务处理D. 常用于嵌入式系统答案:C17. 片上系统(SOC)的集成度不断提高,以下不是其带来的挑战的是()A. 设计复杂度增加B. 测试难度降低C. 信号完整性问题D. 功耗管理困难答案:B18. 以下哪种不是片上系统(SOC)中的嵌入式存储类型?()A. eDRAMB. MRAMC. SRAMD. HDD答案:D19. 片上系统(SOC)中的片上网络(NoC)的主要优势不包括()A. 提高通信效率B. 降低布线复杂度C. 增加系统功耗D. 支持并行通信答案:C20. 关于片上系统(SOC)中的验证平台,以下说法不正确的是()A. 可以基于软件进行模拟B. 只能使用硬件进行验证C. 可能包括仿真器和原型开发板D. 有助于提高验证效率答案:B21. 在片上系统(SOC)中,以下哪种组件通常用于实现高速数据缓存?()A. 静态随机存储器(SRAM)B. 动态随机存储器(DRAM)C. 闪存(Flash Memory)D. 只读存储器(ROM)答案:A22. 对于片上系统(SOC)的电源管理组件,以下描述不正确的是()A. 能实现不同电压域的管理B. 仅关注核心组件的供电C. 有助于降低系统功耗D. 包括降压转换器和稳压器答案:B23. 片上系统(SOC)中的模拟数字转换器(ADC)组件,其主要性能指标不包括()A. 分辨率B. 转换速度C. 存储容量D. 信噪比答案:C24. 以下哪种组件在片上系统(SOC)中负责实现硬件加密功能?()A. 加密协处理器B. 图形处理器(GPU)C. 数字信号处理器(DSP)D. 直接内存访问控制器(DMA)答案:A25. 片上系统(SOC)中的实时时钟(RTC)组件,其特点不包括()A. 低功耗运行B. 高精度计时C. 占用大量芯片面积D. 通常由电池供电答案:C26. 在片上系统(SOC)中,以下哪个组件用于实现系统的复位功能?()A. 复位控制器B. 时钟发生器C. 中断控制器D. 看门狗定时器答案:A27. 关于片上系统(SOC)中的DMA(直接内存访问)组件,以下说法正确的是()A. 只能在内存与外设之间传输数据B. 会降低系统的数据传输效率C. 无需处理器干预即可进行数据传输D. 不支持突发传输模式答案:C28. 片上系统(SOC)中的UART(通用异步收发传输器)组件,常用于()A. 高速并行数据传输B. 短距离无线通信C. 低速串行通信D. 音频信号处理答案:C29. 以下哪种组件在片上系统(SOC)中用于产生精准的时钟信号?()A. 锁相环(PLL)B. 计数器C. 移位寄存器D. 译码器答案:A30. 片上系统(SOC)中的温度传感器组件,其输出通常为()A. 模拟电压信号B. 数字脉冲信号C. 串行数据D. 并行数据答案:A31. 在片上系统(SOC)中,负责处理音频信号的组件通常是()A. 音频编解码器B. 网络控制器C. 显示控制器D. 存储控制器答案:A32. 关于片上系统(SOC)中的USB(通用串行总线)控制器组件,以下错误的是()A. 支持多种传输速率B. 只能连接主机设备C. 遵循特定的通信协议D. 具备电源管理功能答案:B33. 片上系统(SOC)中的中断控制器组件,其主要作用不包括()A. 管理外部中断请求B. 确定中断优先级C. 执行中断服务程序D. 屏蔽不需要的中断答案:C34. 以下哪种组件在片上系统(SOC)中用于实现图像显示控制?()A. 显示引擎B. 蓝牙模块C. 以太网控制器D. 红外收发器答案:A35. 片上系统(SOC)中的SPI(串行外设接口)组件,其特点包括()A. 全双工通信B. 多主设备支持C. 高速数据传输D. 复杂的协议答案:A36. 在片上系统(SOC)中,用于实现无线通信功能的组件可能是()A. Wi-Fi 模块B. 模数转换器C. 数模转换器D. 定时器答案:A37. 关于片上系统(SOC)中的GPIO(通用输入输出)组件,以下说法正确的是()A. 只能作为输入端口B. 引脚数量固定C. 可配置为输入或输出D. 不支持中断功能答案:C38. 片上系统(SOC)中的I2C(两线式串行总线)组件,其通信方式为()A. 同步串行通信B. 异步串行通信C. 并行通信D. 无线通信答案:A39. 以下哪种组件在片上系统(SOC)中用于存储启动代码?()A. 高速缓存B. 引导 ROMC. 随机存储器D. 闪存答案:B40. 片上系统(SOC)中的CAN(控制器局域网络)总线控制器组件,常用于()A. 工业自动化领域B. 消费电子领域C. 航空航天领域D. 医疗设备领域答案:A41. 片上系统(SOC)技术的发展起源于以下哪个时期?()A. 20 世纪 70 年代B. 20 世纪 80 年代C. 20 世纪 90 年代D. 21 世纪初答案:C42. 在片上系统(SOC)技术早期发展阶段,以下哪个因素对其发展起到了关键推动作用?()A. 半导体工艺的进步B. 软件编程语言的创新C. 计算机体系结构的变革D. 通信技术的发展答案:A43. 以下哪个事件标志着片上系统(SOC)技术进入快速发展期?()A. 英特尔推出第一款集成度较高的 SOC 芯片B. 台积电研发出先进的制程工艺C. 移动设备对低功耗高性能芯片的需求增加D. 量子计算技术的突破答案:C44. 片上系统(SOC)技术发展过程中,以下哪种设计方法的出现极大提高了设计效率?()A. 自顶向下设计B. 自底向上设计C. 基于模块的设计D. 软硬件协同设计答案:D45. 在片上系统(SOC)技术的发展历程中,以下哪个阶段开始注重系统的低功耗设计?()A. 初期阶段B. 中期阶段C. 近期阶段D. 一直都很注重答案:C46. 片上系统(SOC)技术发展中,以下哪种封装技术的应用促进了芯片性能的提升?()A. BGA 封装B. CSP 封装C. QFN 封装D. 3D 封装答案:D47. 以下哪个领域的需求对片上系统(SOC)技术的发展产生了重要影响?()A. 工业控制B. 医疗设备C. 消费电子D. 以上都是答案:D48. 片上系统(SOC)技术发展的哪个阶段,多核架构开始广泛应用?()A. 早期B. 中期C. 近期D. 一直都有广泛应用答案:C49. 在片上系统(SOC)技术的演进过程中,以下哪个因素促使芯片集成度不断提高?()A. 市场竞争的加剧B. 客户对功能多样化的需求C. 制造工艺的改进D. 以上都是答案:D50. 片上系统(SOC)技术发展中,以下哪种验证技术的出现提升了芯片的可靠性?()A. 形式验证B. 功能验证C. 物理验证D. 以上都是答案:D51. 以下哪个时间段,片上系统(SOC)技术在汽车电子领域得到了广泛应用?()A. 20 世纪 80 年代B. 20 世纪 90 年代C. 21 世纪初D. 近十年答案:D52. 片上系统(SOC)技术发展历程中,以下哪个因素对其成本降低起到了关键作用?()A. 大规模生产B. 设计工具的优化C. 产业链的完善D. 以上都是答案:D53. 在片上系统(SOC)技术的发展过程中,以下哪个阶段开始引入人工智能相关的功能模块?()A. 早期B. 中期C. 近期D. 尚未引入答案:C54. 片上系统(SOC)技术发展中,以下哪种通信标准的出现推动了其在物联网领域的应用?()A. ZigbeeB. Bluetooth Low EnergyC. Wi-Fi 6D. 以上都是答案:D55. 以下哪个时期,片上系统(SOC)技术在图像处理方面取得了重大突破?()A. 20 世纪 90 年代B. 21 世纪初C. 近五年D. 近十年答案:D56. 片上系统(SOC)技术发展过程中,以下哪个技术的发展使得芯片的工作频率不断提高?()A. 散热技术B. 电源管理技术C. 时钟技术D. 以上都是答案:D57. 在片上系统(SOC)技术的发展历史中,以下哪个阶段开始重视芯片的安全性设计?()A. 早期B. 中期C. 近期D. 一直都重视答案:C58. 片上系统(SOC)技术发展中,以下哪种新兴材料的应用有望进一步提升芯片性能?()A. 石墨烯B. 碳化硅C. 氮化镓D. 以上都是答案:D59. 以下哪个事件对片上系统(SOC)技术的全球化发展产生了深远影响?()A. 互联网的普及B. 5G 通信技术的商用C. 国际贸易的自由化D. 以上都是答案:D60. 片上系统(SOC)技术的发展历程中,以下哪个阶段开始强调芯片的可重构性?()A. 早期B. 中期C. 近期D. 尚未强调答案:C61. 以下哪项不是片上系统(SOC)的主要特点?()A. 高集成度B. 低功耗C. 单一功能D. 小型化答案:C62. 片上系统(SOC)技术能够实现小型化的关键因素在于()A. 采用先进的封装技术B. 减少组件数量C. 提高芯片工作频率D. 降低电源电压答案:A63. 在片上系统(SOC)中,实现低功耗的常见技术不包括()A. 动态电压缩放B. 增加晶体管数量C. 门控时钟D. 睡眠模式答案:B64. 片上系统(SOC)的高集成度带来的优势不包括()A. 降低成本B. 提高性能C. 增加设计复杂度D. 减小系统体积答案:C65. 以下关于片上系统(SOC)的实时性特点,描述正确的是()A. 所有任务都能在规定时间内完成B. 只适用于对实时性要求不高的应用C. 实时性不受系统负载影响D. 不需要考虑任务优先级答案:A66. 片上系统(SOC)的可扩展性特点体现在()A. 能方便地添加或删除功能模块B. 集成度固定不可改变C. 性能无法进一步提升D. 对新的技术不兼容答案:A67. 以下哪项不是片上系统(SOC)可靠性特点的保障措施?()A. 冗余设计B. 错误检测与纠正C. 降低工作温度D. 频繁更新软件答案:D68. 片上系统(SOC)的高性能特点主要通过以下哪种方式实现?()A. 降低时钟频率B. 减少缓存大小C. 优化系统架构D. 增加系统延迟答案:C69. 关于片上系统(SOC)的智能化特点,以下错误的是()A. 具备自适应能力B. 完全依赖人工干预C. 能进行智能决策D. 具有学习能力答案:B70. 片上系统(SOC)的并行处理特点能够()A. 提高单个任务的处理速度B. 同时处理多个任务C. 降低系统资源利用率D. 增加任务执行时间答案:B71. 以下哪项不是片上系统(SOC)灵活性特点的表现?()A. 支持多种工作模式B. 硬件架构固定不变C. 可根据需求定制功能D. 能够适应不同应用场景答案:B72. 片上系统(SOC)的保密性特点主要通过以下哪种方式实现?()A. 公开系统架构B. 加密关键数据C. 减少安全模块D. 降低系统防护级别答案:B73. 关于片上系统(SOC)的兼容性特点,以下正确的是()A. 只能与特定设备兼容B. 支持多种接口和协议C. 无法与旧版本系统交互D. 限制了系统的应用范围答案:B74. 片上系统(SOC)的高效能特点体现在()A. 能源利用率低B. 计算效率高C. 存储容量小D. 通信速度慢答案:B75. 以下哪项不是片上系统(SOC)可重构性特点的优势?()A. 快速适应新需求B. 增加硬件成本C. 延长产品生命周期D. 提高系统灵活性答案:B76. 片上系统(SOC)的集成化特点导致()A. 系统复杂度降低B. 测试难度减小C. 芯片面积增大D. 开发周期缩短答案:C77. 关于片上系统(SOC)的高速通信特点,以下错误的是()A. 数据传输速率高B. 通信延迟低C. 信道带宽有限D. 不支持多通道通信答案:D78. 片上系统(SOC)的自适应性特点能够()A. 无视环境变化B. 根据工作负载自动调整性能C. 降低系统稳定性D. 增加系统功耗答案:B79. 以下哪项不是片上系统(SOC)高可靠性特点的影响因素?()A. 优质的原材料B. 复杂的电路设计C. 严格的生产工艺D. 频繁的系统升级答案:D80. 片上系统(SOC)的多功能特点意味着()A. 功能单一且固定B. 能满足多种应用需求C. 限制了系统的扩展性D. 降低了系统的性能答案:B二、填空题1. 片上系统(SOC)技术的优势之一是能够显著提高系统的(集成度),减少芯片外的组件数量,从而降低系统成本和(尺寸)。

DSP应用系统设计流程:有以下几步:(1)确定系统性能指标;(2)核心算法模拟和验证;(3)选择DSP芯片及其他系统组件;(4)硬件设计和调试;(5)软件设计和测试;(6)系统测试、集成。

芯片选择:芯片选择要注意几个因素:(1)预算速度;(2)算法格式和数据宽度;(3)存储器;(4)功耗;(5)开发工具。

DSP芯片选择中通常有下列几条应注意的:(1)精度:表数格式(定点或浮点),通常可以用定点器件解决的问题,尽量用定点器件,因为它经济、速度快、成本低,功耗小。

但是在编程时要关注信号的动态范围,在代码中增加限制信号动态范围的定标运算。

(2)字长的选择:一般浮点DSP芯片都用32位的数据字,大多数定点DSP芯片是16位数据字。

而MOTOROLA公司定点芯片用24位数据字,以便在定点和浮点精度之间取得折中。

字长大小是影响成本的重要因素,它影响芯片的大小、引脚数以及存储器的大小,设计时在满足性能指标的条件下,尽可能选用最小的数据字。

(3)存储器安排:包括存储器的大小,片内存储器的数量,总线寻址空间等。

片内存储器的大小决定了芯片运行速度和成本,例如TI公司同一系列的DSP芯片,不同种类芯片存储器的配置等硬件资源各不相同。

(4)开发工具:在DSP系统设计中,开发工具是必不可少的,一个复杂的DSP系统,必须有功能强大的开发工具支持。

开发工具包括软件和硬件两部分。

软件开发工具主要包括:C编译器、汇编器、链接器、程序库、软件仿真器等,在确定DSP算法后,编写的程序代码通过软件仿真器进行仿真运行,来确定必要的性能指标。

硬件开发工具包括在线硬件仿真器和系统开发板。

在线硬件仿真器通常是JTAG周边扫描接口板,可以对设计的硬件进行在线调试;在硬件系统完成之前,不同功能的开发板上实时运行设计的DSP软件,可以提高开发效率。

甚至在有的数量小的产品中,直接将开发板当作最终产品。

(5)功耗与电源管理:在一些手提便携式的消费类电子产品中,供电电源的节省是很重要的问题,因而目前DSP生产厂商越来越重视这方面。

基于PLC的玻璃原片上料系统设计1. 引言1.1 研究背景玻璃原片上料系统是现代工业生产中非常重要的一部分,它负责将玻璃原片按照要求进行运输和放置,是玻璃加工生产线的重要组成部分。

传统的玻璃原片上料系统通常由人工操作或简单的机械设备完成,存在效率低、生产成本高和安全隐患大的问题。

针对玻璃原片上料系统的自动化控制需求,本研究旨在通过设计一个基于PLC的玻璃原片上料系统,实现对原片的自动运输和放置。

通过合理的系统结构设计、精准的PLC控制系统设计、合适的传感器选择与配置、流畅的运行流程设计和完善的安全防护设计,使系统能够高效、安全地运行。

通过本研究,将为玻璃加工行业提供更加智能化、高效化的生产解决方案。

1.2 研究意义玻璃原片上料系统在现代工业生产中起着至关重要的作用。

该系统能够实现对玻璃原片的准确、高效的上料,为后续加工工艺提供可靠的原材料支持。

其在玻璃加工行业中的应用,不仅提高了生产效率,降低了成本,还提高了产品质量和工作环境的安全性。

玻璃原片上料系统的设计与研究具有重要的意义。

通过优化系统设计,可以实现更加智能化、自动化的生产方式,提高生产效率,降低对人力的依赖,降低生产成本。

完善的系统设计能够提高生产线的稳定性和可靠性,减少因操作失误而造成的生产事故,保护员工的生命财产安全。

通过研究和改进玻璃原片上料系统,可以推动整个玻璃加工行业的发展,促进行业技术水平的提升,提高企业的竞争力和市场份额。

1.3 研究目的研究的目的是为了设计一种基于PLC的玻璃原片上料系统,以实现自动化生产,提高生产效率,并降低人力成本。

通过对系统结构设计、PLC控制系统设计、传感器选择与配置、运行流程设计以及安全防护设计等方面的研究与探讨,最终达到提高生产线稳定性和生产效率的目的。

通过对系统性能评价和存在问题的分析,提出改进建议,进一步完善该系统的设计与实施,以满足工业生产的需求,促进生产线的智能化、自动化发展。

在当前工业生产环境下,实现自动化生产已成为产业升级的必然趋势,本研究将为相关行业提供参考和借鉴,推动工业生产向智能化方向迈进。

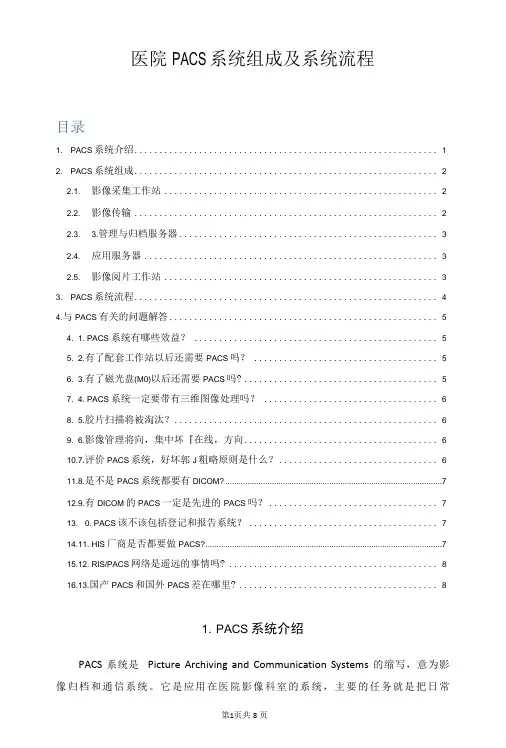

医院PACS系统组成及系统流程目录1. PACS系统介绍 (1)2. PACS系统组成 (2)2.1. 影像采集工作站 (2)2.2. 影像传输 (2)2.3. 3.管理与归档服务器 (3)2.4. 应用服务器 (3)2.5. 影像阅片工作站 (3)3. PACS系统流程 (4)4.与PACS有关的问题解答 (5)4. 1. PACS系统有哪些效益? (5)5. 2.有了配套工作站以后还需要PACS吗? (5)6. 3.有了磁光盘(M0)以后还需要PACS吗? (5)7. 4. PACS系统一定要带有三维图像处理吗? (6)8. 5.胶片扫描将被淘汰? (6)9. 6.影像管理将向,集中坏『在线,方向 (6)10. 7.评价PACS系统,好坏郭J粗略原则是什么? (6)11. 8.是不是PACS系统都要有DICOM? (7)12. 9.有DICOM的PACS一定是先进的PACS吗? (7)13. 0. PACS该不该包括登记和报告系统? (7)14. 11. HIS厂商是否都要做PACS? (7)15. 12. RIS/PACS网络是遥远的事情吗? (8)16. 13.国产PACS和国外PACS差在哪里? (8)1. PACS系统介绍PACS 系统是Picture Archiving and Communication Systems 的缩写,意为影像归档和通信系统。

它是应用在医院影像科室的系统,主要的任务就是把日常产生的各种医学影像(包括核磁,CT,超声,各种X光机,各种红外仪、显微仪等设备产生的图像)通过各种接口(模拟,DICOM,网络)以数字化的方式海量保存起来,当需要的时候在一定的授权下能够很快的调回使用,同时增加一些辅助诊断管理功能。

PACS主要分为医学图像获取、大容量数据库存储管理、图像显示和处理、数据处理库管理以及用于传输影像的局域或广域网络等五个单元。

PACS有硬件和软件两部分构成,硬件主要有接口设备、存储设备、主机、网络设备和显示系统等;软件功能包括通信、数据库管理、存储管理、任务调度、错误管理和网络监控等。

片上系统可重构性设计与实现方法片上系统可重构性设计与实现方法随着电子技术的不断发展,片上系统(SoC)已经成为现代电子产品中的重要组成部分。

片上系统的设计和实现过程中,可重构性是一个重要的考量因素。

可重构性主要体现在系统的灵活性、可扩展性和可维护性等方面。

本文将重点介绍片上系统可重构性的设计和实现方法。

1. 模块化设计模块化设计是片上系统可重构性的重要保证。

通过将系统划分为若干个功能独立的模块,可以降低系统的复杂性,提高系统的可重构性。

在模块化设计过程中,可以采用标准接口和通信协议,使得模块之间可以独立开发、独立测试和独立替换。

同时,可以采用面向对象的设计方法,通过继承和接口的方式,实现模块的可重用性,提高系统的可扩展性。

2. 分层设计分层设计是片上系统可重构性的另一种设计方法。

通过将系统划分为若干个层次,每个层次负责不同的功能,可以实现系统的模块化和可重构化。

分层设计可以将系统的功能分解为独立的、关注点单一的模块,使得系统的各个层次可以独立开发、独立测试和独立替换。

同时,通过定义合适的接口和协议,可以实现不同层次之间的通信和交互,提高系统的灵活性和可扩展性。

3. 配置管理配置管理是片上系统可重构性的关键环节。

配置管理主要包括硬件配置和软件配置两个方面。

在硬件配置方面,可以通过设计可重构的硬件模块和接口,实现硬件的动态重配置。

例如,通过配置FPGA(现场可编程门阵列)或PLD(可编程逻辑器件),可以实现硬件功能的实时切换。

在软件配置方面,可以通过配置文件或注册表等方式,实现软件功能的动态切换。

配置管理可以提高系统的灵活性和可扩展性,使系统适应不同的应用需求。

4. 软件定义软件定义是片上系统可重构性的重要手段之一。

通过采用软件定义的方式,可以实现片上系统的功能和架构的动态调整。

例如,可以采用软件定义网络(SDN)的方式,实现网络功能的动态配置和调整。

此外,通过采用面向服务的架构(SOA),可以实现系统功能的动态组合和复用。

可配置片上系统—CSoC

孟宪元[1];周荣[2]

【期刊名称】《中国集成电路》

【年(卷),期】2002(000)002

【摘要】可配置片上系统——CSoC(Configurable System-on-Chip)以其在制成的芯片上具有可重新配置的能力为基本特点,在掩膜价格越来越昂贵,标准、协议和

规范滞后于技术的高速发展和不断变革的情况下,有其重要的应用价值。

本文在介

绍各种CSoC器件的基础上,以Xilinx的FPGA平台为主,着重介绍CSoC平台技术。

【总页数】6页(P20-24,7)

【作者】孟宪元[1];周荣[2]

【作者单位】[1]清华大学电子工程系;[2]温州大学信息工程学院

【正文语种】中文

【中图分类】TN47

【相关文献】

1.基于FPGA的可重新配置片上导航计算机设计 [J], 邱吉冰;赵伟

2.一种用于FPGA的片上可配置SRAM设计 [J], 王文;曹靓;王栋

3.豪华车"爱上"高级音响系统——2007年奥迪S8配置Bang & Olufsen高级音

响系统 [J], Ben oh;Casey Thorson;阳昌盛

4.面向音频应用的可配置片上系统的设计与实现 [J], 谭洪贺;孙义和

5.直流牵引电动机试验过程测量控制系统(上)——特点及系统硬件配置 [J], 梁裕

国

因版权原因,仅展示原文概要,查看原文内容请购买。

片上系统:片上系统soc又称为集成系统,简称IS。

一般将一个完整产品的各功能集成在一个芯片上或一个芯片组上。

可编程sopc:SOPC是一种通用器件,是基于FPGA的可重构SOC。

Cyclone:特点:1.Nios嵌入式处理器支持2.中等容量的片内存储器3.从低到中等速度的I/O和存储器4.广泛的IP核支持CycloneII:~:用于那些考虑成本多与性能或其他功能的设计。

特点:1.NiosII嵌入式处理器支持2.嵌入式18x18数字信号处理(DSP)乘法器3.中等容量的片内存储器4.中等速度的I/O和存储器接口5.广泛的IP核支持QuartusII设计流程:设计输入——设计综合——布局布线——验证、仿真——嵌入式软件Cyclone架构:垂直结构的逻辑单元(IE)、嵌入式存储块和锁相环(PLL)、周围环绕着的I/O单元(IOE)支持的接口及协议:PCI:标准总线型接口、SDRAM及FCRAM接口、10/100及千兆以太网、串行总线接口、通信协议锁相环的目的:给用户提供高性能的时钟管理能力。

工作原理:压控振荡器给出一个信号,一部分作为输出另一部分通过分频与外部输入的分频信号作相位比较,如果相位差发生了变化,则相位比较器输出端电压发生变化去控制压控振荡器(VCO)直到相位差恢复,达到锁频的目的。

k=0,1,2I/O特性:支持差分I/O口(LVTTL、LVCOMS)和普通I/O口(LVDS、RSDS)普通I/O口特点:驱动能力强、电流小、抗干扰性能差差分I/O口特点:抗干扰性能强、驱动能力差,电流大、电磁干扰低、电源功耗低Cyclone与CycloneII区别:CycloneII器件提供了最多150个18X18位乘法器,可以实现通用数字信号处理(DSP)功能引脚锁定步骤:1.打开引脚锁定界面2.双击引脚锁定区Location 3.在列出的引脚号中进行选择4.所有引脚锁定好后,再次进行编译波形仿真步骤:1.新建波形仿真步骤2.设置仿真器3.插入仿真节点4.编辑输入波形文件5.运行仿真器SOPC Builde是Altera公司推出的一种可加快在PLD内实现嵌入式处理器相关设计的工具,是一个系统级开发工具~设计流程阶段:配置和生成。

可配置片上系统设计流程摘要:这章主要讲述异构可配置片上系统自顶向下设计流程。

设计流程主要关于系统级设计到后端独立设计技术问题。

重点是讲述可配置,尤其是系统级设计中现有流程不涉及到的方面。

1简介:异构片上系统与嵌入式可配置资源的结合组成一个有效解决无线通信和多媒体系统的方案。

这是因为他们提供了可配置硬件的同时还提供了类似普通指令集处理器用于一般用途的硬件架构和专用集成电路。

更重要的是有些片上系统可以通过可配置资源(资源类型和密度)完成实际用途和设计目标。

图4.1给出异构可配置片上系统的简图,片上系统通常包含指令集处理器(一般用于,DSP,ASIP专用指令处理器),专门的硬件模块,可配置硬件模块。

嵌入式可配置模块即可以在粗粒(字级粒度)或FPGA(位级粒度)。

不同的处理单元通过总线交流,然而目前的趋势是片上网络通信(处于可扩展性,灵活性,功耗问题的讨论)。

设计一个可配置硬件的片上系统不是一个繁琐的活。

为了取得一个有效实现,一个多余设计流程是需要的,这个多余的设计是为了处理在大规模商用平台上的可配置方面。

此外,一个高抽象层次设计方法需要用于帮助决定技术实施的实例,细粒和粗粒可配置硬件都需要。

这些设计方法的需求和准则在其他章节讨论。

必须指出的是设计流程和在剩下章节讲述的高级设计方法一样用于现成FPGA包括嵌入式硬连线模块(包块软件处理和专用集成电路)。

2 可配置片上系统设计要求引进可配置片上系统资源需要对传统设计流程的修改和扩展,重点在于高层次抽象,这里产生了最重要的设计决定。

在这部分,传统系统级设计流程简要讲述,可配置片上系统系统级设计流程要求将被讨论。

2.1 传统系统级设计流程随着片上系统设计的发展,系统级合作设计方法需求也正在增长。

学术和商业资源为一系列应用领域提供协同设计方法/工具,在不同的自动化程度和成熟水平上进行软硬件划分,综合,仿真和验证机制。

随着系统规范受到关注,一系列的语言(HDL,面相对象,专门语言)正在用于系统级规范。

一些设计方法正结合这些语言,是为了正确描述系统设计的硬件或软件部分。

但是目前的趋势是用一种能在高层次抽象代表系统的描述语言去规范系统设计规范。

硬件与软件划分目的是为了优化软件和硬件组件的系统功能配置。

与此对应的是,最有效的方法是提供在不同层次模型上的划分,无需重写硬件和软件规范。

这不仅减少设计迭代步骤,但是也使预定义或IP块的包含变得容易。

在协同综合中应该考虑的最重要特征是接口综合的可能性。

在不同设计方法中会谈到不同的可能进程间通信原语。

他们即可以固定在特定的设计方法,也可以和现有的原语创造出可能性选择的新原语。

联合仿真技术从基于设计特定仿真引擎的商业仿真到多种仿真引擎工具的结合。

大多数的设计依赖的仿真器基于事件驱动仿真,而其中一些可以与其他仿真器一起实现联合仿真。

协和验证主要是基于仿真的,这意味着HDL,ISS,专有的仿真在协同设计流程的不同层次的正确功能和时序在初始规范的比较。

一些方法可以通过图形工具或者专用的用户界面环境进行调试。

最具有代表性的系统级硬件或软件协同设计方法典型特征列于表4.1.先前的已经提到段落指出一个自然结果,一般传统系统级设计流程包含下面几个重要阶段:系统规范硬件或软件的划分和映射结构级设计系统级仿真(总线周期精准)硬件和软件的使用工具由技术供应商提供。

2.2 可配置片上系统系统级设计流程要求嵌入式可重构资源影响系统级设计主要流程,这部分将要讲述多余要求。

2.2.1系统规范在系统规范这一阶段,当不需要使用可配置资源时要求,限制,和规范聚集在一起,但是必须花费额外精力确认充当可配置硬件的实现应用中的部分。

采用可配置硬件在结构设计任务和划分,映射任务带来新的方面。

在结构设计任务中,一个新的结构元素将要被介绍。

在结构设计空间中,可配置硬件可以被当作一个时间片调度的特定硬件模块的应用。

在结构中纳入可配置部分意味要用一简单可配置模块取代一些硬件加速器。

在他们被有效使用之前,可配置模块的面积,速度,和功耗都应该被完全了解。

2.2.2 硬件/软件划分和映射在这一章节,一个新的层次被加到问题中讨论。

在可配置硬件中的那部分目标系统必须被确认。

这里有一些应该遵循的经验法则提供了一个简单的这个问题的解决方案。

如果应用中有几个大致相同大小硬件加速器没有同时运行或者不是在满负载运行,一个动态的可配置模块比硬连线可以是一个很可有效的解决方法。

如果应用中有一些规范的变化是可预见的,那么可实施选择就是可配置硬件。

如果新一代应用中有一些可预见的计划,那么这些改动的部分可以由可配置硬件完成。

更重要的是,对于可配置硬件的设计,不需考虑面积,速度,和功耗,好像他发生在传统硬件设计中-时间分配和调度问题必须解决。

这个解决方法类似于在单处理器上处理的软件任务的策略。

这导致了设计流程中复杂度,因为用可配置硬件技术完成功能代价包括硬件和软件设计。

现有的商业设计流程中提供两个划分和映射的途径。

(a)工具导向设计流程(b)语言导向设计流程。

工具设计流程的例子有CoWare的N2C和cadence的VCC。

这些工具支持的设计流程很好地在传统的硬件和软件方法工作。

然而,对于RTL的统一和联合定时模型的细化设计处理是指定工具的,新的可配置部分的纳入不可能脱离非传统的方法。

语言导向设计流程的例子是OCAPI-XL和SystemC。

尤其对于后者,他承诺开放源码和标准,内核语言中可加入新的方面。

然而,大多数首选的方法是要求建模和可仿真的可配置硬件的用基本语言框架编写的模型架构。

通过这种方式,能与现有工具和设计兼容的语言被保留下来。

SystemC扩展可配置硬件而OCAPI_XL相应在第五章、第六章讲到。

2.2.3 结构设计一个支持高层次抽象的系统描述设计流程必须也支持不同类型和供应商的可重构技术。

即使在抽象的最高层面上,必须要回答的问题就是:怎么实现可重构技术和使用哪项可重构技术?设计流程可以利用不同的技术回答这些问题。

首先,基于工具的分析器编译了应用功能的统一表现和产生从未并行运行的应用部分信息。

这信息可以用来确定什么功能可以被执行在可配置模块的不同的环境中。

另一种方法是为各个实现技术使用代价函数。

代价函数可以帮助在同一时间使用多个参数和优化标准时做出快速的设计决策。

另一个工具的方法是使用在仿真中收集到的编译信息去进行对应用程序划分及产生一个用在最后实现的上下文调度。

这种方法的例子是一个MorphoSys[14]工具箱的可重构结构。

最后,最容易实现在在工业领域中的选择是基于方法的仿真。

在这种方法中,划分,映射,调度由设计师手动完成, 而结果和效率是通过仿真器验证。

这种方法也是最容易纳入现有的流程, 因为与以前的方法相比它所需要的工具的支持是有限的。

这也把所有的设计决定留给设计师,更适合用在工业上的许多设计流程。

在考虑设计添加能支持可重构技术建模与仿真的一门语言、一种工具,一系列用于区分可实现技术的参数需要确定:(a)可重构模块在门级的容量,(b)需要用于保持配置上下文记忆存储、(c)重构和支持部分重构、(d)典型的时钟或传输速度,(e)功率消耗的信息。

上述参数对于任何类型的同源的可重构技建模是充足的。

用这些参数产生的仿真精度不是最佳的,但它足以让设计师知道各个不同的可重构技术如何影响整个系统的性能。

结果需要转向设计空间探索,验证设计决定,使满足整个系统的性能,有:空间利用率,用于验证模块的正确的尺寸和粒度的环境。

时间利用率,用于比较花在重构模块配置,等待激活和做计算的时间。

上下文存储器总线负载,用于分析可重构存储器存储器总线交通在系统总线性能上的作用。

面积和功耗,对比硬件和软件的执行。

上述结果应以作为附加信息以决定使用哪一个可重构技术和哪部分应用程序将被执行。

与现有的设计流程中可重构性的要求比较,可以看出现有的设计流程和工具不支持任何要求。

无论工具和语言都应该改善,还是需要伴随具体修改。

This section provides the general framework of the proposed design flowfor designing complex SoCs that contain reconfigurable parts. The flow aimsto improve the design process of a SoC in order to use the available tools inan optimal way [11].这部分提供了包含可重构部分的复杂片上系统设计的提议的设计流程。

为了用一个最佳方法使用可用的工具,这个流程旨在改善一个片上系统的设计过程。

The main idea of the design flow proposed is to identify the parts of a codesignmethodology, where the inclusion of reconfigurable technologies has the greatest effect. This is very important since there are no commercialtools or methodologies to support reconfigurable technologies, yet. Thedesign flow is divided in three parts as shown in Figure 4-2. The System-Level Design (SLD) refers to the high level part of the proposed flow, whilethe Detailed Design (DD) and Implementation Design (ID) refer to the backend part of the methodology.该设计流程的主要思想就是鉴别出一个协同设计方法论的部分,在这部分里可重构技术的包含有最大的影响。

这是非常重要的,因为目前还没有来支持可重构技术的商业工具或方法。

这个设计流程被分为三个部分,如图4-2。

系统级设计是被提议的设计流程的最高一级,详细设计和执行设计在后。

Details on the formalisms used are thoroughly covered in Chapters 5 and6, while Chapters 7, 8 and 9 provide information how the proposedframework can be applied for the design of real world case studies所使用的形式的细节全部包含在第五六章,七八九章提供了这个被提议的流程框架是怎样应用在现实世界中的。