8086存储系统扩展设计

- 格式:doc

- 大小:377.41 KB

- 文档页数:15

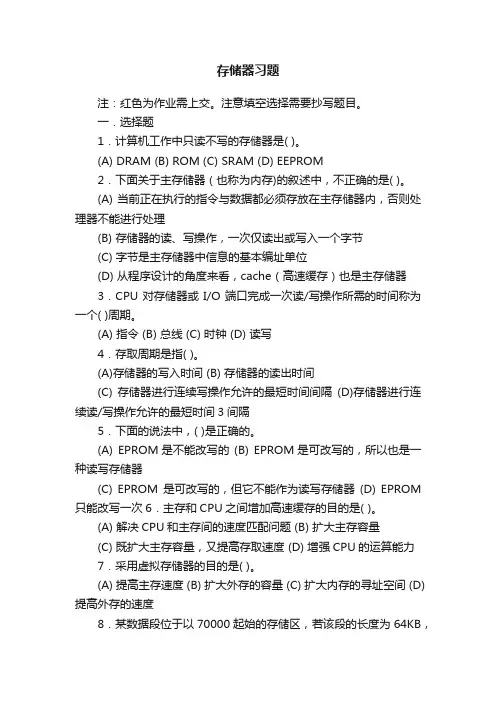

存储器习题注:红色为作业需上交。

注意填空选择需要抄写题目。

一.选择题1.计算机工作中只读不写的存储器是( )。

(A) DRAM (B) ROM (C) SRAM (D) EEPROM2.下面关于主存储器(也称为内存)的叙述中,不正确的是( )。

(A) 当前正在执行的指令与数据都必须存放在主存储器内,否则处理器不能进行处理(B) 存储器的读、写操作,一次仅读出或写入一个字节(C) 字节是主存储器中信息的基本编址单位(D) 从程序设计的角度来看,cache(高速缓存)也是主存储器3.CPU对存储器或I/O端口完成一次读/写操作所需的时间称为一个( )周期。

(A) 指令 (B) 总线 (C) 时钟 (D) 读写4.存取周期是指( )。

(A)存储器的写入时间 (B) 存储器的读出时间(C) 存储器进行连续写操作允许的最短时间间隔(D)存储器进行连续读/写操作允许的最短时间3间隔5.下面的说法中,( )是正确的。

(A) EPROM是不能改写的(B) EPROM是可改写的,所以也是一种读写存储器(C) EPROM是可改写的,但它不能作为读写存储器(D) EPROM 只能改写一次6.主存和CPU之间增加高速缓存的目的是( )。

(A) 解决CPU和主存间的速度匹配问题 (B) 扩大主存容量(C) 既扩大主存容量,又提高存取速度 (D) 增强CPU的运算能力7.采用虚拟存储器的目的是( )。

(A) 提高主存速度 (B) 扩大外存的容量 (C) 扩大内存的寻址空间 (D) 提高外存的速度8.某数据段位于以70000起始的存储区,若该段的长度为64KB,其末地址是( )。

(A) 70FFFH (B) 80000H (C) 7FFFFH (D) 8FFFFH9.微机系统中的存储器可分为四级,其中存储容量最大的是( )。

(A) 内存 (B) 内部寄存器 (C) 高速缓冲存储器 (D) 外存10.下面的说法中,( )是正确的。

![控制小直流电机转速微机原理课程设计[文档在线提供]](https://uimg.taocdn.com/2a54b9ea376baf1ffd4fad6e.webp)

课程设计任务书2009~2010学年第1学期学院: 信息科学与工程学院专业年级: 自动化075班课程: 微机原理与应用指导教师: 柴琳学号:200704134117姓名:王强一、设计题目8086微机应用DAC0832控制小直流电机转速的设计二、设计目的巩固“微机原理”课程学过的知识,加强理论与实践的联系。

通过本课程设计,使学生初步了解8086系列微机系统的硬件设备,学会8086系列编程指令的基本功能。

三、设计内容与要求1、内容采用8086CPU构建微机系统,扩展4K EPROM和2K静态RAM作为存储系统,采用最小模式,利用DAC0832,编制程序输出双极性模拟电压驱动小直流电机,使电机能以不同转速正反向运行。

2、设计要求(1)、查阅文献资料,了解DAC0832双极性电压输出控制原理,并在报告书中综述之。

(2)、设计系统的硬件连接原理图,对原理图加以说明。

(3)、画出程序框图,并说明。

(4)、编写应用程序,并注解程序。

(5)、提交课程设计说明书。

四、设计资料与参数1、电机转速由8个按钮开关以补码形式给定输入,并以发光二极管形式显示出来。

电机的转速变化范围为反向500 rpm~正向500rpm;2、DAC0832双极性电压输出控制原理,控制小直流电机以不同转速运行。

3、小直流电机额定电压为5V。

电源:5V由外部提供。

五、设计前准备DAC0832双极性电压输出控制原理自学DAC0832 是电流形式输出,当需要电压形式输出时,必须外接运算放大器。

根据输出电压的极性不同,DAC0832 又可分为单极性输出和双极性输出两种输出方式。

(1) 单极性输出。

DAC0832 的单极性输出电路如图一所示。

VREF 可以接±5V 或±10V 参考电压,当接+5V 时,输出电压范围是0V~-5V;当接-5V 时,输出电压范围是0V~+5V;当接+10V 时,输出电压范围是0V~-10V ;当接-10V 时,输出电压范围是0V~+10V。

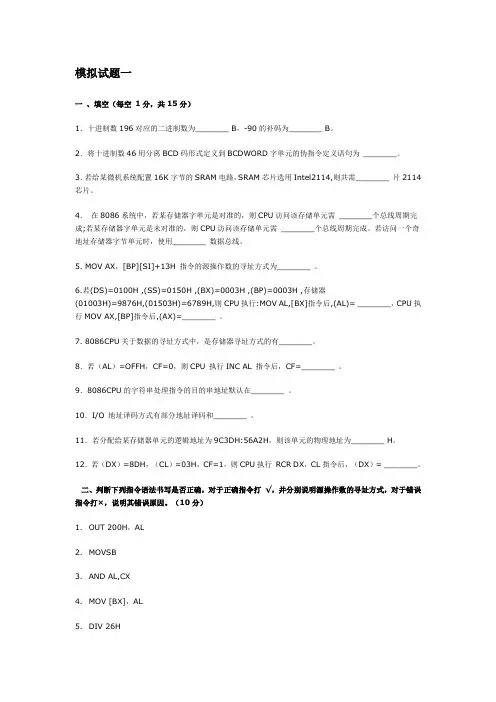

模拟试题一一、填空(每空1分,共15分)1.十进制数196对应的二进制数为_______ B,-90的补码为_______ B。

2.将十进制数46用分离BCD码形式定义到BCDWORD字单元的伪指令定义语句为_______。

3.若给某微机系统配置16K字节的SRAM电路,SRAM芯片选用Intel2114,则共需_______ 片2114芯片。

4.在8086系统中,若某存储器字单元是对准的,则CPU访问该存储单元需 _______个总线周期完成;若某存储器字单元是未对准的,则CPU访问该存储单元需_______个总线周期完成。

若访问一个奇地址存储器字节单元时,使用_______ 数据总线。

5. MOV AX,[BP][SI]+13H 指令的源操作数的寻址方式为_______ 。

6.若(DS)=0100H ,(SS)=0150H ,(BX)=0003H ,(BP)=0003H ,存储器(01003H)=9876H,(01503H)=6789H,则CPU执行:MOV AL,[BX]指令后,(AL)= _______,CPU执行MOV AX,[BP]指令后,(AX)=_______ 。

7. 8086CPU关于数据的寻址方式中,是存储器寻址方式的有_______。

8.若(AL)=OFFH,CF=0,则CPU 执行INC AL 指令后,CF=_______ 。

9.8086CPU的字符串处理指令的目的串地址默认在_______ 。

10.I/O 地址译码方式有部分地址译码和_______ 。

11.若分配给某存储器单元的逻辑地址为9C3DH:56A2H,则该单元的物理地址为_______ H。

12.若(DX)=8DH,(CL)=03H,CF=1,则CPU执行RCR DX,CL指令后,(DX)= _______。

二、判断下列指令语法书写是否正确,对于正确指令打√,并分别说明源操作数的寻址方式,对于错误指令打×,说明其错误原因。

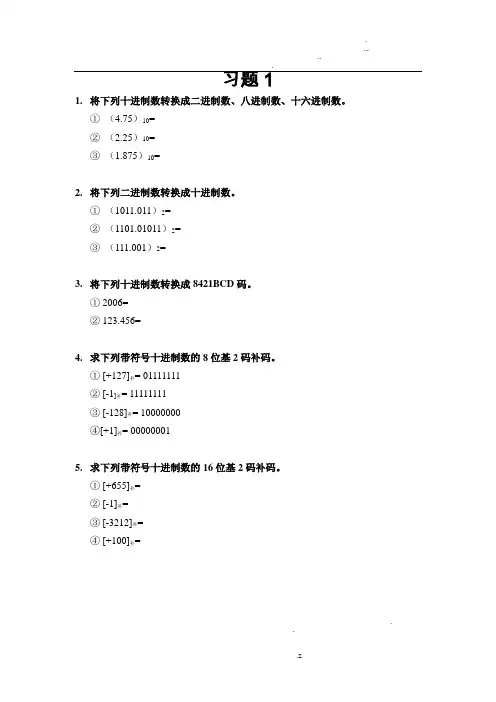

. . 习题11. 将下列十进制数转换成二进制数、八进制数、十六进制数。

① (4.75)10= ② (2.25)10= ③ (1.875)10=2. 将下列二进制数转换成十进制数。

① (1011.011)2= ② (1101.01011)2= ③ (111.001)2=3. 将下列十进制数转换成8421BCD 码。

① 2006= ② 123.456=4. 求下列带符号十进制数的8位基2码补码。

① [+127]补= 01111111 ② [-1]补= 11111111 ③ [-128]补= 10000000 ④[+1]补= 000000015. 求下列带符号十进制数的16位基2码补码。

① [+655]补= ② [-1]补= ③ [-3212]补= ④ [+100]补=习题21.8086 CPU在部结构上由哪几部分组成?各部分的功能是什么?答:8086 CPU部由两大独立功能部件构成,分别是执行部件EU和总线接口部件BIU。

执行部件负责进行所有指令的解释和执行,同时管理有关的寄存器。

总线接口部件是CPU在存储器和I/O设备之间的接口部件,负责对全部引脚的操作。

2.简述8086 CPU的寄存器组织。

答:8086 CPU部共有14个16位寄存器,按用途可分为数据寄存器,段寄存器,地址指针与变址寄存器和控制寄存器。

数据寄存器包括累加器,基址寄存器,计数器,和数据寄存器。

段寄存器用来存放各分段的逻辑段基值,并指示当前正在使用的4个逻辑段。

地址指针与变址寄存器一般用来存放主存地址的段偏移地址,用于参与地址运算。

控制寄存器包括指令寄存器和标识寄存器。

3.试述8086 CPU标志寄存器各位的含义与作用。

答:标志寄存器是16位的寄存器,但实际上8086只用到9位,其中的6位是状态标识位,3位是控制标识位。

状态标志位分别是CF,PF,AF,ZF,SF,和OF。

CF:进位标志位。

算数运算指令执行后,若运算结果的最高位产生进位或借位,则CF=1,否则CF=0。

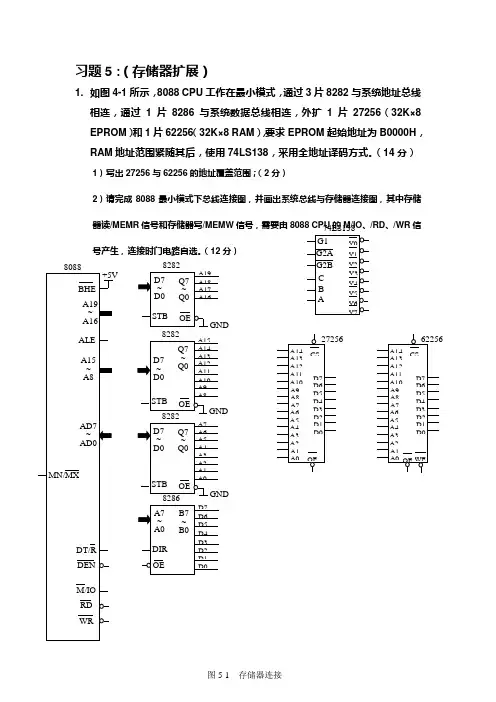

习题5:(存储器扩展)1. 如图4-1所示,8088 CPU工作在最小模式,通过3片8282与系统地址总线相连,通过1片8286与系统数据总线相连,外扩1片27256(32K×8 EPROM)和1片62256(32K×8 RAM),要求EPROM起始地址为B0000H,RAM地址范围紧随其后,使用74LS138,采用全地址译码方式。

(14分)1)写出27256与62256的地址覆盖范围;(2分)2)请完成8088最小模式下总线连接图,并画出系统总线与存储器连接图,其中存储器读/MEMR信号和存储器写/MEMW信号,需要由8088 CPU的M/IO、/RD、/WR信号产生,连接时门电路自选。

(12分)74LS138 图5-1 存储器连接2. 8086系统总线与存储器连接的总线信号为20根地址线A19~A0,16根数据线D15~D0、高八位数据允许信号BHE以及存储器读写信号MEMR和MEMW。

使用这些信号,通过控制存储器芯片的WE端,扩展2片62256(32K×8 RAM),组成64KB的RAM系统。

要求RAM的起始地址为A0000H,使用74LS138(3-8译码器)采用全译码方式产生片选信号。

(1)写出构成的RAM系统的地址范围。

(2分)(2)请在右图中画出计算机存储器系统连接图(门电路自选)。

(10分)(3)当8086处理器执行第三条指令时,需要几个总线周期?(3分)MOV AX,0A000HMOV DS,AXMOV WORD PTR [2011H],10H3. 用2片62256(32K*8 RAM)和2片27256(32K*8 EPROM)组成8086存储器系统。

要求EPROM的起始地址为10000H,RAM的起始地址为B0000H,使用全地址译码方式,试画出计算机的存储器连接图,并写出地址范围。

4. 某SRAM 存储器芯片的容量为32K ×8,表示该片有______(多选)(A) 15根地址线,8根数据线(B) 8根地址线,15根数据线(C) 32×1024个存储单元,每个单元为8位(D) 32×1024×8个存储单元,每个单元为8位 5. 8086 CPU 有20根地址线,当用该CPU 构成微机系统时,若采用全地址译码方式已经扩展00000H~0FFFFFH 地址范围的存储器,一般_____(A) 不能再扩展I/O 接口电路;(B) 还能扩展I/O 接口电路;(C) 还能扩展随机访问存储器;(D) 还能扩展只读存储器。

微原补充习题第1、2章1、有一二进制数为10110101B,表示的十六进制数为H,八进制数为Q,若表示有符号的数,则对应的十进制数为。

2、10011011B=_________H,2AB0H=_________D。

3、设机器字长为8位,已知X=-1,则[X]原= H,[X]补= H。

4、10010011B= H,2AB0H= D。

5、8086/8088CPU的编程结构中,从内部功能上由____________和____________两个独立功能部件组成。

6、8086CPU内存寻址空间最大为______字节,I/O接口寻址能力为______个8位端口。

7、8086CPU通过数据总线对________进行一次访问所需的时间为一个总线周期,一个总线周期至少包括_____个时钟周期。

当时需要插入等待周期。

8、在8086CPU引脚中,INTR端子引入的是_________中断请求信号,NMI端子引入的是__________中断请求信号。

9、8086/8088 CPU在总线周期的T1时刻,用A19/S6~A16/S3输出位地址信息的最高位,而在其他时钟周期,则输出信息。

10、8086/8088 CPU复位后,从单元开始读取指令字节,一般这个单元在区中,在其中设置一条指令,使CPU对系统进行初始化。

11、8086/8088系统中,可以有个段地址,任意相邻的两个段地址相距个存储单元。

12、8086CPU的READY引脚的作用是。

13、若(CS)=0100H、IP=0050H,则该指令的物理地址为_____________。

14、若(CS)=4200H,物理转移地址为4A230H,当CS的内容被设定为7900H时,则物理转移地址为。

15、计算机内存的堆栈是一种特殊的数据存储区,对它的存取采用的原则。

16、8086的指令队列缓冲器为个字节,8088的指令队列缓冲器为个字节。

17、8086/8088系统中CPU要求加到RESET引脚上的复位脉冲信号其宽度至少有个时钟周期,才能有效复位。

作业题目:141页第6、7题。

上交时间:2020年11月7日23:59:59学生姓名:侯永志学号:1960170124评分标准:第6题6分、第7题14分,共20分。

特别提醒:①凡发现复制粘贴他人作业者,就视为抄袭。

抄袭者和被抄袭者本次作业均按0分处理。

②用Word排版不易的内容,可以先手写,在拍照,把照片插入Word中。

③作业文件的命名格式:学号姓名,例如:1919202021张三.doc。

6.在8086系统中,若用1024×1位的RAM芯片组成16K×8位的存储器,需要多少芯片?在CPU的地址线中有多少位参与片内寻址?多少位用作芯片组选择信号?解:(1)1024*1位的RAM芯片即1K*1位的RAM芯片,组成16K×8位的存储器,需要16*8=128片芯片。

(2)分16组合成,每组8片构成1K*8位,16组共16K*8位,每组均为10个地址脚(2^10=1024),因此地址线中有10位参与片内寻址。

(3)每组都需要1个选择信号,16组需要16个选择信号,2^4=16,因此地址线中有4位作为片选信号。

7.试使用62512(64K*8位)和28C512(64K*8位),在8086系统(最小工作模式)中设计具有256KB RAM、128KB E^2PROM的存储体,RAM的地址从0000:0000H开始、E^2PROM的地址从E000:0000H开始。

解:62512是64K×8容量的芯片,组成256KB需要四片62512,起始地址为:00000H,地址范围为:00000H~3FFFFH。

28C512是64K×8容量的芯片,组成128KB需要两片28C512。

起始地址为:E0000H,地址范围为:E0000H~FFFFFH。

地址范围分配表如下:注:U1、U3、U5为偶地址存储体,U2、U4、U6为奇地址存储体。

62512(64K*8位):U1、U2、/3、/4;28C512(64K*8位):U5、U6。

单片机系统扩展在由单片机构成的实际测控系统中,最小应用系统往往不能满足要求,因此在系统设计时首先要解决系统扩展问题。

单片机的系统扩展主要有程序存储器(ROM)扩展,数据存储器(RAM)扩展以及I/O口的扩展。

MCS-51单片机有很强的扩展功能,外围扩展电路、扩展芯片和扩展方法都非常典型、规范。

本章首先通过实训初步了解扩展的方法及应用,然后详细讨论各种扩展的常见电路、芯片以及使用方法。

实训6 片外RAM对信号灯的控制及可编程I/O口的应用1.实训目的(1) 掌握扩展片外RAM的方法及使用。

(2) 熟悉8155可编程接口芯片的内部组成。

(3) 掌握8155初始化的方法及I/O口的使用。

(4) 了解8155内部定时器和RAM的编程使用。

(5) 认识片外RAM及8155相关地址的确定。

2.实训设备和器件实训设备:单片机开发系统、微机。

实训器件:实训电路板1套。

3.实训电路图下图为实训电路图,与附录1中的电路图连接完全相同。

图6.1 实训6电路图4.实训步骤与要求1)查阅附录实训电路板原理图及芯片手册,初步认识51单片机扩展片外RAM 所使用的芯片6264的管脚排列,以及与单片机的连接关系;初步分析8155与单片机的连接及三个I/O口与外部LED的关系。

2)将电路板与仿真器连接好。

3)输入参考程序1,汇编并调试运行,观察P1口发光二极管的亮灭状态。

4)输入参考程序2,汇编并调试运行,观察电路板中LED(共阴极)的显示情况。

参考程序1:对片外RAM写入数据并输出,控制P1口的亮灭状态。

ORG 0000HMOV DPTR,#1000H ;指向片外RAM的首地址MOV A,#0FEH ;设置第一个要送入的数据MOV R1,#08H ;设循环次数WRITE: MOVX @DPTR,A ;向RAM中写入数据INC DPTR ;片外RAM地址加1CLR CYRL A ;更新数据DJNZ R1,WRITE ;8次未送完,继续写入,否则顺序执行下一条指令MOV R1,#08H ;再次设置循环次数START: MOV DPTR,#1000H ;指向第一个数据单元1000HREAD: MOVX A,@DPTR ;读出数据到A累加器MOV P1,A ;送P1口点亮发光二极管LCALL DELAY ;延时一段时间INC DPTR ;更新地址DJNZ R1,READ ;连续读出8个数据,送P1口显示SJMP START ;8个数据读完,继续从第一个数据单元开始。

摘要8086 CPU是使用广泛的16位微处理器。

存储器是组成计算机系统的重要成分,按在计算机中作用分类,存储器可分为主存储器(内存)、辅助存储器(外村)、高速缓冲存储器等在8086最小模式系统和最大模式系统中,8086CPU可寻址的最大存储空间为1MB。

存储器的容量是指一块存储芯片上能存放的二进制位数,而微机的存储容量是指由多片存储芯片组成的存储容量,本实验是基于8086CPU工作在最小模式下将存储系统的扩充到最大即1MB,使用的内存芯片为621024(128K*8位)静态RAM。

关键词:8086CPU 存储系统最小模式绪论进入21世纪,信息社会发展的脚步越来也快,对人才的需求也呈现出新的变化趋势。

计算机也得到了迅猛的发展,科学家实现了计算机一代接一代的跨越性发展。

作为自动化专业本科生,微机原理与接口技术是十分重要的课程。

它是我们学习生活中不可或缺的一部分,计算机更是我们需要掌握的“第二语言”。

所以对微机原理与接口技术的学习也显得十分重要。

本设计是基于8086CPU上的内存扩充。

8086项目起始于1976年5月,是英特尔公司当时更为看重的16位的iAPX 432微处理器的备份项目。

8086一方面要与Motorola, Zilog, National Semiconductor等公司的16位、32位微处理器竞争市场份额,另一方面也是对Zilog Z80在8位微处理器市场上的成功的回击。

由于采用了与8085微处理器近似的微体系结构与物理实现工艺,8086项目进展相当快。

8086微处理器被设计为在汇编源程序上向前兼容8008, 8080, 8085等微处理器。

指令集与编程模式是基于8080微处理器,但指令集做了扩展以完全支持16位计算。

1 存储器扩展设计原理及方案选择1.1 原理介绍设计要求将8086的存储系统扩展到最大,在8086最小系统和最大系统中,8086 CPU 可寻址的最大存储空间为1MB,随机读写存储器在计算机系统中的功能主要是存储程序、变量等,在计算机运行过程中程序锁处理的变量可能要随时更新,甚至运行的程序都可能被系统动态删除以腾出空间给其他进程这类信息用ROM来存储是不行的。

通过RAM的扩展电路将8086的存储系统内存扩展到1MB,在CPU中设置两个寄存器来实现存储器和CPU之间的数据传输:存储器地址寄存器(MAR)和存储器缓冲寄存器(MBR)。

最后,编写测试程序,向扩展的存储单元写入数据并读出进行比较。

1.2 方案选择RAM的扩展分为位扩展和字扩展。

位扩展是指存储芯片的字数满足要求而位数不够需要对每个存储单元的位数进行扩展,将地址线、控制线并联,数据线对应接到8086的数据线上。

字扩展即地址扩展,用于存储芯片的位数满足要求而字数不够的情况,是对存储单元数量的扩展。

根据片选信号产生的方法不同,字扩展分为线选法、局部译码法和全译码法。

线选法是地址线与存储器的地址线连接,余下的高地址分别作为各个存储器的片选。

局部译码法是将高地址的一部分进行译码,产生哥哥存储器的片选。

全译码法是高地址全部进行译码产生各个存储器的片选。

本次设计要求将存储器扩展到1MB,选择芯片为621024(128K*8位),它的位数为8位,需要地址线17根,所以选择方案为字扩展全译码法进行实验设计。

2 存储系统扩展设计2.1 CPU系统设计2.1.1 CPU系统原理框图图1 CPU系统电路图以8086 CPU 构成的微型计算机系统,有最小模式和最大模式两种配置。

最小模式是单机系统,系统中所需要的控制信号全部由8086 CPU本身直接提供;最大系统可以构成多处理系统,系统中所需要的控制信号由总线控制器8288提供,本次设计CPU工作在最小模式下。

图1为8086 CPU构成的最小模式系统配置图,整个CPU系统以8086微处理器为核心,经过地址锁存器74LS373后形成三种线(地址总线,数据总线,控制总线)结构。

通过在总线上挂接上ROM,PAM和I/O接口,就构成微机了。

该系统中,74LS373为地址锁存器。

在8086系统中,地址线和数据线是复用的,这些复用的管脚在某时刻只能体现地址线或者数据线之一,所以在对存储器访问时,首先要将地址输出。

此时,复用的管脚是地址线,然后利用地址锁存器保存这些地址。

之后,这些管脚才是数据线,将数据读出或者写入到存储器。

在某一时刻,处理器把某个存储单元的地址发送到地址总线上,经锁存器将这些地址保存起来,只有这样,处理器才能把数据通过某些共享的管脚送到数据总线上,完成对存储器的读/写操作。

所以,在8086最小模式系统中,数据缓冲器是不必要的。

2.1.2 芯片74LS373介绍74LS373为三态输出的八D透明锁存器,373 的输出端Q0~Q7 可直接与总线相连,管脚图如图2所示。

当三态允许控制端OE 为低电平时,Q0~Q7为正常逻辑状态,可用来驱动负载或总线。

当OE 为高电平时,Q0~Q7 呈高阻态,即不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。

当锁存允许端LE 为高电平时,Q 随数据D 而变。

当LE 为低电平时,D 被锁存在已建立的数据电平。

当LE 端施密特触发器的输入滞后作用,使交流和直流噪声抗扰度被改善400mV。

它的真值表见表1。

引出端符号:D0~D7 数据输入端OE 三态允许控制端(低电平有效)LE 锁存允许端Q0~Q7 输出端图2 74LS373管脚图图3 74LS373内部结构图表1 74LS373真值表2.2 存储器扩展电路2.2.1 存储扩展电路原理图图4 存储电路电路图试验中共用了8个621024(128K*8位)芯片,每行两个为一组,其中一片存储第八位信息,接CPU数据线的D0~D7;另一片存储高八位信息,接CPU数据线的D8~D15,如图连接,十七根地址线(A1~A17)分别与八个SRAM连接,片选信号由A18,A19产生,由A0和BHE选择偶片或者奇片RAM工作,表2给出了A0和BHE逻辑组合所对应的8086CPU不同类型的数据操作。

表2 A0和BHE编码含义2.2.2 芯片621024介绍静态RAM是由MOS管组成的触发电路,每个触发器可以存放一位信息只要不掉电所储存的信息就不会丢失。

因此,SRAM工作稳定,不必外加刷新电路,使用方便。

621024RAM 有131072个存储单元,每个单元为8位字长。

621024的引脚图如图1所示:图5 621024管脚图表3 621024管脚意义2.2.4 74LS139译码电路译码电路作用是将输入的一组二进制编码转换成为一个特定的输出信号,即:输入的一组高位地址信号通过转换,产生一个有效的输出信号,用于选中某一个存储芯片,聪而确定了该存储芯片在内存中的地址范围,设计中我们选择74LS139构成译码电路74LS139 为两个2线-4 线译码器,共有54/74S139和54/74LS139 两种线路结构型式,它的引脚图如图5所示。

当选通端(G1)为低电平,可将地址端(A、B)的二进制编码在一个对应的输出端以低电平译出。

若将选通端(G1)作为数据输入端时,139 还可作数据分配器。

真值表如表4所示。

图6 74LS139引脚图图7 74LS139内部结构图2.2.5 存储器地址分配用八片SRAM621024(128K*8)组成1MB的存储器,各存储器地址的分配情况如表5所示:表5 存储器地址分配存储空间。

2.3 存储器读写程序2.3.1 存储器读写分析存储器“读”操作工作过程:(1)送地址——CPU通过地址总线将地址送入地址总线寄存器,并进行译码;(2)发出“读”命令——CPU通过控制总线将“存储器读”信号送入读/写控制电路; (3)从存储器读出数据——读/写控制电流根据“读”信号和片选信号选中存储体中的某一个存储单元,从该单元读出数据,送到数据缓存器,再经过数据总线送到CPU。

存储器“写”操作工作过程:(1)送地址——CPU通过地址总线将地址送入地址总线寄存器,并进行译码;(2)发出“写”命令——CPU通过控制总线将“写”信号送入读/写控制电路;(3)写入数据到存储器——读/写控制电流根据“写”信号和片选信号选中存储体中的某一个存储单元,将数据总线上的数据送到数据缓存器,在写入到选中的存储单元。

2.3.2 读写内存流程图图6 读写程序流程图2.3.3 存储扩展电路电路读写程序DA TA SEGMENTMESSAGE DB ‘ENTER A KEY TO SHOW THE CONTENS’,ODH,OAH,’$’DA TA ENDSSTACK SEGMENTSTA DW 50 DUP(?)TOP EQU LENGTH STASTACK ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA,ES:DATASTART:MOV AX, DA TAMOV DS, AXMOV AX, STACK ;段寄存器及指针初始化MOV SS, AXMOV SP, TOPMOV AX, 0000H ;附加段寄存器指向扩充内存区域MOV ES, AXMOV BX, 0000H ;偏移地址MOV CX, 100H ;显示的字符数MOV DL, 40H ;以‘A’字符开始显示REP1:INC DLMOV ES:[BX], DL ;字符存入扩充内存区域INC BXCMP DL, 5AH ;是否超过‘Z’字符JNZ SS1 ;超过则重置DL的值MOV DL, 40HSS1:LOOP REP1 ;循环256次MOV DX, OFFSET MESSAGEMOV AH, 09 ;显示提示信息INT 21HMOV AH, 01H ; 等待按键INT 21HMOV AX, 00000HMOV ES, AXMOV BX, 0000HMOV CX, 0100HREP2:MOV DL, ES:[BX] ;取出扩充内存的内容并显示MOV AX, 02HINT 21HINC BXLOOP REP2MOV 4COOH ;返回DOSINT 21HCODE ENDSEND START执行程序后屏幕上依次显示存入扩充内存的内容‘A~Z’。

3 小结通过这次将8086存储系统扩展到最大课程设计,对于8086CPU的内部结构、8086系统的结构配置、存储器结构、8086CPU最小和最大模式下的读写总线周期以及汇编语言程序设计、存储器原理都有了更加深刻的认识,尤其通过对程序一步一步跟踪可以更加生动、清楚的看到数据在内存中的存储情况。

虽然存储器扩展在课程进行中已经接触到,但实验一开始遇到了一些瓶颈,尤其是对于芯片的选择以及读写程序汇编等,在通过查阅资料后终于克服了这些困难,最后得以按时完成课程设计。

参考文献[1] 彭虎、周佩玲、傅忠谦,微机原理与接口技术,电子工业出版社(第二版),2010[2] 周明德,微机原理与接口技术实验指导,人民邮电出版社,2001[3] 何晓明,微机原理及应用,机械工业出版社,1999[4] 史家全,微机原理与技术,清华大学出版社,1988[5] 贾金玲,微机原理与接口技术课程设计指导,重庆大学出版社,2009附件:存储系统扩展电路图。