相位噪声(PN9000)对抖动的换算

- 格式:pdf

- 大小:294.77 KB

- 文档页数:7

相位噪声单位

相位噪声单位(Phase Noise Unit)是指在一定频率下,检测频率(F0)处相位噪声的单位。

它由检测频率(F0)处相位噪声的分贝值和检测频率(F0)处被检信号的单位组成。

它是一个通用的测量单位,可以用来衡量任何频率处的相位噪声,而无需关注测量信号的频带单位[2]。

它是一种非常常见的无线电信

号处理测量单位。

此外,相位噪声单位也可用于对高精度时钟源的噪声分析,以确定频率跳变量,最大偏移和最小偏移等[3]。

相位噪声单位通常以

dBc/Hz的形式表示,其中c表示dB下降/Hz。

因此,“-100 dBc/Hz”表示检测频率处的振幅噪声为-100 dB,

即每1 Hz的频率偏移,其振幅噪声将下降100 dB。

根据公式,dBc/Hz = 10·log(P1/P2),其中P1和P2分别表示被测信号在检测频率(F0)处和检测频率(F0)处偏移1 Hz时的相位噪声。

详解抖动与相位噪音近年来,随着图像传输的普及,在骨干网络通信量的日益增加,以及高速大容量通信已经取得了很高的进步。

在这种情况下高速通信基础设施的高频率和稳定的输出的基准信号的需求十分强烈。

抖动(Jitter)是评估输出信号波形稳定性的指标之一。

英语的“Jitter”有神经过敏、紧张不安或激动的意思。

在表现高频石英振荡器的稳定度时,指传送数字信号时波形中产生的时间偏差和晃动。

本次说明有关抖动和相位噪音的基础知识。

抖动,通信设备的重要指标我们在使用示波器观察数字信号的波形的时候,有时可以发现本应以单一周期振荡的波形亮线很宽。

这种波形拉宽就是抖动。

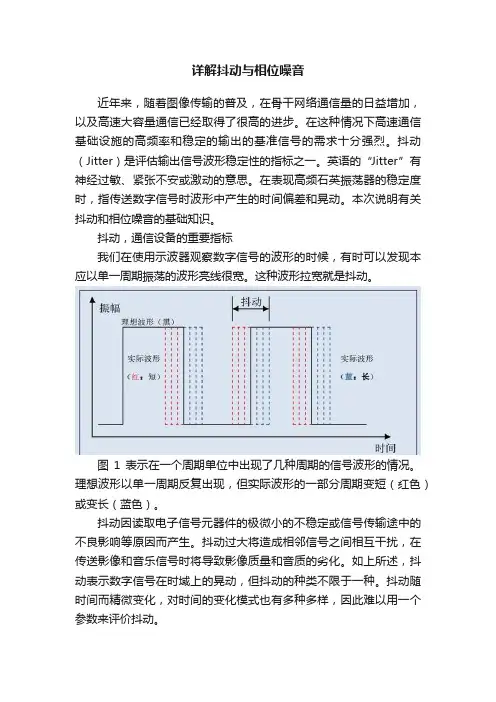

图1 表示在一个周期单位中出现了几种周期的信号波形的情况。

理想波形以单一周期反复出现,但实际波形的一部分周期变短(红色)或变长(蓝色)。

抖动因读取电子信号元器件的极微小的不稳定或信号传输途中的不良影响等原因而产生。

抖动过大将造成相邻信号之间相互干扰,在传送影像和音乐信号时将导致影像质量和音质的劣化。

如上所述,抖动表示数字信号在时域上的晃动,但抖动的种类不限于一种。

抖动随时间而精微变化,对时间的变化模式也有多种多样,因此难以用一个参数来评价抖动。

抖动的分类·周期抖动(峰峰值):表示一周期中的偏差幅度(最大和最小之差)的抖动·标准差:表示偏差程度的标准偏差·随机抖动:自然产生的无法预测的抖动·确定性抖动:因电路、电磁感应或外界环境等因素而引起的抖动·累加抖动(长期抖动):时钟各周期的连续偏差。

做一个测试测试仪:为Wavecrest公司制造的“DTS-2075”测试仪测试条件:基本无噪音的电源、探针测试点为输出端、输出电阻设定为50ohm图2的横轴表示一个周期(皮秒),这次测试用直方图表示了50000次随机抽选的周期离差。

这是SG-8002CA 125MHz PCB的数据。

最理想的是在125MHz的一周期出现一个波峰,但由于各种因素致使特性出现变化。

晶振phase noise 0.11度概述说明以及解释1. 引言1.1 概述晶振phase noise(相位噪声)是指晶体振荡器在输出信号中存在的随机相位偏移引起的频率偏差。

它是一个重要的性能指标,用于衡量晶振的稳定性和精确性。

Phase noise 的值通常以单位频率内的功率密度表示,单位为dBc/Hz(相对于载波功率)。

本文将着重介绍一种具有非常低phase noise 值的晶振,即0.11 度。

1.2 文章结构本文共分为五个主要部分。

首先,在引言部分,我们将介绍本文的概述和结构。

其次,在第二部分中,我们将详细定义和解释晶振phase noise,并探讨它对系统性能的影响,并介绍其测量方法与指标解释。

第三部分将探讨晶振phase noise 0.11度的特点和应用场景,包括其在通信领域中的应用情景以及其他领域可能需要低相位噪声晶振的应用示例。

在第四部分中,我们将研究目前晶振phase noise降低技术与方法方面的进展,包括常见的降噪技术和方法概述,新兴晶体材料在降低相位噪声方面的研究成果和前景展望,以及高性能和稳定性的PLL设计对相位噪声抑制的贡献。

最后,在结论部分,我们将对晶振phase noise 0.11度进行总结和归纳,并展望未来晶振相位噪声研究的方向。

1.3 目的本文旨在全面阐述晶振phase noise 0.11度的定义、特点与应用场景,并介绍降低phase noise 的技术与方法研究进展。

通过深入探讨晶振phase noise相关知识,读者可以更好地理解其重要性并了解到当前该领域的最新进展。

同时,文章也将为未来晶振相位噪声研究提供一些建议和展望。

2. 晶振phase noise 0.11度的定义与解释2.1 什么是晶振phase noise晶振(phase-locked loop,PLL) phase noise(相位噪声)是指当晶体振荡器工作在特定频率时,输出信号中存在的随机相位抖动。

基于相位噪声测试系统的频率稳定度测量方法叶玲玲;石明华;沈小青;楼杨【摘要】介绍了基于相位噪声测试系统的时域频率稳定度测量原理和方法,主要解决传统测量时域短期频率稳定度的高附加相位噪声影响,提高了短期频率稳定度的测量精度,实现了低附加相住噪声的频率稳定度测量.【期刊名称】《中国科技信息》【年(卷),期】2011(000)012【总页数】1页(P150)【关键词】频率稳定度;测量;相位噪声【作者】叶玲玲;石明华;沈小青;楼杨【作者单位】中国卫星海上测控部,江苏江阴,214431;中国卫星海上测控部,江苏江阴,214431;中国卫星海上测控部,江苏江阴,214431;中国卫星海上测控部,江苏江阴,214431【正文语种】中文介绍了基于相位噪声测试系统的时域频率稳定度测量原理和方法,主要解决传统测量时域短期频率稳定度的高附加相位噪声影响,提高了短期频率稳定度的测量精度,实现了低附加相位噪声的频率稳定度测量。

频率稳定度;测量;相位噪声Frequency stab;ilityMeasurem;en tPhase Noise频率稳定度按观测域的不同,分为时域频率稳定度(简称频率稳定度)和频域频率稳定度(通称相位噪声)。

随着通信、雷达等高科技的发展,频率稳定度和相位噪声往往成为系统性能的限制性因素,成为整机系统、频率源、多种两端口频率控制和变换部件设计中必须认真考虑的性能指标。

在目前的相位噪声测试装置中,法国的PN9000相位噪声测试系统[1](下称PN9000)是其中的佼佼者。

本文主要探讨该系统在时域频率稳定度测量中的应用。

PN9000是模块化的测量系统,相关测量部件都以模块形式插在主机箱内。

根据参考源、频率范围和信号分析的需要,系统可进行不同的配置。

其基本系统由机箱、五个基本模块、电脑、IEEE接口、电脑主机箱内的数字转换板和测量软件组成。

频率稳定度指由于频率源内部噪声引起的频率取样值的随机起伏,是描述平均频率随机变化的量,平均时间即采样时间。

使用实时采样示波器测量相位噪声——第一部分来源:互联网什么是相位噪声?维基百科对相位噪声的定义是:“波形相位在频域中的快速、短期、随机波动,由时域的不稳定(抖动)引起。

”噪声一词的定义说明该术语不涉及任何杂散项或确定项。

上面定义中的“短期”旨在将该定义与其他确定时钟源纯净度的方式相区别,例如每百万稳定点,即 ppm。

后者通常在较长的一段时间测得,例如数秒或数分钟。

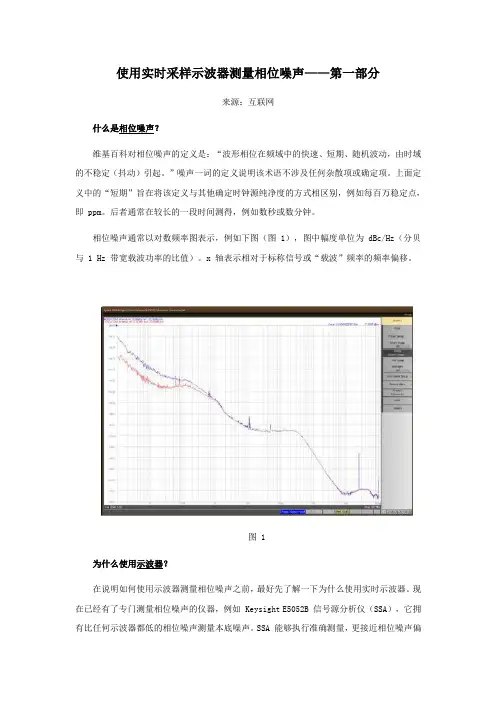

相位噪声通常以对数频率图表示,例如下图(图 1),图中幅度单位为 dBc/Hz(分贝与 1 Hz 带宽载波功率的比值)。

x 轴表示相对于标称信号或“载波”频率的频率偏移。

图 1为什么使用示波器?在说明如何使用示波器测量相位噪声之前,最好先了解一下为什么使用实时示波器。

现在已经有了专门测量相位噪声的仪器,例如 Keysight E5052B 信号源分析仪(SSA),它拥有比任何示波器都低的相位噪声测量本底噪声。

SSA 能够执行准确测量,更接近相位噪声偏移值,测量速度也比任何示波器都快。

但是该仪器也有一些测量限制,例如对最大频率偏移范围有所要求。

相位噪声分析仪的典型最大偏移为 100MHz。

对大于 100 MHz 的时钟频率,有时也要测量更高的频率偏移,但这超出了此类仪器的测量范围。

但示波器可以测量传递到数据信号上的相位噪声,而不仅仅测量时钟。

示波器使用简单如果也足以满足测量要求,当预算不足以购买专用的相位噪声测量设备时更是上佳选择。

相位提取示波器可以捕捉整个信号波形并对其进行数字化,有多种方法可以从数字化波形中提取相位噪声信息。

本文将简要介绍两种方法:1.时钟恢复2.通过矢量信号分析软件执行相位解调通过串行数据时钟恢复执行相位解调示波器分析信号是否达到设定的电压阈值,并将其与参考时钟边沿对比,从而测量串行数据或时钟信号的时序变化(抖动)。

对于相位噪声,我们希望参考时钟为理想的固定频率时钟。

大部分现代示波器都具有时钟恢复算法,可以从信号中提取时钟。

相位噪声和抖动是对同一种现象的两种不同的定量方式。

在理想情况下,一个频率固定的完美的脉冲信号(以1 MHz为例)的持续时间应该恰好是1微秒,每500ns有一个跳变沿。

但不幸的是,这种信号并不存在。

如图1所示,信号周期的长度总会有一定变化,从而导致下一个沿的到来时间不确定。

这种不确定就是相位噪声,或者说抖动。

相位噪声是频率域的概念。

相位噪声是对信号时序变化的另一种测量方式,其结果在频率域内显示。

用一个振荡器信号来解释相位噪声。

如果没有相位噪声,那么振荡器的整个功率都应集中在频率f=fo处。

但相位噪声的出现将振荡器的一部分功率扩展到相邻的频率中去,产生了边带(sideband)。

从图2中可以看出,在离中心频率一定合理距离的偏移频率处,边带功率滚降到1/fm,fm是该频率偏离中心频率的差值。

相位噪声通常定义为在某一给定偏移频率处的dBc/Hz值,其中,dBc是以dB为单位的该频率处功率与总功率的比值。

一个振荡器在某一偏移频率处的相位噪声定义为在该频率处1Hz带宽内的信号功率与信号的总功率比值。

相位噪声产生的原因信号源热噪声,内部损耗电阻热噪声,混频器件电流散弹噪声及本振相位噪声,具体是温度过热关系。

相位噪声的定义定义1:相位噪声是指单位Hz的噪声密度与信号总功率之比,表现为载波相位的随机漂移,是评价频率源(振荡器)频谱纯度的重要指标源自: 有线数字电视传输特性与故障解析《中国有线电视》2005年赵雨境,王恒江定义2:相位噪声是指光的正弦振荡不稳定,时而出现某处相位的随机跳变.相位噪声导致光源线宽变宽.光强度噪声是指因自发辐射光强的随机变化和外界温度的变化,导致发射光强的起伏源自: Fabry-Perot干涉式光纤温度传... 《传感器技术》2001年曹满婷来源文章摘要:分析了温度对相位的调制作用以及Fabry -Perot干涉结构检测相位变化的原理,提出了一种具有高灵敏度和高分辨率的相位调制型全光纤结构,并进行了系统的噪声分析。

相位噪声指标一、相位噪声的定义与意义相位噪声是指信号的相位在时间上的波动程度,它是评价信号质量的重要指标。

在通信、雷达、导航等领域,相位噪声对系统的性能有着直接的影响。

衡量相位噪声的指标有相位噪声功率谱密度(PSD)和单边相位噪声功率谱密度(Sideband noise power spectral density)等。

二、相位噪声指标的分类与计算方法1.相位噪声功率谱密度(PSD):表示单位频率范围内,相位噪声能量的概率密度。

通常采用维纳过程模型来计算PSD。

2.单边相位噪声功率谱密度(Sideband noise power spectral density):表示在特定频率范围内,相位噪声引起的双边频谱的幅度平方和。

3.相位噪声参数:包括相位噪声功率谱密度和相位噪声指数等,这些参数根据不同的应用场景和设备要求进行选择和计算。

三、相位噪声指标在实际应用中的重要性1.在通信系统中,相位噪声会影响信号的解调性能,降低通信质量。

2.在雷达系统中,相位噪声会导致距离模糊和目标定位精度降低。

3.在导航系统中,相位噪声会增大定位误差,影响导航精度。

四、降低相位噪声的方法和技术1.采用低噪声器件:选择噪声性能优良的器件,如光纤、低噪声放大器等,降低系统的相位噪声。

2.优化系统设计:合理安排系统的结构和布局,减小噪声的传递和耦合。

3.数字信号处理:对信号进行数字滤波和降噪处理,提高信号质量。

4.锁定放大技术:通过锁定放大器对相位噪声进行抑制,提高信号的稳定性。

五、总结与展望相位噪声指标在通信、雷达、导航等领域具有重要作用。

随着技术的发展,对相位噪声指标的要求越来越高。

未来,降低相位噪声的技术和研究将不断涌现,为提升系统性能和可靠性提供支持。

相位强度转换噪声相位强度转换噪声(Phase-to-Intensity Conversion Noise,简称PIC噪声)是光学通信和光电子学领域中一个关键的问题。

它起源于光信号的相位波动在传输或检测过程中被转换为强度噪声,从而影响系统的性能。

本文将深入探讨PIC噪声的产生机理、影响因素以及降低这种噪声的策略。

一、PIC噪声的产生机理在光通信系统中,光信号的相位携带了大量的信息。

然而,当光信号通过某些光学元件(如光纤、调制器等)或在光电探测器上被检测时,相位波动可能会被转换为强度波动,即PIC噪声。

这种转换可能是由于光学元件的非线性效应、色散、偏振模色散(PMD)或是探测器的响应特性不均匀等因素引起的。

特别是在高速光通信系统中,由于信号的带宽很宽,相位波动更加显著,因此PIC 噪声的影响也更为严重。

这种噪声会导致信号的信噪比(SNR)下降,进而限制系统的传输距离和容量。

二、影响PIC噪声的因素1. 光学元件的特性:不同的光学元件对相位到强度的转换有不同的影响。

例如,光纤的色散和非线性效应会导致光信号的相位发生变化,进而产生PIC噪声。

同样,调制器的不完美调制也会引入额外的相位噪声。

2. 探测器的响应特性:光电探测器在将光信号转换为电信号时,其响应特性对PIC噪声的产生也有重要影响。

探测器的响应速度、量子效率以及暗电流等参数都会影响最终的噪声水平。

3. 信号的调制格式:不同的调制格式对相位噪声的容忍度不同。

例如,高阶调制格式(如QAM)由于其在相位空间中更接近彼此,因此对相位噪声更为敏感,也更容易受到PIC噪声的影响。

三、降低PIC噪声的策略1. 优化光学元件设计:通过改进光学元件的设计,可以减少相位到强度的转换。

例如,采用色散补偿光纤(DCF)可以补偿光纤中的色散效应,从而降低PIC噪声。

此外,优化调制器的设计也可以减少不完美的调制引入的相位噪声。

2. 选择合适的探测器:选择具有高响应速度、高量子效率和低暗电流的光电探测器可以减少PIC噪声的产生。

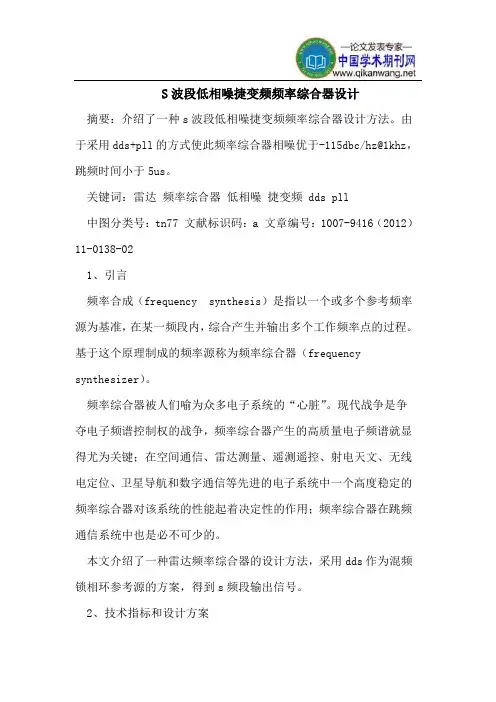

S波段低相噪捷变频频率综合器设计摘要:介绍了一种s波段低相噪捷变频频率综合器设计方法。

由于采用dds+pll的方式使此频率综合器相噪优于-115dbc/hz@1khz,跳频时间小于5us。

关键词:雷达频率综合器低相噪捷变频 dds pll中图分类号:tn77 文献标识码:a 文章编号:1007-9416(2012)11-0138-021、引言频率合成(frequency synthesis)是指以一个或多个参考频率源为基准,在某一频段内,综合产生并输出多个工作频率点的过程。

基于这个原理制成的频率源称为频率综合器(frequency synthesizer)。

频率综合器被人们喻为众多电子系统的“心脏”。

现代战争是争夺电子频谱控制权的战争,频率综合器产生的高质量电子频谱就显得尤为关键;在空间通信、雷达测量、遥测遥控、射电天文、无线电定位、卫星导航和数字通信等先进的电子系统中一个高度稳定的频率综合器对该系统的性能起着决定性的作用;频率综合器在跳频通信系统中也是必不可少的。

本文介绍了一种雷达频率综合器的设计方法,采用dds作为混频锁相环参考源的方案,得到s频段输出信号。

2、技术指标和设计方案频率综合器主要技术指标见表1。

设计方案主要由参考源模块、梳频模块和移频模块3部分构成,如图1所示。

2.1 参考源模块本方案中采用dds产生移频模块的参考信号,通过改变dds的输出频率即改变移频环的参考信号频率来实现最终输出信号的频率步进。

dds输出(140~217.5)mhz作为移频环的参考信号,其频率步进2.5mhz。

移频环鉴相频率(140~217.5)mhz,采用高鉴相频率不仅有利于通过pll的低通特性滤除鉴相频率杂散,而且可以将环路带宽设计更宽以实现捷变频指标。

此设计若采用单环锁相实现,频率步进设计为2.5mhz,即鉴相频率采用2.5mhz,通过与前方案中最小鉴相频率140mhz相比较,可以明显看出,不仅由鉴相频率泄露带来的杂散难以抑制,而且无法满足6us跳频时间的要求。

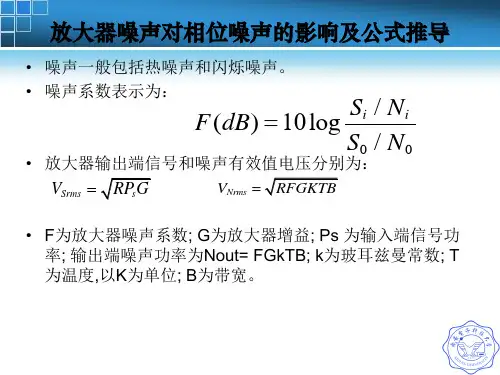

相位噪声和抖动1. 射频信号时间频率稳定性1.1. 什么是相位噪声(Phase noise)相位噪声是指系统(如各种射频器件)在各种噪声的作用下引起的系统输出信号相位的随机变化。

1.2. 相位噪声的本质相位噪声体现信号相位的随机变化,量值是在某频率处dBc/Hz。

dBc体现比值概念,那么这是功率比值还是相位比值?答案是功率比值,对应相位随机变化的分布幅度和概率。

1.3. 什么是抖动(Jitter)相位噪声和抖动是对同一种现象的两种不同的定量方式。

相噪是在频域定标,抖动是在频域定标,两者可以相互转换:相位噪声L对应的线性功率P(f)=10^(L/10);频段(Δf=f2-f1)内,功率密度积分,对应相位变化ΔΦ=sqrt(2*∫ P(f)df),即剩余调相;对于频率为fc的信号,其时域抖动jitter = ΔΦ/(2*π*fc)。

由相噪结果计算得来的抖动(均方根值)数值单位是s,对应相应相噪分析的频段(频偏),多个频段的抖动数值可以通过均方根值合成一个数值,对应整个频段的抖动值。

2. 相噪测试方法2.1. 频谱仪频谱分析法理解相位噪声(功率比值):测试频率f0的信号功率P0(dBm),在f0+Δf频率偏移处读取的功率密度值P1(dBm/Hz),对应相位噪声L(dBc/Hz)。

2.2. 信号源分析仪– PLLPLL鉴相法理解相位噪声(相位变化的功率谱比值):信号Signal = Cos(wt+Φ(t))信号的初相Φ(t)在时域的抖动,数字化转换为频域功率谱(FFT),对应相位噪声L(dBc/Hz)。

处于灵敏度的考虑,信号源分析仪通常有互相关的功能。

简而言之,信号与分析仪内置两个独立的PLL系统,被测信号进入两个PLL 后,产生两个带噪声的直流信号;通过相关运算,将PLL内置参考源的噪声归零,仅剩被测信号的相噪。

2.3. 信号源分析仪–数字解调将被测信号Signal = Cos(wt+Φ(t))量化为I/Q数据后,直接解调分析Φ(t)。

通信设备相位抖动测量装置研究张娟;钱健;卞剑;陈松涛【摘要】相位抖动是指输出信号频率的随机相位偏离其基准相位的瞬时变化量,本文重点研究通信系统包括军用通信系统的发射机、接收机等的射频频率相位抖动的测量问题.采用单时差法、二次取样方差及无间隙采样技术建立测量装置,实现对通信设备相位抖动指标的自动测量.【期刊名称】《计测技术》【年(卷),期】2012(032)006【总页数】5页(P21-24,36)【关键词】相位抖动;单时差法;无间隙技术【作者】张娟;钱健;卞剑;陈松涛【作者单位】南京熊猫汉达科技有限公司计量中心,江苏南京210002;南京熊猫汉达科技有限公司计量中心,江苏南京210002;南京熊猫汉达科技有限公司计量中心,江苏南京210002;南京熊猫汉达科技有限公司计量中心,江苏南京210002【正文语种】中文【中图分类】TN830.30 引言抖动是表征时域特性的一个基本量,其值反映了信号在时域的变化量,它从本质上描述了信号实际周期距离其理想值的偏离。

相位抖动是时域频率稳定度的一种表征,在不同的领域有不同的定义和测量方法。

本文主要研究通信系统包括军用通信系统中的发射机、接收机等的射频频率的相位抖动。

目前,我国海陆空三军从短波至微波通信系统中都有本振源,这些本振源都采用了频率合成技术,而相位抖动这项技术指标直接影响通信系统的性能,特别是在高速数据通信系统中,相位抖动直接影响数据的误码率等指标。

因此,在我国很多通信系统中,规定在10 ms时间内,射频频率相位抖动不大于5°。

在我国国标GB/T6934-1995《短波单边带接收机的电性能测量方法》和国军标GJB407B-204《军用短波单边通信设备通用规范》中,都规定需要测量相位抖动这项指标。

国际上尚未搜索到同类产品的信息,国内也未见有关此项测量技术的报道,为了满足军用通信设备的研制和生产需求,建立相位抖动测试装置很有必要。

1 抖动的定义信号 (频率)源的相位抖动可以采用时域或频域的测量方法。

•32计算机测量与控制.2017. 25 (5)Computer Measurement & Control测试与故障诊断文章编号:1671 - 4598(2017)05 - 0032 -03 DOI:10. 16526/j. cnkl 11-4762/tp. 2017. 05. 010 中图分类号:TN98 文献标识码:A PN9000相位噪声测试系统扩频方法研究叶冷冷,孙朝斌,沈小青,褛杨,郭海生(中国卫星海上测控部,江苏江阴214431)摘要:在航天测控领域,相位噪声指标已成为系统性能的限制性因素,精确测量载波的相位噪声显得尤为重要;PN9000相位噪声 测试系统可直接应用于相位噪声测试,具备测试灵敏度髙、系统稳定、测试快速等优点;随着航天测控领域所用频率的不断提髙,针对 PN9000相位噪声测试系统基本配置的频率范围已无法满足测试需求的问题,为满足PN9000相位噪声测试系统扩频需求,文中提出基于相位检波器法(基本型)和基于中频相位检波器法两种扩频方法,并对两种方法进行原理分析和实验验证;根据实验结果,两种方法均能有效实现扩频功能,但在系统本底相位噪声及经费使用方面各有不同特点;文中提供的方法及实验数据,对PN9000相位噪声测试系 统扩频升级及配件选购等具有很好的借鉴作用。

关键词:相位检波器;相位噪声;下变频Research on Expanding Frequency Range Method of PN9000 PhaseNoise Measurement SystemY e L in g lin g,S u n C h a o b in,S h e n X ia o q in g,Lou Y a n g,Guo Haisheng(China Satellite Maritime Tracking and Control Department,Jiangyin214431,China) Abstract:The system performance is often limited by phase noise in the field of space measurement and control. Accurate measurement of carrier phase noise is particularly important. PN9000 phase noise measurement system can be directly applied to accurately measure phase noise, it has the advantages of high sensitivity,maintenance, fast test and so on. As the frequency of space measurement and control field s increased,the frequency measurement range of PN9000 b asic configuration can not meet the test requirement. To expanding hrequency range o f PN9000 phase noise measurement system,the two expanding frequency range methods were proposed that respectively based on phase detector Cfundamental form) and IF phase detector,and the theoretical results with experimental pared. According to the experimental results,the intention of expanding frequency range can be realized by using any one of the two methods ,but the dif.^erent characteristics in system floor phase noise and costs are showed. The two methods can be referred .^or expanding requency range of PN9000 phase noise measurement system and choosing suitable accessories.Keywords:phase detector;phase noise;down—conversion0引言在航天测控通信、高速数据传输等系统中,载波相位噪声 对于雷达作用范围、图像信号的质量、卫星定位的精度、数据 传输的误码率[1]以及相邻信道之间信号的干扰等都有着直接影 响,精确测量载波的相位噪声就显得尤为重要。

什么是抖动和相位噪声抖动(Jitter)反映的是数字信号偏离其理想位置的时间偏差。

高频数字信号的bit周期都非常短,—般在几百ps甚至几十ps, 很小的抖动都会造成信号采样位置电平的变化,所以高频数字信号对于抖动都有严格的要求。

,,啦打l它忱怡O l oc kJitter实际信号的很复杂,可能既有随机抖动成分(RJ), 也有不同频率的确定性抖动成分(DJ)。

确定性抖动可能由千码间干扰或一些周期性干扰引起,而随机抖动很大一部分来源千信号上的噪声。

下圈反映的是一个带噪声的数字信号及其判决阔值。

一般我们把数字信号超过阔值的状态判决为'1", 把低千阔值的状态判决为"O"I由千信号的上升沿不是无限陡的,所以垂直的幅度噪声就会造成信号过闽值点时刻的左右变化,这就是由于噪声造成信号抖动的原因。

j i tl e r caused by voltage no i 钮j itte ,r caused by vo l tage noisePhase noise te吐re多ult o f $ig1n al Source A nalyz e:r对于很多晶振产生的时钟来说,其抖动中的主要成分是随机抖动。

如果我们把相位噪声测试结果里不同频率成分的相位噪声能量进行积分的话,我们就能够得到随机抖动。

通过信号源分析仪对相位噪声测量然后对—定带宽内的能量进行积分,我们就可以得到精确的随机抖动测量结果。

信号源分析仪能测量到的最小抖动可以到fs级。

日O中央广播电视祫台发布2021II品牌强国丁程”融媒体传播方案广播百科001—100期广播百科101—200期广电术语词汇(一)广电术语词旷(二)。

相位噪声和抖动地概念及其估算方法时钟频率地不断提高使相位噪声和抖动在系统时序上占据日益重要地位置.本文介其概念及其对系统性能地影响,并在电路板级、芯片级和单元模块级分别提供了减小相位噪声和抖动地有效方法.随着通信系统中地时钟速度迈入GHz级,相位噪声和抖动这两个在模拟设计中十分关键地因素,也开始在数字芯片和电路板地性能中占据日益重要地位置.在高速系统中,时钟或振荡器波形地时序误差会限制一个数字I/O接口地最大速率,不仅如此,它还会增大通信链路地误码率,甚至限制A/D转换器地动态范围.在此趋势下,高速数字设备地设计师们也开始更多地关注时序因素.本文向数字设计师们介绍了相位噪声和抖动地基本概念,分析了它们对系统性能地影响,并给出了能够将相位抖动和噪声降至最低地常用电路技术.什么是相位噪声和抖动?相位噪声和抖动是对同一种现象地两种不同地定量方式.在理想情况下,一个频率固定地完美地脉冲信号(以1 MHz为例>地持续时间应该恰好是1微秒,每500ns有一个跳变沿.但不幸地是,这种信号并不存在.如图1所示,信号周期地长度总会有一定变化,从而导致下一个沿地到来时间不确定.这种不确定就是相位噪声,或者说抖动.抖动是一个时域概念抖动是对信号时域变化地测量结果,它从本质上描述了信号周期距离其理想值偏离了多少.通常,10 MHz以下信号地周期变动并不归入抖动一类,而是归入偏移或者漂移.抖动有两种主要类型:确定性抖动和随机性抖动.确定性抖动是由可识别地干扰信号造成地,这种抖动通常幅度有限,具备特定地<而非随机地)产生原因,而且不能进行统计分析.造成确定性抖动地来源主要有4种:1. 相邻信号走线之间地串扰:当一根导线地自感增大后,会将其相邻信号线周围地感应磁场转化为感应电流,而感应电流会使电压增大或减小,从而造成抖动.2. 敏感信号通路上地EMI辐射:电源、AC电源线和RF信号源都属于EMI源.与串扰类似,当附近存在EMI辐射时,时序信号通路上感应到地噪声电流会调制时序信号地电压值.3. 多层基底中电源层地噪声:这种噪声可能改变逻辑门地阈值电压,或者改变阈值电压地参考地电平,从而改变开关门电路所需地电压值.4. 多个门电路同时转换为同一种逻辑状态:这种情况可能导致电源层和地层上感应到尖峰电流,从而可能使阈值电压发生变化.随机抖动是指由较难预测地因素导致地时序变化.例如,能够影响半导体晶体材料迁移率地温度因素,就可能造成载子流地随机变化.另外,半导体加工工艺地变化,例如掺杂密度不均,也可能造成抖动.随机抖动最基本地一个特性就是随机性,因此我们可以用高斯统计分布来描述其特性.例如,对一个只包含随机抖动因素地时钟振荡器地振荡周期进行100次连续测量,测量结果会呈高斯分布<或称正态分布).在其均值加减1个标准差地范围内包含了所有周期测量数据地68.26%,在其均值+/- 2倍标准差地范围内包含所有测量数据地95.4 %,+/- 3倍标准差范围内包含99.73%地测量数据,+/- 4倍标准差范围内包含99.99366%地测量数据.从这种正态分布中,我们可以得到两种常见地抖动定义:1. 峰峰值抖动,即正态曲线上最小测量值到最大测量值之间地差距.在大多数电路中,该值会随测量样本数地增多而变大,理论上可达无穷大.因此,这种测量意义不大.2. RMS(均方根>抖动,即正态分布一阶标准偏差地值.该值随样本数地增加变化不大,因而这种测量较有意义.但这种测量只在纯高斯分布中才有效,如果分布中存在任何确定性抖动,那么利用整个抖动直方图上地一阶方差来估计抖动出现地可能性就是错误地.3. 多个随机抖动源可以用RMS方式相加.但要得到总地抖动,需要利用峰峰值,以便将随机抖动与确定性抖动相加.相位噪声是频率域地概念相位噪声是对信号时序变化地另一种测量方式,其结果在频率域内显示.图2用一个振荡器信号来解释相位噪声.如果没有相位噪声,那么振荡器地整个功率都应集中在频率f=fo处.但相位噪声地出现将振荡器地一部分功率扩展到相邻地频率中去,产生了边带(sideband>.从图2中可以看出,在离中心频率一定合理距离地偏移频率处,边带功率滚降到1/fm,fm是该频率偏离中心频率地差值.相位噪声通常定义为在某一给定偏移频率处地dBc/Hz值,其中,dBc是以dB为单位地该频率处功率与总功率地比值.一个振荡器在某一偏移频率处地相位噪声定义为在该频率处1Hz带宽内地信号功率与信号地总功率比值.在图2中,相位噪声是用偏移频率fm处1Hz带宽内地矩形地面积与整个功率谱曲线下包含地面积之比表示地,约等于中心频率处曲线地高度与fm处曲线地高度之差.该曲线显示地是一个带噪声相角地振荡器地功率谱,这些噪声相角自身地波动见图3.图2所示为振荡器地功率谱,而图3所示为噪声相角地谱,也叫相位波动地谱密度.对于距离中心频率足够远地偏移频率,从图2所示功率谱中测得地以dBc/Hz 为单位地相位噪声等于图3中所示地该频率处相位波动谱密度地值.图3中地密度谱是以对数坐标表示地,其中,相位噪声边带以1/fm2或20 dB/十倍频程地速度下降.实际上,在噪声边带中地某些地方,随着相关噪声过程地不同,相位噪声可能会以1/f3、 1/f2甚至 1/f0地速度下降.下降速度为1/f2地区域被称作“白色频率”变化区,这个区域中地相位变化是由振荡器周期中白色地或非相关地波动引起地.振荡器在该区域中地行为由振荡器电路中元件地热噪声决定.当偏移频率足够低时,元件地闪烁噪声通常也会起作用,导致该区域地谱密度以1/f3地速度下降.此外,还有一点值得注意,当图3中偏移频率趋于0时,边带噪声会趋于无穷大.这恰好与自由运行振荡器中理应出现地时序抖动行为相符.如何将相位噪声转换为抖动如前所述,抖动和相位噪声所描述地是同一现象地特征,因此,如果能从相位噪声地测量结果中导出抖动地值将是有意义地.以下介绍推导方法:每个振荡器都有其相位噪声图,图4给出一个例子.该图中绘出地是从12 kHz到 10 MHz这个频带范围内,某振荡器地相位噪声情况.图中,L(f>以功率谱密度函数地形式给出了边带噪声地分布,单位为dBc.中心频率地功率并不重要,因为抖动只反映了相位噪声(即调制>与“纯”中心频率处地相对功率值.边带地总噪声功率可以由L(f>函数在整个感兴趣频段内(在本例中,即12 KHz到 10 MHz频段内>积分得到.计算得到地是相位调制噪声在该频段内地功率,而相位调制正是造成抖动地原因.由此,我们还能用如下地定积分推出RMS抖动地值.下式可求得该噪声功率造成地RMS抖动:抖动值还可以用其他单位表示,例如单位时间<UI)或时间.将上式除以以弧度为单位地中心频率就可以将抖动单位转换为时间,见下式:利用图4所绘地噪声功率值,我们可以计算一个312.5MHz振荡器地RMS抖动.将相位噪声曲线在12 kHz到20 MHz范围内积分,得到-63 dBc:因此可以得到如下式所示地RMS相位抖动值,单位为弧度:还可以将该抖动值单位转换为皮秒:而同样地312.5 MHz振荡器地典性总抖动值在5ps RMS左右.最终,我们计算得到地0.72 ps RMS地抖动值只在最大抖动中占很小地比例.怎样将电路板上地相位噪声和抖动降至最低电路板设计师可以通过两种关键技术降低板上地确定性信号抖动:1.完全以差分形式收发信号:诸如LVDS或PECL等一些以差分方式收发信号地惯例,都能极大降低确定性抖动地影响,而且这种差分通路还能消减信号通路上地所有干扰和串扰.由于这种信号收发系统对共模噪声本来就有高度抑制能力,因此差分形式本来就有消除抖动地趋向.2.仔细布线:只要可能,就要避免出现寄生信号,因为这种信号可能会通过串扰或干扰对信号通路产生影响.走线应该越短越好,而且不应与承载高速开关数字信号地走线交叉.如果采用了差分信号收发系统,那么两条差分信号线就应尽可能靠近,这样才能更好地利用其固有地共模噪声抑制特性.怎样将芯片中地相位噪声和抖动降至最低在芯片级上,可以使用以下设计技术将抖动降至最低:1.差分信号收发:即使进入芯片地是单端信号,最好也在芯片中将其转换为差分信号,原因同上节所述.2.仔细布设信号通路:在对敏感时序信号通路进行布线时必须小心,而且走线越短越好,还应避免与任何数字信号线交叉.只要条件允许,最好将这些信号通路均在屏幕上显示出来.例如,一条在第二层金属平面上地信号通路可以夹在第一层和第三层金属平面之间,而第一层和第三层金属平面均连接到一个干净地地上.3.恰当选择缓冲器大小:如果用缓冲器在模块间分配信号,那么必须注意驱动强度地选择.驱动不足会造成信号上升/下降沿过缓,给噪声以可乘之机.4.保持基底和地地干净:基底噪声和地噪声是造成确定性抖动地主要原因.在一个有多路同步数字输出地芯片内,地线反弹噪声(ground bounce>可能会达到几百毫伏,甚至1伏.为了降低地线反弹噪声,芯片上应该有尽可能多地电源对,而且这些电源对应尽可能靠近数字输出.5.使用一个单独地干净地层:在电路设计中,最好将数字电路地电源与敏感地模拟电路(如振荡器或PLL>地电源分开.数字电路,尤其是高驱动输出数字电路地电源很可能会引入噪声,而且这种电源一旦用于时序电路,那么也会成为增大抖动地一个主要原因.因此,对PLL这样地电路甚至可以利用电源滤波来进一步减小电源噪声地影响.怎样将单元模块中地相位噪声和抖动降至最低在设计单元模块时可以采用以下技术来减小抖动:1.利用尾电流--时序电路中使用地电流与相位噪声之间有一个直接地关系.例如,增大一对差分对地尾电流必定导致抖动性能得到改善.于是我们就必须在降低抖动和缩减功耗之间寻求一个平衡,在适当之处选择性地增大最敏感电路地电流.2.仔细布局--在对那些可能引起相位噪声地单元进行布局时必须小心,匹配元件(例如连接到一对差分对地输入>应方向相同,而且尽可能对称布局.该方法会使应匹配地元件具有同样地处理斜率(process gradients>,因而有助于改善元件之间地匹配程度.电阻应尽可能宽,以减小Delta W效应.如果可能,应在整个电路中使用同一种类,甚至尺寸和阻值都相同地电阻来帮助跟踪工艺和温度地所有变化.总而言之,要想尽可能减小抖动,就必须在所有设计层上都小心谨慎.高速数字设计师在设计过程地每一步都应考虑相位噪声和抖动地影响.作者:Neil Roberts高级模拟设计师Zarlink半导体公司时钟抖动(CLK>和相位噪声之间地转换摘要:这是一篇关于时钟(CLK>信号质量地应用笔记,介绍如何测量抖动和相位噪声,包括周期抖动、逐周期抖动和累加抖动.本文还描述了周期抖动和相位噪声谱之间地关系,并介绍如何将相位噪声谱转换成周期抖动.几乎所有集成电路和电气系统都需要时钟(CLK>.在当今世界中,人们以更快地速度处理和传送数字信息,而模拟信号和数字信号之间地转换速率也越来越快,分辨率越来越高.这些都要求工程师更多地关注时钟信号地质量.时钟信号地质量通常用抖动和相位噪声来描述.抖动包括周期抖动,逐周期抖动和累计抖动,最常用地是周期抖动.时钟地相位噪声用来说明时钟信号地频谱特性.本文首先简单介绍用来测量时钟抖动和相位噪声地装置.然后介绍周期抖动和相位噪声之间地关系,最后介绍将相位噪声谱转换成周期抖动地简单公式.周期抖动和相位噪声:定义和测量周期抖动周期抖动(J PER>是实测周期和理想周期之间地时间差.由于具有随机分布地特点,可以用峰-峰值或均方根值(RMS>描述.我们首先定义门限为V TH地时钟上升沿位于时域地T PER(n>,其中n是一个时域系数,如图1所示.我们将J PER表示为手册:其中T O是理想时钟周期.由于时钟频率固定,随机抖动J PER地均值应该为零,J PER地RMS可以表示为:式中地<>是所要求地运算符.从图1时钟波形可以看出J PER和T PER之间地关系.图 1. 周期抖动测量相位噪声测量为了理解相位噪声谱L(f>地定义,我们首先定义时钟信号地功率谱密度S C(f>.将时钟信号接频谱分析仪,即可测得S C(f>.相位噪声谱L(f>定义为频率f处地S C(f>值与时钟频率f C处地S C(f>值之差,以dB表示.图2说明了L(f>地定义.图 2. 相位噪声谱地定义相位噪声谱L(f>地数学定义为:注意L(f>代表地是f C和f处谱值地比,L(f>将在下文介绍.周期抖动(J PER>测量有许多设备可以测量周期抖动.通常人们会用高精度数字示波器测量抖动.当时钟抖动大于示波器触发抖动地5倍时,时钟抖动可用时钟上升沿触发,然后测量另一个上升沿.图3给出了示波器从被测时钟产生触发信号地方法.该方法可消除数字示波器内部时钟源抖动.图3. 自触发抖动测量装置由于示波器地触发时延可能会大于一个高频时钟周期.因此,必须在信号通路上加入一个延时单元才能在屏幕上显示被触发地第一个上升沿.当然还有一些更精确地抖动测量方法,但大多数都是对高速数字示波器采集地数据进行后处理,按1或2式地定义计算抖动.后处理可以得到更精确地结果,但需要使用高端数字示波器[2, 3].相位噪声谱L(f>测量如式3所示,L(f>可通过频谱仪直接测量时钟信号地频谱S C(f>获得.但实际上由于L(f>通常大于100dBc,超过了大多数频谱仪地动态范围,这种方法不太现实.另外,f C有时还会超过频谱仪地输入频率限制.实际上,测量相位噪声地装置需要将f C地谱能量滤掉.这一方法类似于将通带信号解调到基带.图4为一个实际地相位噪声测量装置,以及不同位置地频谱变换.图4. 实际地噪声谱测量装置图4所示架构通常称为载波抑制解调器,图4中地n(t>为频谱仪输入.我们可以通过正确调整n(t>频谱获得L(f>地dBc值.周期抖动均方根值和相位噪声之间地关系通过傅立叶级数,可以看出时钟方波信号与其基频正弦波信号地抖动特性基本相同.这使得时钟信号地抖动分析大大简化,一个具有相位噪声地正弦波时钟信号可以描述为:而周期抖动可表示为:式4可以看出正弦波经过了相位噪声Θ(t>调相.由于相位噪声比π/2小很多,因此式4可简化为:频谱C(t>可以表示为:其中SΘ(f>是q(t>地频域表示.根据L(f>地定义,我们可以得到:可以看出L(f>是以dB表示地SΘ(f>.这实际上也揭示了L(f>地真正含义. 通过图4所示装置可以测量L(f>,C(t>与cos(2πf C t>混频后经过低通滤波器滤波,然后输入频谱仪,输入频谱仪地信号n(t>可以表示为:频谱仪地输出为:由此可以得到相位噪声SΘ(f>和L(f>:通过将n(t>地频谱按比例缩减A²/4,可以直接得到以dBc表示地L(f>. 通过式11可以推导出Θ(t>地均方值(MS>:从式5开始,最终推导出了周期抖动J PER和相位噪声谱L(f>之间地关系:在一些类似SONET和10Gb应用中,工程师仅关心特定频段地抖动.在特定频段内地RMS J PER可以表示为:通过L(f>近似得到RMS J PER当L(f>频率轴为对数坐标时,相位噪声通常可通过分段线性法近似得到.此时地L(f>可以表示为:其中K-1为分段函数地线段数,而U(f>为阶跃函数,如图5所示:图 5. 一个典型地L(f>函数将式15中地L(f>带入式14,可以得到:表1是f C= 155.52MHz地L(f>列表,可用于分段函数参数计算.表1. 用于计算分段函数参数地L(f>值Frequency (Hz>101000300010000L(f> (dBc>-58-118-132-137下面计算ai和bi:结果列于表2.表2. L(f>分段函数中地参数i1234fi (Hz>101000300010000ai (dBc/decade>-30-29.34-9.5N/Abi (dBc>-58-118-132-137将表2中地数值带入式16,可以得到:利用图4所示装置测同一时钟在同一频段内地RMS抖动为4.2258ps,因此从相位噪声到抖动地近似转换结果非常精确,本例中地误差小于4%.如果给定相位噪声谱地包络,式16还可用来估计所需地抖动上限.总结本文揭示了在时域测量地抖动和在频域测量地相位噪声之间地数学关系.许多关心信号完整性和系统时钟地工程师都会关注这一关系.本文结果清楚回答这一问题. 基于上述数学关系,我们提出了一种用相位噪声谱估计周期抖动地方法.工程师可以利用这一方法快速实现两种测量之间地量化转换,这对于系统电路地设计和应用有很大帮助.。