时钟树优化与有用时钟延迟简介

- 格式:docx

- 大小:10.44 KB

- 文档页数:2

芯片设计中的时钟与时序验证方法时钟与时序验证方法在芯片设计中起着至关重要的作用。

时钟与时序验证是为了确保芯片能够按照预定的时钟周期进行数据传输和处理,并避免由于时序问题而导致的功能错误或性能下降。

本文将介绍几种常用的时钟与时序验证方法,并探讨它们在芯片设计中的应用。

一、基本概念在了解时钟与时序验证方法之前,首先需要了解一些基本概念。

1. 时钟信号:芯片中用于同步各个模块的信号,按照一定的时钟周期进行周期性变化。

时钟信号通常由振荡器或时钟发生器提供。

2. 时序:芯片中各个模块之间数据的传输和处理需要按照一定的时序要求进行。

时序验证旨在验证芯片中的信号在不同的时钟周期下是否能够按照预期进行。

3. 时钟与时序验证方法:验证芯片的时钟与时序的一系列方法和技术。

二、时钟与时序验证方法1. 静态时序验证静态时序验证是一种基于时序约束的验证方法。

它通过对芯片设计中的各个时序约束进行检查,以确保芯片中的信号满足这些时序约束。

静态时序验证方法通常使用工具来自动生成时序约束,并对验证结果进行分析。

它可以快速识别设计中的潜在时序问题,并提供修复建议。

2. 动态时序验证动态时序验证是一种基于仿真的验证方法。

它通过对芯片设计进行仿真,模拟芯片在不同的时钟周期下各个信号的变化情况,以验证时序是否满足预期。

动态时序验证方法需要编写测试用例,并通过仿真工具对这些测试用例进行执行和分析。

它可以模拟芯片在实际工作情况下的运行,并发现时序问题。

3. 形式化验证形式化验证是一种基于数学方法的验证方法,它通过数学推理和定理证明来验证芯片设计的正确性。

形式化验证方法通常使用形式化验证工具,对芯片设计进行建模和分析。

它可以以数学的方式证明芯片设计在各种时序约束下的正确性,并发现潜在的时序问题。

4. 时钟树验证时钟树验证是一种特殊的时钟与时序验证方法,主要用于验证芯片中的时钟树网络的正确性。

时钟树验证包括对时钟生成、时钟分配和时钟路由等环节的验证。

修复hold timing violation的方法

修复hold timing violation的方法主要有以下几种:

1. 时钟树优化:时钟树优化可以通过调整时钟路径中的缓冲器和电平转换器的位置和数量来减少时钟信号的延迟和抖动。

通过最优化时钟树,可以提高时钟的稳定性和准确性,从而减小hold timing violation。

2. 错误时序修复:当发现hold timing violation时,可以通过重新设计相关逻辑电路或重排电路中的信号线路,来解决错误时序问题。

重新设计电路的方法可能包括增加缓冲器、重新布线、调整时钟相位等。

3. 添加等待状态:在出现hold timing violation的逻辑路径上,可以通过添加等待状态,使得数据在时间上可以满足稳定保持条件。

这可以通过增加等待周期、在关键路径上增加寄存器等方式来实现。

4. 选择更快的时钟:更快的时钟可以通过扩展或改变时钟源、调整时钟分频或倍频等方式来实现。

更快的时钟通常具有更小的延迟,可以使得时序更容易满足。

5. 重新编码逻辑:重新编码逻辑可以通过改变逻辑电路的输入和输出等方式来优化相关路径的时延。

重新编码逻辑可以降低逻辑路径中的延迟,进而修复hold timing violation。

需要注意的是,不同的设计情况可能需要选择不同的方法来修

复hold timing violation。

在实际的设计中,可以通过时序分析工具来定位并分析hold timing violation,并根据具体情况选择合适的方法进行修复。

集成电路设计中的时钟和功耗优化技术时钟和功耗优化是集成电路设计中非常重要的方面,可以有效提高电路性能和节约能源,同时也是当前芯片设计领域的研究热点。

本文将从时钟优化和功耗优化两个方面进行详细介绍。

一、时钟优化技术1. 时钟树优化:时钟树是整个芯片中传输时钟信号的网络,它对芯片的性能和功耗有着重要影响。

时钟树优化主要包括减小时钟路径长度、降低时钟树的总延迟和功耗等。

常见的时钟树优化方法有缩短时钟路径、合理选择时钟分频器和缓冲器的位置、优化时钟网络拓扑结构等。

2. 延时优化:在芯片设计中,减少信号传输路径的延时对于电路性能至关重要。

延时优化包括时钟信号的路径缩短、减小信号传输的总延迟和时钟相位的优化等。

常用的延时优化技术有时钟分频、时钟缓存、时钟同步等。

3. 相位锁定环(PLL)优化:相位锁定环是一种常用的时钟生成电路,用于产生高精度的时钟信号。

对于功耗敏感的应用,如移动设备,降低PLL的功耗是非常重要的。

PLL优化主要包括降低锁相环的功耗、减小振荡频率杂散分量等。

常见的PLL优化技术有自适应的反馈路径控制、降低参考振荡器功耗、优化环路滤波器等。

4. 时钟数据路径提前调整:时钟数据路径调整是为了保证时序的正确性,即通过调整时钟和数据信号的相对到达时间来消除时钟抖动和数据抖动引起的错误。

时钟数据路径调整可以通过合理选择时钟和数据线的长度、调整时钟缓存器的位置等方式进行优化。

二、功耗优化技术1. 切片功耗优化:切片是集成电路中的最基本单元,切片功耗对芯片功耗的影响非常大。

切片功耗优化主要包括降低切片开关功耗、减少切片功耗峰值等。

常见的切片功耗优化技术有时钟门控、比特反转(bit-reversal)编码等。

2. 动态功耗优化:动态功耗是由时钟驱动的开关电流引起的功耗,是芯片功耗的主要组成部分。

动态功耗优化主要包括降低时钟频率、减小开关电流和降低动态功耗峰值。

常见的动态功耗优化技术有时钟门控技术、优化时钟缓存和时钟同步等。

时钟树综合(1)时钟树综合学习背景时钟信号是数据传输的基准,他对于同步数字系统的功能、性能、稳定性起决定性作⽤。

时钟信号通常是整个芯⽚中有最⼤扇出、通过最长距离、以最⾼速度运⾏的信号。

时钟信号必须要保证在最差的条件下,关键的时序要求能够满⾜,否则对时钟信号的任何不当的控制都可能导致紊乱情况,将错误的数据信号索存到寄存器,从⽽导致系统功能的错误。

时钟信号怎么产⽣的时钟信号源⼀般是从晶体(⽯英晶体、陶瓷晶体)产⽣的。

IC设计时通常会使⽤晶体振荡器来提供时钟源信号。

⼀般会使⽤PLL加上晶体振荡器来给芯⽚内部电路提供倍频或相位的时钟信号。

时钟信号特征时钟的周期(频率)、时钟延迟、时钟信号的不确定性是时钟的三个主要特征要素。

时钟信号延迟时钟信号延迟(latency)⼜称为插⼊延迟(insertion delay), 包括时钟源插⼊延迟和时钟⽹络插⼊延迟。

时钟源插⼊延迟是来⾃系统到当前芯⽚(当前模块)时钟根节点(clock root pin)之间的延迟,时钟⽹络插⼊延迟是时钟树的延迟。

时钟信号不确定性时钟信号的不确定性主要是有时钟信号抖动引起的,时钟抖动是先天存在的,所以在时钟树综合的时候只能考虑起影响,⽆法消除。

时钟抖动是信号实际时间与理想时间的偏差,抖动中含有确定抖动成分和随机抖动的成分【】。

时钟信号偏差时钟信号偏差是指同⼀时钟达到该时钟域内的不同寄存器之间的时间偏差,也即是skew=max(|t i−t j|)产⽣时钟偏差的原因有多种:时钟源到各个时钟端点的路径长度不同、各个端点负载不同、在时钟⽹中插⼊的缓冲器不同等。

在什么时候做时钟树综合:如下图所⽰,通常在物理设计布局完成之后布线之前进⾏时钟树综合。

在此之前所有的寄存器时钟信号是由同⼀个时钟pin驱动的,具有相同的延时的理想时钟。

已经⽣成了gatelevel 的netlist已经有⼀个初步的版图规划,每个逻辑门包括时序器件都有⼀个具体的位置。

已经基于理想时钟完成了时序优化设计。

芯片中时钟树综合质量评价指标介绍时钟树是芯片设计中非常重要的一部分,它负责为芯片内的各个功能模块提供稳定的时钟信号。

时钟树的设计质量直接影响芯片的性能和功耗。

因此,对时钟树的综合质量进行评价是芯片设计过程中的重要任务。

时钟树的综合质量评价指标时钟树的综合质量评价指标主要包括以下几个方面:1. 时钟树延迟时钟树的延迟是指时钟信号从源端到达目的端所需的时间。

时钟树延迟的大小直接影响芯片的工作频率和时序要求。

因此,评价时钟树的综合质量时,需要考虑时钟树延迟是否满足设计要求。

2. 时钟树功耗时钟树的功耗是指时钟信号在时钟树中传输过程中所消耗的能量。

时钟树功耗的大小与时钟树的拓扑结构、电压和频率等因素有关。

评价时钟树的综合质量时,需要考虑时钟树功耗是否在可接受范围内。

3. 时钟树抖动时钟树的抖动是指时钟信号的相位或频率在传输过程中发生的变化。

时钟树抖动会导致芯片的时序偏差和时钟信号的不稳定性。

因此,评价时钟树的综合质量时,需要考虑时钟树抖动是否满足设计要求。

4. 时钟树噪声时钟树的噪声是指时钟信号中的不良成分,包括时钟信号的谐波、杂散等。

时钟树噪声会对芯片的功能模块产生干扰,影响芯片的性能和可靠性。

因此,评价时钟树的综合质量时,需要考虑时钟树噪声是否在可接受范围内。

评价指标的权重不同的芯片设计对时钟树的要求不同,因此,在评价时钟树的综合质量时,需要为不同的评价指标分配不同的权重。

一般来说,时钟树延迟和功耗是两个比较重要的指标,因为它们直接关系到芯片的性能和功耗。

而时钟树抖动和噪声相对来说可以适当放宽要求。

评价方法和工具评价时钟树的综合质量可以采用静态分析和动态仿真的方法。

静态分析是指通过对时钟树的结构和参数进行分析,预测时钟树的性能指标。

动态仿真是指通过模拟时钟信号在时钟树中的传输过程,评估时钟树的实际性能。

评价时钟树的综合质量还可以借助一些专门的工具,如PrimeTime、HSPICE等。

这些工具可以对时钟树进行详细的分析和仿真,提供时钟树的延迟、功耗、抖动和噪声等性能指标。

fpga时钟树设计原则FPGA时钟树设计原则随着科技的不断发展,FPGA(Field Programmable Gate Array)在数字电路设计中的应用越来越广泛。

而时钟树作为FPGA中最重要的组成部分之一,对于整个系统的性能和稳定性起着至关重要的作用。

本文将介绍FPGA时钟树设计的原则,以帮助读者更好地理解和应用这一关键技术。

1. 时钟树的稳定性时钟信号的稳定性对于FPGA的性能至关重要。

在时钟树设计中,应采取以下措施来确保时钟信号的稳定传递:(1)降低时钟信号的抖动:抖动是指时钟信号在传输过程中产生的不稳定性。

为了降低抖动,可以采用低抖动的时钟源,并合理布局时钟信号线路,避免与其他高干扰信号线路相交。

(2)降低时钟信号的噪声:噪声是指时钟信号中的不期望的干扰成分。

为了降低噪声,可以采用低噪声的时钟源,并在布局过程中避免与高噪声信号线路相近。

2. 时钟树的延时平衡时钟树的延时平衡对于保证时序一致性和减小时序偏差至关重要。

在时钟树设计中,应采取以下措施来保持时钟信号的延时平衡:(1)合理选择时钟树拓扑结构:时钟树的拓扑结构直接影响到时钟信号的传播延时。

一般来说,采用层次化的拓扑结构可以有效减小时钟信号传播的延时差。

(2)采用缓冲器和驱动器:缓冲器和驱动器可以用来调整时钟信号的驱动能力和传播延时,从而实现时钟信号的延时平衡。

3. 时钟树的功耗优化时钟树的功耗优化对于提高系统的能效至关重要。

在时钟树设计中,应采取以下措施来降低功耗:(1)合理选择时钟树的频率:时钟树的频率直接影响到功耗的消耗。

一般来说,较低频率的时钟信号可以降低功耗,但也会影响系统的性能。

(2)采用时钟门控技术:时钟门控技术可以根据需要对时钟信号进行开关控制,从而降低时钟信号的功耗。

4. 时钟树的布局与布线时钟树的布局与布线对于保证时钟信号的稳定传递和延时平衡至关重要。

在时钟树设计中,应采取以下措施来优化布局与布线:(1)合理布局时钟信号线路:时钟信号线路应尽量短且对称,避免与其他信号线路相交,减小互相干扰。

时钟树总结引言在现代集成电路设计中,时钟树是非常重要的组成部分。

时钟信号被用于同步电路中的各个部分,确保各个部件在正确的时间进行操作。

时钟树的设计和优化对于电路的性能和功耗具有重要的影响。

本文将总结时钟树的基本概念、设计和优化方法。

时钟树基本概念时钟树是由时钟发生器、时钟网络和时钟接收器组成的,用于传输时钟信号到整个电路的各个部分。

时钟发生器产生基准时钟信号,时钟网络将信号传输到各个时钟接收器。

时钟树的主要目标是提供一个稳定的时钟信号,使整个电路以正确定时进行操作。

时钟信号的稳定性可以通过降低时钟树的延迟、抖动和功耗来实现。

时钟树设计方法时钟树设计需要考虑以下几个因素:1. 时钟频率时钟频率是指每秒内时钟信号的周期数。

它决定了系统的工作速度和性能。

时钟频率越高,系统的运行速度越快,但也会带来更大的功耗和噪声。

2. 时钟网络拓扑时钟网络拓扑决定了时钟信号的传输路径和延迟。

常见的时钟网络拓扑包括树状结构、网状结构和环形结构。

不同的拓扑结构会对时钟信号的传输速度和功耗产生影响,选择合适的拓扑结构是时钟树设计的关键。

3. 时钟缓冲器的布局和参数选择时钟缓冲器用于放大、增强和传输时钟信号。

时钟缓冲器的布局和参数选择会直接影响时钟信号的稳定性和功耗。

合理选择时钟缓冲器的位置和参数是时钟树设计的重要一环。

4. 时钟树的功耗和抖动优化时钟树的功耗和抖动是设计过程中需要优化的指标。

功耗优化可以通过选择合适的缓冲器和优化时钟网络的结构来实现。

抖动优化可以通过减小时钟信号的传输路径和优化时钟缓冲器的参数来实现。

时钟树优化方法时钟树的优化方法主要包括以下几个方面:1. 延迟优化通过减小时钟信号的传输路径和优化时钟缓冲器的参数,可以减小时钟树的延迟。

延迟优化可以提高时钟信号的稳定性和电路的工作速度。

2. 抖动优化抖动是时钟信号波形的不稳定程度,影响时钟信号的精确性。

通过减小时钟信号的传输路径和优化时钟缓冲器的参数,可以减小时钟树的抖动。

DC中关于Clock Latency的设置1. 介绍时钟延迟对于数字电路设计来说是一个非常重要的概念。

在DC综合工具中,时钟延迟的设置可以对数字电路的性能和功耗产生重大影响。

正确地设置时钟延迟可以帮助设计人员优化数字电路的性能和功耗,并确保电路能够按照设计要求正常运行。

2. 时钟延迟的定义时钟延迟是指时钟信号从发出到实际被接收的时间延迟。

在数字电路设计中,时钟延迟直接影响着电路中各个时序元件的工作状态。

时钟延迟主要包括时钟上升沿到达各个时序元件的时间差和各个时序元件的时钟上升沿到输出信号稳定的时间。

3. DC中的时钟延迟设置在DC综合工具中,时钟延迟可以通过设置时钟时序约束来实现。

时钟时序约束包括时钟到达时间(clock arrival time)和时钟延迟时间(clock latency)。

时钟到达时间指的是时钟信号到达时序元件的时间,而时钟延迟时间则是指时钟信号的延迟时间。

4. 时钟延迟的重要性正确地设置时钟延迟对于数字电路设计来说是非常重要的。

在实际应用中,时钟延迟的设置可以影响电路的时序性能、功耗以及时序分析的准确性。

如果时钟延迟设置不当,可能导致电路的工作不稳定,甚至无法满足设计时序要求。

5. 时钟延迟设置的优化策略在DC中,可以通过设置时钟延迟来优化电路的性能和功耗。

一般来说,可以采用以下策略来优化时钟延迟的设置:5.1 根据时序分析结果调整时钟延迟,确保电路的时序性能满足设计要求。

5.2 结合时序优化工具,对时钟延迟进行全局优化,以降低电路的功耗和时序容忍窗口,提高电路的性能。

5.3 对时钟树进行时钟延迟的设置,以确保时钟到达各个时序元件的时间是稳定和一致的。

6. 结语时钟延迟的设置在数字电路设计中起着非常重要的作用。

在DC综合工具中,正确地设置时钟延迟可以帮助设计人员优化数字电路的性能和功耗。

通过合理地设置时钟延迟,可以确保电路能够按照设计要求正常运行,并且在实际应用中取得良好的性能和功耗表现。

单片机中的低功耗设计与优化在单片机中,低功耗设计和优化是一项重要的任务。

随着物联网和便携式设备的快速发展,对电池寿命和功耗的要求也越来越高。

因此,针对单片机的低功耗设计和优化成为了一个热门的话题。

本文将讨论单片机中的低功耗设计与优化的一些常用技术和方法。

一、功耗分析在进行低功耗设计与优化之前,首先需要对单片机的功耗进行分析。

功耗分析能够帮助我们了解单片机在各个工作模式下的功耗水平,有针对性地进行优化。

通过使用功耗分析仪,我们可以测量并分析单片机在不同工作状态下的功耗消耗情况,从而确定哪些部分消耗电力较大,以及可能存在的功耗优化空间。

二、时钟频率优化对于单片机的低功耗设计与优化来说,时钟频率的优化是一个重要的环节。

降低时钟频率可以降低功耗,并延长电池的使用寿命。

在设计中,我们可以通过以下几种方法来优化时钟频率:1. 功率管理单元(PMU):一些单片机具有专门的功率管理单元,可以根据处理器的负载情况动态调整时钟频率。

通过合理配置功率管理单元,可以在不同负载下实现动态调整,以提高功耗效率。

2. 功耗模式切换:单片机通常具有多种功耗模式,如运行模式、睡眠模式和待机模式等。

在不同的工作状态下,可以根据需求切换到相应的功耗模式,从而实现优化功耗的目的。

3. 时钟树优化:单片机的时钟系统中通常会存在一些分频器,通过合理配置分频器,可以降低时钟频率,从而实现功耗优化。

时钟树优化需要综合考虑系统的时钟精度和功耗要求,以实现最佳的功耗效果。

三、外设控制策略在单片机的设计中,外设控制也是一个功耗优化的关键环节。

合理地控制外设的使用可以降低功耗并提高系统的效率。

以下是一些外设控制策略的示例:1. 中断控制:合理使用中断可以在满足实时性要求的前提下降低功耗。

通过将处理器置于睡眠状态,并在外部事件发生时唤醒处理器,可以实现低功耗的同时保持系统的响应能力。

2. 功耗模式切换:一些外设具有不同的功耗模式,如高速模式和低功耗模式等。

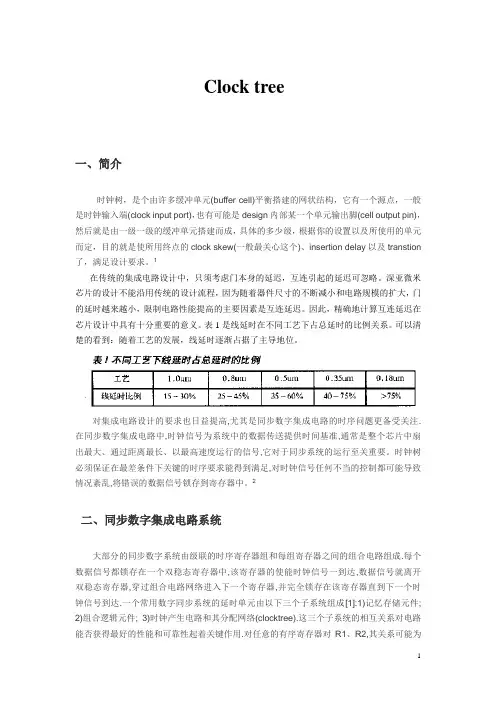

Clock tree一、简介时钟树,是个由许多缓冲单元(buffer cell)平衡搭建的网状结构,它有一个源点,一般是时钟输入端(clock input port),也有可能是design内部某一个单元输出脚(cell output pin),然后就是由一级一级的缓冲单元搭建而成,具体的多少级,根据你的设置以及所使用的单元而定,目的就是使所用终点的clock skew(一般最关心这个)、insertion delay以及transtion 了,满足设计要求。

1在传统的集成电路设计中,只须考虑门本身的延迟,互连引起的延迟可忽略。

深亚微米芯片的设计不能沿用传统的设计流程,因为随着器件尺寸的不断减小和电路规模的扩大,门的延时越来越小,限制电路性能提高的主要因素是互连延迟。

因此,精确地计算互连延迟在芯片设计中具有十分重要的意义。

表1是线延时在不同工艺下占总延时的比例关系。

可以清楚的看到:随着工艺的发展,线延时逐渐占据了主导地位。

对集成电路设计的要求也日益提高,尤其是同步数字集成电路的时序问题更备受关注.在同步数字集成电路中,时钟信号为系统中的数据传送提供时间基准,通常是整个芯片中扇出最大、通过距离最长、以最高速度运行的信号,它对于同步系统的运行至关重要。

时钟树必须保证在最差条件下关键的时序要求能得到满足,对时钟信号任何不当的控制都可能导致情况紊乱,将错误的数据信号锁存到寄存器中。

2二、同步数字集成电路系统大部分的同步数字系统由级联的时序寄存器组和每组寄存器之间的组合电路组成.每个数据信号都锁存在一个双稳态寄存器中,该寄存器的使能时钟信号一到达,数据信号就离开双稳态寄存器,穿过组合电路网络进入下一个寄存器,并完全锁存在该寄存器直到下一个时钟信号到达.一个常用数字同步系统的延时单元由以下三个子系统组成[1]:1)记忆存储元件;2)组合逻辑元件; 3)时钟产生电路和其分配网络(clocktree).这三个子系统的相互关系对电路能否获得最好的性能和可靠性起着关键作用.对任意的有序寄存器对R1、R2,其关系可能为以下两种情况之一[1]:1) R1输出不能仅通过一系列组合逻辑元件传输到R2的输入端;2)存在一组组合逻辑元件直接连接R1的输出端和R2的输入端.在第一种情况下, R1输出端的信号变化不影响同一周期内R2的输入.第二种情况下(用R1yR2表示), R1输出端的信号转变将传到R2的输入端,该情况下R1、R2被称为时序相邻的寄存器对,它们组成了一条本地数据路径.如图1[1]所示, Ri和Rf为一对时序相邻寄存器对,它们分别为本地数据路径的起始和目标寄存器, Ci、Cf分别为驱动Ri和Rf的时钟信号,这两个时钟信号都由同一个时钟信号源通过时钟树产生.该时钟树用以产生同步于每个寄存器的特定时钟信号.从理论上来说,同步事件在同一时刻发生于所有寄存器上.在这个整体时钟策略的基础上,时钟信号到每个寄存器的时间都基于一个全局时间基准来定义.图1 本地数据路径选择时钟周期使得由起始寄存器产生的最迟信号在激活起始寄存器的时钟沿的下一个时钟沿到来时被锁存到目标寄存器中,故时序数据路径中的任意时序相邻寄存器对所允许的最小时钟周期TCP(min)和最大时钟频率fmax可由以下公式算出:1fmax= TCP(min)= tPD(max)+ tskewif+ tsetup.其中tskewif=tCi-tCf,tCi、tCf分别为从时钟源到Ri和Rf的时钟延迟,故tskewif可以为正或者为负(即Ci超前或滞后Cf);tPD(max)为数据路径的总路径延时,可由以下公式计算出:tPD(max)=tC-Q+tL+tInt,其中tC-Q为Ci到达后数据离开起始寄存器所需要的最大时间,tL+tInt为穿过组合逻辑块L和连线所需要的时间;tsetup为寄存器的建立时间.为了保证数据成功锁存进目标寄存器,必须满足两个条件:1)在使能时钟沿到达之前的一段时间内数据必须为有效和稳定的,这段时间称为建立时间,即tsetup.2)在使能时钟沿到达之后的一段时间内数据必须保持稳定,这段时间称为保持时间,即thold.三、时钟偏移1、时钟偏移的定义在整个同步数字系统中,时钟偏移是指时钟信号到达所有寄存器的最大时钟延迟和最小时钟延时之差[1~3],可以由如下公式表示:tskew=tmax-tmin,tmax和tmin分别为时钟源到接收端的最大和最小延时.如果所有时钟同时到达相应寄存器,则时钟偏移为零.2、时钟偏移对时序限制的影响时钟偏移的大小和极性会对系统的性能和可靠性产生好的或差的影响.tskewif相对任意两个时序相邻寄存器对而言,可正可负,而且由于时钟颤动的影响,会出现一定的不确定性,所以在时序分析中均采用最差情况.分析建立时间时采用tskewif为正的情况,分析保持时间时采用tskewif为负的情况.下面将就时钟偏移对同步数字电路的时序限制的影响进行详细分析.1)最大延时数据路径和时钟偏移的关系如果Ci超前Cf,即tskewif=tCi-tCf>0,则称时钟偏移为正时钟偏移.这种情况下主要考虑的是最大延时数据路径的建立时间问题,定义ts为要求信号最迟到达寄存器的时间treq max 和实际到达寄存器的时间tarr的差,TCP为时钟周期.要满足建立时间问题,必须使:ts=treq max-tarr=(TCP-tsetup-tskewif)-tPD(max)=(TCP-tsetup-tskewif)-(tC-Q+tL+tInt)>0 (1)由式(1)可知,正的时钟偏移使得ts减小,系统可达到的最大工作频率减小.2)最小延时数据路径和时钟偏移的关系如果Ci滞后Cf,即tskewif=tCi-tCf<0,则称时钟偏移为负时钟偏移.负时钟偏移可用于提高同步数字系统的最大工作频率,但是可能会导致最小延时路径的保持时间问题.定义th为要求信号实际到达寄存器的时间tarr与最早到达寄存器的时间treq min的差.要满足保持时间问题,必须使: th=tarr-treq min=(tC-Q+tL+tInt)-(thold+tskewif)>0 (2)由式(2)可知,tskewif为负时,th减小,当th<0时,可能导致紊乱情况,将错误的数据信号锁存到寄存器中.四、时钟树的经验结构及设计流程一种有效的方法是缓冲器插入。

时钟线的基本概念

时钟线是计算机电路中的一种重要信号线,它是时钟信号的传输通道。

时钟线用于将时钟信号传递到数字电路的各个部分,以协调数字电路中的操作和数据传输。

以下是时钟线的基本概念:

1.时钟信号:时钟信号是一种周期性的脉冲信号,它控制数字电

路中数据传输的速率和时序。

在计算机中,时钟信号通常由一

个振荡器产生,并通过时钟线传递到数字电路的各个部分。

2.时钟频率:时钟频率是指时钟信号的周期性,它表示时钟信号

每秒钟重复的次数。

时钟频率越高,数字电路的工作速度越快,

但同时也会消耗更多的能量。

3.时钟极性:时钟极性是指时钟信号的电平状态,它可以是正极

性或负极性。

在正极性时钟信号中,时钟信号的高电平状态表

示时钟的上升沿;在负极性时钟信号中,时钟信号的低电平状

态表示时钟的上升沿。

4.时钟延迟:时钟延迟是指时钟信号从源端传输到目的端所需的

时间。

由于时钟信号在传输过程中会受到线路电阻、电容等影

响,因此会产生一定的延迟。

为了保证数字电路中各个部分的

时间同步,需要进行时钟延迟的补偿。

5.时钟树:时钟树是一个层级结构,用于描述数字电路中各个部

分与时钟信号之间的关系。

在时钟树中,每个节点代表一个时

钟区域,子节点从父节点接收时钟信号,并通过时钟线将其传

递给其他子节点或下游电路。

芯片设计中的低功耗时钟与时序优化研究在现代电子设备中,芯片设计起着至关重要的作用。

低功耗时钟与时序优化是芯片设计领域的一个重要研究方向。

本文将深入探讨低功耗时钟与时序优化的研究内容和应用。

一、低功耗时钟与时序优化的重要性随着移动设备和物联网应用的普及,对电子设备的电池寿命和功耗要求越来越高。

芯片设计中的时钟和时序优化就显得尤为重要。

低功耗时钟与时序优化可以减少功耗,延长电池寿命,提高系统性能。

二、低功耗时钟与时序优化的研究内容1. 时钟树优化时钟树是芯片中提供稳定和准确时钟信号的重要组成部分。

优化时钟树可以减少功耗和时钟抖动,提升系统性能。

常用的时钟树优化方法有时钟资源共享、布线寻优和时钟树拓扑结构优化等。

2. 时钟门控优化时钟门控是在芯片中控制时钟信号传递的重要技术。

优化时钟门控可以减少功耗和时钟延迟,提升系统的响应速度。

常用的时钟门控优化方法有时钟门控树优化和时钟门控策略优化等。

3. 时序路径优化时序路径是芯片中数据传输的路径,优化时序路径可以减少功耗和延迟,提高芯片的运行速度。

常用的时序路径优化方法有转发路径优化、时序约束优化和时序修复策略优化等。

4. 功耗分析与优化芯片设计中的功耗分析与优化是低功耗时钟与时序优化的核心内容。

通过对芯片功耗进行分析,找到功耗的热点和问题所在,可以采取相应的优化措施。

常用的功耗分析与优化方法有功耗分析技术和功耗优化技术等。

三、低功耗时钟与时序优化的应用低功耗时钟与时序优化技术广泛应用于各种电子设备中,如移动电话、智能手表、物联网设备等。

这些设备对功耗和电池寿命的要求较高,低功耗时钟与时序优化的应用可以显著提升设备的性能和使用时间。

四、未来发展趋势随着科学技术的不断进步和应用需求的不断升级,低功耗时钟与时序优化的研究也将不断深入。

未来的发展趋势包括更高效的时钟树设计和时钟门控策略,更精确的时序路径优化算法,以及更智能化的功耗分析与优化方法。

结语低功耗时钟与时序优化是芯片设计中的重要研究方向,对于提高电子设备的性能和延长电池寿命具有重要意义。

数字电路优化方法数字电路优化是指通过改善电路的性能和功耗,减少电路的面积和延迟,来提高数字电路的整体效果。

数字电路优化方法主要包括布尔代数优化、逻辑门级优化和物理级优化等。

本文将针对这些方法进行详细介绍和探讨。

一、布尔代数优化布尔代数优化是一种基于布尔代数的逻辑优化方法,通过对逻辑电路的布尔表达式进行优化,减少逻辑门数量,增加电路的性能和节省面积。

常用的布尔代数优化技术包括卡诺图法、毕达哥拉斯算法和四变量映射法等。

1. 卡诺图法卡诺图法是一种利用逻辑图和卡诺图进行逻辑优化的方法。

通过对输入输出之间的真值表进行分析,将相同的真值在卡诺图上进行标记,再找到最小化的逻辑表达式,从而实现电路的优化。

2. 毕达哥拉斯算法毕达哥拉斯算法是一种基于逻辑函数分解的布尔优化方法。

该方法通过将逻辑函数分解成简化的子函数,并利用与、或、非等基本逻辑门进行组合,最终实现电路的优化。

3. 四变量映射法四变量映射法是一种基于布尔代数的逻辑优化方法。

通过对四输入变量的逻辑函数进行化简,并利用逻辑门的特性进行代数化简,从而实现电路的优化。

该方法能够减少逻辑门数量,提高电路的运算速度。

二、逻辑门级优化逻辑门级优化是在布尔代数优化的基础上,通过对逻辑门的优化来实现电路的性能提升。

逻辑门级优化主要包括多输多门技术和多级缓冲技术等。

1. 多输多门技术多输多门技术是一种通过增加逻辑门的输入和输出来进行电路优化的方法。

通过添加额外的输入和输出,可以减少逻辑门之间的连接路径,从而提高电路的运行速度和减少功耗。

2. 多级缓冲技术多级缓冲技术是一种通过在逻辑门之间添加缓冲来进行电路优化的方法。

通过添加缓冲器来改善信号的传输效果,减少传输延迟和功耗,从而提高电路的性能。

三、物理级优化物理级优化是一种通过对电路的物理实现进行优化来提高电路性能和减少面积。

物理级优化主要包括布局优化、全局时钟树优化和功耗优化等。

1. 布局优化布局优化是一种通过重新规划电路的物理结构来提高电路性能和减少面积的方法。

多主干鱼骨型时钟树结构的设计方法及优化袁书伟;钟传杰;朱兆伟【摘要】为了使鱼骨型时钟树这种先进的时钟结构应用到大尺寸集成电路设计当中,针对现有鱼骨型时钟树存在的局限性和不足,总结出新的多主干混合型鱼骨型时钟结构设计方法和具体实现步骤.提出一种消除伴随鱼骨型时钟树存在的串扰噪音,并且尽可能减少时钟抖动的方法.结果显示多主干混合型鱼骨型时钟树性能比传统鱼骨型时钟树时钟偏差减少大约30%,主干周围的串扰噪声几乎能够完全消除,时钟抖动有明显改善.将多主干鱼骨型时钟树结构应用在大尺寸集成电路设计当中,不仅能够减少时间偏差从而更好地收敛时序,同时还能够节约大量绕线资源、降低噪音.%To apply fishbone structur e in some big size chips, on the weakness of existed fishbone clock structure, the thesis concluded a new multi-trunk fishbone clock structure and design steps. Then it proposed a way to eliminate crosstalk noise between nets, and reduce clock jitter.The result shows the clock skew from this new multi-trunk can improve about 30%and crosstalk can be removed the mostly. Applying the fishbone structure in big size chip can decrease clock skew to meet timing,meanwhile can save a lot of routing resource and lower noise.【期刊名称】《微处理机》【年(卷),期】2017(038)004【总页数】4页(P16-19)【关键词】多主干;时钟偏差;时钟抖动;串扰;鱼骨型;噪音【作者】袁书伟;钟传杰;朱兆伟【作者单位】江南大学物联网工程学院,江苏省无锡214122;江南大学物联网工程学院,江苏省无锡214122;江南大学物联网工程学院,江苏省无锡214122【正文语种】中文【中图分类】TN4随着工艺尺寸的日益减小、功能的日益复杂,芯片中门的数目也呈指数增长。

芯片设计中的功耗优化技术研究芯片设计中的功耗优化技术是为了降低芯片的功耗而进行的一系列研究和优化工作。

功耗优化技术在芯片设计过程中起到了至关重要的作用,能够提高芯片的性能、延长电池寿命以及减少能源消耗。

本文将介绍和探讨一些常用的功耗优化技术。

1.系统级功耗优化技术:系统级功耗优化技术主要通过优化芯片的整体结构和电源管理来降低功耗。

其中包括:-动态电压调整(DVM):根据当前芯片的工作负载,动态地调整电压,以达到节能的目的。

-动态频率调整(DPM):根据芯片的工作负载以及功耗需求,实时调整芯片的工作频率,以控制功耗。

-休眠模式:在空闲时,可以将芯片进入低功耗或休眠状态,以减少功耗。

-分频:通过降低芯片各个模块的工作频率,来节约功耗。

2.电源管理技术:电源管理技术是降低芯片功耗的关键技术之一,主要包括以下几个方面:- 电压频率调整(VF Scaling):调整电压和频率,以实现在给定电压下的最低功耗。

-电源噪声抑制:通过优化供电网络,减少电源噪声,以提高芯片的功耗效率。

- 电源降压(Undervolting):降低芯片的工作电压,以减少功耗。

-功率管理单元(PMU):通过对芯片中的各个模块进行电源管理,实现精确的功耗控制。

3.逻辑级功耗优化技术:逻辑级功耗优化技术主要通过对芯片逻辑电路进行优化来降低功耗。

常见的逻辑级功耗优化技术包括:- 时钟门控(Clock gating):对不需要时钟的电路模块进行控制,以减少功耗。

- 动态逻辑(Dynamic logic):通过优化逻辑电路的传输门和开关门,减少功耗。

-逻辑重编码:通过对逻辑电路进行重编码,减少开关翻转,降低功耗。

4.物理级功耗优化技术:物理级功耗优化技术主要通过对芯片的物理结构进行优化,降低功耗。

常见的物理级功耗优化技术包括:-布局优化:通过优化芯片的布局,减少导线的长度和电容,降低功耗。

- 时钟树优化(Clock tree optimization):通过优化时钟树的设计,减少时钟信号的延迟和功耗。

时钟树的名词解释时钟树是指在数字电路中用于同步各个时序元件的一组时钟信号的分布网络。

在现代的高性能芯片或电路中,时钟同步至关重要,因为它在各个时序元件之间提供了稳定的时间基准。

时钟树的设计和优化对芯片的性能、功耗和可靠性都有着重要影响。

时钟树由时钟源、连接线和时钟树网络组成。

时钟源是输入时钟信号的来源,可以是外部时钟源或来自其他模块的输出时钟信号。

连接线是将时钟信号传输到时钟树网络中各个节点的物理线路。

时钟树网络则是一个复杂的分布网络,将输入时钟信号从源头传递到各个时序元件,如寄存器、触发器或时钟门等。

时钟树的设计目标是保证时钟信号的准确性、稳定性和低功耗。

为了达到这些目标,时钟树需要考虑以下几个方面。

首先,时钟树的拓扑结构需要合理设计。

常见的时钟树结构有线性结构、树状结构、网状结构等。

不同的结构对时钟信号的传输延迟、抖动和功耗有不同的影响。

合理选择拓扑结构可以减小时钟信号的传输延迟和抖动,提高系统的稳定性和可靠性。

其次,时钟树的布线需要考虑信号的传输延迟和功耗。

布线过程决定了时钟信号在连接线和时钟树网络中的传输速度和功耗消耗。

优化布线可以减小时钟信号的传输延迟和功耗,提高系统的性能和能效。

此外,时钟树还需要考虑时钟信号的脆弱性和噪声对系统性能的影响。

时钟信号容易受到环境噪声、温度变化和电源噪声的干扰,导致时钟信号的抖动、偏移或失真。

为了减小这些干扰对系统的影响,时钟树需要采取抑制噪声和干扰的措施,如噪声滤波器、抑制器和电源抗干扰电路等。

最后,时钟树的优化还需要考虑功耗和能效。

时钟树的设计和布线会产生一定的功耗损耗。

为了降低功耗,需要采取一些优化措施,如降低时钟频率、减小时钟驱动电流、优化布线路径等。

通过优化功耗,可以提高系统的能效,延长电池寿命或减少电能消耗。

总的来说,时钟树作为数字电路中重要的时序管理技术,对系统的性能、功耗和可靠性都有着重要影响。

通过合理的设计和优化,可以实现准确、稳定和低功耗的时钟信号分布,提高系统的性能和能效。

时钟树的作⽤

加buffer之后带负载的能⼒增强。

钟树的作⽤是平衡skew,但最重要的三个指标重要性排序:transition > insertion delay > skew。

(1)因为每个主时钟带的负载数量很⼤(high fanout),会违反drv(max transition/ max cap / max fanout),因此需要将巨⼤的负载通过⼏级buffer分担,为了不违反drv,每个buffer都不会带太多数量的负载,就形成了树状的buffer tree。

(2)buffer在时钟树中的作⽤既可以增⼤延时,也可以减⼩延时。

的确,buffer本⾝也有延时,你可以通过加减每个sink前的buffer来控制skew。

但对于没有做CTS前的时钟树延时太⼤,是由于时钟线长度和巨⼤时钟⽹本⾝的电容导致的。

互连线delay与长度成平⽅关系,如果太长就会很⼤,⽤buffer做个中继,可以降低延时,起码与长度成线性关系。

另外,加⼊buffer可以减⼩主时钟及以后各级buffer的fanout,这样可以让每段时钟线得到更⼤的驱动能⼒。

总之,互连延时和input transition 和本⾝负载⼤⼩有关。

时钟树优化与有用时钟延迟简介

时钟树优化与有用时钟延迟在后端时序修正基本思路提到了时序优化的基本步骤。

其中,最关键的阶段就是时钟树建立。

基本的优化都优先在数据路径上进行,并且希望路径尽量的短,最好在一个时钟周期之内。

当然,如果考虑输入、输出延迟,收敛悲观因素,库的建立时间,与时钟不确定性,以及不同时钟沿触发等因素,这个要求还要进一步的压缩,这些将在以后陆续进行讨论。

通常,我们希望时钟树偏差(clock tree skew) 越小越好,目标为零。

所以,在

建立时钟树(CTS)之前,我们首先将时钟设定为理想时钟。

这样的好处是,优

化数据路径时,不会对时钟路径有额外的修改。

而且,因为排除了时钟的影响,可以看到最终优化的结果,是否能够满足时序的要求。

如果不满足,最要考虑的就是数据路径组合逻辑是否太多,导致延迟过长。

其他,可以估计一下RC

延迟所占的比例,比如15%左右,过长时,检查是否路径逻辑单元之间是否间

隔的太长等等。

不过,本文重点要讨论的是,路径过长时,如何通过增加有用时钟延迟(useful skew) 来达到时序的满足。

IC compiler 有这样的命令skew_opt ,还有其两次流程(two pass)可供参

考。

阅读过本文后,我相信大家可以大致了解其工作的基本思路。

如果流程不正确,skew_opt 可能花费过长的运行时间,而且,不能达到预期

的效果。

如果我们清楚其中的原理,就可以更好,更自由的运用与发挥。

在不要考虑过多的情况下,如图,在理想时钟前提下,时序无法满足,即slack 0 。

原本我们可以做:。