H树时钟树设计

- 格式:doc

- 大小:659.50 KB

- 文档页数:5

数字后端设计实现之时钟树综合实践篇时钟树综合定义时钟树综合就是指从某个clock的root点长到各个sink点的clock buffer/inverter tree。

工具试图将某个clock所属的所有sinks做到相同长度。

从概念上,我们可以得到几个要点。

图1 时钟树CTS之前你应该先搞清楚以下几点(非常重要)•clock的root点需要定义清楚。

这个可以通过create_clock来定义。

如果是create_generated_clock,它的master clock需要定义清楚。

同时要求generate clock与master clock是可以trace通的•clock 的sinks•哪些clock是同步,哪些是异步的•分析时钟结构,大致画出其结构图。

如果时钟结构比较复杂,建议编写CTS constraint,来引导工具build tree•定义好stop pin ignore pin exclude pin floating pin等•哪些clock是需要做inter-balance的衡量时钟树的几大指标合理的时钟结构能够加速Timing收敛(时钟树综合中级篇)时钟树综合(clock tree synthesis)基础篇设置DRC参数设置max_transition max_capacitance max_fanout等参数。

对于clock的max transition的设置,应该根据clock的频率来设置。

高频率的clock,需要额外设置严格点。

指定clock inverter listset_clock_tree_references -references $cts_clock_inv_listset_clock_tree_references -references $cts_clock_inv_list -sizing_onlyset_clock_tree_references -references $cts_clock_inv_list -delay_insertion_onlyclock inverter cell list的选择往往比较有讲究。

芯片物理设计龙芯中科依托中科院计算所微处理器研究中心,源源不断得到坚实的技术支持和充足的人才储备。

芯片物理设计团队先后完成龙芯1号、龙芯2C、龙芯2E 和龙芯2F等高性能通用微处理器芯片的设计,采用工艺从0.18um至90nm,最高主频已经达到GHz范围。

为了实现更高性能的设计目标,结合通用设计流程先后开发了一系列高性能设计流程及点工具,诸如基于规则H树的高性能时钟树生成(High Performance Clock Tree Generation based on Formal H Tree)、规则化设计方法学(Regular Design Methodology)等等。

目前主要设计方向为高性能SOC设计,面向90nm以下工艺(65nm、45num等),产品成果处于国内尖端水平。

近十年积累的独创性经验能帮助客户顺利完成物理设计阶段的工作。

龙芯中科以跟踪国际最新CPU技术为标准,以发展和推广龙芯自有知识产权技术为己任。

目前在自主创新高端通用CPU领域中处于领先的地位,并成为国内最有影响力的核心技术和芯片供应商,已为用户开发多款专用芯片和CPU系统。

这些产品已经成功地应用于网络、工控、安全、移动等各种领域。

公司借助在龙芯系列研发过程中掌握的核心技术,愿为行业客户提供各种基于龙芯的应用解决方案和全方位技术合作。

龙芯一号龙芯一号处理器是完全自主设计的32位RISC 结构通用微处理器,其技术参数如下表。

龙芯一号处理器的微体系结构如下图所示,它采用了寄存器重命名、动态调度、乱序执行等主流技术。

龙芯一号处理器芯片实现了批量生产,并针对市场的需求,在其基础上陆续开发出龙芯32位处理器IP 核。

有关龙芯处理器IP 核产品方面的情况,请参看“IP产品”链接。

龙芯2C龙芯2号(C版本)处理器(简称“龙芯2C”)是完全自主设计的64位RISC结构高性能通龙芯2C处理器的微体系结构如下图所示,它在结构上采用了四发射、猜测执行、动态调度等先进技术。

多级门控时钟网络设计优化探究摘要:近年来,我国信息技术和经济水平不断发展,计算机技术、移动通讯技术、多媒体技术及半导体技术等取得了飞快进步,集成电路产业在此背景下得到了迅猛发展。

在实际运行过程中,对芯片集成度及其工作效率的要求不断提升,导致门控时钟的不确定性与复杂性特征逐渐显现,加快多级门控时钟网络优化的步伐成为集成电路产业未来的发展方向。

本文就针对门控时钟网络优化常用时钟树类型展开分析,深入探究多级门控时钟网络设计优化策略,希望对相关部门开展工作有所参考。

关键词:门控时钟;网络设计;优化前言:时钟树的主要作用是降低时钟偏差,提高时钟信号同步传输到每一触发器的效率和质量。

随着集成电路制造工艺的不断缩小,时钟网络的传播延时特征逐渐增大,加强多级门控时钟网络设计优化进程,采用时钟网络公共路径比重大的混合树进行时钟树综合,可在其中增加有效的时序检查,还能确保功能的正确性,从而提高信号的逻辑深度,提升运行效率和质量。

1.门控时钟网络优化常用时钟树类型1.1树型时钟树树型时钟树顾名思义就是类似于一棵树的时钟树,不存在拓扑回路,以时钟根节点作为树根,以寄存器、存储器等时序单元作为叶节点,而拓扑结构表示树干,具体包括平衡树、H树及X树。

平衡树的结构较为简单,所占的布线布局所用资源较少,且实现方便,是目前使用较为广泛的时钟树;H树属于一种高度对称的时钟树,时钟根节点到叶节点的距离和级数相同,时钟延时也相同,但实际实施过程中,常因为各种因素难以做到完全对称,如布线拥塞、设计硬宏、布线阻挡层等,从而增加时钟偏差无法控制的可能性;X树属于H树的变型,主要采用非曼哈顿线的方式,使用诸多非90°的互连线达到降低公共路径比重的目的。

1.2网状时钟树网状时钟树的主要特点是拓扑结构存在回路或者并行驱动,将时钟信号由单一的阶段扩散遍布到整个时钟区域网络内,以鱼骨型、网格型、多脊柱型较为常见。

鱼骨型时钟树由于拓扑结构类似鱼的骨架而得名,主要从时钟根节点出发,经过多级并行预驱动的结构驱动主干,适用于矩形的模块或者芯片;网格型时钟树可以说是鱼骨型时钟树的延伸,主要用多种的横向和纵向走线来代替鱼骨型单条的主干或者多条分支,并将其覆盖到整个叶节点分布区域,使叶节点获得充足的驱动能力;多脊柱型时钟树可对设计硬宏、布局布线阻挡层等导致叶节点分布不均的情况进行针对性解决,通过对其进行优化调整,使网格能够覆盖整个时钟叶节点[1]。

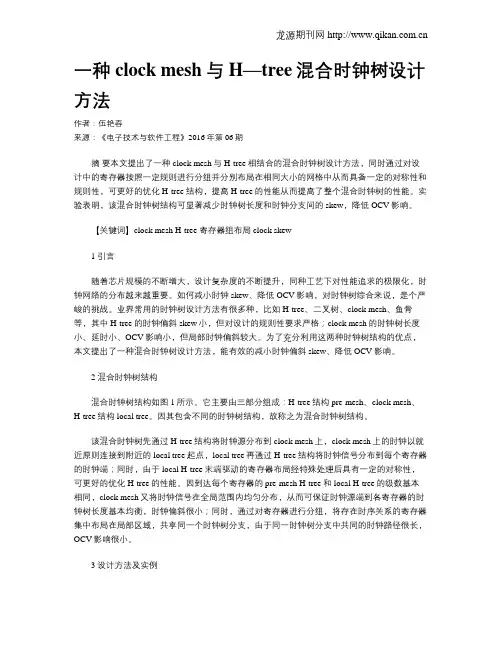

一种clock mesh与H—tree混合时钟树设计方法作者:伍艳春来源:《电子技术与软件工程》2016年第06期摘要本文提出了一种clock mesh与H-tree相结合的混合时钟树设计方法,同时通过对设计中的寄存器按照一定规则进行分组并分别布局在相同大小的网格中从而具备一定的对称性和规则性,可更好的优化H-tree结构,提高H-tree的性能从而提高了整个混合时钟树的性能。

实验表明,该混合时钟树结构可显著减少时钟树长度和时钟分支间的skew,降低OCV影响。

【关键词】clock mesh H-tree 寄存器组布局 clock skew1 引言随着芯片规模的不断增大,设计复杂度的不断提升,同种工艺下对性能追求的极限化,时钟网络的分布越来越重要。

如何减小时钟skew、降低OCV影响,对时钟树综合来说,是个严峻的挑战。

业界常用的时钟树设计方法有很多种,比如H-tree、二叉树、clock mesh、鱼骨等,其中H-tree的时钟偏斜skew小,但对设计的规则性要求严格;clock mesh的时钟树长度小、延时小、OCV影响小,但局部时钟偏斜较大。

为了充分利用这两种时钟树结构的优点,本文提出了一种混合时钟树设计方法,能有效的减小时钟偏斜skew、降低OCV影响。

2 混合时钟树结构混合时钟树结构如图1所示。

它主要由三部分组成:H-tree结构pre-mesh、clock mesh、H-tree结构local tree。

因其包含不同的时钟树结构,故称之为混合时钟树结构。

该混合时钟树先通过H-tree结构将时钟源分布到clock mesh上,clock mesh上的时钟以就近原则连接到附近的local tree起点,local tree再通过H-tree结构将时钟信号分布到每个寄存器的时钟端;同时,由于local H-tree末端驱动的寄存器布局经特殊处理后具有一定的对称性,可更好的优化H-tree的性能。

数字电路设计中的时钟树设计原理

时钟树设计原理在数字电路设计中起着至关重要的作用,它主要用于在整个芯

片中分配和传递时钟信号,保证整个系统的同步性和稳定性。

时钟信号在数字电路中被广泛应用,它决定了数据的采样时间、触发时间和稳定性,是整个系统中最重要的信号之一。

时钟树设计的主要目的是传送时钟信号到整个芯片的各个部分,并确保各个部

分同时受到相同的时钟信号,避免出现时序偏差和时序冲突。

时钟树设计需要考虑到时钟信号的频率、延迟、功耗、噪声等多方面因素,以确保整个系统的性能和稳定性。

在时钟树设计中,一般会采用层次式的结构,将时钟信号从芯片的输入端传输

到各个功能模块,并通过缓存器、分频器、中继器等组件来进行时钟信号的分配和缓存,最终保证整个系统内部各个部分的同步。

时钟树设计中需要考虑的一个重要因素是时钟分配网络的拓扑结构,不同的拓

扑结构会对时钟信号的传输速度、功耗和稳定性等方面产生影响。

常见的拓扑结构包括二叉树结构、星型结构、环状结构等,根据具体的设计需求和性能指标选择合适的拓扑结构进行时钟树设计。

此外,时钟树设计中还需要考虑时钟信号的布线与布局,以减小时钟信号在传

输过程中的延迟和功耗,提高整个系统的性能。

合理的布线和布局可以降低时钟信号的传输损耗和噪声干扰,确保时钟信号能够准确、稳定地传输到各个功能模块。

总的来说,时钟树设计原理是数字电路设计中至关重要的一环,它直接影响到

整个系统的性能和稳定性。

通过合理的时钟树设计,可以确保系统内部各个功能模块的同步运行,提高系统的可靠性和性能,是数字电路设计中不可或缺的关键步骤。

时钟树综合(1)时钟树综合学习背景时钟信号是数据传输的基准,他对于同步数字系统的功能、性能、稳定性起决定性作⽤。

时钟信号通常是整个芯⽚中有最⼤扇出、通过最长距离、以最⾼速度运⾏的信号。

时钟信号必须要保证在最差的条件下,关键的时序要求能够满⾜,否则对时钟信号的任何不当的控制都可能导致紊乱情况,将错误的数据信号索存到寄存器,从⽽导致系统功能的错误。

时钟信号怎么产⽣的时钟信号源⼀般是从晶体(⽯英晶体、陶瓷晶体)产⽣的。

IC设计时通常会使⽤晶体振荡器来提供时钟源信号。

⼀般会使⽤PLL加上晶体振荡器来给芯⽚内部电路提供倍频或相位的时钟信号。

时钟信号特征时钟的周期(频率)、时钟延迟、时钟信号的不确定性是时钟的三个主要特征要素。

时钟信号延迟时钟信号延迟(latency)⼜称为插⼊延迟(insertion delay), 包括时钟源插⼊延迟和时钟⽹络插⼊延迟。

时钟源插⼊延迟是来⾃系统到当前芯⽚(当前模块)时钟根节点(clock root pin)之间的延迟,时钟⽹络插⼊延迟是时钟树的延迟。

时钟信号不确定性时钟信号的不确定性主要是有时钟信号抖动引起的,时钟抖动是先天存在的,所以在时钟树综合的时候只能考虑起影响,⽆法消除。

时钟抖动是信号实际时间与理想时间的偏差,抖动中含有确定抖动成分和随机抖动的成分【】。

时钟信号偏差时钟信号偏差是指同⼀时钟达到该时钟域内的不同寄存器之间的时间偏差,也即是skew=max(|t i−t j|)产⽣时钟偏差的原因有多种:时钟源到各个时钟端点的路径长度不同、各个端点负载不同、在时钟⽹中插⼊的缓冲器不同等。

在什么时候做时钟树综合:如下图所⽰,通常在物理设计布局完成之后布线之前进⾏时钟树综合。

在此之前所有的寄存器时钟信号是由同⼀个时钟pin驱动的,具有相同的延时的理想时钟。

已经⽣成了gatelevel 的netlist已经有⼀个初步的版图规划,每个逻辑门包括时序器件都有⼀个具体的位置。

已经基于理想时钟完成了时序优化设计。

高性能芯片设计中的时钟树优化技术时钟树是芯片设计中至关重要的一个组成部分,它负责传输时钟信号以保证芯片的正常工作。

在高性能芯片设计中,时钟树的优化技术尤为重要,可以提高芯片的稳定性、降低功耗,并保证芯片的高性能工作。

本文将介绍高性能芯片设计中的时钟树优化技术,并探讨其在芯片设计中的应用。

一、时钟树设计的重要性时钟信号是芯片工作的基准,它控制着各个功能模块的操作时序,因此时钟树设计的合理性直接影响着芯片的性能和功耗。

在高性能芯片设计中,要实现较高的工作频率和低功耗,时钟树的设计至关重要。

一个优秀的时钟树设计应具备以下几个方面的特点:1. 低时钟抖动:时钟抖动会导致芯片工作不稳定,降低性能。

通过合理的时钟树设计,可以减少时钟抖动,提高芯片的工作稳定性和可靠性。

2. 低功耗:时钟信号在芯片中的传输需要消耗功耗,较长的时钟路径和不优化的时钟树设计将导致大量的功耗浪费。

通过优化时钟树设计,可以降低功耗,提高芯片的能效。

3. 均衡和分布平衡:时钟信号在传输过程中,应该保持均衡和分布平衡,避免信号传输的不平衡导致时钟抖动和延迟问题。

二、时钟树优化的目标在高性能芯片设计中,时钟树优化的目标是实现如下几个方面的优化:1. 降低时钟路径的长度:时钟路径越短,芯片的工作频率越高,性能越好。

2. 降低时钟路径的延时:通过合理的时钟树设计,可以降低时钟路径的延时,提高芯片的工作速度。

3. 降低时钟树的功耗:优化时钟树设计,可以减少时钟信号传输过程中的功耗损耗,提高芯片的能效。

三、时钟树优化技术1. 时钟树综合:时钟树综合是时钟树优化的一项重要技术,通过对时钟信号的分析和综合,优化时钟树的结构,减少时钟路径的长度和延时。

时钟树综合工具可以根据设计需求自动完成时钟树的综合工作,生成一个最优的时钟树结构,提高芯片的性能和功耗。

2. 缓冲器插入:在时钟路径过长或者时钟分布不均衡时,可以通过插入合适的缓冲器来优化时钟树设计。

缓冲器可以提升时钟信号的驱动能力,减少时钟路径的延时和功耗。

fpga时钟树设计原则FPGA时钟树设计原则随着科技的不断发展,FPGA(Field Programmable Gate Array)在数字电路设计中的应用越来越广泛。

而时钟树作为FPGA中最重要的组成部分之一,对于整个系统的性能和稳定性起着至关重要的作用。

本文将介绍FPGA时钟树设计的原则,以帮助读者更好地理解和应用这一关键技术。

1. 时钟树的稳定性时钟信号的稳定性对于FPGA的性能至关重要。

在时钟树设计中,应采取以下措施来确保时钟信号的稳定传递:(1)降低时钟信号的抖动:抖动是指时钟信号在传输过程中产生的不稳定性。

为了降低抖动,可以采用低抖动的时钟源,并合理布局时钟信号线路,避免与其他高干扰信号线路相交。

(2)降低时钟信号的噪声:噪声是指时钟信号中的不期望的干扰成分。

为了降低噪声,可以采用低噪声的时钟源,并在布局过程中避免与高噪声信号线路相近。

2. 时钟树的延时平衡时钟树的延时平衡对于保证时序一致性和减小时序偏差至关重要。

在时钟树设计中,应采取以下措施来保持时钟信号的延时平衡:(1)合理选择时钟树拓扑结构:时钟树的拓扑结构直接影响到时钟信号的传播延时。

一般来说,采用层次化的拓扑结构可以有效减小时钟信号传播的延时差。

(2)采用缓冲器和驱动器:缓冲器和驱动器可以用来调整时钟信号的驱动能力和传播延时,从而实现时钟信号的延时平衡。

3. 时钟树的功耗优化时钟树的功耗优化对于提高系统的能效至关重要。

在时钟树设计中,应采取以下措施来降低功耗:(1)合理选择时钟树的频率:时钟树的频率直接影响到功耗的消耗。

一般来说,较低频率的时钟信号可以降低功耗,但也会影响系统的性能。

(2)采用时钟门控技术:时钟门控技术可以根据需要对时钟信号进行开关控制,从而降低时钟信号的功耗。

4. 时钟树的布局与布线时钟树的布局与布线对于保证时钟信号的稳定传递和延时平衡至关重要。

在时钟树设计中,应采取以下措施来优化布局与布线:(1)合理布局时钟信号线路:时钟信号线路应尽量短且对称,避免与其他信号线路相交,减小互相干扰。

时钟树总结引言在现代集成电路设计中,时钟树是非常重要的组成部分。

时钟信号被用于同步电路中的各个部分,确保各个部件在正确的时间进行操作。

时钟树的设计和优化对于电路的性能和功耗具有重要的影响。

本文将总结时钟树的基本概念、设计和优化方法。

时钟树基本概念时钟树是由时钟发生器、时钟网络和时钟接收器组成的,用于传输时钟信号到整个电路的各个部分。

时钟发生器产生基准时钟信号,时钟网络将信号传输到各个时钟接收器。

时钟树的主要目标是提供一个稳定的时钟信号,使整个电路以正确定时进行操作。

时钟信号的稳定性可以通过降低时钟树的延迟、抖动和功耗来实现。

时钟树设计方法时钟树设计需要考虑以下几个因素:1. 时钟频率时钟频率是指每秒内时钟信号的周期数。

它决定了系统的工作速度和性能。

时钟频率越高,系统的运行速度越快,但也会带来更大的功耗和噪声。

2. 时钟网络拓扑时钟网络拓扑决定了时钟信号的传输路径和延迟。

常见的时钟网络拓扑包括树状结构、网状结构和环形结构。

不同的拓扑结构会对时钟信号的传输速度和功耗产生影响,选择合适的拓扑结构是时钟树设计的关键。

3. 时钟缓冲器的布局和参数选择时钟缓冲器用于放大、增强和传输时钟信号。

时钟缓冲器的布局和参数选择会直接影响时钟信号的稳定性和功耗。

合理选择时钟缓冲器的位置和参数是时钟树设计的重要一环。

4. 时钟树的功耗和抖动优化时钟树的功耗和抖动是设计过程中需要优化的指标。

功耗优化可以通过选择合适的缓冲器和优化时钟网络的结构来实现。

抖动优化可以通过减小时钟信号的传输路径和优化时钟缓冲器的参数来实现。

时钟树优化方法时钟树的优化方法主要包括以下几个方面:1. 延迟优化通过减小时钟信号的传输路径和优化时钟缓冲器的参数,可以减小时钟树的延迟。

延迟优化可以提高时钟信号的稳定性和电路的工作速度。

2. 抖动优化抖动是时钟信号波形的不稳定程度,影响时钟信号的精确性。

通过减小时钟信号的传输路径和优化时钟缓冲器的参数,可以减小时钟树的抖动。

innovus 的h tree树建立方法H-Tree树是一种用于分层存储和组织数据的树状结构。

它具有分布均匀、容易扩展和高效查找等特点,因此在许多领域都有广泛的应用,如数据库索引、图像处理和网络路由等。

下面将介绍H-Tree树的建立步骤。

1. 定义H-Tree树的结构H-Tree树是一种多叉树,每个节点有多个子节点。

每个节点包含一个键值和一个指向子节点的指针数组。

根节点是整个H-Tree树的入口,其他节点都通过指针与根节点相连。

2. 初始化H-Tree树创建一个空的树,并将根节点初始化为空。

接下来,确定树的最大深度和每个节点的最大子节点数。

这些参数将决定H-Tree树的结构和性能。

3. 插入数据将数据插入H-Tree树的过程称为插入操作。

首先,根据数据的键值找到合适的叶子节点。

如果该节点的子节点已满,则需要进行分裂操作。

分裂操作会将当前节点分裂为两个节点,并将数据插入其中一个节点。

然后,将分裂后的两个节点与当前节点的父节点连接起来。

如果分裂后的父节点也已满,则继续进行分裂操作,直到树的最大深度。

4. 删除数据H-Tree树的删除操作与插入操作相反。

首先,根据数据的键值找到对应的叶子节点。

然后,从该节点中删除数据。

如果删除后该节点的数据数量过少,则需要进行合并操作。

合并操作会将当前节点与相邻的节点合并,并将合并后的节点与父节点连接起来。

如果合并后的父节点数据数量过少,则继续进行合并操作,直到树的最小深度。

5. 查找数据H-Tree树的查找操作非常高效。

首先,根据数据的键值找到对应的叶子节点。

然后,在该节点中查找数据。

如果找到了数据,则返回数据;如果未找到,则返回空。

6. 扩展H-Tree树当H-Tree树中的数据量超过了预设的阈值时,需要进行扩展操作。

扩展操作会增加树的深度,以容纳更多的数据。

具体的扩展方法可以根据实际需求进行设计,如增加每个节点的子节点数或增加树的层数。

通过以上步骤,就可以建立一个完整的H-Tree树。

题目:【目的】掌握H‐树结构形成时钟线分布网的方法,以及用反相器链构成的驱动电路的设计。

【内容】设计一个数字系统的时钟线分布及驱动电路,时钟频率100MHz,总的负载电容200pF,分布到10mm×10mm 的芯片内。

用单层金属线,线宽2μm,不考虑线间电容和边缘电容,单位面积连线对衬底电容0.03fF/μm2, 金属线电阻0.07Ω/□,要求时钟信号的上升边和下降边不应大于1.5ns,时钟线分布网到达芯片四周的终点信号要同步,且延迟量不应大于1.8ns,MOSFET 模型参数用65nm 工艺的参数,电源电压1.2V。

【要求】给出设计思路、采用的驱动电路结构,说明MOS 管尺寸设计的考虑和设计结果,给出模拟结果以及对结果的分析讨论。

上面的图就是H树时钟分布的简图,需要注意的是里面展示的是缓冲器,是由两个反相器连接的。

具体分析延时情况时我们需要将其拆开为反相器进行分析。

由上图中反相器链的延迟时间与级数的关系,书上引出这样一段描述:可知对于x<100的情况,N最多取3;对于x在1000至10000的情况,N取5就足够了,再增大N对延迟时间的改善非常小,但是面积会急剧增加。

其中x=CL/Cin ; CL为最终的负载电容,Cin为输入电容。

在实际设计反相器链时不仅仅是追求延迟时间最小,而是对速度和面积的综合考虑进行优化,为了使得发生时钟的反转和到达负载时的反转能够相比较,经过偶数个反相器后波形相同,我们先取N=4。

所以,我们的时钟分布会像下面这幅图展示的一样。

题目中给的总的负载电容为200pF ,由图中可见我们这里将其平均分为16份,则每一份的负载电容为CL=12.5pF ,这里的CL 即为x=CL/Cin 中的CL 。

分析H 树时钟分布的延迟时间我们需要考虑的是一条反相器路径上的延迟时间即可。

反相器链的总的延迟时间为p po t NSt = (1) S 表示的是反相器链每一级反相器中MOS 管宽度比前一级增大S 倍,则有1/,/N i i L in S C C S C C x +=== (2)若知道了x ,则N=lnx/lnS ,把它带入到式1中,求导得出使反相器延时时间最小的2.7S e =≈。

一种差分结构的时钟树结构分析贾柱良,何凯,何琴(国微电子有限公司,广东深圳,518057)摘 要:本文介绍了一种全定制的差分结构的时钟树结构,采用H型的时钟树网络,时钟信号从时钟IO进入后,单端信号转化成差分时钟双端信号,经过几级差分BUFFER单元,均匀分布在整个芯片,最后再转换成单端信号提供给存储IP的时钟端口。

相比传统EDA工具生成的时钟树,有如下突出优点:功耗小,速度快,时钟偏差小。

这种差分结构的时钟树电路能够满足250MHz频率存储芯片的时序收敛要求,并且经过了实际流片验证,证明此结构是可行的。

关键词:差分时钟树;时钟偏差中图分类号:TN702文献标识码:A 文章编号:2095-8595 (2017) 04-008-004电子科学技术 URL: http// DOI: 10.16453/j.issn.2095-8595.2017.04.003A Clock Tree Struction of Differential Circuit AnalysisZhulia ng Ji a, Kai He, Qin He(S H ENZHEN S TATE MIC ROELEC T RON IC S C O.,LTD ,Shenzhen,Guangdong,518057,Chi na)Abstract: The paper introduce a kind of clock tree struction of differential circuit,using H-type clock mesh method,clock signal input IC from clock IO,transform into differential clock signals,go through several level differential buffer,distributed evenly over the whole IC,then transform into one-output terminal signal,provide to the clock terminal of memory IP.By comparison with the tradition clocktree produced by EDA,the advantages of the clock tree struction is as follows: low power,fast speed,small clock skew. The kind of clock tree struction of differential circuit can fill the timing requirements of 250MHz memory IC,and the module has been proved reliable by taping out.Key words: Clocktree of difference channel;Clock skew引言随着芯片规模的不断扩大,IC设计日益复杂化,如何在高频下满足时序,减小Skew,降低OCV影响,对时钟树设计来说,是个严峻的挑战。

时钟树综合算法时钟树综合算法是在集成电路设计中非常重要的一项技术。

它的作用是将时钟信号传输到整个电路中的各个部分,确保电路的稳定运行。

在现代集成电路中,时钟信号被用来同步各个模块之间的操作。

因为电路中的不同模块需要按照一定的顺序进行操作,所以时钟信号的传输是非常关键的。

时钟信号不仅要准确地传输到每个模块,还需要满足一些设计约束,比如时延、功耗等方面的要求。

时钟树综合算法的目标是在满足设计约束的前提下,最小化时钟信号路径的时延和功耗。

为了实现这个目标,时钟树综合算法通常包括以下几个步骤:1. 时钟树构建:首先,根据设计规格和约束,确定时钟树的拓扑结构和时钟信号的传输路径。

这个步骤中需要考虑信号的时延、功耗以及电磁干扰等因素。

2. 时钟树优化:在确定了时钟树的拓扑结构后,需要对时钟信号路径进行优化。

优化的目标是使得时钟信号的时延最小化,从而提高电路的工作频率和性能。

常用的优化技术包括缩短时钟信号路径、减少时钟缓冲器的数量等。

3. 时钟树布线:优化后的时钟树需要进行布线,将时钟信号传输到各个模块。

布线的目标是使得时钟信号的功耗尽可能小,并且满足电磁兼容性和电磁互容性的要求。

为了达到这个目标,布线时需要考虑时钟线的走向、间距、层间距、抗干扰措施等因素。

4. 时钟树验证:最后,根据设计规格和约束进行时钟树的验证。

验证的目标是确保时钟信号能够准确地传输到每个模块,并满足时延和功耗等设计要求。

验证过程需要使用专门的工具进行模拟和分析,以确保时钟树的正确性。

时钟树综合算法在集成电路设计中起着重要的作用。

它可以帮助设计工程师在设计过程中更好地管理和优化时钟信号,从而提高电路的性能和稳定性。

通过合理的时钟树设计和优化可以降低时延和功耗,提高电路的工作频率和可靠性。

同时,时钟树综合算法也需要与其他的电路设计工具和算法进行配合,共同完成电路的设计和验证。

总之,时钟树综合算法是一项非常重要的电路设计技术,它对电路的性能和稳定性具有重要影响。

时钟树综合(clocktreesynthesis)基础篇时钟树综合(clock tree synthesis)今天,小编为大家简单介绍下数字后端设计过程中非常重要的一个环节,时钟树综合(clock tree synthesis)。

很多两三年及以上的数字后端工程师,依旧停留在跑flow,工具如何build tree也是两眼一抹黑,甚至不知道如何去分析你的clock tree质量和debug clock tree 的一个状态。

因此,很有必要再把这个步骤拎出来,唠唠嗑。

1什么是时钟树综合简单概括下,时钟树综合就是指从某个clock的root点长到各个sink点的clock buffer/inverter tree。

工具试图将某个clock所属的所有sinks做到相同长度。

从概念上,我们可以得到几个要点。

1.clock的root点需要定义清楚。

这个可以通过create_clock来定义。

如果是create_generated_clock,它的master clock也是很清晰的,即知道generate clock的source latency;2.clock 的sinks要知晓。

2时钟树综合的目标1.clock skew尽量小,特别是对时钟质量要求比较高或者高频时钟;2.clock latency尽量短。

那么,为了达到以上两大目标,数字后端工程师任到重远。

首先,我们拿到一个design,需要先花点时间,理清楚clock 结构,各种mode如何切换。

同时,需要不断向前端设计人员请教design相关(后端需要知道的信息),比如哪些clock是需要同步,哪些是异步。

3时钟树质量分析可能很多工程师估计都没用过下面这个功能吧。

ICC/ICC2中这个功能还是很不错的,可以帮助工程师快速理清clock的结构和debug clock tree 质量。

特地向大家推荐下。

借助上面推荐的方法GUI操作辅助我们分析。

选中某个clock,然后查看clock的时钟树综合结果,比如clock buffer的级数,clock latency,clock的最短路径和最长路径。

题目:

【目的】掌握H‐树结构形成时钟线分布网的方法,以及用反相器链构成的驱动电路的设计。

【内容】设计一个数字系统的时钟线分布及驱动电路,时钟频率100MHz,总的负载电

容200pF,分布到10mm×10mm 的芯片内。

用单层金属线,线宽2μm,不考虑线间电容和边缘电容,单位面积连线对衬底电容0.03fF/μm2, 金属线电阻0.07Ω/□,要求时钟信号的上升边和下降边不应大于1.5ns,时钟线分布网到达芯片四周的终点信号要同步,且延迟量不应大于1.8ns,MOSFET 模型参数用65nm 工艺的参数,电源电压1.2V。

【要求】给出设计思路、采用的驱动电路结构,说明MOS 管尺寸设计的考虑和设计结果,给出模拟结果以及对结果的分析讨论。

上面的图就是H树时钟分布的简图,需要注意的是里面展示的是缓冲器,是由两个反相器连接的。

具体分析延时情况时我们需要将其拆开为反相器进行分析。

由上图中反相器链的延迟时间与级数的关系,书上引出这样一段描述:

可知对于x<100的情况,N最多取3;对于x在1000至10000的情况,N取5就足够了,再增大N对延迟时间的改善非常小,但是面积会急剧增加。

其中x=CL/Cin ; CL为最终的负载电容,Cin为输入电容。

在实际设计反相器链时不仅仅是追求延迟时间最小,而是对速度和面积的综合考虑进行优化,为了使得发生时钟的反转和到达负载时的反转能够相比较,经过偶数个反相器后波形相同,我们先取N=4。

所以,我们的时钟分布会像下面这幅图展示的一样。

题目中给的总的负载电容为200pF ,由图中可见我们这里将其平均分为16份,则每一份的负载电容为CL=12.5pF ,这里的CL 即为x=CL/Cin 中的CL 。

分析H 树时钟分布的延迟时间我们需要考虑的是一条反相器路径上的延迟时间即可。

反相器链的总的延迟时间为

p po t NSt = (1) S 表示的是反相器链每一级反相器中MOS 管宽度比前一级增大S 倍,则有

1/,/N i i L in S C C S C C x +=== (2)

若知道了x ,则N=lnx/lnS ,把它带入到式1中,求导得出使反相器延时时间最小的2.7S e =≈。

这是一个理论上的最优解,无论对于任何负载的反相器链都成立,但是需要注意的是它没有考虑反相器链的面积,这会在H 树时钟分布设计中对它进一步调整的一个主要的原因。

我们首先取S=2.7。

由上面的分析我们就可以将N=4和S=2.7带入到2式中求解出x 来,进而通过x=CL/Cin 求解出Cin 的大小 ,Cin 约为0.2352pF 。

我们首先假设Cin 全为第一级反相器栅电容,这样方便我们进行下一步的分析,对于CMOS 反相器来说,栅电容组成包括栅、氧化层、衬底沟道部分组成的栅氧化层电容,还有栅覆盖在源和漏部分的覆盖电容,但由于覆盖电容跟栅氧化层电容相比比较小,在手工计算时可以忽略。

我们根据式3求解出第一级反相器的宽度值Wn 和Wp ,其中Wp=3Wn Cin=CoxWnLn+CoxWpLp=Cox*4Wn*L (3) 我们这里利用的是65nmBSIM4的工艺参数,可以在参数中找出对应的tox 来求解Cox 的大小。

Cox=3.9*8.85e-12/1.2e-9=0.0288F.

我们在这里取用的L=65nm*2=130nm 的沟道长度,进一步求解出Wn=15.7um ,Wp=47.1um ,在这里要意识到是不是Wn 和Wp 太大了,验算四级反相器处的Wp=47.1um*2.7*2.7*2.7 =927um=0.927mm,题目中是在10mm×10mm 的芯片内分布,这样的宽度可以接受。

接下来需要建立的概念便是,传输的延迟最主要是由传输线造成的,反相器在这里起到的作用是改善传输线造成的上升和下降沿使得上升沿和下降沿延时变小,可用如下图表示

A

B

C

12

由于长距离传输线的存在,使得信号由图中的A 变到B ,又由于在其中加上反相器链驱动的原因,信号由B 变到C 。

图中1和2段的时间相加为总的延时,在本题中即为1.8ns ,图中2段的时间表示为上升延时,在本题中为1.5ns 。

在题目中利用总的延迟时间1.8ns 求解传输线的长度,进而求解出传输线的电阻和电容分布情况,这里利用传输线的集总模型,即

0.69p t RC = (4)

2

000.690.69*()*()0.69p L t RC R C WL R C L W === (5)

这里的tp 表示的是传输线的延时,带入 1.8ns 进行计算,在本题中方块电阻值为0.07Ω/□,电容C0为0.03fF/μm 2,化成标准单位,则求得L=0.0352m 。

进而求得总电阻R=1233欧,总电容为2.112pF 。

因为利用了四级的反相器链,所以我们将总电阻和总电容平均分成四份来进行分析,每一份电容和电阻都作为各自对应的那一级反相器的负载。

则R0=308.25,C0=0.528pF 。

经过一些假设的手工计算得到的初步参数表示如下 N=4

S=2.7

Wn=15.7um

Wp=47.1um

R0=308.25

C0=0.528pF

根据上边的H 树时钟分布图编辑HSpice 中的sp 文件进行仿真验证。

得到初步仿真结果表示如下

图中显示最终图形不对,对图中的结果进行分析,最大的影响是传输线的延时太大了,这并不是说明手工分析的结果出错了,因为我们进行的是最简单的集总模型分析,并且是简单的认为是平均分成四份,没有考虑到反相器MOS管中的大电阻的影响。

这总分析偏差是存在的。

那就需要我们减小传输线的长度,在考虑到10mm×10mm 的芯片大小的实际情况,

传输线的大小也不宜过小,当传输线的长度减小到0.0044m时,得到的仿真结果如下

已经接近传输延时1.8ns指标,下面进一步调整MOS管的宽度使得达到对应的指标。

我们在前面计算中一直假设反相器链的输入电容为第一级反相器的栅电容,有仿真结果可知,这种假设与实际有偏差,也即输入电容应该大于第一级反相器的栅电容,所以第一级反

相器的尺寸应该更小,修改使Wn=10um,Wp=30um,进一步仿真得到如下结果

此时对应的时钟信号的上升边和下降边为1.62ns-0.62ns=1ns,总的延迟时间为1.8ns,达到设计要求。

最终的设计指标为

反相器链级数N=4

后一级反相器尺寸是前一级反相器尺寸的S=2.7倍

第一级反相器中的NMOS的宽度Wn=10um

第一级反相器中的NMOS的宽度Wp=30um

第一级反相器中MOS管的沟道长度L=130nm

传输线的总长度L=0.0044m

需要注意的地方

需要注意的是这里并不是唯一的结果。

H树时钟树设计是一种工程设计,而并不是一种科学精确计算的求解过程,这就意味着它会有很多组解可以达到设计结果。

但是需要考虑实际的情况;

需要把所有参数的单位统一,以统一为标准单位为最佳;

手工计算只是一种辅助解决问题的方法,不能迷信手工计算就可以一下子就求出很好的设计,同时Hspice也不仅仅是一个用来看最终仿真结果的出图工具,而应该是被用来分析和修

改设计的帮手,Hspice大展身手的地方应该是分析过程中,而并不是最后;。