第四章 时序逻辑电路

- 格式:ppt

- 大小:697.50 KB

- 文档页数:46

数字电子技术基础第四章习题及参考答案第四章习题1.分析图4-1中所示的同步时序逻辑电路,要求:(1)写出驱动方程、输出方程、状态方程;(2)画出状态转换图,并说出电路功能。

CPY图4-12.由D触发器组成的时序逻辑电路如图4-2所示,在图中所示的CP脉冲及D作用下,画出Q0、Q1的波形。

设触发器的初始状态为Q0=0,Q1=0。

D图4-23.试分析图4-3所示同步时序逻辑电路,要求:写出驱动方程、状态方程,列出状态真值表,画出状态图。

CP图4-34.一同步时序逻辑电路如图4-4所示,设各触发器的起始状态均为0态。

(1)作出电路的状态转换表;(2)画出电路的状态图;(3)画出CP作用下Q0、Q1、Q2的波形图;(4)说明电路的逻辑功能。

图4-45.试画出如图4-5所示电路在CP波形作用下的输出波形Q1及Q0,并说明它的功能(假设初态Q0Q1=00)。

CPQ1Q0CP图4-56.分析如图4-6所示同步时序逻辑电路的功能,写出分析过程。

Y图4-67.分析图4-7所示电路的逻辑功能。

(1)写出驱动方程、状态方程;(2)作出状态转移表、状态转移图;(3)指出电路的逻辑功能,并说明能否自启动;(4)画出在时钟作用下的各触发器输出波形。

CP图4-78.时序逻辑电路分析。

电路如图4-8所示:(1)列出方程式、状态表;(2)画出状态图、时序图。

并说明电路的功能。

1C图4-89.试分析图4-9下面时序逻辑电路:(1)写出该电路的驱动方程,状态方程和输出方程;(2)画出Q1Q0的状态转换图;(3)根据状态图分析其功能;1B图4-910.分析如图4-10所示同步时序逻辑电路,具体要求:写出它的激励方程组、状态方程组和输出方程,画出状态图并描述功能。

1Z图4-1011.已知某同步时序逻辑电路如图4-11所示,试:(1)分析电路的状态转移图,并要求给出详细分析过程。

(2)电路逻辑功能是什么,能否自启动?(3)若计数脉冲f CP频率等于700Hz,从Q2端输出时的脉冲频率是多少?CP图4-1112.分析图4-12所示同步时序逻辑电路,写出它的激励方程组、状态方程组,并画出状态转换图。

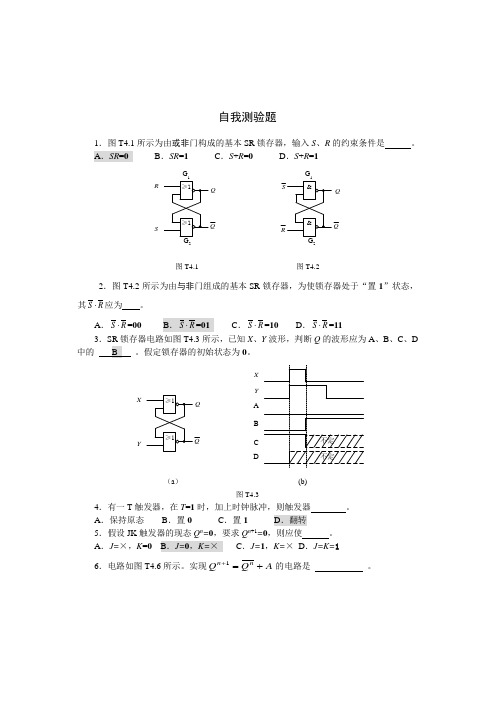

自我测验题1.图T4.1所示为由或非门构成的基本SR锁存器,输入S、R的约束条件是。

A.SR=0B.SR=1C.S+R=0D.S+R=1QG22QRS图T4.1 图T4.22.图T4.2所示为由与非门组成的基本SR锁存器,为使锁存器处于“置1”状态,其RS⋅应为。

A.RS⋅=00C.RS⋅=10D.RS⋅=113.SR锁存器电路如图T4.3所示,已知X、Y波形,判断Q的波形应为A、B、C、D 中的。

假定锁存器的初始状态为0。

XYXYABCD不定不定(a)(b)图T4.34.有一T触发器,在T=1时,加上时钟脉冲,则触发器。

A.保持原态B.置0C.置1D.翻转5.假设JK触发器的现态Q n=0,要求Q n+1=0,则应使。

A.J=×,K=0B.J=0,K=×C.J=1,K=×D.J=K=16.电路如图T4.6所示。

实现AQQ nn+=+1的电路是。

4 时序逻辑电路习题解答63A AA AA .B .C .D .图T4.67.电路如图T4.7所示。

实现n n Q Q =+1的电路是 。

CPCPCPA .B .C .D .图T4.78.电路如图T4.8所示。

输出端Q 所得波形的频率为CP 信号二分频的电路为 。

1A . B . C .D .图T4.89.将D 触发器改造成T 所示电路中的虚线框内应是 。

TQ图T4.9A .或非门B .与非门C .异或门D .同或门 10.触发器异步输入端的作用是 。

A .清0 B .置1 C .接收时钟脉冲 D .清0或置1 11.米里型时序逻辑电路的输出是 。

A .只与输入有关B .只与电路当前状态有关C .与输入和电路当前状态均有关D .与输入和电路当前状态均无关12.摩尔型时序逻辑电路的输出是 。

A .只与输入有关 B .只与电路当前状态有关C .与输入和电路当前状态均有关D .与输入和电路当前状态均无关13.用n 只触发器组成计数器,其最大计数模为 。