基于STM32及AD7606的16通道同步数据采集系统设计

- 格式:doc

- 大小:801.00 KB

- 文档页数:4

16通道声发射同步数据采集中的电路设计为了实现16通道声发射同步数据采集,需要设计一套电路系统。

以下是该电路系统的详细设计方案。

1. 电路整体设计方案整体设计方案是将16个声发射通道连接到一块数据采集板上。

每个声发射通道都有一个独立的放大电路和数字采集电路。

这些电路通过一个中央控制单元进行同步。

2. 放大电路设计放大电路用于将声音信号放大至适合数字采集的幅度范围。

采用差动放大器进行放大,可以有效抑制共模干扰。

每个声发射通道的放大电路都可以独立调节增益。

3. 数字采集电路设计数字采集电路用于将放大的声音信号转换为数字信号。

采用AD转换器将模拟信号转换为数字信号,并利用FPGA进行数据处理和存储。

每个声发射通道都有一个独立的AD转换器和FPGA。

4. 同步控制电路设计同步控制电路用于实现16通道声发射的同步。

中央控制单元通过同步信号发给每个声发射通道,使得它们同时开始发射声音,并控制各个通道的数据采集和存储。

5. 电源电路设计电源电路提供工作所需的各种电压。

采用稳压电源设计,保证电路工作的稳定性和可靠性。

6. PCB设计根据以上电路设计方案进行PCB设计,将各个电路和元件布局在一块PCB板上,并进行丝印、焊接等工艺处理。

7. 系统调试和测试完成PCB设计后,进行系统调试和测试。

首先进行各个电路的功能测试和性能测试,如放大电路的增益调节、AD转换器的精度测试等。

然后进行整个16通道声发射同步数据采集系统的综合测试。

8. 优化和改进在测试过程中,根据实际情况对电路系统进行优化和改进。

可以针对放大电路的增益范围进行调整,或者对AD转换器的采样频率进行优化。

16通道声发射同步数据采集中的电路设计16通道声发射同步数据采集是一种用于采集多个声源信号并实现同步数据传输的技术。

在这种技术中,多个声源信号将被同时采集并用于数据传输,这就需要一个稳定可靠的电路设计来实现这一功能。

本文将介绍16通道声发射同步数据采集中的电路设计,包括硬件和软件部分。

一、硬件设计1. 信号输入在16通道声发射同步数据采集中,首先需要设计一个能够接收多个声源信号的信号输入电路。

这个电路一般会使用16个输入通道,每个通道都会有一个专门的接收电路。

这些接收电路可以是放大器、滤波器等,用来增强和净化声源信号。

2. 数据转换和传输接收到声源信号后,需要将这些信号进行数字化处理,然后传输给输入输出接口,用于后续处理。

在这个过程中,通常会使用模数转换器(ADC)来完成模拟信号到数字信号的转换,然后通过串行通信接口(SPI)、并行接口等方式将数据传输给主控制器。

3. 主控制器主控制器是整个系统的核心部分,它将接收到的数字化声源信号进行处理和分析,并将这些数据传输给外部设备。

在16通道声发射同步数据采集中,主控制器一般会选用高性能的微处理器或者数字信号处理器(DSP)。

4. 时钟同步为了实现数据的同步采集,需要设计一个时钟同步电路,可以让所有通道的数据采集动作在同一时刻进行。

这需要使用精准的时钟电路,通过外部时钟信号或者自身的时钟生成电路来实现。

5. 供电管理在整个系统中,需要设计一个供电管理电路,用于为各个模块提供稳定的电源。

这个电路一般包括稳压器、滤波器等,用于消除功率噪声和提供稳定的电压输出。

1. 数据处理在16通道声发射同步数据采集中,需要设计一套完善的数据处理算法,用于处理和分析接收到的声源信号。

这个算法一般会包括信号滤波、功率谱分析、时域分析等,用于获取声源信号的各种特征。

接收到的数据需要进行存储和传输,一般会设计一个数据存储和传输模块。

这个模块一般会使用固态存储器,如SD卡、EEPROM等,用于存储采集到的数据。

16通道声发射同步数据采集中的电路设计1.引言随着数字信号处理技术的不断发展,以及数字音频处理器在音频处理方面的应用,越来越多的声发射同步数据采集系统被应用于各种领域,如语音识别、音频处理、通信系统等。

在这些应用中,数据采集电路的设计是至关重要的,其性能直接影响整个系统的性能。

本文将介绍一种用于16通道声发射同步数据采集系统的电路设计,该设计具有高精度、高灵敏度和低功耗的特点。

本文还将对该电路设计的原理进行详细的阐述,并对其性能进行评估。

2.系统需求1) 高灵敏度:系统需要能够精准地采集声音信号,并将其转换为数字信号,因此采集电路需要具有高灵敏度,能够捕捉到细微的声音信号。

3) 低功耗:在移动设备等资源受限的环境下,系统需要尽可能降低功耗,延长设备的使用时间。

3.电路设计原理为了满足以上需求,本设计采用了一种基于ΔΣ调制的数据采集电路。

ΔΣ调制是一种高精度、高灵敏度的模数转换技术,它通过过取样和高速数字滤波的方法,将模拟信号转换为数字信号,并在转换过程中消除了一些噪声。

具体来说,ΔΣ调制电路由前置放大器、ΔΣ调制器和数字滤波器组成。

前置放大器负责放大声音信号,并将其送入ΔΣ调制器。

ΔΣ调制器将放大后的信号进行过取样,并使用高速数字滤波器将其转换为数字信号。

数字信号经过解调器进行解调,并送入处理器进行后续处理。

为了实现16通道声发射同步数据采集系统,需要设计16路ΔΣ调制电路,并将其并联。

每路ΔΣ调制电路均由前置放大器、ΔΣ调制器和数字滤波器组成,其中数字滤波器可以采用FIR滤波器或IIR滤波器。

在实际设计中,可以采用集成电路芯片或FPGA实现16路ΔΣ调制电路,并通过串并转换器将16路数字信号并联输出。

如图1所示为16通道声发射同步数据采集系统的电路设计示意图。

5.性能评估为了评估该电路设计的性能,可以从以下几个方面进行评估:1) 灵敏度:通过测量电路的信噪比和失真率等参数,评估其对声音信号的灵敏度。

16通道声发射同步数据采集中的电路设计1. 引言1.1 研究背景16通道声发射同步数据采集系统是一种广泛应用于实时数据采集与处理领域的重要设备。

随着科学技术的不断发展和进步,人们对于声发射数据采集系统的要求也越来越高,尤其是在实时性、准确性和稳定性方面的需求日益增加。

目前市面上的声发射数据采集系统在16通道同步数据采集方面存在着诸多问题,如数据丢失、时序不同步等。

研究16通道声发射同步数据采集中的电路设计成为当前科研工作者关注的焦点之一。

通过对该领域的深入研究和实验,我们可以寻找到更加准确、稳定和高效的电路设计方案,从而提高系统的性能表现和数据采集的准确性。

这不仅对于声发射数据采集系统的应用具有重要意义,也对于推动相关技术的发展和实现科学研究具有积极的推动作用。

1.2 研究目的研究目的是为了设计一种适用于16通道声发射同步数据采集的电路,实现高效稳定的数据采集功能。

通过研究不同的电路设计原理和硬件设计模块,我们旨在提高数据采集的精度和速度,以满足各种实时数据采集需求。

通过电路测试方法和性能分析,我们可以评估所设计电路的稳定性和准确性,为进一步的优化方案提供依据。

研究的最终目的是为了实现对16通道声发射同步数据采集过程的全面控制和监测,以提高数据采集的效率和可靠性,并为相关领域的研究和应用提供支持。

通过本研究,我们希望能够为声发射数据采集领域的技术发展和应用提供新的思路和方法,促进相关领域的进步和发展。

1.3 研究意义在当今数字时代,数据采集和信号处理技术得到了广泛的应用。

16通道声发射同步数据采集中的电路设计是一项重要的研究课题,对于提高数据采集的精度和效率有着重要的意义。

通过对16通道声发射同步数据采集电路的设计研究,可以提高数据采集系统的稳定性和可靠性。

在实际应用中,数据采集系统需要在复杂的环境下工作,如电磁干扰、温度变化等,因此需要设计出具有良好抗干扰能力的电路,以确保数据的准确性和可靠性。

基于STM32及AD7606的16通道同步数据采集系统设计摘要: 介绍了基于STM32及AD7606的同步数据采集系统的软硬件设计。

主控芯片采用基于ARM Cortex-M4内核的STM32F407IGT6,实现对AD 采集数据的实时计算并通过以太网络进行数据传输。

A7606为16位、8通道同步采样模数数据采集系统[],利用两片AD7606,可以实现对16路通道的实时同步采样。

经过测试,该系统可以实现较高精度的实时数据采集。

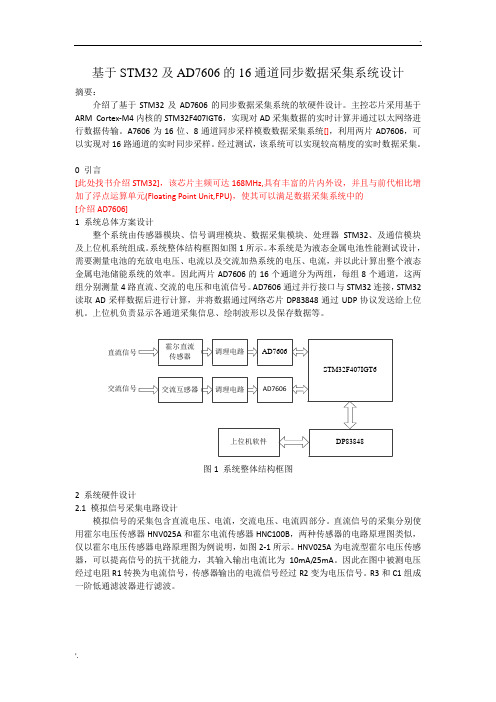

0 引言[此处找书介绍STM32],该芯片主频可达168MHz,具有丰富的片内外设,并且与前代相比增加了浮点运算单元(Floating Point Unit,FPU),使其可以满足数据采集系统中的 [介绍AD7606]1 系统总体方案设计整个系统由传感器模块、信号调理模块、数据采集模块、处理器STM32、及通信模块及上位机系统组成。

系统整体结构框图如图1所示。

本系统是为液态金属电池性能测试设计,需要测量电池的充放电电压、电流以及交流加热系统的电压、电流,并以此计算出整个液态金属电池储能系统的效率。

因此两片AD7606的16个通道分为两组,每组8个通道,这两组分别测量4路直流、交流的电压和电流信号。

AD7606通过并行接口与STM32连接,STM32读取AD 采样数据后进行计算,并将数据通过网络芯片DP83848通过UDP 协议发送给上位机。

上位机负责显示各通道采集信息、绘制波形以及保存数据等。

STM32F407IGT6霍尔直流传感器上位机软件DP83848直流信号交流信号交流互感器调理电路调理电路AD7606AD7606图1 系统整体结构框图2 系统硬件设计2.1 模拟信号采集电路设计 模拟信号的采集包含直流电压、电流,交流电压、电流四部分。

直流信号的采集分别使用霍尔电压传感器HNV025A 和霍尔电流传感器HNC100B ,两种传感器的电路原理图类似,仅以霍尔电压传感器电路原理图为例说明,如图2-1所示。

16通道声发射同步数据采集中的电路设计【摘要】本文主要介绍了在16通道声发射同步数据采集中的电路设计。

在从研究背景、研究意义和研究目的三个方面对该主题做了详细介绍。

在分别从硬件设计、信号处理设计、同步数据采集设计、电路调试设计和性能评估设计五个方面展开讨论。

最后在总结了设计的优点,分析了存在的问题,并展望了未来的发展方向。

通过本文可以更加深入地了解16通道声发射同步数据采集中电路设计的相关内容,为相关领域的研究和实践提供参考和指导。

【关键词】16通道声发射、同步数据采集、电路设计、硬件设计、信号处理设计、同步数据采集设计、电路调试设计、性能评估设计、设计优点、存在问题、未来展望。

1. 引言1.1 研究背景在现代科技的发展中,数据采集技术在各个领域都起着非常重要的作用。

特别是在声发射领域,精准的数据采集对于声音信号的处理和分析至关重要。

而在大规模数据采集系统中,如何保证多通道数据的同步采集是一个具有挑战性的问题。

对于16通道声发射同步数据采集中的电路设计进行深入研究,对于提高数据采集的精准度和可靠性具有非常重要的意义。

随着科技的不断发展,现有的数据采集系统也在不断更新换代。

研究16通道声发射同步数据采集中的电路设计,对于推动数据采集技术的进步,提高声发射系统的性能和稳定性具有重要意义。

通过深入研究硬件设计、信号处理设计、同步数据采集设计、电路调试设计以及性能评估设计等方面,可以更好地了解该领域的最新发展动态,为未来的数据采集系统的设计和优化提供重要参考。

1.2 研究意义16通道声发射同步数据采集是当今数字信号处理领域的热点问题之一,其研究意义主要体现在以下几个方面:通过对16通道声发射同步数据采集中的电路设计进行深入研究可以有效提高声音数据采集的精确度和准确性,为后续的信号处理和分析提供可靠的数据支撑。

这对于语音识别、环境监测等领域的研究具有非常重要的意义。

研究16通道声发射同步数据采集中的电路设计可以促进数字信号处理技术的发展和应用。

16通道声发射同步数据采集中的电路设计随着现代科技的不断发展,音频采集技术已经越来越成熟。

在各种音源采集的应用中,多通道声发射同步数据采集系统的应用已经越来越广泛。

本文将介绍一种16通道声发射同步数据采集系统的电路设计。

1. 总体方案设计该系统的总体方案设计采用FPGA(现场可编程门阵列)+DSP(数字信号处理器)的方案,具体的实现方式是:将模拟信号经过模拟前置放大、低通滤波后,通过ADC(模数转换器)转换成数字信号,然后通过FPGA进行原始数据采集和处理,再通过DSP对数字信号进行滤波、降噪、增益等处理,最终输出符合要求的数字信号。

2. 模拟前置放大电路设计模拟前置放大电路是将传感器采集到的微弱模拟信号进行尽可能的放大,以便使ADC能够检测到信号。

本设计采用了以下方案:1)在每个通道的输入端加入差动电路,以增加信号的可靠性,降低杂音水平。

2)采用精密电压参考源来保证输入信号稳定。

3)差分放大器的设计,可实现输入端电阻匹配使得信号传输更可靠。

4)放大倍数实现以左右声道输入电压偏差为目标。

3. 数字电路设计数字电路的设计主要任务是实现模拟信号转换成数字信号,并对数字信号进行处理。

本设计采用了以下方案:1)使用16位ADC进行数字化采集,以便能够保证数据的高精度采集。

2)将采集到的数据通过FPGA获取原始数据,并进行处理。

3)为了保证系统的高稳定性,采用了时钟同步的方式无缝转换。

DSP电路的主要设计任务是对数字信号进行滤波、降噪、增益等处理,在此过程中,需要进行系统参数调优等工作。

本设计采用了以下方案:1)采用高性价比的TMS320VC5502PGE DSP,处理速度和精度极高。

2)进行滤波、降噪、增益等数字信号处理,使用滤波器等数字电路,实现对数字信号的处理。

3)通过SPI(串行外设接口)接口将数据传输到主控芯片中进行处理。

结论以上就是16通道声发射同步数据采集中的电路设计。

该系统通过FPGA+DSP方案,可实现对模拟信号进行采样转换,数字信号处理,使其成为符合要求的数据。

电路笔记CN-0148连接/参考器件8通道DAS ,内置16位、双极性、同步采样ADCAD7606利用ADI 公司产品进行电路设计Rev.0“Circuits from the Lab” from Analog Devices have been designed and built by Analog Devices engineers. Standard engineering practices have been employed in the design and construction of each circuit, and their function and performance have been tested and verified in a lab environment at room temperature. However, you are solely responsible for testing the circuit and determining its suitability and applicability for your use and application. Accordingly, in no event shall Analog Devices be liable for direct, indirect, special, incidental, consequential or One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781.329.4700 Fax: 781.461.3113 ©2010 Analog Devices, Inc. All rights reserved. AD7606-66通道DAS ,内置16位、双极性、同步采样ADC放心运用这些配套产品迅速完成设计。

16通道声发射同步数据采集中的电路设计引言:随着科学技术的不断发展,声学研究在工业、医学、通信等领域中扮演着重要的角色。

在某些应用场景下,需要同时采集多个声音信号,并对其进行分析和处理。

本文将介绍一种16通道声发射同步数据采集系统的电路设计。

设计方案:我们需要设计一个16通道的声发射电路。

声发射电路由麦克风和放大电路组成,其中麦克风负责将声音信号转化为电信号,而放大电路则负责将微弱的电信号放大至合适的幅度。

每个通道的声发射电路都是相互独立的,这样可以保证不同通道间的信号不会相互干扰。

为了实现数据的同步采集,我们需要设计一个时钟同步电路。

时钟同步电路通过将时钟信号分发给各个通道的声发射电路,保证它们在同一个时刻开始采集数据。

时钟同步电路还需要收集各个通道的数据,并将其发送给数据处理模块。

为了保证数据的稳定性和准确性,我们还需要设计一个采样电路。

采样电路负责将连续的模拟信号转换为离散的数字信号。

在本设计中,我们可以使用模数转换器(ADC)来完成这一转换过程。

每个通道都需要一个独立的ADC,以确保数据的独立采集。

我们还需要设计一个数据处理模块。

数据处理模块负责接收来自各个通道的数据,并进行分析和处理。

在本设计中,我们可以使用嵌入式处理器或者FPGA芯片来实现数据处理功能。

数据处理模块还可以与其他设备进行通信,以完成更复杂的应用,比如将数据发送给计算机进行进一步处理或存储。

结论:本文介绍了16通道声发射同步数据采集系统的电路设计。

通过设计声发射电路、时钟同步电路、采样电路和数据处理模块,我们可以实现同时采集多个声音信号的功能。

这种系统可以应用于各种领域,比如语音识别、声音信号处理等。

通过不断的技术改进和创新,我们可以进一步提高数据采集系统的性能和功能,以满足不同应用场景的需求。

第34卷第1期2020年1月兰州文理学院学报(自然科学版)J o u r n a l o fL a n z h o uU n i v e r s i t y ofA r t s a n dS c i e n c e (N a t u r a l S c i e n c e s )V o l .34N o .1J a n .2020收稿日期:2019G09G25基金项目:安徽省教育厅自然科学研究重点项目(K J 2019A 0980);安徽省质量工程项目(2016c k j h 232);2018年度校级精品资源共享课程项目 F P G A 应用技术 ;安徽省教育厅自然科学研究重点项目(K J 2018A 0699)作者简介:杨会伟(1982G),男,河南南阳人,副教授,硕士,研究方向:嵌入式仪器仪表和数字信号处理.E Gm a i l:150496837@q q.c o m ㊀㊀文章编号:2095G6991(2020)01G0062G05十六通道高精度同步数据采集系统设计杨会伟,马书香,周先飞(芜湖职业技术学院信息工程学院,安徽芜湖241000)摘要:为了对探测对象进行多个探测点同步探测,实时精确反应探测对象某时刻的真实情况,提出了一种16通道高精度同步数据采集系统,系统利用可编程F P G A 作为控制单元,统一控制两片A D 7606的C O N S T A B ㊁C S N 使能以及RD 读操作,通过2个并行的任务执行将两片A D 7606的8通道数据同步采集到两个F I F O 阵列中,最后通过两个F I F O 的乒乓操作将数据交替转换成U S B 格式数据传送到P C 机,利用上位机软件进行存储和显示.实验结果表明:系统能够实现16通道数据的同步采集和显示,采样速率为200K S P S ,可采样电压量程为-10~+10V.关键词:高精度;同步;数据采集;时序控制中图分类号:T P 391㊀㊀㊀文献标志码:A0㊀引言信息化㊁现代化的快速发展使数据采集作用越来越重要,数据采集的采样率㊁采样精度㊁实时性㊁丰富性越来越高.多通道高精度同步数据采集系统可完成多个探测单元数据的同步采集,同步获得丰富的数据信息,提高数据分析的准确性,实时精确反映探测对象某时刻的真实情况,广泛应用于地质勘探㊁环境监测㊁电力控制系统等领域[1G3].当前基于不同控制器的数据采集系统方案也很多,比如嵌入式微处理器㊁嵌入式微控制器㊁虚拟仪器等,每种处理器都有各自的优缺点,都能够构建完整的数据采集系统,但对于大多数单核处理器来说,处理器在某一时刻只能处理一个任务,且受到主频的限制,在实现多通道数据采集时通常无法实现高精度同步.F P G A 在时序控制上优势明显,能够实现多任务并行执行,外部引脚资源丰富,且内部有大量的I P 核资源,可扩展性强,在实现多通道高精度同步采集时能够充分体现出优势.利用F P G A 和多片A D 7606构建一个16位精度多通道可扩展同步数据采集系统具有一定的应用价值[4G7].1㊀高精度多通道同步数据采集系统方案㊀㊀高精度多通道同步数据采集系统总体结构如图1所示.整个系统包括:F P G A 控制器作为系统主控单元,A D 7606前端信号采集转换单元㊁F T 2232_U S B 接口数据传输模块㊁上位机数据处理和存储软件组成.前端利用两片A D 7606在F P G A 的控制下实现16位精度㊁16通道模拟信号的同步A D转换,在下次数据采集之前,通过F P G A 内部的A D 7606控制程序模块分别将转换后的数据采集到内部两个16∗8F I F O 中进行数据缓存;再通过F P G A 内部的F I F O 乒乓访问控制模块程序将F I F O 数据交替采集到F T 2232_U S B 控制模块,实现F I F O 数据接口到U S B 数据接口的转换,最后通过F T 2232_U S B 接口将数据传输到上位机,通过上位机软件对采集数据进行存储和处理.2㊀高精度多通道同步数据采集系统设计2.1㊀硬件电路设计系统采用两片A D 7606与F P G A 进行连接,图1㊀高精度多通道同步数据采集系统框图系统主要引脚电路设计包括:①每片A D7606都采用正常工作方式,将它们的#S T B Y引脚连在一起,接上拉电阻到V C C;②O S2~O S0引脚用来控制A D7606内部数字一阶s i n c滤波器的过采样倍率,为了达到系统的采样速率,将O S2~ O S0设置为000,-10~+10V量程的S N R为90d B,3d B带宽22k H z,采样速率可达200k H z.③将F P G A的一个G P I O口与A D7606的R A N G E引脚相连,通过F P G A控制该引脚的高/低电平来设置每片A D7606外部采样输入模拟电压量程;将P A R#/S E R/B Y T E引脚接地输入低电平,使得每片A D7606采用平行接口;④为了实现双A D7606构成的16通道数据高精度同步采样,分别将每片A D7606的C O N V S T A和C O N V S T B连在一起,实现多通道同时采集;⑤将每片A D7606的16位平行数据输出(D B0~ D B15)分别与F P G A引脚相连,实现数据的同步输出;⑥两片A D7606的采样使能信号#C S和读数据触发信号R D/C L K由F P G A统一控制,实现两片A D7606真正的同步采样.⑦用一个外部基准电压源A D S421驱动2片A D7606器件的R E F I N/R E F O U T引脚,提供基准电压为2 5V.另外,每片A D7606的R E F I N/R E F O U T引脚连接100n F陶瓷去耦电容[8G9].如图2所示.2.2㊀系统数字逻辑控制时序设计F PG A作为高精度多通道同步数据采集系统的控制核心,主要实现的功能包括:A D7606驱动控制模块㊁双F I F O数据缓存㊁F T2232_U S B转换控制模块.2.2.1㊀C O N V S T A B转换时序㊀首先上电后提供上升沿复位信号R E S E T进行复位,初始化设图2㊀硬件连接图置A D7606的工作模式:设置O S0~O S2=3ᶄb000,R A N G E=1,关闭过采样,设置每片A D7606最高采样频率支持200K,-10~+10V 量程;设置2片A D7606的P A R#/S E R/B Y T E (P I N6)㊁D B15(P I N33)为0,选择16位并行接口模式.为了实现2片A D7606所有16通道同步采样,将2片A D7606的C O N V S T A和C O N V S T B 连在一起,统一进行控制,施加一个转换开始信号;数据的读取包括转换之后读取和转换期间读取两种,为了实现更快的吞吐率,两片A D7606都采用转换期间读取数据.A D7606所有通道同步采样控制时序如图3所示.其中,t1为C O N V S T A B高电平到B U S Y高电平的时间间隔,最大值为40n s;t2为C O N VGS T A B的低电平脉冲,最短时间为25n s;t3为C O N V S T A B的高电平脉冲,最短为25n s;t C Y C L E 为吞吐率的倒数,并行模式转换期间读取时间; t C O N V为转换时间,介于3.45μs与4.15μs之间,典型应用值为4μs;t4为复位信号R S T低电平到C O N V S T A B高电平之间的最短延迟时间,最小36第1期杨会伟等:十六通道高精度同步数据采集系统设计图3㊀C O N V S T A B转换时序图值为25n s;t5是C S N下降沿与B U S Y下降沿之间的时间设置,没有特殊要求;t R E S E T为复位信号高电平脉冲宽度,最短复位时间为50n s[10].根据时序图,利用V e r i l o g语言设计A D7606的C O N V S T A B转换时序,首先在系统上电后利用外部的复位按钮产生复位信号,该复位信号输出后经过处理产生一个约50n s的高电平脉冲复位信号,发送至A D7606复位引脚进行复位操作.在复位信号的高电平有效时,初始化产生C O NGS T A B的分频计数器为0,A D7606采用200K S P S的采样频率,C O N S T A B的周期为1s/200K=5μs,已知外部时钟为50MH z,分频计数器大小为50∗106/1/0.000005=500.复位结束后,利用复位信号的下降沿作为起点,以50MH z时钟上升沿为触发条件,开始对C O N S T A B分频计数器进行计数,计数范围为0~500,参照时序图和数据手册,设定计数器前10个计数状态下C O N S T A B为低电平,其余11~500计数状态下C O N S T A B为高电平.在C O N S T A B由低电平转换到高电平后,A D7606产生输出高电平B U S Y 信号并开始转换,大约4μs后转换结束,B U S Y 信号由高电平跳变为低电平,B U S Y信号的下降沿表明当前转换数据已经锁存到输出数据寄存器中,B U S Y低电平稳定后就可以读取本次转换数据.为了便于实现并保证当前读取数据为最新转换数据,两片A D7606都采用转换后读取数据的方式,在B U S Y信号高电平期间,产生一定时间的低电平采样使能信号C S N,开始读取上次数据,在B U S Y下降沿到来前,任何在B U S Y高电平状态数据的读取必须都要完成,所以在设计时, C S N上升沿比B U S Y信号上升沿提前一段时间[10].2.2.2㊀并行数据读取控制㊀在设计好C O N VGS T A B转换时序和采样使能信号C S N后,启动多通道并行数据读取,将上次转换数据读取至相应的F I F O中.两片A D7606并行多通道数据读取时序如图4所示.其中,t6为采样使能信号C S N有效到读使图4㊀并行数据读取时序能信号R D的有效时间间隔,没有特殊要求,可根据C S N下降延为基准产生R D有效低电平;t7为读使能信号R D读取一个通道数据周期中低电平脉冲宽度,最低为21n s;t8为读使能信号R D读取一个通道数据周期中高电平脉冲宽度,最短时间为15n s;t9为R D下降沿后的数据访问时间,最大值为21n s;t10为C S N到R D保持时间,没有特殊要求,保证在一个C S N的低电平时间内有8个周期的R D信号,以读取V1~V88个通道的数据,两片A D7606共用同一个C S N和R D,以实46㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀兰州文理学院学报(自然科学版)㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀第34卷现16通道同步采样.根据时序图,利用V e r i l o g语言设计两片A D7606的16通道数据的读取功能.首先,建立16个深度为128㊁宽度为16的F I F O数组阵列,分别用于存放16通道采样数据,为每个F I F O指定读写地址.在复位信号高电平有效时,清空各个F I F O,F I F O满状态标志位设置为空状态,建立两个并行的过程块,分别用于完成两片A D7606各个通道的数据采集.针对每个数据采集过程,利用状态机控制实现8个通道数据采样到F I F O数组中,执行流程为:(1)进入空闲状态,在空闲状态下等待B U S Y信号高电平到来,当获得B U S Y信号为高电平时,进入A D转换,B U S Y等信号一直保持高电平.(2)当检测到B U S Y信号恢复低电平后,说明A D转换完成,数据已经锁存到输出寄存器中,开始进入A D76068个通道数据顺序读取状态,在B U S Y信号下降沿的触发下设置C S N 为低电平,该低电平一直保持到8个通道数据读取结束为止.在C S N低电平期间,参照图4中t7和t8,设计产生8个R D周期性脉冲信号.A D7606的8个R D脉冲信号从通道1到通道8顺序读取数据,并将数据依次存入到相应的F I F O数组中,在读取期间同时检测B U S Y状态,在B U S Y下一个上升沿到来之前完成8通道数据读取工作.在第8个通道数据读完后,设置F I F O满状态标志为满状态,以提示可以将F I F O 数据取出传送至其他模块,另一片A D7606的数据读取是按照同样设计同步进行的,最终完成16通道数据的同步采样.将16个通道数据全部采集到F I F O数组后,通过判断F I F O标志为满状态,开始将16个F I F O数组数据依次传送至F T2232_U S B模块,通过U S B接口传送至上位机进行显示和保存.3㊀上位机数据采集与测试利用F T2232_U S B模块的F I F O转U S B功能,实现将16个通道16位宽度F I F O数据依次转换成U S B串口数据并传输至上位机,U S B串口数据通信格式为:帧头+多通道数据;2个字节为1个数据,低字节在前,16通道数据的帧头定义为0x5a10.F T2232H为F T D I公司的2通道高速U S B 2.0芯片,F T D I提供了F T2232H开发所需的所有驱动和多种语言上位机示例,无需编写U S B底层驱动,F T官方已提供了D L L,用户只需调用A P I即可.安装F T2232H驱动程序,在V B.n e t 开发环境中利用V B语言调用F T提供的D L L,进行U S B接口数据采集和显示,采集结果如图5所示.测试结果表明:当动态改变外部通道采样电压,16个通道采样数据会立刻改变,该系统能够完成16通道数据的实时同步采集.图5㊀数据采集界面4㊀结束语本文提出了一种16通道高精度同步数据采集系统,系统分辨率16位㊁16通道,采样率可达200K S P S;可采样电压量程为-10~+10V.该系统利用可编程器件F P G A作为主控制器,便于56第1期杨会伟等:十六通道高精度同步数据采集系统设计系统功能灵活升级和优化,采用多任务并行执行和V e r i l o g并行硬件语言编程,可提高多通道同步采样精度,利用两个F I F O阵列的乒乓操作便于实现16通道数据转换为U S B上位机数据采集,提高系统采集效率.参考文献:[1]阳继军.基于G P S授时的地震采集系统同步系统设计[J].石油仪器,2009,23(1):82G85.[2]邱桂芬.高速多通道数据采集系统的时钟同步设计[J].舰船电子对抗,2013,36(1):93G96.[3]刘小林,范育兵,罗春晖.基于F P G A的多通道数据采集系统设计[J].北京:电子技术应用,2009(7):42G44.[4]徐加彦.基于F P G A的高速多通道A D采样系统的设计与实现[J].自动化与仪表,2014(9):49G52.[5]纪大伟,徐抒岩,胡君.基于F P G A的多通道高速数据采集系统[J].仪表技术与传感器,2011,12:31G32.[6]甘建伟,秦付军,王鹏.基于F P G A的高速多通道数据采集系统设计[J].电子技术应用,2013,39(4):87G88.[7]杨炜新.基于F P G A的多通道数据采集系统设计[D].太原:中北大学,2014.[8]秦爽.多通道同步数据采集系统设计与实现[D].成都:电子科技大学,2009.[9]刘洋.基于N i o s I I的多路基阵信号数据采集与传输技术研究[D].哈尔滨:哈尔滨工程大学,2013.[10]刘曲波.基于I E C61850的电子式互感器数字接口的设计[D].武汉:华中科技大学,2007.[责任编辑:李岚]D e s i g no f16GC h a n n e lH i g hGp r e c i s i o nS y n c h r o n i z e dD a t aA c q u i s i t i o nS y s t e mY A N G H u iGw e i,MAS h uGx i a n g,Z H O U X i a nGf e i(S c h o o l o f I n f o r m a t i o nE n g i n e e r i n g,W u h u I n s t i t u t e o fT e c h n o l o g y,W u h u241002,A n h u i,C h i n a)A b s t r a c t:I n o r d e r t o s y n c h r o n o u s l y d e t e c tm u l t i p l e d e t e c t i o n p o i n t s a n d a c c u r a t e l y r e f l e c t t h e r e a l s i t uGa t i o no f t h e d e t e c t i o n o b j e c t a t a c e r t a i n t i m e,a16Gc h a n n e l h i g hGp r e c i s i o n s y n c h r o n o u s d a t a a c q u i s i t i o n s y s t e mi s p r o p o s e d.T h e s y s t e mf i r s t l y a p p l i e s p r o g r a mm a b l eF P G Aa s t h e c o n t r o l u n i t t o p r o v i d e a u n i f i e dC O N S T A B,C S N e n a b l e m e n ta n d RGr e a d i n g c o n t r o l s e q u e n c ef o rt h et w o p i e c e so fF P G A, t h e n t w o t a s k s a r e e x e c u t e d i n p a r a l l e l t o c o m p l e t e t h e16Gp a s s c o m p o s e d o f t w o p i e c e s o fA D7606a n d c h a n n e l d a t aa r ec o l l e c t e ds y n c h r o n o u s l y i n t ot w oc o r r e s p o n d i n g F I F Oa r r a y s,f i n a l l y,t h ed a t aa r e c o n v e r t e d i n t oU S Bd a t ab y t a b l e t e n n i s o p e r a t i o no f F I F Oa n d t r a n s m i t t e d t oP C f o r s t o r a g e a n dd i sGp l a y.T h e e x p e r i m e n t a l r e s u l t s s h o wt h a t t h e s y s t e mc a n a c h i e v e16Gc h a n n e l d a t a s y n c h r o n o u s a c q u i s iGt i o na n dd i s p l a y,t h es a m p l i n g r a t e i s200K S M P S,a n dt h er a n g eo f s a m p l i n g v o l t a g e i s-10~+10V.K e y w o r d s:h i g hGp r e c i s i o n;s y n c h r o n i z a t i o n;d a t a a c q u i s i t i o n;t i m i n g c o n t r o l66㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀兰州文理学院学报(自然科学版)㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀第34卷。

基于STM32及AD7606的16通道同步数据采集系统设计

摘要: 介绍了基于STM32及AD7606的同步数据采集系统的软硬件设计。

主控芯片采用基于ARM Cortex-M4内核的STM32F407IGT6,实现对AD 采集数据的实时计算并通过以太网络进行数据传输。

A7606为16位、8通道同步采样模数数据采集系统[],利用两片AD7606,可以实现对16路通道的实时同步采样。

经过测试,该系统可以实现较高精度的实时数据采集。

0 引言

[此处找书介绍STM32],该芯片主频可达168MHz,具有丰富的片内外设,并且与前代相比增加了浮点运算单元(Floating Point Unit,FPU),使其可以满足数据采集系统中的 [介绍AD7606]

1 系统总体方案设计

整个系统由传感器模块、信号调理模块、数据采集模块、处理器STM32、及通信模块及上位机系统组成。

系统整体结构框图如图1所示。

本系统是为液态金属电池性能测试设计,需要测量电池的充放电电压、电流以及交流加热系统的电压、电流,并以此计算出整个液态金属电池储能系统的效率。

因此两片AD7606的16个通道分为两组,每组8个通道,这两组分别测量4路直流、交流的电压和电流信号。

AD7606通过并行接口与STM32连接,STM32读取AD 采样数据后进行计算,并将数据通过网络芯片DP83848通过UDP 协议发送给上位机。

上位机负责显示各通道采集信息、绘制波形以及保存数据等。

STM32F407IGT6

霍尔直流传感器

上位机软件DP83848

直流信号

交流信号

交流互感器

调理电路

调理电路

AD7606

AD7606

图1 系统整体结构框图

2 系统硬件设计

2.1 模拟信号采集电路设计 模拟信号的采集包含直流电压、电流,交流电压、电流四部分。

直流信号的采集分别使用霍尔电压传感器HNV025A 和霍尔电流传感器HNC100B ,两种传感器的电路原理图类似,仅以霍尔电压传感器电路原理图为例说明,如图2-1所示。

HNV025A 为电流型霍尔电压传感器,可以提高信号的抗干扰能力,其输入输出电流比为10mA/25mA 。

因此在图中被测电压经过电阻R1转换为电流信号,传感器输出的电流信号经过R2变为电压信号。

R3和C1组成一阶低通滤波器进行滤波。

HNV25A R1

R2

R3

C1

+15V

-15V

AD_IN

100Ω

3K Ω

316Ω

10uF

接被测电压

+

-

图2-1 直流电压信号采集原理图

交流电压、电流信号的调理电路同样类似,以交流电压信号采集为例,其电路原理图如图2-2所示。

交流电压互感器变比为2mA/2mA ,运放T1及电阻R3组成电流-电压转换电路,R2和C1是为了补偿电压互感器的相移,电容C2用来去耦和滤波。

+

-AD_IN

+

-R2 200K R3 1.5K

C1 47nF

R1 110K

C2 470pF

接被测电压

T1

T2

图2-2 交流电压信号采集原理图

2.2 数据采集模块设计

数据采集模块由两片AD7606组成,AD7606与STM32之间的电路连接示意图如图2-3所示。

图2-3 SD7606与STM32连接示意图

(1)AD7606提供了三种接口选项【参考】:并行接口、高速串行接口和并行字节接口。

其

中并行接口具有最高的数据传输速度,并且与STM32的FSMC(Flexible Static Memory Controller,可变静态存储控制器)兼容。

因此两片AD7606与STM32通过并行接口方式连接。

AD7606的数据线DB0~DB15分别连接对应的FSMC数据线,片选信号分别接到FSMC接口片选信号PG9_FSMC_NE2和PG12_FSMC_NE4上。

(2)AD7606的BUSY引脚电平为高时表示AD正在进行转换,变低表示转换完成。

将BUSY 引脚接到STM32的外部中断引脚并配置为下降沿触发,这样可以在AF转换完成后及时读取数据。

(3)OS[0..2]为过采样配置引脚,通过控制STM32相关GPIO的电平可以是AD7606工作在不同的过采样状态。

(4)CONVST_A,CONVST_B为转换触发信号,上升沿触发。

对于每一个AD7606来说,CONVST_A控制模拟通道1~4,CONVST_B控制模拟通道5~8。

由于需要对所有通道同步采样,因此将CONVST_A,CONVST_B引脚同时连接在一个触发信号引脚上以实现同步采样。

(5)REFOUT引脚为外部基准电压输入引脚。

AD7606可以配置为使用内部基准电压或外部基准电压。

当两片AD7606同时工作时,使用外部基准电压可以保证所有输入通道转换精度的一致性。

外部基准电压源选择ADR421,ADR421为2.5V基准电源,具有出色的噪声性能、稳定性和精度【参考】,可以满足AD对基准电压源的精度要求。

2.3 通讯模块设计

本系统中数据通过以太网络传输,与传统串行通讯相比,可以实现更高的数据传输速度,同时便于实现对设备的远程访问以及将多套系统共同接入网络。

3 系统软件设计

软件的开发是在Keil MDK开发环境下进行的,应用程序主要包括STM32F4的初始化、AD7606采样程序配置、LWIP协议栈的移植、数据处理等。

初始化部分包括GPIO初始化、内存管理初始化、定时器初始化以及各项计算系数初始化等;AD7606采样程序配置主要包含FSMC配置、中断配置、数据读取、过采样配置等;LWIP协议栈移植包括编写DP83848驱动程序、修改LWIP源码、实现UDP发送接收数据等;数据处理部分包括根据采样数据计算所需要的电压、电流有效值、功率等等。

程序运行时,首先进行初始化操作,之后会在AD7606的触发引脚CONVST_A,CONVST_B 上产生预设的固定频率和脉宽的脉冲信号,脉冲信号的上升沿触发AD进行采集,此时AD7606的BUSY信号引脚为高,转换结束后BUSY变低,由此产生外部中断,在中断程序中读取AD的采样结果。

有两个缓冲区交替存储AD的采样结果,当一个缓冲区存满时再进行各项参数计算,此时AD的采样结果将保存在另外一个缓冲区中。

双缓冲区的机制保证了在计算过程中缓中区中的数据不会被AD实时采样的数据所覆盖而导致计算错误。

计算所得到的结果会定时发送给上位机。

上下位机之间通过UDP协议进行数据传输,在主函数中会循环检测是否接收到上位机的命令数据,如果接收到数据,则根据既定的命令代码执行不行的操作。

每一帧发送的数据通信格式如图3-1所示:

根据命令号的不同,已经实现的功能有:修改定时发送数据时间间隔、请求实时波形数据、AD复位、传感器校零、AD过采样率设置等。

4系统精度测试与分析

为测试系统精度,选择。

作为参考标准。

理想的霍尔传感器在输入为零时输出电流也应为零,不过实际的霍尔传感器即使输入为零时也会有很小的输出电流,这样会对测量结果造成一定的直流偏置。

通过上文提到的传感器校零操作,可以将此直流偏置对测量结果的影响减少到最小。

具体方法是在霍尔传感器输入为零时保存此时的AD采样值,然后在之后的实际测试中将每个采样值均减去此值。

下面的测试结果均为将传感器校零后的测试结果。