第五章 寄生参数

- 格式:ppt

- 大小:3.03 MB

- 文档页数:42

寄生参数提取 starrc流程英文回答:## Parasitic Parameter Extraction (StarRC Flow)。

Introduction.Parasitic parameters are key factors influencing the accuracy and efficiency of modern integrated circuit (IC) designs. These parameters account for the unwantedelectrical effects caused by the physical layout of transistors and interconnects, and their accurateextraction is crucial for predicting circuit performance and reliability.StarRC is a widely used commercial tool for parasitic parameter extraction. It employs a full-wave electromagnetic field solver to compute the resistance, capacitance, and inductance of various structures within an IC layout. This approach provides highly accurate resultsbut can be computationally intensive for large and complex designs.StarRC Extraction Flow.The StarRC parasitic parameter extraction flowtypically involves the following steps:1. Layout Preparation: The IC layout is prepared by flattening the layers and removing unnecessary details.2. Mesh Generation: A mesh is generated over the layout to define the geometry for electromagnetic field simulations.3. Electromagnetic Field Simulation: The full-wave solver in StarRC is employed to compute the electromagnetic fields and extract the parasitic parameters.4. Post-Processing: The extracted parasitic parameters are post-processed to remove unwanted effects and improve the accuracy of the extraction.Applications of Parasitic Parameter Extraction.The parasitic parameters extracted using StarRC can be utilized in various applications, including:Circuit simulation: Parasitic parameters can be incorporated into circuit simulators to predict circuit behavior under different operating conditions.Timing analysis: Parasitic parameters impact circuit delays and timing characteristics, and their accurate extraction is essential for accurate timing analysis.Electrostatic discharge (ESD) analysis: Parasitic parameters influence the ESD susceptibility of ICs, and their extraction is crucial for ESD protection design.Power integrity analysis: Parasitic parameters affect power distribution networks and can lead to power supply noise and voltage drop issues, which can be mitigated by considering these parameters in power integrity analysis.Benefits of Using StarRC.StarRC offers several advantages for parasitic parameter extraction:Accuracy: StarRC employs a full-wave electromagnetic field solver, which provides highly accurate results.Scalability: StarRC can handle large and complex designs with millions of transistors and billions of interconnects.Efficiency: StarRC utilizes advanced algorithms and parallelization techniques to optimize the extraction process.User-Friendliness: StarRC provides a user-friendly interface and comprehensive documentation to facilitate its usage.Conclusion.Parasitic parameter extraction is critical for modern IC design. StarRC offers a robust and accurate solution for extracting these parameters, enabling designers to better predict circuit performance, improve reliability, and mitigate design risks.中文回答:## 寄生参数提取(StarRC 流程)。

版图设计中的寄生参数分析深圳中兴集成电路设计有限公司金善子1.引言正如我们了解的,工艺层是芯片设计的重要组成部分。

一层金属搭在另一层金属上面,一个晶体管靠近另一个晶体管放置,而且这些晶体管全部都是在衬底上制作的。

只要在工艺制造中引入了两种不同的工艺层,就会产生相应的寄生器件,这些寄生器件广泛地分布在芯片各处,更糟糕的是我们无法摆脱它们。

寄生器件是我们非常不希望出现的,它会降低电路的速度,改变频率响应或者一些意想不到的事情发生。

既然寄生是无法避免的,那么电路设计者就要充分将这些因素考虑进去,尽量留一些余量以便把寄生参数带来的影响降至最低。

2.寄生参数的种类寄生参数主要包括了电容寄生、电阻寄生,和电感寄生。

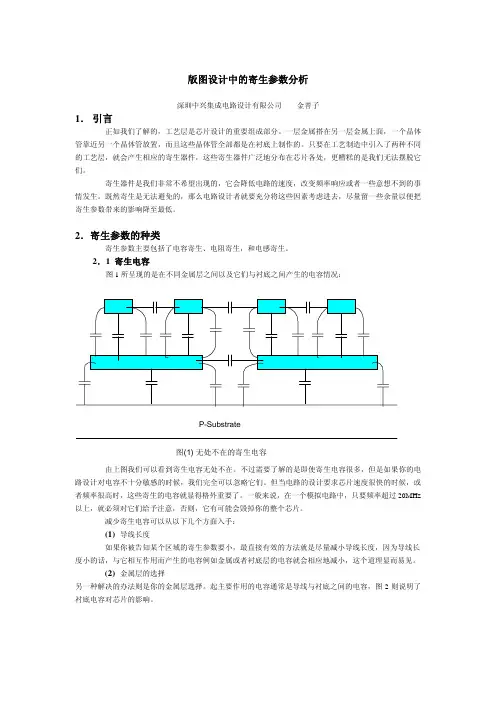

2.1 寄生电容图1所呈现的是在不同金属层之间以及它们与衬底之间产生的电容情况:图(1) 无处不在的寄生电容由上图我们可以看到寄生电容无处不在。

不过需要了解的是即使寄生电容很多,但是如果你的电路设计对电容不十分敏感的时候,我们完全可以忽略它们。

但当电路的设计要求芯片速度很快的时候,或者频率很高时,这些寄生的电容就显得格外重要了。

一般来说,在一个模拟电路中,只要频率超过20MHz 以上,就必须对它们给予注意,否则,它有可能会毁掉你的整个芯片。

减少寄生电容可以从以下几个方面入手:(1)导线长度如果你被告知某个区域的寄生参数要小,最直接有效的方法就是尽量减小导线长度,因为导线长度小的话,与它相互作用而产生的电容例如金属或者衬底层的电容就会相应地减小,这个道理显而易见。

(2)金属层的选择另一种解决的办法则是你的金属层选择。

起主要作用的电容通常是导线与衬底之间的电容,图2则说明了衬底电容对芯片的影响。

Noisy Quiet图(2) 衬底电容产生的噪声影响如上所示,电路1和电路2都对地产生了一个衬底电容,衬底本身又有一个寄生电阻,这样一来电路1的噪声就通过衬底耦合到电路2上面,这是我们不希望看到的。

因此我们改变一下金属层,通常情况下,最高金属层所形成的电容总是最小的。

高频小信号谐振放大器(总结)高频小信号谐振放大器=高频+小信号+谐振+放大;高频:由于高频频率高波长短,不同于低频,所以在线路中会存在反射、串扰;以及整块电路板的寄生参数的影响会导致效果会一点也出不来。

因为此次的频率在6M频率不算很高,总结一些解决方法:①反射:器件之间的连线要短,最好是直接相连,背面焊接不要出现就90°转折。

②串扰:级与级之间的地线处理好,最好是单点供地,并且地线要是所有传输线中最粗的一根,信号线不要裸露的从地线上方走过。

③寄生参数:是个不好处理的参数,但是可以通过输出的波形分析出,然后实施相应方法避免或解决,如布线不要有平行线,减小接入系数可以减小晶体管极间电容的影响。

注:自制扼流线圈或电感在绕制好后需用绝缘胶布固定,防止其因线圈变动影响稳定性。

小信号:小信号的输入大小影响晶体管的基极偏置,但是不能太小,因为学校的数字合成信号发生器在输出小于10mv的时候会有寄生波纹输出,在示波器上显示的可能是几百Hz属于低频信号,但是此时的信号仍然是高频信号,出现这种现象是因为示波器导致的视觉误差。

因为这种波纹的存在导致输出的波形上下浮动,很容易认为是电路的寄生振荡。

解决方法是提高小信号的输出幅度,一般在100mv时寄生波纹很小。

(注:有的数字合成信号发生器输出没有寄生波纹)谐振:涉及到输出的中心频率和带宽,如图:电容和电感可由计算可得,而这个电位器的作用是在输出带宽窄的情况下,调节电位器,减小其接入阻值,可以增加带宽。

放大:此次的核心是放大,其他的工作做的再好,不放大就是做无用功,只有放大了,再出现问题就好解决。

出现不放大的情况有以下几种:①输出增益为负值②增益不够高③输出波形失真,如图:解决方法:①静态工作点没有设置好,基极偏置跟低频不一样,经验值为+5V左右;②增益不够高很大程度上是因为晶体管的截止频率不够(静态工作点合理),可以尝试换截止频率高的晶体管,如9018 的截止频率为1G,足够放大。

finfet单元结构的寄生参数提取FinFET(Fin Field-Effect Transistor)是一种三维晶体管结构,其带来了新的寄生参数,需要进行提取和建模。

寄生参数是指在电路元件中存在且具有一定影响的电阻、电容和电感等参数。

对于FinFET单元结构,其中的寄生参数包括通道电阻、接触电阻、源/漏接触电阻、栅氧电容、外延电阻等,下面将对这些寄生参数进行详细的提取方法进行介绍。

首先,通道电阻是FinFET单元结构中的一个重要寄生参数。

它影响了传输特性和输出特性的性能。

常用的提取方法是基于建模和测量的结合。

在建模方面,可以使用二维有限元方法或二维瞬态电流导数方法进行计算模拟。

而在测量方面,可以通过量测终端I-V曲线和直流注入方法进行实验测量。

通过这些方法可以获得通道电阻的数值和变化规律。

其次,接触电阻是FinFET单元结构中的另一个重要寄生参数。

它影响了信号传输的稳定性和速度。

接触电阻的提取方法可以分为电学方法和物理方法两种。

电学方法主要通过测量接触电阻的电流-电压关系,如线性插值法或基于界面Hamiltonian的方法。

而物理方法主要通过X射线能谱学和原子力显微镜技术等手段进行非接触测量。

这些方法可以获得接触电阻的数值和分布情况。

此外,源/漏接触电阻也是需要提取的寄生参数之一。

它对FinFET 单元结构的低电压操作和快速开关速度具有重要影响。

提取方法主要是通过测量晶体管结构的源/漏接触电压和电流关系,获取接触电阻的数值和特性。

栅氧电容是FinFET单元结构中的一个重要寄生参数。

它在FinFET 单元结构的小尺寸和高频操作中起到关键作用。

常用的提取方法包括基于测量和建模的方法。

测量方法主要通过C-V(电容-电压)曲线测量、电流充放技术和频率响应技术进行实验测量。

而建模方法可以通过有限元分析和开路时域反射法进行计算模拟。

这些方法可以获得栅氧电容的数值和变化规律。

最后,外延电阻是寄生参数中的一个重要因素。

一、概述在电子电路中,谐振电路是一种常见的重要组成部分。

谐振电路具有对特定频率的信号具有放大作用的特点,在无线电通信、射频信号处理、切换电源等领域应用广泛。

谐振电路包括谐振电感和寄生参数震荡两种类型,本文将对这两种谐振电路进行深入探讨。

二、谐振电感1. 概念谐振电感是指在谐振电路中起到储能和调节电流的作用的电感元件。

谐振电感通常采用线圈的形式,其具有选择性放大特定频率信号的特点。

在谐振电路中,谐振电感可以使电路在特定频率下形成谐振现象,从而实现对特定频率信号的放大。

2. 特性谐振电感的特性包括自感和互感。

自感指的是电感元件产生的自感应电动势,即线圈本身所产生的感应电压。

而互感则是指在多圈线圈之间互相感应的电动势。

在谐振电路中,自感和互感的存在使得谐振电感具有对特定频率信号的放大和滤波作用。

三、寄生参数震荡1. 概念寄生参数震荡是指在电路中由于元件本身的不完美性或者布线方式所导致的一种非预期的自激振荡现象。

在谐振电路中,由于元件之间的电容、电感、电阻等参数,加上布线形式和接地方式等因素,可能会出现寄生参数震荡的情况。

2. 原因寄生参数震荡通常是由于元件本身的不完美性引起的。

电容元件的内部电阻、电感元件的漏电感、电阻元件的电感等,都可能会导致电路中出现一定的寄生参数。

布线方式、接地方式等也会对电路的稳定性产生影响,从而引起寄生参数震荡。

四、谐振电感与寄生参数震荡的区别和通联1. 区别谐振电感是一种被设计用于特定频率信号放大的元件,具有正常工作状态下对特定频率信号的响应特性。

而寄生参数震荡是一种非预期的自激振荡现象,通常是由于元件本身的不完美性或者电路的布线方式等因素所引起的。

2. 通联谐振电感和寄生参数震荡都与电路中的参数相关。

在谐振电路中,如果元件本身存在不完美性或者电路设计不合理,也可能会导致寄生参数震荡的发生。

谐振电感与寄生参数震荡在某种程度上具有关联性。

五、如何应对谐振电感和寄生参数震荡1. 对谐振电感的处理在设计谐振电路时,应当考虑到电感元件的自感和互感特性,合理选择电感元件的参数并保证其质量稳定性。

寄生参数对基于常通型SiC JFET器件的中压直流固态断路器过电压的影响及抑制方法何东;李俊桦;兰征;王伟;曾进辉【期刊名称】《南方电网技术》【年(卷),期】2024(18)4【摘要】研究了寄生电感对基于常通型碳化硅(silicon carbide,SiC)结型场效应晶体管(junction field effect transistor,JFET)串联结构的中压直流固态断路器(solid state circuit breaker,SSCB)过电压的影响,并在此基础上提出了一种SSCB的过电压抑制方法。

首先介绍了基于常通型SiC JFET器件串联结构的SSCB拓扑及工作原理,建立了考虑完整回路寄生电感的SiC JFET串联结构开关过程的数学模型。

其次利用MATLAB软件对数学模型进行解析计算,揭示了SSCB开关过程中寄生电感对SiC JFET器件串联运行时过电压的影响机理,并利用PSPICE仿真结果验证了理论分析的正确性。

最后设计了一种适用于SSCB过电压抑制的单栅极驱动及缓冲电路,并通过SSCB实验样机验证了所提方法的有效性。

【总页数】11页(P19-29)【作者】何东;李俊桦;兰征;王伟;曾进辉【作者单位】湖南工业大学电气与信息工程学院;湖南大学电气与信息工程学院【正文语种】中文【中图分类】TM561【相关文献】1.一种混合型直流断路器中晶闸管关断过电压抑制方法研究2.基于SiC MOSFET 直流固态断路器关断初期电压尖峰抑制方法3.基于常通型碳化硅JFET的自供电固态断路器4.基于逆阻型IGCT器件的固态式直流断路器设计及研制5.基于级联常通型SiC JFET的快速中压直流固态断路器设计及实验验证因版权原因,仅展示原文概要,查看原文内容请购买。

实验八寄生参数提取(PE)及信号完整性分析(SI)一、实验目的1.了解寄生参数的产生及对电路的影响。

2.掌握寄生参数提取和信号完整性分析的流程和意义。

二、实验内容1. 寄生参数提取(1)在Zeni LE窗口中,选择V erification->Layout V erification,在弹出的对话框中,选择Tool->Zeni V eri。

(2)在Command file栏里,浏览输入以下路径/zeni/v4627/demo/veri/PE_demo/pe_demo.pe,该文件是Zeni系统中PE_demo样本库所提供的用于PE提取的规则命令文件。

(3)将Custom Operation前的方框选中,选择PE选项卡。

(4)按下Appy键或OK键,Zeni开始运行PE分析。

报告结果存放在工作路径中的<cellname>.veri.log文件中。

注意:PE分析完成后,Zeni将在工作路径下生成一个以<cellname>.spi为名称的SPICE网表文件。

打开该文件可以看到,PE过程将按照提取规则,提取出版图中存在的所有器件,而不仅仅是寄生电阻和寄生电容,用户自己设计的晶体管及电容电阻等也会被一起提取出来。

该文件的名字和设计原理图时生成的网表一样,所以在PE进行时,原理图的spi网表将被覆盖。

如果需要保留,应该在PE之前将原spi网表文件换一个名字保存。

2. 局部寄生参数提取(Partial PE)(1)Partial PE执行的过程和全局PE是一样的,采用同样的PE规则命令文件。

只是在Custom Operation选项处,选择Partial PE选项卡,如下图所示。

3. 信号完整性分析(SI)在版图进行寄生参数提取(PE)之后,应该进行信号完整性分析(SI Analysis),以考察寄生参数对信号的影响程度,是否达到不可接受的程度。

目前,Zeni SI工具可以提供以下分析:Time Delay(时延分析)RC-Reduction(R,C值分析)Noise Analysis(噪声分析)(1)在PE进行完成之后,在LE窗口中,选择主菜单栏-verification,在下拉菜单中选择SI Analysis。

数字集成电路设计笔记归纳第三章、器件⼀、超深亚微⽶⼯艺条件下MOS 管主要⼆阶效应:1、速度饱和效应:主要出现在短沟道NMOS 管,PMOS 速度饱和效应不显著。

主要原因是TH GS V V -太⼤。

在沟道电场强度不⾼时载流⼦速度正⽐于电场强度(µξν=),即载流⼦迁移率是常数。

但在电场强度很⾼时载流⼦的速度将由于散射效应⽽趋于饱和,不再随电场强度的增加⽽线性增加。

此时近似表达式为:µξυ=(c ξξ<),c s a t µξυυ==(c ξξ≥),出现饱和速度时的漏源电压DSAT V 是⼀个常数。

线性区的电流公式不变,但⼀旦达到DSAT V ,电流即可饱和,此时DS I与GS V 成线性关系(不再是低压时的平⽅关系)。

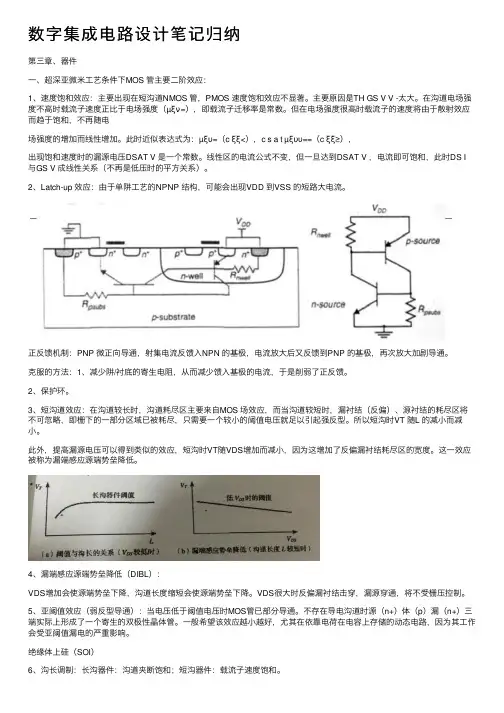

2、Latch-up 效应:由于单阱⼯艺的NPNP 结构,可能会出现VDD 到VSS 的短路⼤电流。

正反馈机制:PNP 微正向导通,射集电流反馈⼊NPN 的基极,电流放⼤后⼜反馈到PNP 的基极,再次放⼤加剧导通。

克服的⽅法:1、减少阱/衬底的寄⽣电阻,从⽽减少馈⼊基极的电流,于是削弱了正反馈。

2、保护环。

3、短沟道效应:在沟道较长时,沟道耗尽区主要来⾃MOS 场效应,⽽当沟道较短时,漏衬结(反偏)、源衬结的耗尽区将不可忽略,即栅下的⼀部分区域已被耗尽,只需要⼀个较⼩的阈值电压就⾜以引起强反型。

所以短沟时VT 随L 的减⼩⽽减⼩。

此外,提⾼漏源电压可以得到类似的效应,短沟时VT随VDS增加⽽减⼩,因为这增加了反偏漏衬结耗尽区的宽度。

这⼀效应被称为漏端感应源端势垒降低。

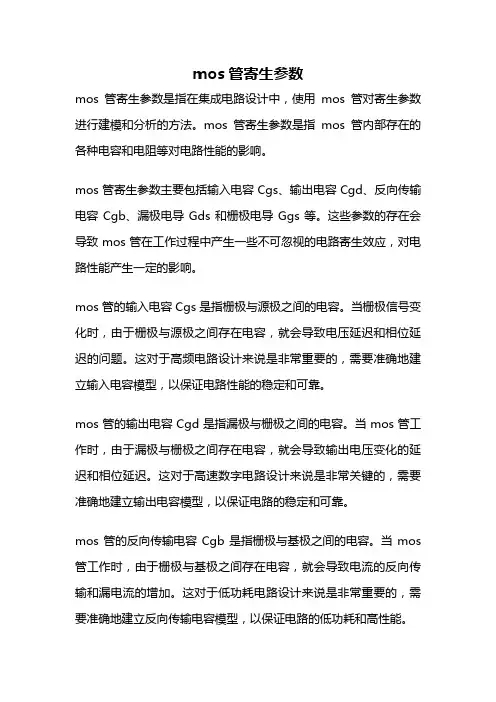

4、漏端感应源端势垒降低(DIBL):VDS增加会使源端势垒下降,沟道长度缩短会使源端势垒下降。

VDS很⼤时反偏漏衬结击穿,漏源穿通,将不受栅压控制。

5、亚阈值效应(弱反型导通):当电压低于阈值电压时MOS管已部分导通。

不存在导电沟道时源(n+)体(p)漏(n+)三端实际上形成了⼀个寄⽣的双极性晶体管。

mos管寄生参数mos管寄生参数是指在集成电路设计中,使用mos管对寄生参数进行建模和分析的方法。

mos管寄生参数是指mos管内部存在的各种电容和电阻等对电路性能的影响。

mos管寄生参数主要包括输入电容Cgs、输出电容Cgd、反向传输电容Cgb、漏极电导Gds和栅极电导Ggs等。

这些参数的存在会导致mos管在工作过程中产生一些不可忽视的电路寄生效应,对电路性能产生一定的影响。

mos管的输入电容Cgs是指栅极与源极之间的电容。

当栅极信号变化时,由于栅极与源极之间存在电容,就会导致电压延迟和相位延迟的问题。

这对于高频电路设计来说是非常重要的,需要准确地建立输入电容模型,以保证电路性能的稳定和可靠。

mos管的输出电容Cgd是指漏极与栅极之间的电容。

当mos管工作时,由于漏极与栅极之间存在电容,就会导致输出电压变化的延迟和相位延迟。

这对于高速数字电路设计来说是非常关键的,需要准确地建立输出电容模型,以保证电路的稳定和可靠。

mos管的反向传输电容Cgb是指栅极与基极之间的电容。

当mos 管工作时,由于栅极与基极之间存在电容,就会导致电流的反向传输和漏电流的增加。

这对于低功耗电路设计来说是非常重要的,需要准确地建立反向传输电容模型,以保证电路的低功耗和高性能。

mos管的漏极电导Gds是指漏极电流与漏极电压之间的关系。

当mos管工作时,由于漏极电流与漏极电压之间存在一定的关系,就会导致漏极电流的非线性增加和漏极电压的非线性变化。

这对于模拟电路设计来说是非常关键的,需要准确地建立漏极电导模型,以保证电路的线性和稳定。

mos管的栅极电导Ggs是指栅极电流与栅极电压之间的关系。

当mos管工作时,由于栅极电流与栅极电压之间存在一定的关系,就会导致栅极电流的非线性增加和栅极电压的非线性变化。

这对于模拟电路设计来说也是非常关键的,需要准确地建立栅极电导模型,以保证电路的线性和稳定。

mos管寄生参数是集成电路设计中不可忽视的重要因素。

Ads 晶体管寄生参数1. 导言晶体管是一种重要的电子元件,广泛应用于电子设备中。

在实际应用中,晶体管的寄生参数对其性能有着重要影响。

本文将介绍晶体管的寄生参数以及其对电路性能的影响。

2. 晶体管的基本结构晶体管是一种半导体器件,通常由三个区域组成:发射区、基区和集电区。

发射区和集电区分别为N型或P型半导体,基区为P型或N型半导体。

晶体管的工作原理是通过控制基区的电流来控制发射区和集电区之间的电流。

3. 晶体管的寄生参数晶体管的寄生参数是指在实际电路中,由于晶体管的物理结构和制造工艺等因素引起的一些不可避免的电阻、电容和电感等效应。

常见的晶体管寄生参数包括:3.1 发射结电容(Cbe)发射结电容是指发射区和基区之间的电容。

它由于发射区和基区之间的结电容而产生,是晶体管的一个重要参数。

发射结电容的值取决于晶体管的结构和工艺等因素。

3.2 集电结电容(Cbc)集电结电容是指集电区和基区之间的电容。

它由于集电区和基区之间的结电容而产生。

集电结电容的值也取决于晶体管的结构和工艺等因素。

3.3 输入电容(Cin)输入电容是指晶体管的输入端(一般为基极)与其他端口(一般为集电极)之间的电容。

它是由发射结电容、集电结电容以及基区和集电区之间的电容等共同组成的。

3.4 输出电容(Cout)输出电容是指晶体管的输出端(一般为集电极)与其他端口(一般为基极)之间的电容。

它是由集电结电容以及基区和集电区之间的电容等共同组成的。

3.5 输入电阻(Rin)输入电阻是指晶体管的输入端(一般为基极)与其他端口(一般为集电极)之间的电阻。

输入电阻的值取决于晶体管的结构和工艺等因素。

3.6 输出电阻(Rout)输出电阻是指晶体管的输出端(一般为集电极)与其他端口(一般为基极)之间的电阻。

输出电阻的值取决于晶体管的结构和工艺等因素。

3.7 互导(h参数)h参数是一组用于描述晶体管电路特性的参数。

常见的h参数有hfe(直流电流放大倍数)、hie(输入电阻)、hre(反馈系数)和hoe(输出电导)等。

精讲变压器的“寄生参数”——漏感与分布电容

本文主要为大家讲解一下变压器中的两个寄生参数,漏感与分布电容。

从定义到产生的原因,以及危害等多方面进行讲解。

大家好好学习吧!下面

先来介绍一下漏感的相关知识。

漏感的定义

漏感是电机初次级在耦合的过程中漏掉的那一部份磁通

变压器的漏感应该是线圈所产生的磁力线不能都通过次级线圈,因此产生漏

磁的电感称为漏感。

漏感产生的原因

漏感的产生是由于某些初级(次级)磁通没有通过磁芯耦合到次级(初级),而是通过空气闭合返回到初级(次级)。

导线的电导率大约为空气电导率的109倍,而变压器用的铁氧体磁芯材料

的磁导率大约只有空气磁导率的104倍。

因此磁通在通过铁氧体磁芯构成的

磁路时,就会有一部分漏入空气,在空气中形成闭合磁路,从而产生漏磁。

而且随着工作频率的提高,所使用的铁氧体磁芯材料的磁导率会降低。

因此

在高频下,这种现象更为明显。

漏感的危害

漏感是开关变压器的一项重要指标,对开关电源性能指标的影响很大,漏

感的存在,当开关器件截止瞬间会产生反电动势,容易把开关器件过压击穿;漏感还可以与电路中的分布电容以及变压器线圈的分布电容组成振荡回路,

使电路产生振荡并向外辐射电磁能量,造成电磁干扰。

影响漏感的因素

对于固定的已经制作好的变压器,漏感与以下几个因素有关:。

pex提取寄生参数摘要:I.引言- 介绍pex 提取寄生参数的概念II.pex 提取寄生参数的方法- 简述pex 提取寄生参数的具体步骤III.pex 提取寄生参数的应用- 阐述pex 提取寄生参数在实际问题中的运用IV.pex 提取寄生参数的优缺点- 分析pex 提取寄生参数的优点和不足V.结论- 总结pex 提取寄生参数的重要性和前景正文:I.引言在数据分析、机器学习等领域,特征提取是关键步骤,它直接影响到后续模型效果的好坏。

寄生参数(parasitic parameter)指的是在特征提取过程中,除了目标参数以外的其他辅助参数,这些参数可能对目标参数的提取起到一定作用,但同时也可能带来噪声。

近年来,pex 提取寄生参数的方法逐渐受到研究者们的关注。

II.pex 提取寄生参数的方法pex 提取寄生参数主要包括以下几个步骤:1.数据准备:收集与目标参数相关的数据,进行预处理,如缺失值填充、异常值处理等。

2.特征工程:利用现有的特征提取方法,如主成分分析(PCA)、自动编码器(AE)等,对数据进行特征提取。

3.参数估计:根据提取到的特征,使用统计方法或机器学习算法,估计目标参数和寄生参数。

4.模型评估:对估计出的参数进行模型评估,检查模型效果。

5.参数优化:根据模型评估结果,调整特征提取方法和参数估计方法,以提高模型效果。

III.pex 提取寄生参数的应用pex 提取寄生参数在实际问题中具有广泛应用,例如在金融领域的信用评分卡、医疗领域的疾病预测等。

通过寄生参数的提取,可以降低目标参数的估计误差,提高模型预测效果。

IV.pex 提取寄生参数的优缺点pex 提取寄生参数的优点在于能够提高目标参数估计的精确度,降低模型预测误差。

然而,它也存在一些不足,如在特征提取过程中可能引入过多噪声,导致模型过拟合。

此外,pex 提取寄生参数的方法依赖于数据和特征,当数据量不足或特征选择不当时,可能无法有效提高模型效果。