盐城工学院EDA实验仿真图

- 格式:doc

- 大小:392.04 KB

- 文档页数:17

EDA智能四路抢答器设计(框图+vhdl源程序+仿真图)-课程设计EDA智能四路抢答器设计(框图+vhdl源程序+仿真图) 设计目的 1. 进一步了解VHDL语言功能;2. 了解EDA在高频工作下的优势;3. 学习资料的收集与整理,学会撰写课程设计报告。

实验环境 1 微型电子计算机(PC);2. 安装Windows 2000以上操作系统,Maxplus软件等开发工具。

3. EDA综合实验仪,连线若干。

任务要求 1. 按照课题设计任务和要求,对设计系统进行验证调试或仿真;观察程序运行和仿真结果,判断其正确性。

2. 利用课余时间去图书馆或上网查阅课题相关资料,深入理解课题含义及设计要求,注意材料收集与整理;3. 在第15周末之前完成预设计,并请指导教师审查,通过后方可进行下一步工作;4. 结束后,及时提交设计报告(含纸质稿、电子稿),要求格式规范、内容完整、结论正确。

工作进度计划序号起止日期工作内容1 2009.12.14~2009.12.14 在预设计的基础上,进一步查阅资料,完善设计方案.2 2009.12.15~2009.12.16 设计总体方案,编写代码,上机调试,实验仿真验证。

3 2009.12.17~2009.12.17 测试程序,完善功能,撰写设计报告。

42009.12.18 参加答辩,根据教师反馈意见,修改、完善设计报告。

摘要抢答器作为一种工具,已经广泛应用于各种智力和知识竞赛场合。

但是抢答器的使用频率较低,且有的要么制作复杂,要么可靠性低,减少兴致。

作为一个单位若专购一台抢答器虽然在经济上可以承受,但每年使用的次数极少,往往因长期存放使抢答器损坏,再购置一台新的就会影响活动的开展,因此设计了本抢答器。

本设计是以四路抢答为基本概念。

从实际应用出发,利用电子设计自动化( EDA)技术,用可编程逻辑器件设计具有扩充功能的抢答器。

它以VHDL硬件描述语言作为平台,结合动手实验而完成的。

它的特点是电路简单、制作方便、操作简单、方便、性能可靠,实用于多种智力竞赛活动。

EDA仿真实验报告院系:电信学院学号:姓名:实验四、组合逻辑电路仿真实验一、组合逻辑电路分析仿真实验A B CU1A 74LS00DU1B 74LS00DU1C 74LS00D U2A74LS10DU2B74LS10DFXLC1A B将所得真值表填入表格1A BCF逻辑功能0 0 0 0 实 现 A,B,C 的 异 或0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 111最简逻辑函数表达式F= A ’C+AB ’+BC ’依据真值表和逻辑函数表达式分析该逻辑电路的逻辑功能二、 组合逻辑电路设计仿真实验设计一个燃油锅炉报警逻辑电路:燃油喷嘴处于开启状态时,如果锅炉水温或者烟道温度过高则发出报警信号。

1、 根据实际问题,进行逻辑抽象,确定输入变量和输出变量,并进行逻辑赋值。

2、 在逻辑转换仪上列真值表并求出最简表达式。

3、 利用真值表求得逻辑电路图。

4、 验证逻辑是否正确。

①油嘴状态:1开启0关闭 报警信号:1报警0不报警 锅炉水温:1高0低 烟道温度:1高0低真值表Y(报警信号) A(油嘴状态) B(锅炉水温) C(烟道温度)0 1 0 01 1 0 11 1 1 01 1 1 10 0 XX②③三、常用组合逻辑电路部件功能测试仿真实验1、编码器逻辑功能仿真实验U174LS148DA09A17A26GS 14D313D41D52D212D111D010D74D63EI5EO15J1Key = A J2Key = B J3Key = C J4Key = D J5Key = E J6Key = F J7Key = G J8Key = HVCC5V集成8线-3线优先编码器真值表:输入 输出 0 1 2 3 4 5 6 7 A2 A1 A0 X X X X X X X 0 0 0 0 X X X X X X 0 1 0 0 1 X X X X X 0 1 1 0 1 0 X X X X 0 1 1 1 0 1 1 X X X 0 1 1 1 1 1 0 0 X X 0 1 1 1 1 1 1 0 1 X 0 1 1 1 1 1 1 1 1 0 0 1 1 1 1 1 1 1 1 1 1 11111111111分析验证集成8线-3线优先编码器的逻辑功能2、译码器逻辑功能仿真实验 2.1 3-8译码器逻辑功能仿真XWG1RT X O X XO O 0161531XLA1C Q T1FVCC 5VAB C Y0Y1Y2Y3Y4Y5Y6Y774LS138DY015Y114Y213Y312Y411Y510Y69Y77A 1B 2C 3G16~G2A 4~G2B5字产生信号发生器 逻辑显示器 (1)真值表输入 输出G1 G2A+G2B A B C Y 0’ Y 1’ Y 2’ Y 3’ Y 4’ Y 5’ Y 6’ Y 7’ 0 X 1 1 1 1 1 1 1 1X 1 0 0 0 0 0 0 0 0X X X X X X 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 11 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0(2)逻辑分析仪工作波形分析验证集成3-8译码器的逻辑功能2.2七段显示译码器逻辑功能仿真XWG1RT X O X XO O 0161531AB C D 4511BD_5VDA 7DB 1DC 2DD 6OA 13OD 10OE 9OF 15OC 11OB 12OG14~EL 5~BI 4~LT3VCC 5V470¡Á7U1A B C D E F GCK真值表输入输出 D C B A OA OB OC OD OE OF OG 数码显示的数字0 0 0 0 1 1 1 1 1 1 0 0 0 0 0 1 0 1 1 0 0 0 0 1 0 0 1 0 1 1 0 1 1 0 1 2 0 0 1 1 1 1 1 1 0 0 1 3 0 1 0 0 0 1 1 0 0 1 1 4 0 1 0 1 1 0 1 1 0 1 1 5 0 1 1 0 0 0 1 1 1 1 1 6 0 1 1 1 1 1 1 0 0 0 0 7 1 0 0 0 1 1 1 1 1 1 1 8 1 0 0 11 1 1 1 0 0 193、数据选择器逻辑功能仿真实验YJ1Key = CVCC5VJ2Key = B J3Key = ACBAU174LS151D~W6D04D13D22D31D415D514D613D712A 11C 9B 10Y 5~G7真值表输入输出 输入 输出 C B A F C B A F 0 0 0 0 1 0 0 0 0 0 1 1 1 0 1 1 0 1 0 1 1 1 0 0 0 11111分析验证8选1数据选择器74LS151D 的逻辑功能实验五、时序逻辑电路仿真实验实验目的:1、掌握常用触发器的逻辑功能和时序特性。

10-11学年第二学期《EDA实验指导书》(试用)学时:12班级:机电811、812指导教师:孙立香盐城纺织职业技术学院机电系电子教研室目录实验一 Protel 99 SE 启动、建库、文件环境参数设置 (3)实验二熟悉元器件库,编辑简单原理图 (5)实验三电路原理图设计 (6)实验四原理图元件制作 (9)实验五 PCB 设计基础 (11)实验六 PCB 图元件制作 (12)附加印制电路板设计 (14)实验一 Protel 99 SE 启动、建库、文件环境参数设置一、实验目的1 .熟悉 scH 99 的基本界面。

2 .学会文件环境参数设置。

二、实验内容1. 启动 Protel99SE ,建立名为 MYPRO 的文件夹,并在文件夹中建立名为MYFIRST 的设计数据库文件。

提示:单击桌面上的 Protel99SE 快捷图标,进入 Protel99SE 设计环境。

若环境中已经有设计数据库文件,就执行菜单 File/Close Design 将其关闭。

若环境中没有设计数据库文件,就执行菜单 File/New ,在弹出的窗口中,单击Browse 按钮,在弹出的文件名输入窗口中建立 MYPRO 的文件夹,并在文件夹中建立 MYFIRST 的设计文件。

2. 在练习 1 的基础上,建立名为 FIRSCH 的原理图文件,并进入原理图设计窗口。

提示:执行 File/New 菜单,在弹出的窗口中选择 Schematic Document 图标。

3. 设置原理图的图纸尺寸为 A0 ,去掉可视栅格,去掉标题栏。

提示:在原理图设计环境中,执行菜单 Design/Options ,在弹出的窗口中选择 Sheet Options 页面,在页面右上角的 Standard Styles 下拉框中选择A0 。

4. 把光标设置成大十字,并把光标移动到图纸边沿时的移动速度设置为 Auto Pan Recenter 。

提示:设置光标:在原理图设计环境中,执行菜单 Tools/Preferences ,在弹出的窗口中选择 Graphical Editing 页面,然后在该页面 Cursor/Grid Options 区域的 Cursor Type 下拉列表框中选择 Large Cursor 90 。

![最新[工学]eda实验指导及讲义PPT课件](https://img.taocdn.com/s1/m/26e31dd0b52acfc789ebc9f0.png)

盐城工学院高频实验指导书-CAL-FENGHAI.-(YICAI)-Company One1《高频电子线路》实验指导书盐城工学院信息学院2010、09目录2一、函数信号发生实验 (1)二、非线性波型变换实验 (7)三、小信号调谐放大实验 (12)四、LC与晶体振荡器实验 (17)五、集成乘法器混频实验 (25)六、幅度调制与解调实验 (29)七、变容二极管调频器与相位鉴频器实验 (34)3八、通频带展宽实验 (41)41实验一、函数信号发生实验一、实验目的1)、了解单片集成函数信号发生器ICL8038的功能及特点。

2)、掌握ICL8038的应用方法。

二、实验预习要求参阅相关资料中有关ICL8038的内容介绍。

三、实验原理(一)、ICL8038内部框图介绍ICL8038是单片集成函数信号发生器,其内部框图如图1-1所示。

它由 恒流源I 2和I 1、电压比较器A 和B 、触发器、缓冲器和三角波变正弦波电路等组成。

外接电容C 可由两个恒流源充电和放电,电压比较器A 、B 的阀值分别为总电 源电压(指U CC +U EE )的2/3 和1/3。

恒流源I 2和I 1的大 小可通过外接电阻调节,但 必须I 2>I 1。

当触发器的输出为低电平时,恒流源I 2断开 图1-1、ICL8038原理框图,恒流源I 1给C 充电,它的两端电压u C 随时间线性上升,当达到电源电压的确2/3时,电压比较器A 的输出电压发生跳变,使触发器输出由低电平外接电容EE2变为高电平,恒流源I 2接通,由于I 2>I 1(设I 2=2I 1),I 2将加到C 上进行反充电,相当于C 由一个净电流I 放电,C 两端的电压u C 又转为直线下降。

当它下降到电源电压的1/3时,电压比较器B 输出电压便发生跳变,使触发器的输出由高电平跳变为原来的低电平,恒流源I 2断开,I 1再给C 充电,……如此周而复始,产生振荡。

若调整电路,使I 2=2I 1,则触发器输出为方波,经反相缓冲器由引脚9输出方波信号。

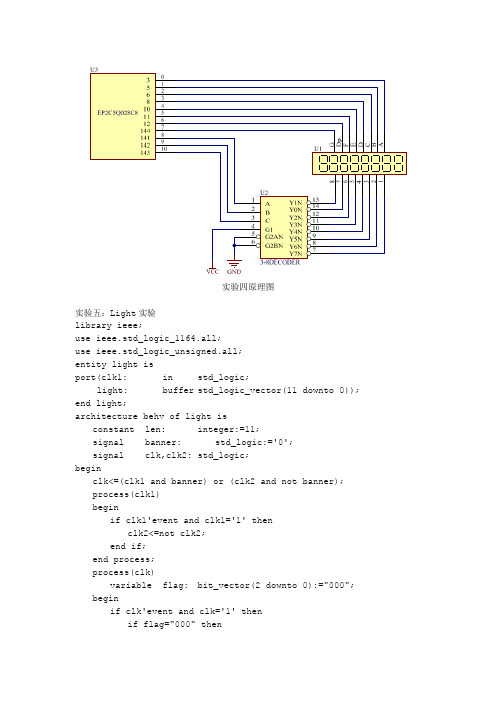

实验四原理图实验五:Light实验library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity light isport(clk1: in std_logic;light: buffer std_logic_vector(11 downto 0)); end light;architecture behv of light isconstant len: integer:=11;signal banner: std_logic:='0';signal clk,clk2: std_logic;beginclk<=(clk1 and banner) or (clk2 and not banner);process(clk1)beginif clk1'event and clk1='1' thenclk2<=not clk2;end if;end process;process(clk)variable flag: bit_vector(2 downto 0):="000";beginif clk'event and clk='1' thenif flag="000" thenlight<='1' & light(len downto 1);if light(1)='1' thenflag:="001";end if;elsif flag="001" thenlight<=light(len-1 downto 0) & '0';if light(10)='0' thenflag:="010";end if;elsif flag="010" thenlight(len downto 6)<=light(len-1 downto 6)&'1';light(len-6 downto 0)<='1'&light(len-6 downto 1);if light(1)='1' thenflag:="011";end if;elsif flag="011" thenlight(len downto 6)<='0'&light(len downto 7);light(len-6 downto 0)<=light(len-7 downto 0)&'0';if light(2)='0' thenflag:="100";end if;elsif flag="100" thenlight(len downto 6)<='1'&light(len downto 7);light(len-6 downto 0)<='1'&light(len-6 downto 1);if light(1)='1' thenflag:="101";end if;elsif flag="101" thenlight<="000000000000";flag:="111";elsif flag="111" thenbanner<=not banner;flag:="000";end if;end if;end process;end behv;实验结构框图LED阵列结构--元件例化library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity ledall isport(clkin :in std_logic;outera:out std_logic_vector(15 downto 0); outerb:out std_logic_vector(3 downto 0));end ledall;architecture beh of ledall iscomponent pinport(f1m :in std_logic;f800 :out std_logic);end component;component source1port(clk :in std_logic;outer:out std_logic_vector(7 downto 0));end component;component source2port(clk :in std_logic;iner :in std_logic_vector(3 downto 0);outer:out std_logic_vector(3 downto 0));end component;component rom1port(address:in STD_LOGIC_VECTOR (7 DOWNTO 0);inclock:in STD_LOGIC ;q :out STD_LOGIC_VECTOR (15 DOWNTO 0));end component;signal sig0,sig1,sig2:std_logic;signal temp:std_logic_vector(7 downto 0);beginsig1<=not sig0;sig2<=not sig0;U1:source1 port map(sig0,temp(7 downto 0));U2:source2 port map(sig1,temp(3 downto 0),outerb(3 downto 0)); U3:rom1 port map(temp(7 downto 0),sig2,outera(15 downto 0)); U4:pin port map(clkin,sig0);end beh;--分频程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity pin isport(f1m:in std_logic;f800:out std_logic);end pin;architecture behave of pin issignal Count : integer range 0 to 4999;beginDivideCLK :process(f1m)--对1M的信号1000分频 1KHzbeginif (f1m'event and f1m = '1')thenif Count<2499 then f800<='0';Count<=Count+1;elsif Count<4999 then f800<= '1';Count <= Count+1;elsif Count>=4999 then f800<='0';Count<=0; end if;end if;end process;end behave;ROM1程序:LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY rom1 ISPORT(address : IN STD_LOGIC_VECTOR (7 DOWNTO 0);inclock : IN STD_LOGIC ;q : OUT STD_LOGIC_VECTOR (15 DOWNTO 0));END rom1;ARCHITECTURE SYN OF rom1 ISSIGNAL sub_wire0 : STD_LOGIC_VECTOR (15 DOWNTO 0);COMPONENT lpm_romGENERIC (lpm_width : NATURAL;lpm_widthad : NATURAL;lpm_address_control : STRING;lpm_outdata : STRING;lpm_file : STRING);PORT (address : IN STD_LOGIC_VECTOR (7 DOWNTO 0);inclock : IN STD_LOGIC ;q : OUT STD_LOGIC_VECTOR (15 DOWNTO 0));END COMPONENT;BEGINq <= sub_wire0(15 DOWNTO 0);lpm_rom_component : lpm_romGENERIC MAP (LPM_WIDTH => 16,LPM_WIDTHAD => 8,LPM_ADDRESS_CONTROL => "REGISTERED",LPM_OUTDATA => "UNREGISTERED",LPM_FILE => "rom1.mif")PORT MAP (address => address,inclock => inclock,q => sub_wire0);END SYN;rom1:rom1_inst : rom1 PORT MAP(address => address_sig,inclock => inclock_sig,q => q_sig);Soucel:library IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_arith.all;entity source isport(clk:in std_logic;outer:out integer range 0 to 255);end source;architecture behave of source isbeginprocess(clk)variable temp:integer range 0 to 255;beginif(clk'event and clk='1')then temp:=temp+1; end if;outer<=temp;end process;end behave;soucel1:--Source1 地址寻址信号library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity source1 isport(clk:in std_logic;outer:out std_logic_vector(7 downto 0));end source1;architecture behave of source1 issignal temp1:std_logic_vector(3 downto 0);--temp1为地址低4位代表一帧数据signal temp2:std_logic_vector(3 downto 0);--temp1为地址高4位代表帧数signal time:integer range 0 to 15;--time为帧循环次数计数每帧扫16遍beginprocess(clk)beginif(clk'event and clk='1')thenif temp1="1111" thenif time<15 then time<=time+1;else time<=0;temp2<=temp2+'1';end if;end if;temp1<=temp1+'1'; --转为下帧数据end if;end process;outer<=temp2 & temp1;end behave;八位十进制频率计实验:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity freq isport(clk :in std_logic;--1Hz 标准时钟fs_in :in std_logic;--被测时钟dout :out std_logic_vector (31 downto 0)--被测时钟频率值);end freq;architecture ex4 of freq issignal clr_cnt :std_logic;--清零测频计数器signal en_cnt :std_logic;--使能测频计数器signal load :std_logic;--加载测量值signal div2clk :std_logic;signal d_temp :std_logic_vector (31 downto 0);--被测时钟频率值缓存器signal c :std_logic_vector (7 downto 0);--进位链component cnt10 isport(clk :in std_logic;--计数时钟clr :in std_logic;--复位ena :in std_logic;--使能qout :out std_logic_vector (3 downto 0);--10进制计数输出car_out :out std_logic --进位);end component;begin--2分频clkprocess(clk)beginif clk'event and clk = '1' thendiv2clk <= not div2clk;end if;end process;--产生控制信号clr_cnt <= '1' when clk = '0' and div2clk = '0' else'0';load <= not div2clk;en_cnt <= div2clk;process(load)beginif load'event and load = '1' thendout <= d_temp;end if;end process;u1 : cnt10 PORT MAP(clk=>fs_in,clr=>clr_cnt,ena=>en_cnt,qout=>d_temp(3 downto 0),car_out=>c(0));u2 : cnt10 port map(clk=>c(0), clr=>clr_cnt,ena=>en_cnt,qout=>d_temp(7 downto 4),car_out=>c(1));u3 : cnt10 port map(clk=>c(1), clr=>clr_cnt,ena=>en_cnt,qout=>d_temp(11 downto 8),car_out=>c(2));u4 : cnt10 port map(clk=>c(2), clr=>clr_cnt,ena=>en_cnt,qout=>d_temp(15 downto 12),car_out=>c(3));u5 : cnt10 port map(clk=>c(3), clr=>clr_cnt,ena=>en_cnt,qout=>d_temp(19 downto 16),car_out=>c(4));u6 : cnt10 port map(clk=>c(4), clr=>clr_cnt,ena=>en_cnt,qout=>d_temp(23 downto 20),car_out=>c(5));u7 : cnt10 port map(clk=>c(5), clr=>clr_cnt,ena=>en_cnt,qout=>d_temp(27 downto 24),car_out=>c(6));u8 : cnt10 port map(clk=>c(6), clr=>clr_cnt,ena=>en_cnt,qout=>d_temp(31 downto 28),car_out=>c(7)); end ex4;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt10 isport(clk :in std_logic;--计数时钟clr :in std_logic;--复位ena :in std_logic;--使能qout :out std_logic_vector (3 downto 0);--10进制计数输出car_out :out std_logic --进位);end cnt10;architecture ex5 of cnt10 issignal qout_t :std_logic_vector (3 downto 0);begin--10进制计数process(clk,clr)beginif clr = '1' thenqout_t <= x"0";elsif clk'event and clk = '1' thenif ena = '1' thenif qout_t < 9 thenqout_t <= qout_t + '1';elseqout_t <= x"0";end if;end if;end if;end process;--产生进位car_out <= '1' when qout_t = x"9" else'0';qout <= qout_t;end ex5;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity LED isport(din :in std_logic_vector (3 downto 0);dout :out std_logic_vector (7 downto 0) );end entity;architecture ex3 of LED isbeginprocess(din)begincase din iswhen "0000"=> dout <= "00111111";--"0"when "0001"=> dout <= "00000110";--"1"when "0010"=> dout <= "01011011";--"2"when "0011"=> dout <= "01001111";--"3"when "0100"=> dout <= "01100110";--"4"when "0101"=> dout <= "01101101";--"5"when "0110"=> dout <= "01111101";--"6"when "0111"=> dout <= "00000111";--"7"when "1000"=> dout <= "01111111";--"8"when "1001"=> dout <= "01101111";--"9"when "1010"=> dout <= "01110111";--"a"when "1011"=> dout <= "01111100";--"b"when "1100"=> dout <= "00111001";--"c"when "1101"=> dout <= "01011110";--"d"when "1110"=> dout <= "01111001";--"e"when "1111"=> dout <= "01110001"; --"f"when others => dout <= "00000000";end case;end process;end architecture;数字时钟原理图library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity clock isport(clk:in std_logic;--时钟输入20MHzclr:in std_logic;--清零端en:in std_logic;--暂停信号mode:in std_logic;--控制信号,用于选择模式inc:in std_logic;--置数信号seg7:out std_logic_vector(6 downto 0);--7段显示控制信号scan:out std_logic_vector(5 downto 0));--数码管地址选择信号end;architecture one of clock issignal state:std_logic_vector(1 downto 0);--定义4种状态signal qhh,qhl,qmh,qml,qsh,qsl:std_logic_vector(3 downto 0);--小时、分、秒的高位和地位signal data:std_logic_vector(3 downto 0);signal cnt:integer range 0 to 5;--扫描数码管的计数器signal clk1khz,clk1hz,clk2hz:std_logic;--1kHz、1Hz、2Hz的分频信号signal blink:std_logic_vector(2 downto 0);--闪烁信号signal inc_reg:std_logic;signal sec,min:integer range 0 to 59;signal hour:integer range 0 to 23;beginprocess(clk)--20000分频,产生1kHz信号,用于扫描数码管variable count:integer range 0 to 9999;beginif clk'event and clk='1' thenif count=9999 then clk1khz<=not clk1khz;count:=0;else count:=count+1;end if;end if;end process;process(clk1khz)--1000分频,产生1Hz信号,用于计时variable count:integer range 0 to 499;beginif clk1khz'event and clk1khz='1' thenif count=499 then clk1hz<=not clk1hz;count:=0;else count:=count+1;end if;end if;end process;process(clk1khz)--500分频,产生2Hz信号,用于数码管闪烁variable count:integer range 0 to 249;beginif clk1khz'event and clk1khz='1' thenif count=249 then clk2hz<=not clk2hz;count:=0;else count:=count+1;end if;end if;end process;process(mode,clr)--模式转换beginif clr='1' then state<="00";elsif mode'event and mode='1' thenstate<=state+1;end if;end process;process(clk1hz,state,en,clr,hour,sec,min)--状态控制beginif en='1' thenhour<=hour;min<=min;sec<=sec;elsif clr='1' thenhour<=0;min<=0;sec<=0;elsif clk1hz'event and clk1hz='1' then case state iswhen "00"=> --模式0,正常计时if sec=59 then sec<=0;if min=59 then min<=0;if hour=23 then hour<=0;else hour<=hour+1;end if;else min<=min+1;end if;else sec<=sec+1;end if;when "01"=> --模式1,设定小时时间if inc='1' thenif inc_reg='0' then inc_reg<='1';if hour=23 then hour<=0;else hour<=hour+1;end if;end if;else inc_reg<='0';end if;when "10"=> --模式2,设定分钟时间if inc='1' thenif inc_reg='0' then inc_reg<='1';if min=59 then min<=0;else min<=min+1;end if;end if;else inc_reg<='0';end if;when "11"=> --模式3,设定秒钟时间if inc='1' thenif inc_reg='0' then inc_reg<='1';if sec=59 then sec<=0;else sec<=sec+1;end if;end if;else inc_reg<='0';end if;end case;end if;end process;process(state,clk2hz)--当进行时间设定时,令数码管闪烁begincase state iswhen"00"=>blink<="000";when"01"=>blink<=(2=>clk2hz,others=>'0');when"10"=>blink<=(1=>clk2hz,others=>'0');when"11"=>blink<=(0=>clk2hz,others=>'0');when others=>null;end case;end process;process(sec)--秒计数的十进制转BCD码begincase sec iswhen 0|10|20|30|40|50=>qsl<="0000";when 1|11|21|31|41|51=>qsl<="0001";when 2|12|22|32|42|52=>qsl<="0010";when 3|13|23|33|43|53=>qsl<="0011";when 4|14|24|34|44|54=>qsl<="0100";when 5|15|25|35|45|55=>qsl<="0101";when 6|16|26|36|46|56=>qsl<="0110";when 7|17|27|37|47|57=>qsl<="0111";when 8|18|28|38|48|58=>qsl<="1000";when 9|19|29|39|49|59=>qsl<="1001";when others=>null;end case;case sec iswhen 0|1|2|3|4|5|6|7|8|9=>qsh<="0000";when 10|11|12|13|14|15|16|17|18|19=>qsh<="0001";when 20|21|22|23|24|25|26|27|28|29=>qsh<="0010";when 30|31|32|33|34|35|36|37|38|39=>qsh<="0011";when 40|41|42|43|44|45|46|47|48|49=>qsh<="0100";when 50|51|52|53|54|55|56|57|58|59=>qsh<="0101";when others=>null;end case;end process;process(min)--分计数的十进制转BCD码begincase min iswhen 0|10|20|30|40|50=>qml<="0000";when 1|11|21|31|41|51=>qml<="0001";when 2|12|22|32|42|52=>qml<="0010";when 3|13|23|33|43|53=>qml<="0011";when 4|14|24|34|44|54=>qml<="0100";when 5|15|25|35|45|55=>qml<="0101";when 6|16|26|36|46|56=>qml<="0110";when 7|17|27|37|47|57=>qml<="0111";when 8|18|28|38|48|58=>qml<="1000";when 9|19|29|39|49|59=>qml<="1001";when others=>null;end case;case min iswhen 0|1|2|3|4|5|6|7|8|9=>qmh<="0000";when 10|11|12|13|14|15|16|17|18|19=>qmh<="0001";when 20|21|22|23|24|25|26|27|28|29=>qmh<="0010";when 30|31|32|33|34|35|36|37|38|39=>qmh<="0011";when 40|41|42|43|44|45|46|47|48|49=>qmh<="0100";when 50|51|52|53|54|55|56|57|58|59=>qmh<="0101";when others=>null;end case;end process;process(hour)--小时计数的十进制转BCD码begincase hour iswhen 0|10|20=>qhl<="0000";when 1|11|21=>qhl<="0001";when 2|12|22=>qhl<="0010";when 3|13|23=>qhl<="0011";when 4|14=>qhl<="0100";when 5|15=>qhl<="0101";when 6|16=>qhl<="0110";when 7|17=>qhl<="0111";when 8|18=>qhl<="1000";when 9|19=>qhl<="1001";when others=>null;end case;case hour iswhen 0|1|2|3|4|5|6|7|8|9=>qhh<="0000";when 10|11|12|13|14|15|16|17|18|19=>qhh<="0001";when 20|21|22|23=>qhh<="0010";when others=>null;end case;end process;process(clk1khz)--数码管动态扫描计数beginif clk1khz'event and clk1khz='1' thenif cnt=5 then cnt<=0;else cnt<=cnt+1;end if;end if;end process;process(cnt,qhh,qhl,qmh,qml,qsh,qsl,blink)begincase cnt iswhen 0=>data<=qsl or (blink(0)&blink(0)&blink(0)&blink(0));scan<="000001";when 1=>data<=qsh or (blink(0)&blink(0)&blink(0)&blink(0));scan<="000010";when 2=>data<=qml or (blink(1)&blink(1)&blink(1)&blink(1));scan<="000100";when 3=>data<=qmh or (blink(1)&blink(1)&blink(1)&blink(1));scan<="001000";when 4=>data<=qhl or (blink(2)&blink(2)&blink(2)&blink(2));scan<="010000";when 5=>data<=qhh or (blink(2)&blink(2)&blink(2)&blink(2));scan<="100000";when others=>null;end case;end process;process(data)--7段译码begincase data iswhen "0000"=>seg7<="1111110";when "0001"=>seg7<="0110000";when "0010"=>seg7<="1101101";when "0011"=>seg7<="1111001";when "0100"=>seg7<="0110011";when "0101"=>seg7<="1011011";when "0110"=>seg7<="1011111";when "0111"=>seg7<="1110000";when "1000"=>seg7<="1111111";when "1001"=>seg7<="1111011";when others=>seg7<="0000000";end case;end process;end;。

南京理工大学EDA设计(Ⅰ)实验报告作者: 学号:91211学院(系):自动化学院专业: 自动化实验日期:2014年10月20日至24日2014 年 10 月目录实验一单级放大电路的设计与仿真实验二差动放大电路的设计与仿真实验三负反馈放大电路的设计与仿真实验四阶梯波发生器电路的设计设计一—单级放大电路设计一、实验要求1.设计一个分压偏置的单管电压放大电路,要求信号源频率20kHz,峰值5mV ,负载电阻1.8kΩ,电压增益大于50。

2.调节电路静态工作点,观察电路出现饱和失真和截止失真的输出信号波形,并测试对应的静态工作点值。

3.在正常放大状态下测试:①电路静态工作点值;②三极管的输入、输出特性曲线和 、r be 、r ce值;③电路的输入电阻、输出电阻和电压增益;④电路的频率响应曲线和f L、f H值。

二、实验过程1.实验原理图2.实验状态测试图(a)饱和失真失真原因:静态工作点Q电压值设置偏低,Q点偏左。

此时静态工作点:Ic=5.866mA Ib=162.826uA Uce=105.84mV(b)截止失真失真原因:静态工作点Q电压值设置的过高,Q点偏右。

此时静态工作点Ib=8.308uA Ic=1.532mA Uce=8.929V3.在正常放大状态下测试(a)正常放大电路静态工作点测量值ib=44.779uA ic=5.545mA Uce=0.866v β=ic/ib=123.82(b) 利用输入特性曲线求RbeRbe=dx/dy=1/(1.415m)=0.707kΩ(c)利用输出特性曲线求RceRce=dx/dy=1/(548.2092u)=1.824kΩ(d)求放大倍数实验放大倍数实验放大倍数 Au=-293.778mV/3.535mV=-83.106β=123.82理论值Au=-β(Rc//Rl//Rce)/Rbe=-123.82 (1k//1.8k//1.824k)/ 0.707k =-83.246 误差分析,相对不确定度E=|83.246-83.106|/83.246=0.17%(e)测量输入电阻和输出电阻1) 利用万能表法测量输入电阻输入电阻测量值R=3535/8.42=419.83Ω理论值R=Rb1//Rb2//Rbe=1.8k//2k//0.707k=404.86Ω误差分析:相对不确定度E=|419.83-404.86|/404.86=3.70% 2) 利用万能表法测量输出电阻输出电阻测量值Ro=3.535m//5.441u=0.65kΩ理论值Ro=Rc//Rce =1k//1.824k=0.646k误差分析:相对不确定度E=|0.65-0.646|/0.646=0.62%4.电路的幅频和相频特性图f=2.69kHz; f H=1.13MHzL分析实验结果第一个实验刚开始做很艰难,很多知识都忘记了,一边翻书一边做的,然后回头看时发现,电路刚开始就失真了,又重做的。

实验1-------用原理图输入法设计四位全加器实验2------计数译码显示电路设计实验3-----计数器的设计LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY counter ISPORT(ld,ce,clk,rst:IN STD_LOGIC;d:IN STD_LOGIC_VECTOR(7 DOWNTO 0);q:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END counter;ARCHITECTURE behave OF counter IS SIGNAL count:STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINPROCESS(clk,rst)BEGINIF rst='1' THEN count<=(OTHERS=>'0');ELSIF RISING_EDGE(clk) THENIF ld='1' THEN count<=d;ELSIF ce='1' THENcount<=count+1;END IF;END IF;END PROCESS;q<=count;END behave;实验4----序列检测器设计----学习用CASE语句描述序列检测器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY CHK ISPORT( din: IN STD_LOGIC;clk,clr:IN STD_LOGIC;d:IN STD_LOGIC_VECTOR(7 DOWNTO 0);AB: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END CHK;ARCHITECTURE behav OF CHK ISSIGNAL Q:INTEGER RANGE 0 TO 8;BEGINPROCESS(clk,clr)BEGINIF clr='1' THEN Q<=0;ELSIF clk'EVENT AND clk='1' THENCASE Q ISWHEN 0=> IF din=d(7) THEN Q<=1;ELSE Q<=0;END IF ;WHEN 1=> IF din=d(6) THEN Q<=2;ELSE Q<=0;END IF ;WHEN 2=> IF din=d(5) THEN Q<=3;ELSE Q<=0;END IF ;WHEN 3=> IF din=d(4) THEN Q<=4;ELSE Q<=0;END IF ;WHEN 4=> IF din=d(3) THEN Q<=5;ELSE Q<=0;END IF ;WHEN 5=> IF din=d(2) THEN Q<=6;ELSE Q<=0;END IF ;WHEN 6=> IF din=d(1) THEN Q<=7;ELSE Q<=0;END IF ;WHEN 7=> IF din=d(0) THEN Q<=8;ELSE Q<=0;END IF ;WHEN OTHERS =>Q<=0;END CASE;END IF;END PROCESS;PROCESS(Q)BEGINIF Q=8 THENAB<="1010";ELSE AB<="1011";END IF;END PROCESS;END behav;实验5----脉宽可调的发波信号发生器设计LCNT8.vhdLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY LCNT8 ISPORT(CLK,LD:IN STD_LOGIC;D:IN INTEGER RANGE 0 TO 255;CAO:OUT STD_LOGIC);END LCNT8;ARCHITECTURE behav OF LCNT8 ISSIGNAL COUNT:INTEGER RANGE 0 TO 255; BEGINPROCESS(CLK)BEGINIF CLK'EVENT AND CLK='1'THENIF LD='1'THENCOUNT<=D;ELSE COUNT<=COUNT+1;END IF;END IF;END PROCESS;PROCESS(COUNT)BEGINIF COUNT=255 THEN CAO<='1';ELSE CAO<='0';END IF;END PROCESS;END behav;PULSE.vhdLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY PULSE ISPORT(CLK:IN STD_LOGIC;A,B:IN STD_LOGIC_VECTOR(7 DOWNTO 0);PSOUT:OUT STD_LOGIC); END PULSE;ARCHITECTURE mixed OF PULSE IS COMPONENT LCNT8PORT(CLK,LD:IN STD_LOGIC; D:IN STD_LOGIC_VECTOR(7 DOWNTO 0);CAO:OUT STD_LOGIC); END COMPONENT;SIGNAL CAO1,CAO2:STD_LOGIC; SIGNAL LD1,LD2:STD_LOGIC;SIGNAL PSINT:STD_LOGIC; BEGINU1:LCNT8 PORT MAP(CLK=>CLK,LD=>LD1,D=>A,CAO=>CAO1); U2:LCNT8 PORT MAP(CLK=>CLK,LD=>LD2,D=>B,CAO=>CAO2); PROCESS(CAO1,CAO2) BEGINIF CAO1='1'THEN PSINT<='0';ELSIF CAO2'EVENT AND CAO2='1'THEN PSINT<='1'; END IF;END PROCESS; LD1<=NOTPSINT;LD2<=PSINT;PSOUT<=PSINT; END mixed;实验6----序列检测器设计----学习用状态机设计序列检测器library ieee;use ieee.std_logic_1164.all; entity jcq isport(clk,xi:in std_logic;z:out std_logic); end jcq;architecture one of jcq istype state_type is (s0,s1,s2,s3,s4,s5,s6,s7); signal present_state,next_state:state_type; beginstate_comb:process(present_state,xi) begincase present_state is when s0=>z<='0';if xi='1' then next_state<=s1;else next_state<=s0; end if;when s1=>z<='0';if xi='1' then next_state<=s2; else next_state<=s0; end if;when s2=>z<='0';if xi='1' then next_state<=s3; else next_state<=s0; end if;when s3=>z<='0';if xi='1' then next_state<=s3; else next_state<=s4; end if;when s4=>z<='0';if xi='1' then next_state<=s1; else next_state<=s5; end if;when s5=>z<='0';if xi='1' then next_state<=s6; else next_state<=s0; end if;when s6=>z<='0';if xi='1' then next_state<=s2; else next_state<=s7; end if;when s7=>z<='1';if xi='1' then next_state<=s1;else next_state<=s0;end if;end case;end process state_comb;state_clk:process(clk)beginif clk'event and clk='1' thenpresent_state<=next_state;end if;end process state_clk;end one;实验7----8位十进制数字频率计设计LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY testctl ISPORT(clk:IN STD_LOGIC;cnt_ena,cnt_clr,load:OUT STD_LOGIC); END testctl;ARCHITECTURE behav OF testctl IS SIGNAL div2clk:STD_LOGIC;BEGINPROCESS(clk)BEGINIF clk'EVENT AND clk='1' THENdiv2clk<=NOT div2clk;END IF;END PROCESS;PROCESS(clk,div2clk)BEGINIF clk='0' AND div2clk='0' THEN cnt_clr<='1';ELSEcnt_clr<='0';END IF;END PROCESS;load<=NOT div2clk;cnt_ena<=div2clk;END behav;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY reg ISPORT(load:IN STD_LOGIC;din:IN STD_LOGIC_VECTOR(3 DOWNTO 0); dout:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END reg;ARCHITECTURE behav OF reg IS BEGINPROCESS(load,din) BEGINIF load'EVENT AND load='1' THEN dout<=din; END IF; END PROCESS;END behav;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY cnt ISPORT(clk,clr,ena:IN STD_LOGIC;outy:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);cout:OUT STD_LOGIC); END cnt;ARCHITECTURE behav OF cnt ISSIGNAL q:STD_LOGIC_VECTOR(3 DOWNTO 0); BEGINPROCESS(clk,clr,ena) BEGINIF clr='1' THEN q<="0000";ELSIF(clk'EVENT AND clk='1') THEN IF ena='1' THENIF q="1000" THENq<=q+1;cout<='1'; ELSIF q="1001" THENcout<='0';q<="0000"; ELSE q<=q+1;cout<='0'; END IF; END IF; END IF; outy<=q; END PROCESS; END behav;实验8---8路彩灯控制器设计LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY mux21 ISPORT(a,b,s:IN STD_LOGIC; y:OUT STD_LOGIC); END mux21;ARCHITECTURE ar OF mux21 IS BEGINPROCESS(a,b,s) BEGINIF s='0' THEN y<=a; ELSE y<=b; END IF; END PROCESS;END ar;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY fen2 ISPORT(clk:IN STD_LOGIC; clkk:OUT STD_LOGIC); END fen2;ARCHITECTURE behav OF fen2 IS BEGINPROCESS(clk) VARIABLE clkk1:STD_LOGIC:='0'; BEGINIF clk'EVENT AND clk='1' THEN clkk1:=NOT clkk1; END IF; clkk<=clkk1; END PROCESS; END behav;LIBRARY IEEE;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY cd ISPORT(clk:IN STD_LOGIC;jp:OUT STD_LOGIC;qq:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END cd;ARCHITECTURE behav OF cd ISCONSTANT w:INTEGER:=7;SIGNAL q:STD_LOGIC_VECTOR(7 DOWNTO 0); BEGINPROCESS(clk)VARIABLE flag:BIT_VECTOR(2 DOWNTO 0):="000";VARIABLE jp1:STD_LOGIC:='0';BEGINIF clk'EVENT AND clk='1' THENIF flag="000" THENq<='1' & q(w DOWNTO 1);IF q(1)='1' THENflag:="001";END IF;ELSIF flag="001" THENq<=q(w-1 DOWNTO 0) & '0';IF q(6)='0' THENflag:="010";END IF;ELSIF flag="010" THENq(w DOWNTO 4)<=q(w-1 DOWNTO 4) & '1';q(w-4 DOWNTO 0)<='1' & q(w-4 DOWNTO 1);IF q(1)='1' THENflag:="011";END IF;ELSIF flag="011" THENq(w DOWNTO 4)<=q(w-1 DOWNTO 4) & '0';q(w-4 DOWNTO 0)<='0' & q(w-4 DOWNTO 1);IF q(1)='0' THENflag:="100";END IF;ELSIF flag="100" THENq(w DOWNTO 4)<='1' & q(w DOWNTO 5);q(w-4 DOWNTO 0)<=q(w-5 DOWNTO 0) & '1';IF q(4)='1' THENflag:="101";END IF;ELSIF flag="101" THENq(w DOWNTO 4)<='0' & q(w DOWNTO 5);q(w-4 DOWNTO 0)<=q(w-5 DOWNTO 0) & '0';IF q(4)='0' THENflag:="110";END IF;ELSIF flag="110" THENq(w DOWNTO 4)<='1' & q(w DOWNTO 5);q(w-4 DOWNTO 0)<='1' & q(w-4 DOWNTO 1);IF q(1)='1' THENflag:="111";END IF;ELSIF flag="111" THENq<="00000000";jp1:=NOT jp1;flag:="000";END IF;END IF;qq<=q;jp<=jp1;END PROCESS;END behav;。

实验1:

一位全加器:

设计的原理图如下所示:

VHDL源程序如下(行为描述)的RTL与technology map视图

VHDL源程序如下(数据流描述)的RTL与technology map视图:

VHDL源程序如下(结构化描述)的RTL与technology map视图:

功能仿真波形如下:

时序仿真波形如下:

4位全加器:

4位全加器:原理图设计如下(结构化描述):

原理图设计如下(结构化描述)的RTL与technology map视图:

VHDL源程序如下(结构化描述)的RTL与technology map视图:

最终的功能仿真波形如下:

最终的时序仿真波形如下:

实验2:RTL 视图程序A:

程序B;

Technology Map视图:A-B-C

最终的时序波形及输出延时:程序A 时序仿真波形

输出延时的波形及时间

程序B 时序仿真波形

输出延时的波形及时间

程序C时序仿真波形

无输出延时的波形及时间

重新设定clk的时钟频率大于1中的最大工作频率时观察时序仿真波形:程序A 时序仿真波形:

程序B 时序仿真波形:

程序C 时序仿真波形:

实验3:

最终的顶层设计原理图:

时序仿真图如下:

实验四原理图。