EDA技术基础-常用仿真分析

- 格式:ppt

- 大小:1.10 MB

- 文档页数:6

电子EDA技术的基础知识现代电子设计技术的核心就是EDA技术。

EDA技术是一门综合性学科,它打破了软件和硬件间的壁垒,代表了电子设计技术和应用技术的发展方向。

本文将带你一起来了解关于EDA的分类、基本特征、应用、常用软件以及发展前景。

电子设计自动化(Electronic Design Automation)的缩写即是EDA.EDA技术是把计算机技术应用在电子设计过程的一门技术,从而实现了电子设计的自动化进行,现今EDA技术已经广泛用于电子电路的设计仿真以及集成电路版图设计、印刷电路板的设计和可编程器件的编程等工作中。

EDA技术是一门综合的学科,它代表了未来电子设计技术的发展方向,打破了软硬件之间的隔阂。

一、EDA的分类我们依据计算机辅助技术介入程度的不同,将电子系统设计分为以下三类:1.人工的设计方法此种设计方法从提出方案到验证方案等等均需要由人工来完成,并且方案的验证必须搭建实际的电路来完成验证。

这种人工的设计方法缺陷在于:开销特别大,但是效率却极低,并且周期比较长,还有一点就是现在的产品不是单单靠人工就能够完成的。

2.计算机辅助设计CAD1970年以来,计算机开始被应用于Ic版图设计以及PCB布局布线,后来发展为可对电路功能和结构进行设计,并且在原来的基础上增添了逻辑仿真、自动布局布线等等的功能。

可以这么说CAD技术的应用取得了可喜的成果。

但我们也不能过于乐观,因为各种各样的软件层出不穷,每一种设计软件只能够解决一部分的问题,这就造成了软件不能完全脱离人去设计,智能化程度不能够满足人们的需求。

3.EDA电子设计自动化1990年以后是EDA时代的到来。

伴随着电子计算机的不断发展,计算机系统被广泛的应用于电子产品的设计和电子产品的测试以及电子产品的制造等各环节当中。

由于电子产品的性能不断提高以及精密度的增加,产品的更新所需要的时间越来越短。

相应的,电子产品的设计和电子产品的测试以及电子产品的制造也必须跟上更新的步伐。

技术是在电子CAD技术基础上发展起来的软件系统,是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。

利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从设计、性能分析到设计出IC 版图或版图的整个过程在计算机上自动处理完成。

现在对EDA的概念或范畴用得很宽。

包括在、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域,都有EDA的应用。

目前EDA技术已在各大公司、企事业单位和科研教学部门广泛使用。

例如在飞机过程中,从设计、性能及特性分析直到飞行模拟,都可能涉及到EDA技术。

本文所指的EDA技术,主要针对电子电路设计、PCB设计和IC设计。

EDA设计可分为系统级、电路级和物理实现级。

EDA常用软件EDA工具层出不穷,目前进入我国并具有广泛影响的EDA软件有:EWB、PSCE、、PCAD、Prol、ViewLogic、、Graphics、Synopsys、LSIlogic、、croSim 等等。

这些工具都有较强的功能,一般可用于几个方面,例如很多软件都可以进行电路设计与仿真,同时以可以进行PCB自动布局,可输出多种网表文件与第三方软件。

下面按主要功能或主要应用场合,分为电路设计与仿真工具、PCB设计软件、IC设计软件、PLD设计工具及其它EDA软件,进行简单介绍。

1、电子电路设计与仿真工具电子电路设计与仿真工具包括SPICE/PSPICE;EWB;;SystemView;MMICAD等。

下面简单介绍前三个软件。

(1)SPICE(Simulaon Prog with Integrated Circuit Emphasis)是由美国加州大学推出的电路分析仿真软件,是20世纪80年代世界上应用最广的电路设计软件,1998年被定为美国国家标准。

1984年,美国MicroSim公司推出了基于SPICE的微机版PSPICE(Peonal—SPICE)。

EDA仿真软件介绍EDA(Electronic Design Automation)是一类电子设计自动化软件,用于辅助电子产品的设计与仿真。

EDA软件帮助工程师在电子产品的设计过程中快速、准确地完成各种任务,从而提高设计效率和产品质量。

本文将介绍几款常见的EDA仿真软件,以及它们的特点和优势。

1. Cadence AllegroCadence Allegro是一款功能强大的EDA仿真软件。

它提供了完整的设计流程,包括原理图设计、PCB(Printed Circuit Board)布局和仿真。

Cadence Allegro可以帮助工程师快速设计复杂的电子电路,并进行各种信号和功耗仿真。

该软件具有直观的用户界面,易于学习和使用。

此外,Cadence Allegro还提供了丰富的库和模型,方便用户进行各种电路设计和仿真。

2. Mentor Graphics PADSMentor Graphics PADS是一款流行的EDA仿真软件,专门用于PCB设计和仿真。

它提供了直观的用户界面,支持多种设计工具和功能,如原理图设计、电路仿真、PCB布局和封装设计等。

此外,Mentor Graphics PADS还提供了强大的仿真和验证功能,可以帮助工程师检测电路的性能和可靠性问题,提高产品的质量。

3. Altium DesignerAltium Designer是一款专业的PCB设计和仿真软件。

它提供了完整的设计流程,包括原理图设计、PCB布局和仿真。

Altium Designer具有友好的用户界面,支持多种设计工具和功能,如自动布线、3D模拟和原理图捕捉等。

此外,Altium Designer还提供了丰富的库和模型,方便用户进行各种电路设计和仿真。

4. Ansys HFSSAnsys HFSS是一款强大的高频电磁场仿真软件。

它可以帮助工程师对射频(Radio Frequency)和微波(Microwave)电路进行仿真,包括天线设计、滤波器设计和射频电路设计等。

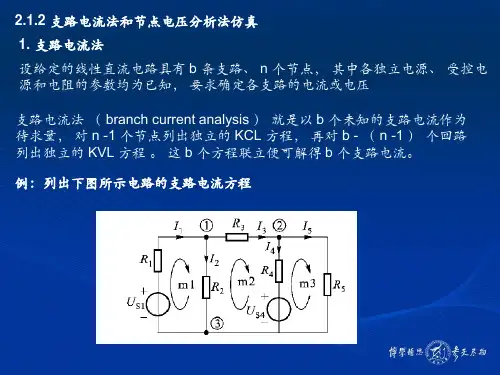

E D A基础总结综述部分1.EDA的中文全称为电子设计自动化,英文全名为Electronic Design Automation;2.EDA平台常用的两种输入电路的方法是:电路原理图输入法、HDL输入法;3.EDA平台工作流程:电路输入、综合优化、功能仿真、布局布线、门级仿真;数字电路部分1.EDA中常用的仿真语言为Verilog和VHDL;2.VHDL其英文全名为VHSIC Hardware Description Language,而VHSIC则是Very HighSpeed Intergeraterd Circuit的缩写词,意为甚高速集成电路,故VHDL其准确的中文译名为甚高速集成电路的硬件描述语言;3.Verilog HDL其英文全名为Verilog Hardware Decription Language,HDL中文译名为硬件描述语言;4.Verilog和VHDL的比较共同点:能形式化地抽象表示电路的行为和结构;支持逻辑设计中层次与范围的描述;可借用高级语言的精巧结构来简化电路行为的描述;具有电路仿真与验证机制以保证设计的正确性;支持电路描述由高层到低层的综合转换;硬件描述与实现工艺无关;便于文档管理;易于理解和设计重用;不同点:Verilog在系统级抽象方面略差,VHDL在门级开关电路方面略差;5.软核、固核和硬核软核:功能经过验证的、可综合的、实现后电路结构总门数在5000门以上的Verilog 模型;固核:在某一种现场可编程门列器件上实现的经验证是正确的,且总门数在5000门以上的电路结构编码文件;硬核:在某一种专用集成电路工艺的器件上实现的,经验证是正确的,且总门数在5000门以上的电路结构版图掩膜;6.自顶向下Top Down设计7.自底向上Down Top设计8.名词解释:ASIC:Application Specific Integrated Circuit,专用集成电路;FPGA:Field Programmable Gate Array,现场可编程门阵列;PLD:Programmable Logic Device,可编程逻辑器件;Verilog编程题:数据比较器2位//数据比较器module compare equal, a, b;input a,b;output equal;reg equal;always a or bif a == bequal = 1;elseequal = 0;endmodule//数据比较器测试代码`timescale 1ns/1ns`include "./1-1.v"module t;reg a,b;wire equal;initialbegina=0;b=0;100 a=0; b=1;100 a=1; b=1;100 a=1; b=0;100 a=0; b=0;100 $stop;endcompare m.equalequal, .aa, .bb; endmodule数据比较器8位module compare8equal, a, b;input 7:0a, b;output equal;reg equal;always a or bif a > bbeginequal = 1;endelsebeginequal = 0;endendmodule分频器module half_clkreset, clk_in, clk_out; input clk_in, reset;output clk_out;reg clk_out;always posedge clk_inbeginifreset clk_out = 0;else clk_out = ~clk_out;endendmodule10M时钟分频为500Kmodule fdivision RESET, MB, KB;input MB, RESET;output KB;reg KB;reg 7:0 j;always posedge MBif RESETbeginKB <= 0;j <= 0;endelsebeginif j == 19begin j <= 0;KB <= ~KB;endelsej <= j+1;endendmodule译码电路`define plus 3'd0`define minus 3'd1`define band 3'd2`define bor 3'd3`define unegate 3'd4module aluout, opcode, a, b;output7:0 out;reg7:0 out;input2:0 opcode;input7:0 a,b;always opcode or a or bbegincaseopcode`plus: out = a + b;`minus: out = a - b;`band: out = a & b;`bor: out = a | b;`unegate: out = ~a;default: out = 8'hx;endcaseendendmodule八路数据选择器module selecting8addr, in1, in2, in3, in4, in5, in6, in7, in8, dataout, reset; input 2:0 addr;input 3:0 in1,in2,in3,in4,in5,in6,in7,in8;input reset;output 3:0 dataout;reg 3:0 dataout;always addr or in1 or in2 or in3 or in4 or in5 or in6 or in7 or in8 or reset beginifresetcaseaddr3'b000: dataout = in1;3'b001: dataout = in2;3'b010: dataout = in3;3'b011: dataout = in4;3'b100: dataout = in5;3'b101: dataout = in6;3'b110: dataout = in7;3'b111: dataout = in8;endcaseelsedataout = 0;endendmodule逻辑运算电路module tryfunctclk, n, result, reset;output31:0 result;input3:0 n;input reset, clk;reg31:0 result;always posedge clkbeginif resetresult <=0;elsebeginresult <= nfactorialn/n2+1;endendfunction 31:0 factorial;input 3:0 operand;reg 3:0 index;beginfactorial = operand 1:0;for index = 2; index <= operand; index = index + 1 factorial = index factorial;endendfunctionendmodulemodule tryfunctclk, n, result, reset;output31:0 result;input3:0 n;input reset, clk;reg31:0 result;always posedge clkbeginif resetresult <=0;elsebeginresult <= nfactorialn/n2+1;endendfunction 31:0 factorial;input 3:0 operand;reg 3:0 index;beginfactorial = operand 1:0;for index = 2; index <= operand; index = index + 1 factorial = index factorial;endendfunctionendmodule高速排序组合逻辑module sort4ra, rb, rc, rd, a, b, c, d;output3:0 ra, rb, rc, rd;input3:0 a, b, c, d;reg3:0 ra, rb, rc, rd;reg3:0 va, vb, vc, vd;always a or b or c or dbegin{va, vb, vc, vd} = {a, b, c, d};sort2va, vc;sort2vb, vd;sort2va, vb;sort2vc, vd;sort2vb, vc;{ra, rb, rc, rd} = {va, vb, vc, vd};endtask sort2;input3:0x, y;reg3:0 tmp;if x > ybegintmp = x;x = y;y = tmp;endendtaskendmodule检测5位二进制序列10010module seqdetx, z, clk, rst, state;input x, clk, rst;output z;output2:0 state;reg2:0 state;wire z;parameter IDLE = 'd0, A = 'd1, B = 'd2, C = 'd3, D = 'd4, E = 'd5, F = 'd6, G = 'd7; assign z = state == E && x == 0 1:0;always posedge clkif rstbeginstate <= IDLE;endelsecase stateIDLE:if x == 1beginstate <= A;endA:if x == 0beginstate <= B;endB:if x == 0beginstate <= C;endelsebeginstate <= F;endC:if x == 1beginstate <= D;endelsebeginstate <= G;endD:if x == 0beginstate <= E;endelsebeginstate <= A;endE:if x == 0beginstate <= C;endelsebeginstate = A;endF:if x == 1beginstate <= A;endelsebeginstate <= B;endG:if x == 1beginstate <= F;enddefault:state = IDLE;endcaseendmodule模拟电路部分1.目前,集成电路最常用的材料是单晶硅;2.集成电路的生产由设计、制造、封装三部分组成;3.集成电路中基片主要制作工艺为:光刻、扩散、注入、刻蚀、键合;4.集成电路中基片的制造步骤为:光刻、扩散、注入、刻蚀;5.衡量集成电路产业水平的两个主要参数为:硅晶圆片直径和光刻精度特征尺寸;这两个参数在业界达到的水平为:硅晶圆片直径12英寸300mm,光刻精度0.13um;主流水平为:硅晶圆片直径200mm,光刻精度0.18um;6.模拟电路中常用的仿真算法是SPICE,英文全名为Simulation Program with IntegratedCircuit Emphasis;7.世界上设计EDA软件实力最强的两个公司为Cadence和Synopsys;其中,Cadence的优势为电路布局布线,Synopsys的优势为逻辑综合仿真;8.WorkBench是加拿大IIT公司推出的电子线路仿真软件;它可以对模拟、数字和模拟/数字混合电路进行仿真,克服了传统电子产品的设计受实验室客观条件限制的局限性,用虚拟的元件搭接各种电路,用虚拟的仪表进行各种参数和性能指标的测试;特点如下:1系统集成度高,界面直观,操作方便;2具备模拟、数字及模拟/数字混合电路仿真;3提供较为丰富的元器件库;4电路分析手段完备;5输出方式灵活;6兼容性好;9.SPICE语言举例:EXAMPLE 文件名任意名都可以但必须要有VCC 8 0 12 电源正极接于节点8 负极接于0 电压为12VVEE 0 9 12 电源正极接于节点0,负接接于节点9,电压为12V;VIN 1 0 AC 1 SIN0 0.1 5MEG 信号源VIN 接于1 和接点0;交流1V 进行交流分析同时加一个正弦信号直流偏置为0,振幅为0.1V频率为5M的交流信号源,进行瞬态分析; RC1 8 4 10K 电阻RC1 分别接于节点8 节点4;阻值为10K;RC2 8 5 10K 电阻RC2 分别接于节点8 节点5;阻值为10K;RS 2 1 1K 电阻RS 分别接于节点 1 节点0;阻值为1K;RS1 8 7 20K 电阻RS1 分别接于节点8 节点7 阻值为20K;RS2 3 0 1K 电阻RS2 分别接于节点3 节点0 阻值为1K;Q1 4 2 6 MOD1 三极管Q1 CBE 分别接于节点 4 2 6 模型为MOD1Q2 5 3 6 MOD1 三极管Q2 CBE 分别接于节点 5 3 6 模型为MOD1Q3 6 7 9 MOD1 三极管Q3 CBE 分别接于节点 6 7 9 模型为MOD1Q4 7 7 9 MOD1 三极管Q4 CBE 分别接于节点 7 7 9 模型为MOD1.OP 求出直流工作点.本电路共有9个节点;温度值为27度;.DC VIN -.15 .15 .01 DC为直流分析语句,分析输入电压从-0.15V 到0.15V扫描特性,每0.1V作一次分析;.PRINT DC V4 V5 .PRINT 为打印语句,其中DC是打印直流内容,这里规定打印节点4和5上的电位,既相对地参考点的电压随输入的变化关系;.PLOT DC V4 V5 .PLOT为绘图语句,其中DC表示绘制直流分析的传输特性,说明是绘制V4 V5的输出电压和VIN关系曲线;.TF V5 VIN .TF是转移函数分析语句,该句表示计算直流分析时,小信号输出电压V5和输入电压VIN的转移函数值,输入电阻和输出电阻;.AC DEC 10 25K 250MEG .AC是交流分析语句,是在规定的频率范围内从25K到250M进行频域分析DEC表示按数量级变化,10表示每一数量级中取的分析点数目; .PRINT AC VM5 VP5 打印AC分析VM5VP5的取点数;.PLOT AC VM5 VP5 绘制AC分析VM5VP5的取点数;.TRAN 4N 100N 1N .TRAN是瞬态分析语句,并规定了打印或绘图时间增量为4N秒,计算终止时间为100N秒,打印或绘图开始时间1NS;.PRINT TRAN V5 V4 .打印出4.5点的电压随时间变化;.PLOT TRAN V5 V4 .绘图出节点4.5的电压随时间变化;.END 结束语句...一定要有;。

EDA仿真功能及应用介绍1、仿真的目的:在软件环境下,验证电路的行为和设想中的是否一致。

2、仿真的分类:a) 功能仿真:在RTL层进行的仿真,其特点是不考虑构成电路的逻辑和门的时间延迟,着重考虑电路在理想环境下的行为和设计构想的一致性;b) 时序仿真:又称为后仿真,是在电路已经映射到特定的工艺环境后,将电路的路径延迟和门延迟考虑进对电路行为的影响后,来比较电路的行为是否还能够在一定条件下满足设计构想。

3、功能仿真的目的:a) 设计出能工作的电路:因此功能仿真不是一个孤立的过程,其和综合、时序分析等形成一个反馈工作过程,只有这个过程收敛,各个环节才有意义。

而孤立的功能仿真通过是没有意义的,如果在时序分析过程中发现时序不满足需要更改代码,则功能仿真必须从新进行。

因此正确的工作流程是:b)代码排错:功能仿真是代码排错的最重要的手段之一。

4、 modelsim的高级功能:Code Coveragea) 代码覆盖率是验证激励是否完备,检验代码质量的一个重要手段。

测试激励的代码覆盖率至少要达到95%以上,才能基本认为代码在逻辑上是通过质量控制的,才能进入综合步骤;b) 代码覆盖率是保证高质量代码的必要条件,但却不是充分条件。

即便代码行覆盖和分支覆盖都能够达到100%,也不能肯定的说代码已经得到100%的验证。

除非所有的分支覆盖都能够进行组合遍历。

c) 在大的设计中,如果想通过一个激励就验证完一个设计或者模块是不现实的。

一方面是从逻辑功能上很难做到;另外一方面是因为如果在一个激励中包括了各种情况,整个仿真过程的速度会随着计算机内存的消耗而成线性下降,效率低下。

d) 通常的做法是每一个激励只验证电路功能的某个方面。

整个电路的功能验证由数个激励共同完成。

在这种验证方法中代码覆盖率更显重要,因为可以通过代码覆盖率来控制激励对功能的覆盖程度。

e) modelsim的Code coverage不但能记录各个激励对代码的“行覆盖”和“分支覆盖”,而且能够将各个激励的覆盖记录进行合并,做到对覆盖率的全面监测。

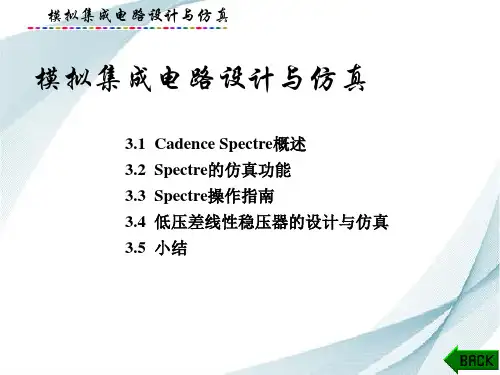

Cadence基础仿真分析与电路控制描述Cadence是一款主要用于集成电路设计和仿真分析的软件工具。

本文档将介绍Cadence的基础仿真分析功能以及电路控制描述的方法。

Cadence基础仿真分析Cadence提供了多种仿真分析工具,包括电路级仿真、时钟级仿真和系统级仿真等。

这些工具可用于验证电路设计的正确性,并进行性能评估。

在进行仿真分析之前,需要进行以下步骤:1. 设计:使用Cadence的设计工具创建电路图和原理图,定义电路的结构和功能。

2. 参数设置:对电路器件进行参数设置,包括电阻、电容、电感等元件的数值设定。

3. 仿真配置:选择适当的仿真工具和仿真设置,如仿真类型、仿真时间和仿真模型等。

接下来,执行仿真分析:1. 电路级仿真:通过电路级仿真工具,如Spectre,对电路进行验证和性能评估。

参数设置和仿真配置完成后,运行仿真并分析仿真结果。

2. 时钟级仿真:通过时钟级仿真工具,如Virtuoso AMS Designer,对电路中时序相关的功能进行验证。

设置时钟源和时钟周期等参数,并运行仿真以验证电路的时序性能。

3. 系统级仿真:通过系统级仿真工具,如Virtuoso System Design Platform,对整个电路系统进行仿真。

设置系统级的参数和信号源,并进行仿真分析。

电路控制描述在Cadence中,可以使用Verilog-A或Verilog-AMS等硬件描述语言来描述电路的行为和控制。

1. Verilog-A:主要用于模拟连续时间的电路。

可以使用Verilog-A描述电路的行为和相互之间的连接关系。

通过编写Verilog-A代码,可以实现电路的仿真和性能分析。

2. Verilog-AMS:结合了连续时间和离散时间的特性,可用于描述混合信号电路。

除了模拟电路行为之外,还可以描述数字电路部分。

通过编写Verilog-AMS代码,可以实现电路的混合仿真和性能分析。

使用这些硬件描述语言时,需要了解其语法和规范,并根据实际需求编写相应的代码。

图3.5-4 7位并串转换电路4.QuartusII仿真QuartusII的Waveform Editor及Simulator提供了便利的功能仿真与时序仿真功能,通过仿真波形报告可以直观地验证电路逻辑行为与时序的正确性。

Waveform Editor编辑仿真输入的矢量波形文件(Vector Waveform file,VWF)。

Simulator仿真VWF文件并计算输出波形数据。

为了便于分享交流,仿真波形图务必做到“完整、简明”的基本原则,即花最少的仿真时间清晰地呈现最多信息。

仿真常规步骤分为新建波形文件、添加仿真节点或总线信号、输入仿真激励、启动仿真、结果分析。

3.5.4 实验内容学习电路仿真基本方法;熟悉双向移位寄存器的原理及设计方法,通过仿真验证及硬件实验箱验证设计并完成报告。

1. 仿真验证用一片74194芯片连接好功能验证电路,如图3.5-5所示,通过功能仿真验证74194并入置数、异步清零、串行右移、串行左移、保持的逻辑行为,如图3.5-6所示。

图3.5-5 74194功能验证电路图3.5-6 74194功能仿真结果本例在电路编译后进行功能仿真,具体说明以下仿真步骤。

1)新建波形文件后的波形图参数设置网格宽度Grid size和时间轴长度End time是波形图的基本参数。

添加节点前设置好参数可以减少波形图重复调整时间开销。

网格宽度与时钟周期紧密相关,通常设置为时钟周期的四分之一、二分之一或整数倍。

时间轴长度默认1us,需要配合网格保证充裕的仿真时间。

2)添加节点或总线后的信号整合与位置分配添加节点或总线后的VWF文件如图3.5-7所示,信号杂乱需要重新调配位置与整合。

信号位置分配要注意:激励输入信号(I类)与待分析的输出信号(O类、R类、C类)上下放置,界限分明;时钟信号置顶,其他输入信号可按“异步控制→同步控制→数据输入”顺序向下放置;同一元器件的控制信号就近放置;同一功能的控制信号就近放置。

EDA仿真二—十进制译码器

Karia.Huang

所谓的二十进制编码器,就是将十进制的0~9编成二十进制码的电路。

输入1个0~9的十进制数,经过编码器编码,在其输出端输出的是相应的二十进制代码。

可以实现组合电路,也可以实现码制转换。

译码器还用于数据分配,存贮器寻址和组合控制信号等。

不同的功能可选用不同种类的译码器。

由十个与非门与八个非门构成的电路,它的功能是将BCD码的10个代码译成10个对应的高低电平输出信号,对BCD码以外的伪码1010—1111这几个代码输出均无低电平信号产生,对和几个代码构成拒绝功能。

4位输入代码共有十六个组合状态,其中六个没有与其对应的输出端,这六个代码称为伪码。

伪码输入时,十个输出端处于无效状态。

若输出端是低电平有效,则此时输出均为高电平。

以下为二—十进制译码器的基本结构:

用EDA仿真出的波形是:

参考其真值表:

当A0A1A2A3输入为0000—1001时,Y0—Y9分别输出对应的高低电平;

当A0A1A2A3输入为1010—1111时,Y0—Y9输出全为高电平。

仿真值与理论值一致,当输入BCD的是是个代码也就是0000—1001时,译码器将它们译成10个对应的低电平信号输出,而对BCD以为的伪码,就是1010—1111这6个代码则无低电平信号产生,译码器拒绝“翻译”,所以这个电路不仅仅可以翻译BCD码,而且

还有拒绝伪码的功能。

实验项目一:74LS318译码器的设计实验目的:1、通过一个简单的三-八译码器的设计,让学生掌握组合逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

3,初步了解QUARTUS II原理图输入设计的全过程。

二、实验的硬件要求:1、EDA2000实验箱(其他厂家具有同等配置试验箱均可),主要使用:输入:DIP拨码开关3位、输出:LED灯;2、主芯片:EP1K1OTC100-3(大于此规模的芯片亦可);3、计算机与QUARTUS 软件;三、实验原理三-译码器为三输入、八输出。

当输入信号按二进制方式的表示值为N时(输入端低电平有效),输出端从零到七,标号为N输出端输出低电平表示有信号产生,而其它则为高电平表示无信号产生。

因为三个输入端能产生的组合状态有八种,所以输出端在每种组合中仅有一位为低电平的情况下,能表示所有的输入组合,因此不需要像编码器实验那样再用一个输出端指示输出是否有效。

但可以在输入中加入一个输出使能端,用来指示是否将当前的输入进行有效的译码,当使能端指示输入信号无效或不用对当前信号进行译码时,输出端全为高电平,表示无任何信号。

本例设计中没有考虑使能输入端,自己设计时可以考虑加入使能输入端时,程序如何设计。

表8.1三-八译码器真值表输入输出A2 A1 A0 Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y00 0 0 0 0 0 0 0 0 0 10 0 1 0 0 0 0 0 0 1 00 1 0 0 0 0 0 0 1 0 00 1 1 0 0 0 0 1 0 0 01 0 0 0 0 0 1 0 0 0 01 0 1 0 0 1 0 0 0 0 01 1 0 1 0 0 0 0 0 01 1 1 1 0 0 0 0 0 0 0四、实验步骤:打开QUARTUS II,打开原理图编辑器,按图8.26进行原理图设计。

各逻辑符号放置在原理图上后,经检查保存原理图。

完成了原理图的输入后,我们就可以用前面介绍的软件的使用方法,对程序进行管脚的定义、编译、仿真、下载,完成整个实验的设计。

EDA技术的基础知识目录一、EDA技术概述 (2)1. EDA技术定义与发展历程 (3)2. EDA技术应用领域及重要性 (4)二、EDA工具软件介绍 (5)1. EDA软件分类与特点 (6)2. 常用EDA软件工具及其功能介绍 (8)三、数字电路设计基础 (9)1. 数字电路概述及特点 (11)2. 数字电路基本原理与器件类型 (12)3. 数字逻辑代数及逻辑设计基础 (14)四、模拟电路设计基础 (15)1. 模拟电路概述及特点 (17)2. 模拟电路基本原理与器件参数分析 (18)3. 模拟电路设计与仿真分析 (19)五、EDA设计流程与实现方法 (20)1. 设计需求分析 (22)2. 设计原理框图与功能验证 (23)3. 逻辑设计与仿真验证 (24)4. 物理设计与布局布线优化 (26)5. 测试验证与可靠性分析 (27)六、EDA技术中的关键概念与技术点解析 (28)1. 原理图输入与混合信号仿真技术解析 (29)2. 布局布线优化算法与技巧探讨 (30)3. 自动化测试生成与验证技术介绍 (32)4. EDA设计中的知识产权保护问题探讨等)进一步深入介绍不同章节内容34七、设计流程详细解析 (36)一、EDA技术概述EDA技术,即电子设计自动化(Electronic Design Automation),是电子工程领域的一门重要技术。

它利用计算机辅助设计(CAD)软件,来完成超大规模集成电路(VLSI)芯片的功能设计、综合、验证、物理设计等一系列流程。

EDA技术能够大大提高电子设计的效率和可靠性,降低设计成本,缩短产品上市时间。

随着半导体技术的飞速发展,集成电路(IC)的设计越来越复杂,传统的硬件描述语言(如Verilog HDL和VHDL)已经无法满足设计需求。

EDA技术应运而生,成为电子设计领域的重要工具。

EDA技术涵盖了数字电路设计和模拟电路设计两个方面。

数字电路设计主要关注逻辑电路的设计和实现,包括组合逻辑电路、时序逻辑电路等。