10G以上传输线和过孔建模

- 格式:pdf

- 大小:1.40 MB

- 文档页数:32

基于正态分布的10GGPON规模预测模型研究引言:随着宽带需求的不断增长,为满足用户对高速、稳定的宽带网络的需求,10G GPON(Gigabit Passive Optical Network)技术应运而生。

10G GPON是一种基于光纤传输的宽带接入技术,能够提供10Gbps的带宽,为用户提供更快、更稳定的网络连接。

在规划光纤网络时,准确预测10GGPON的规模是非常重要的。

过大的规模可能导致资源浪费,而过小的规模则无法满足用户需求。

因此,本文将基于正态分布,研究10GGPON规模预测模型。

方法:本研究基于正态分布构建了一个预测模型,用于预测10GGPON的规模。

首先,我们收集了历史的宽带需求数据。

然后,我们使用统计方法,分析这些数据的分布特征,并构建正态分布模型。

在正态分布模型中,我们使用平均值来表示光纤网络的平均需求,使用标准差来表示需求的变化范围。

通过对历史数据进行分析,我们计算出了平均值和标准差。

接下来,我们利用这个正态分布模型来预测未来的宽带需求。

首先,我们选择未来的时间段,并预测这段时间内的需求曲线。

然后,我们根据正态分布模型,计算出在该时间段内不同需求水平下的概率密度函数。

最后,我们根据概率密度函数,确定最佳的10GGPON规模。

结果:通过使用正态分布模型,我们成功地预测到了10GGPON的规模。

根据实际的宽带需求数据,我们计算出了平均值和标准差。

然后,我们通过预测未来的需求曲线,确定了最佳的10GGPON规模。

通过与实际情况的比较,我们发现,我们的预测模型具有很高的准确性。

讨论:本研究基于正态分布构建了一个预测模型,用于预测10GGPON的规模。

然而,我们也意识到,正态分布模型可能并不适用于所有情况。

在实际情况中,一些特殊因素(如节假日、活动等)可能会导致需求的突然增加或减少。

因此,在实际应用中,我们需要结合其他因素来修正模型。

此外,本研究还可以进一步完善。

我们可以收集更多的历史数据,并使用更多的统计方法来分析数据的分布特征。

过孔阻抗计算公式解释说明以及概述1. 引言1.1 概述过孔阻抗计算公式是在PCB(Printed Circuit Board,印刷电路板)设计和制造过程中非常重要的一个环节。

通过计算过孔阻抗,我们可以评估和控制信号在PCB上传输时的信号完整性和干扰情况。

精确的过孔阻抗计算可以帮助工程师设计出高质量和高可靠性的电子产品。

1.2 文章结构本文将对过孔阻抗计算公式进行解释说明,并概述该领域的相关内容。

文章主要分为五个部分:第一部分是引言,其中概述了过孔阻抗计算公式的重要性,同时介绍了本文的结构和目标。

第二部分将详细解释和说明过孔阻抗的定义、计算方法以及推导公式。

通过这一部分,读者将能够全面理解和掌握过孔阻抗计算的基本原理。

第三部分将对过孔设计与影响因素进行深入分析。

我们会探讨过孔设计所需满足的标准与要求,并研究材料选择以及不同几何参数对过孔阻抗的影响。

第四部分将通过具体的实例分析和应用案例说明,进一步展示过孔阻抗计算公式的实际应用。

我们会分析具体PCB板上的过孔阻抗,并讨论不同应用场景下的过孔设计和优化策略。

此外,还会介绍并评估比较各种过孔阻抗计算工具和软件。

最后一部分是结论与展望。

我们将总结归纳主要论点,并指出当前研究存在的不足之处。

同时,根据当前研究结果,提出未来发展方向对过孔阻抗计算公式进行进一步研究。

1.3 目的本文旨在全面解释和说明过孔阻抗计算公式,并探讨其在PCB设计中的重要性和应用影响。

通过本文,读者将能够理解过孔阻抗计算原理、掌握相关设计标准与要求以及深入了解材料选择和几何参数对过孔阻抗的影响。

此外,我们还将提供实例分析和案例说明,帮助读者更好地应用这些知识于实际工程中。

最后,在结论与展望部分,我们还会指出当前研究的不足之处,并提出未来发展的方向。

通过阅读本文,读者将更加全面地了解和掌握过孔阻抗计算公式的相关内容。

2. 过孔阻抗计算公式解释说明:2.1 过孔阻抗的定义:过孔阻抗是指在印刷电路板(PCB)中穿过板层的导电通孔对于高频信号的阻碍程度。

一.过孔的承载电流PCB上的传输线铜箔,其厚度一般为1.2mil(30um)左右,而过孔内的铜箔厚度,一般都大于2mil,所以展开看,铜箔厚度大于传输线。

而传输线打过孔时,传输线宽度一定会小于过孔直径,所以过孔的铜箔宽度也会显著的大于传输线宽度。

对传输线铜箔而言,厚度为35um时,20mil线宽可通过电流是1.35A。

因此,对于信号过孔,承载电流能力的瓶颈不在过孔上面,而是在传输线上面。

对于电源过孔,一般的经验是1A对应一个过孔(Via10,Via12),如果以更安全的角度来看,一个(Via10,Via12)的过孔通过电流600mA是绝对安全的,一个(Via20)的过孔通过电流1A是绝对安全的。

二.过孔的寄生电容过孔本身存在着对地的寄生电容,如果已知过孔在铺地层上的隔离孔直径为D2,过孔焊盘的直径为D1,PCB板的厚度为H,板基材介电常数为ε,则:过孔的寄生电容大小公式为:(近似)C=1.41εHD1/(D2-D1)其中参数的单位是(H:inch, D1/D2:inch, 计算结果单位pF)寄生电容引起的信号上升时间变量值公式:T(10%-90%) =2.2C(Z0/2)计算结果为ps.从计算公式可以看出:过孔的寄生电容与过孔内径无关,与板厚成正比,与过孔外径成正比。

也就是说,过孔外径越大,寄生电容越大;板厚越大,寄生电容越大;与地层的绝缘距离设的越大,寄生电容越小。

过孔的寄生电容会给电路造成的主要影响是延长了信号的上升时间,降低了电路的速度。

举例来说,对于一块厚度为50mil的PCB板,如果使用内径为10mil,焊盘直径为20mil的过孔,焊盘与地铺铜区的距离为32mil,则我们可以通过上面的公式近似算出过孔的寄生电容大致是:C=1.41x4.4x0.050x0.020/(0.032-0.020)=0.517pF,这部分电容引起的上升时间变化量为:T10-90=2.2C(Z0/2)=2.2x0.517x(55/2)=31.28ps 。

高速数据传输线路中的等效电路建模与优化随着科技的不断进步和信息技术的飞速发展,高速数据传输已经成为现代社会中不可或缺的一部分。

高速数据传输线路的设计和优化对于确保数据的快速、稳定和可靠传输至关重要。

在这篇文章中,我们将探讨高速数据传输线路中的等效电路建模与优化的重要性和方法。

一、等效电路建模的重要性在高速数据传输线路中,等效电路建模是一种将复杂的线路系统简化为简单电路模型的方法。

通过等效电路建模,我们可以更好地理解和分析高速数据传输线路的性能和特性。

同时,等效电路模型也为线路的优化和改进提供了基础。

二、等效电路建模的方法1. 传输线模型传输线模型是等效电路建模中常用的一种方法。

传输线模型将传输线看作是由电感、电阻和电容等基本元件组成的电路。

通过对传输线的电学特性进行建模,我们可以更好地了解信号在传输线上的传播和衰减情况。

2. 时域反射系数模型时域反射系数模型是一种用于描述信号在传输线上反射和传输的方法。

通过建立时域反射系数模型,我们可以分析信号的反射和传输情况,从而优化传输线路的设计和性能。

3. 频域响应模型频域响应模型是一种用于描述信号在传输线上频率响应的方法。

通过建立频域响应模型,我们可以分析信号在不同频率下的传输特性,从而优化传输线路的带宽和响应速度。

三、等效电路优化的方法1. 信号完整性优化信号完整性是指在高速数据传输中保持信号的稳定性和准确性。

通过优化等效电路模型,我们可以减少信号的失真和噪声,提高信号的完整性。

常用的信号完整性优化方法包括降低传输线的阻抗不匹配、减少信号的反射和交叉干扰等。

2. 带宽优化带宽是指传输线路可以传输的最高频率范围。

通过优化等效电路模型,我们可以增加传输线路的带宽,提高数据传输的速度和效率。

常用的带宽优化方法包括增加传输线的电容和电感、减小传输线的电阻等。

3. 耗能优化耗能是指在数据传输过程中传输线路所消耗的能量。

通过优化等效电路模型,我们可以减少传输线路的耗能,提高数据传输的能效。

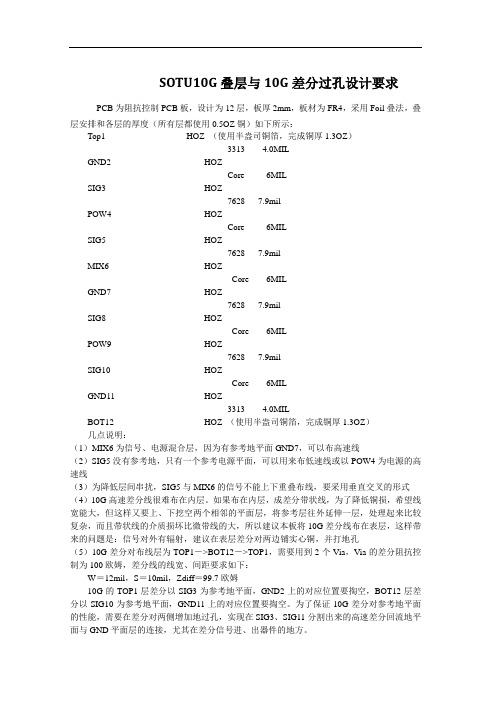

SOTU10G叠层与10G差分过孔设计要求PCB为阻抗控制PCB板,设计为12层,板厚2mm,板材为FR4,采用Foil叠法,叠层安排和各层的厚度(所有层都使用0.5OZ铜)如下所示:Top1 ______________ HOZ (使用半盎司铜箔,完成铜厚1.3OZ)3313 4.0MILGND2 ______________ HOZCore 6MILSIG3 ______________ HOZ7628 7.9milPOW4 ______________ HOZCore 6MILSIG5 ______________ HOZ7628 7.9milMIX6 ______________ HOZCore 6MILGND7 ______________ HOZ7628 7.9milSIG8 ______________ HOZCore 6MILPOW9 ______________ HOZ7628 7.9milSIG10 ______________ HOZCore 6MILGND11 ______________ HOZ3313 4.0MILBOT12 ______________ HOZ (使用半盎司铜箔,完成铜厚1.3OZ)几点说明:(1)MIX6为信号、电源混合层,因为有参考地平面GND7,可以布高速线(2)SIG5没有参考地,只有一个参考电源平面,可以用来布低速线或以POW4为电源的高速线(3)为降低层间串扰,SIG5与MIX6的信号不能上下重叠布线,要采用垂直交叉的形式(4)10G高速差分线很难布在内层。

如果布在内层,成差分带状线,为了降低铜损,希望线宽能大,但这样又要上、下挖空两个相邻的平面层,将参考层往外延伸一层,处理起来比较复杂,而且带状线的介质损坏比微带线的大,所以建议本板将10G差分线布在表层,这样带来的问题是:信号对外有辐射,建议在表层差分对两边铺实心铜,并打地孔(5)10G差分对布线层为TOP1->BOT12->TOP1,需要用到2个Via,Via的差分阻抗控制为100欧姆,差分线的线宽、间距要求如下:W=12mil,S=10mil,Zdiff=99.7欧姆10G的TOP1层差分以SIG3为参考地平面,GND2上的对应位置要掏空,BOT12层差分以SIG10为参考地平面,GND11上的对应位置要掏空。

高速互连通道协同仿真例/串行通道设计例1:10Gb/s 串行通道设计该实例来自Ansoft worldwide technical workshops10Gb/s 串行通道设计3输出信号眼图输入信号眼图基于Virtex-II Pro FPGA设计,分析10Gb/s 的串行通道10Gb/s 的串行通道示意图10Gb/s 串行通道对应的模型图HFSS封装建模。

红线为S21,蓝线为S11。

建模有微带线和带状线两种传输线,通过过孔转换。

Designer微带线建模。

红线为S21,蓝线为S11。

Stripline Modelsdesigner带状线part1到part6建模,HFSS带状线part7建模。

红线为S21,蓝线为S11。

HFSS差分过孔建模。

红线为S21,蓝线为S11。

差分过孔建模红线为蓝线为HFSS SMA转接头建模。

红线为S21,绿线为S11。

微带线带状线SMA接头封装差分过孔分孔带状线Designer全通道建模。

该通道包括:封装、微带线、差分过孔、带状线和SMA接头。

S 群延时参数红线为S21,蓝线为S11Designer 全通道频域分析Designer全通道时域分析仿真眼图测试眼图Designer全通道时域分析,仿真值与测试值一致仿真图测试图Designer全通道时域分析,仿真值与测试值一致例2:高速互连通道场路协同仿真该实例来自教材《ANSYS信号完整性分析与仿真实例》P452 to P510P452t P51020《ANSYS信号完整性分析与仿真实例》例2:高速互连通道场路协同仿真该实例来自教材《ANSYS信号完整性分析与仿真实例》P452 toP51021高速互连通道•高速互连通道由Flipchip封装、带状传输线、差分高速连通道由封装带状传输线差分过孔、SMA 连接器组成高速互连通道示意图1Flipchip1 Flipchip封装•AnsoftLinks与HFSS 协同仿真Flipchip封装¾建模在AnsoftLinks窗口建立新文件打开从AnsoftLinks导出的HFSS 设计文件窗建1 Flipchip封装1Flipchip¾仿真传输系数反射系数创建S 参数报告绘制S 参数图2SMA2 SMA 连接器•HFSS 对SMA 连接器建模HFSS SMA¾建模SMA 连接器在HFSS 中的建模2 SMA 连接器2SMA¾仿真传输系数反射系数SMA 连接器的S参数设置33 差分过孔•HFSS 对差分过孔建模HFSS¾建模差分过孔在HFSS 中的建模3传输系数3差分过孔¾S 参数仿真反射系数差分过孔的S 参数差分过孔的近场图44 带状传输线•Q3D 提取差分Stripline寄生参数Q3D S i li¾建模差分带状线模型与模型参数44 带状传输线¾仿真线宽、间距与阻抗的关系图55 高速互连通道的系统级仿真•Designer 对整个高速互连通道进行系统仿真对整个高速连通道进行系统仿真¾建模Flipchip 封装差分线Stripline差分过孔SMA 连接器Fli hi SMA模型调入Designer 进行系统仿真55 高速互连通道的系统级仿真¾S参数仿真传输系数反射系数参数图可知传输特性在处为反射系数小于通过S参数图可知:传输特性在6GHz -2dB,反射系数小于-10dB。

现在的高速数字系统的频率可能高达数百兆Hz,其快斜率瞬变和极高的工作频率,以及很大的密集度,必将使得系统表现出与低速设计截然不同的行为,出现了信号完整性问题。

破坏了信号完整性将直接导致信号失真、定时错误,以及产生不正确数据、地址和控制信号,从而造成系统误工作甚至导致系统崩溃。

因此,信号完整性问题已经越来越引起高速设计人员的关注。

1 信号完整性问题及其产生机理信号完整性SI(Signal Ingrity)涉及传输线上的信号质量及信号定时的准确性。

在数字系统中对于逻辑1和0,总有其对应的参考电压,正如图1(a)中所示:高于ViH的电平是逻辑1,而低于ViL的电平视为逻辑0,图中阴影区域则可视为不确定状态。

而由图1(b)可知,实际信号总是存在上冲、下冲和振铃,其振荡电平将很有可能落入阴影部分的不确定区。

信号的传输延迟会直接导致不准确的定时,如果定时不够恰当,则很有可能得到不准确的逻辑。

例如信号传输延迟太大,则很有可能在时钟的上升沿或下降沿处采不到准确的逻辑。

一般的数字芯片都要求数据必须在时钟触发沿的tsetup前即要稳定,才能保证逻辑的定时准确(见图1(c))。

对于一个实际的高速数字系统,信号由于受到电磁干扰等因素的影响,波形可能会比我们想象中的更加糟糕,因而对于tsetup 的要求也更加苛刻,这时,信号完整性是硬件系统设计中的一个至关重要的环节,必须加以认真对待。

一个数字系统能否正确工作其关键在于信号定时是否准确,信号定时与信号在传输线上的传输延迟和信号波形的损坏程度有关。

信号传输延迟和波形的原因复杂多样,但主要是以下三种原因破坏了信号完整性:(1)反射噪声其产生的原因是由于信号的传输线、过孔以及其它互连所造成的阻抗不连续。

(2)信号间的串扰随着印刷板上电路的密集度不断增加,间的几何距离越来越小,这使得信号间的电磁已经不能忽略,这将急剧增加信号间的串扰。

(3)电源、地线噪声由于芯片封装与电源平面间的寄生和的存在,当大量芯片内的电路和输出级同时动作时,会产生较大的瞬态,导致电源线上和地线上的电压波动和变化,这也就是我们通常所说的地跳。