LEON微处理器综述

- 格式:doc

- 大小:4.37 KB

- 文档页数:2

LEON处理器的开发应用技术文献及案例汇总LEON 是一款32 位RISC 处理器,支持SPARC V8 指令集,由欧洲航天总局旗下的Gaisler Research 开发、维护,目的是摆脱欧空局对美国航天级处理器的依赖。

LEON 的主要产品线包括Leon2、Leon3、Leon4。

LEON3 开源软核处理器动态图像边缘检测SoC 设计本文采用局部熵边缘检测算法,将图像采集,边缘检测和图像显示三个部分封装设计为IP(Intellectual Property)核,通过AMBA APB 总线嵌入到LEON3 的经典SoC 架构中。

实现了多路数据并行处理和DSP 模块加速处理,配合CPU 软核的协调参数配置功能,可以充分发挥硬件设计的高速性和灵活性。

基于LEON2 的SOC 原型开发平台设计本文就介绍了LEON2 微处理器核,快速的建立起一个SOC 的平台的原型对于验证系统性能与加快软件开发都是相当重要的。

本文还详细阐述了如何在Altera 的FPGA 开发板上建立基于LEON2 微处理器的SOC 原型平台。

Leon2 处理器IP 核的结构、技术特点及其软硬件开发过程本文将从Leon2 的结构、技术特点、软硬件的开发过程和应用实例等四个方面进行介绍。

在技术特点中,主要介绍了它所遵循的SPARCV8 规范、采用的AMBH2.0 内部系统总线协议、容错设计方法和VHDL 编程风格等。

Leon3 软核的FPGA SelectMap 接口配置设计本文结合具体应用需求,介绍了利用嵌入式CPU Leon3 软核处理器对Virtex 系列FPGA 的配置进行控制的方法。

此系统能够实现FPGA 配置数据的重构,并且减少了外围CPU 和CPLD 器件的使用,具有很好的应用价值。

基于LEON3 处理器和Speed 协处理器的复杂SoC 设计实现。

Leon2微处理器流水线相关验证张杨;王竹平【摘要】微处理器的功能验证成为设计验证的瓶颈,指令集的组合验证对流水线处理器具有重要的意义.Leon2流水线相关验证找出了流水线相关的测试向量集,实现了测试程序的自动生成,构造自动化程度较高的验证平台.与指令随机组合测试的方法相比,有针对性地验证了引起流水线相关的情况,同时测试程序达到了较高的流水线状态覆盖率.【期刊名称】《现代电子技术》【年(卷),期】2010(033)020【总页数】4页(P39-42)【关键词】Leon2;功能验证;流水线相关;测试用例【作者】张杨;王竹平【作者单位】西安微电子技术研究所,陕西,西安,710054;西安微电子技术研究所,陕西,西安,710054【正文语种】中文【中图分类】TN911-34;TP3310 引言随着IC技术的飞速发展,微处理器的复杂度和集成度不断提高,验证工作的重要性日益突出,其中功能逻辑验证已经占据了整个设计时间的50%~80%[1]。

由于缺乏高效的功能验证技术,功能验证已日益成为微处理器设计验证过程中的瓶颈。

常用的功能验证方法有形式验证方法和仿真验证方法,形式验证是根据逻辑设计中功能和结构的描述,用定理证明等数学方法来证明逻辑设计的正确性。

形式验证方法已经逐步得到应用[2],但因其固有的计算复杂性等原因,主要应用于小规模的设计中,在现代大规模芯片设计中该方法不能在有效的时间内给出验证结果[3]。

目前所有验证技术中应用最广泛的是基于仿真的验证方法,即将验证用的测试程序加载到待测设计,观察其输出结果是否符合设计规范。

指令集体系结构(instruction set architecture, ISA)划分了整个计算机系统的软件和硬件,是微处理器的核心功能。

针对指令集的验证是微处理器验证中重要的一部分,因此微处理器指令集功能仿真验证的完备性具有重要的意义。

测试程序的生成是指令集仿真验证中的重点,目前普遍采用的方法有手工编写、伪随机生成[4]和针对流水线模型生成。

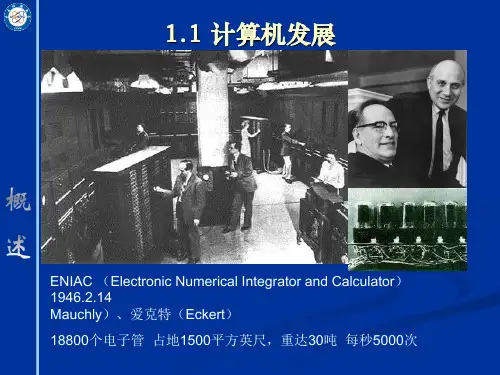

微处理器简介及详细资料基本信息微处理器(英语:Microprocessor,缩写:µP或uP)是可程式化特殊积体电路。

一种处理器,其所有组件小型化至一块或数块积体电路内。

一种积体电路,可在其一端或多端接受编码指令,执行此指令并输出描述其状态的信号。

这些指令能在内部输入、集中或存放起来。

又称半导体中央处理机(CPU),是微型计算机的一个主要部件。

微处理器的组件常安装在一个单片上或在同一组件内,但有时分布在一些不同晶片上。

在具有固定指令集的微型计算机中,微处理器由算术逻辑单元和控制逻辑单元组成。

在具有微程式控制的指令集的微型计算机中,它包含另外的控制存储单元(源自:英汉双解计算机字典)。

用作处理通用数据时,叫作中央处理器。

这也是最为人所知的套用(如:Intel Pentium CPU);专用于作图像数据处理的,叫作Graphics Processing Unit图形处理器(如Nvidia GeForce 7X0 GPU);用于音频数据处理的,叫作Audio Processing Unit音频处理单元(如Creative emu10k1 APU)等等。

物理性来说,它就是一块集成了数量庞大的微型电晶体与其他电子组件的半导体积体电路晶片。

之所以会称为微处理器,并不只是因为它比迷你电脑所用的处理器还要小而已。

最主要的原因,还是因为当初各大晶片厂之制程,已经进入了1 微米的阶段,用1 微米的制程,所产制出来的处理器晶片,厂商就会在产品名称上用“微”字,强调他们很高科技。

就如同现在的许多商业广告一样,很喜欢用“奈米”字眼。

早在微处理器问世之前,电子计算机的中央处理单元就经历了从真空管到电晶体以及再后来的离散式TTL积体电路等几个重要阶段。

甚至在电子计算机以前,还出现过以齿轮、轮轴和杠杆为基础的机械结构计算机。

文艺复兴时期的著名画家兼科学家李奥纳多·达·文西就曾做过类似的设计[来源请求],但那个时代落后的制造技术根本没有能力将这个设计付诸实现。

第一章微处理器是指由一片或几片大规模集成电路芯片组成的中央处理器.微型计算机是指以微处理器为基础,配以内存储器以及输入输出(I/O)接口电路和相应的辅助电路而构成的裸机.微型计算机系统是指由微型计算机配以相应的外围设备和其他专用电器,电源,面板,机架以及足够的软件而构成的系统.对微型计算机系统而言,其硬件部分则由微处理器,内存储器,1/0接口,输入设备和输出设备组成,而其软件则由系统软件和应用软件组成,其中系统软件主要是操作系统和语言处理程序. 按组装形式和系统规模划分,常见单位微型计算机有单片机,单板机和个人计算机等.单片机即单片微型计算机,又称为“微控制器”和“嵌入式计算机”.这是一种把构成一个卫星计算机的一些功能部件集成在一块芯片之中的计算机.单板机.将微处理器,RAM,R0M以及一些I/O接口电路,加上相应的外设以及监控程序固件等安装在一块印刷电路板上所构成的计算机系统.个人计算机.由微处理器芯片装成,便于搬动而且不需要维护的计算机系统.采用芯片组技术后,可以简化主板的设计,降低系统的成本,提高了系统的可靠性,同时对今后的测试,维护和维修等都提供了极大的方便.芯片组决定了系统的如下特称:1CPU的类型,以及芯片主频范围;2.内存条类型;3.提供USB接口的数目以及IEEE1394接口的数目;4.存储器总线的最大频率;5.PC1总线的类型;6.对称多处理能力;7.对内置PC1E1DE控制的支持,8.内置PS/2鼠标,键盘控制器,BIOS以及实时时钟电路.1.3微处理器E要由三部分组成:1.运算器;2.控制器;3.寄存器阵列.总线是微处理器,内存储器和I/O接口之间相互交换信息的公共通路.总线由数据总线,地址总线和控制总线组成,数据总线是从微处理器向内存储器J/0接口传送数据的通路,同时,它也是从内存储器,1/0接口向微处理器传送数据的通路,因为它可以在来那两个方向上往返传送数据,称为双向总线.地址总线是微处理器向内存储器和I/O接口传送地址的信息的通路,它是单向总线,只能从微处理器向外传送.控制总线是微处理器向内存储器和I/O接口传送的命令信号以及外界向微处理器传送状态信号等信号的通路.片总线:又称“元件级总线“,“芯片总线",是微处理器芯片内部引出的总线,它是用微处理器构成的一个部件或是一个很小的系统时,信息传递的通路.内总线(I—BUS):又称“系统总线",“板级总线”,也就是常指的“微机总线”.它是用于微机系统中插件之间信息传递的通路,是微机系统所特有的,应用最多.外总线(E—BUS):又称“通信总线”,它是微机系统之间,或是微机系统与其他系统之间信息传输的通路,往往借用电子工业其他领域已有的总线标准.第二章2.1微处理器执行一段程序通常是通过重复执行如下步骤来完成的,即:*从内存储器中取出一条指令,分析指令操作码;文读出操作数;*执行指令;*将结果写入内存储器.总线接口部件(BIU)由段寄存器,指令指针,地址形成逻辑,总线控制逻辑和指令队列等组成.BIU同外部总线连接为EU完成所有的总线操作,并形成20位的内存物理地址.执行部件(EU)由通用寄存器,标志寄存器,算术逻辑部件(A1U)和EU控制系统等组成.EU负责全部指令的执行晌BIU提供数据和所需访问的内存或I/O端口地址,并对通用寄存器,标志寄存器和指令操作数进行管理.8088和8086的区别:1.8086的指令队列是6字节长,而8088的指令队列尾4字节长;2.8086是真正的16位机,同B1U相连的8086总线中数据总线是16位总线,而8086是准16位机,同BIU相连的8088总线中数据总线为8位总线.在8086微处理器中可供程序员使用的有14个16位寄存器,这14个寄存器按用途可分为通用寄存器,指令指针,标志寄存器和段寄存器四类.通用寄存器可分为两组:1数据寄存器:数据寄存器可以用来存放8位或16位二进制操作数,这些操作数可以是参数操作的数据,操作的中间结果,也可以说操作数的地址.2.指针寄存器和变址寄存器.只能按16位进行存取操作,主要用来形成操作数的地址,用于堆栈操作和变址运算中计算操作数的有效地址.数据寄存器包括:I累加器AX,2基址寄存器BX3计数寄存器CX4数据寄存器DX.指针寄存器和变址寄存器包括:I.堆栈指针寄存器SH3.基址指针寄存器BP4.源变址寄存器SI5.目的变址寄存器D1指令指针IP是一个16位专用寄存器,它指向当前需要取出的指令字节,当B1U从内存中取出一个指令字节后,IP就自动加1,指向下一指令字节.标志寄存器FR:在16位的标志寄存器FR中已定义的有9位,其中6位是状态位,3位是控制位:状态位:1.进位标志CE主要用于加减运算,移位和环移指令等指令也会改变CF值.最高位有进位置12.奇偶标志PF.主要在数据通信中用来检查传送有无错.反映操作结果中“1”的个数,偶数置13.辅助进位标志AF.反应一个8位量有无进位的情况.有则置I,AF用于BCD码算术运算指令4.零标志ZF.反应元素按运算结果是否为零的情况.结果为0,置1.5.符号标志SE反映带符号数运算结果符号位的情况.结果为负,置1.6.溢出标志OE反映带符号数运算结果是否超过机器所能表示的数值范围的情况.溢出置1控制位:1.方向标志DF.决定地址是递增还是递减,置1时递减,置0时递增.2.中断允许标志IF.表示系统是否允许响应外部的可屏蔽中断.置1时允许响应.3.陷阱标志TF.当置】时,微处理器每执行完一条指令便自动产生一个内部中断,转去执行一个中断服务程序.可以借助中断服务程序来监视每条指令的执行情况.在微机系统的内存通常存放着三类信息,即:1.代码(指令)-指示微处理器执行何种操作;2.数据(字符,数值程序处理的对象;3.堆栈信息一被保存的返回地址和中间结果.代码段寄存器CS,指向当前的代码段,指令由此段中取出.堆栈段寄存器SS,指向当前的堆栈段,堆栈操作的对象就是该段中存储单元的内容.数据段寄存器DS,指向当前的数据段,通常用来存放程序变量.附加段寄存器ES,指向当前的附加段,通常也用来存放数据,以及一些专用指令的操作数.存储器分段:因为8086微处理器内部数据通路和寄存器皆为16位,内部A1U只能进行16位运算,在程序中也只能使用16位地址,寻址范围局限在64K字节,为了能寻址1M字节地址,所以引用"分段"的概念.在具有地址变换机构的计算机中,有两种存储器地址,一种是允许在程序中编排的地址-逻辑地址,另一种是信息在存储器中实际存放的地址-物理地址.存储单元的20位物理地址是通常将16位的"段基值”左移4位再奖赏16位的“段内偏移量"生成的.物理地址的生成:1.当取地址时,8086会自动选择SS值作为段基值,再加上由SP提供的偏移量形成物理地址.2.当涉及堆栈操作时,8086会自动选择SS值作为段基值,再加上由SP提供的偏移量形成物理地址.3.当涉及一个存储器操作数时,8086会自动选择DS值作为段基值,再加上16位偏移量形成物理地址.4.ES用于串操作指令中的数据块传送指令5.当存储器操作数中偏移量采用BP为地址寄存器时,8086会自动选择SS值为段基值,再加上以BP为基值的16位偏移量形成物理地址.2.28086的40条引脚信号按功能可分为4部分一地址总线,数据总线,控制总线以及其他(时钟与电源).地址总线和数据总线:1.数据总线用来在CPU与内存储器(或I/O)之间交换信息,地址总线由CPU发出用来确定cpu要访问的内存单元(或I/O)的地址信号.前者为双向,三态信号,后者为输出,三态信号.2.AD15~AD0为地址/数据总线信号,3.A19∕S6~A16∕S3为地址/状态总线信号.4.8086的20条地址线访问存储器时可寻址IMB内存单元,访问外部设备时,只用16条地址A15~A0,可寻址64KB个I/O端口.5.BHE/S7--总线高允许/状态S7信号(输出三态)其他信号1.C1K一-时钟信号,该信号为8086cpu提供基本的定时脉冲,其占空比为1:3,以提供最佳的内部定时.2.Vcc----电源,要求接上正电压.3.GND--地线,两条接地线.8088的引脚与8086的不同之处1.8088的地址/数据服用线为8条,即AD7~AD0,而A15~A8为单一的地址线.2.8088中无BHE/S7,该引脚为SSo-状态信号线.3.8088的存储器/【O控制信号为IO/M,即该信号为高电平时,是I/O端口访问;为低电平时,是存储器访问.这与8086的M/Q线刚好相反.2.4与80486相比Pentium在结构上的特点:1.超标量流水线2.重新设计的浮点部件3.独立的指令cache和数据cache.4.分支检测5.采用64位外部数据总线.Pentiumpro芯片采用了新的体系结构:1.一个封装内安装了两个芯片2.指令分解为微操作3.乱序执行和推测执行4.超级流水线和超标量技术多能奔腾中的MMX技术是Inte180X86微处理器体系结构的重大革新,增加了很多新的技术:1.引入新的数据类型2.采用饱和运算3.具有积和运算能力奔腾2芯片采用的先进技术:1.多媒体增强技术(MMX技术)2.动态执行技术3.双重独立总线结构(DIB)Pentium3芯片中的70条SSE指令可分为:1.内存连续数据流优化处理指令8条2.S1MD浮点运算指令50条3.新的多媒体指令12条Pentium4的主要技术特性是:1.采用3条超标量流水线,流水线深度为20级,流水线深度越大,则越易提高内核的工作频率.2.改进了分支预测单元,为分支预测提供了更好的算法,减少了分支预测错误33%,提高了分支预测的精确度3.采用跟踪缓存和低延迟数据缓存,跟踪缓存可以把己经用过的并经过译码后的微指令存储下来,再次执行到相同指令时,不必再一次重新译码.4.采用该机动态执行技术(ADE),改善因流水线深度加大而带来的运算延迟问题,也可改善分支预测能力.5.待用64位4倍数据速率(QDR)处理器前端总线(FSB)技术6.增加了144条SSE2指令,引入了新的数据格式--128位S1MD整数运算和64位双精度浮点运算.7.在第二代PentiUm3中采用了超线程技术,使单芯片的工作能力类似于双芯片的工作,提高总体性能15%~30%PentiumM微处理器采用全新的体系结构,以解决高性能和低功耗,高性能和小体积的矛盾,采用的技术:1.适合于移动微处理器的流水线2.大容量的12cache3.电源优化的处理器系统总线.4.高级分支预测技术5.专用堆栈管理器6.增强型的speedstep技术7.微指令操作融合8.嵌入双频无线连接功能.ERIC的3项关键技术:1.断定执行2.推测装入3.高级装入在Itanium处理器中的9个执行单元:1.2个整数/MMX执行单元2.2个浮点执行单元3.2个存储管理执行单元4.3个转移处理单元第三章8086的寻址方式有:立即寻址,寄存器寻址,存储器寻址,串操作寻址,外设I/O端口寻址以及程序转移操作寻址.存储器操作数的寻址方式按其有效地址EA分为:1.直接寻址2.寄存器间接寻址3.基址寻址4.变址寻址5.基址变址寻址程序转移运至方式按目的地址的形式方式有如下几种:1.相对寻址2.段内寄存器寻址3.段内间接转移寻址4.段间直接转移寻址5.段间间接转移寻址数据传送指令:1.MoV:传送字节或字.MOVdest,src.dest÷src.2.PUSH:字入栈.PUSHsrc.3.POP:字出栈.POPdest.4.XCHG:交换字或字节.XCHGdest,src5.X1AT:字节转换.6.1EA:装入有效地址.1EAreg,srcζreg÷EA.7.1DS:将指针变量装入寄存器及DS8.1ES:将指针变量装入寄存器及ES9.1AHF:标志寄存器低字节送AH10.SAHF:AH值送标志寄存器低字节11.PUAHF:标志寄存器内容进栈12.POPF:标志寄存器内容出栈13.IN:输入字节或字14.OUT:输出字节或字算术运算指令1.ADD:加法.ADDdest,src;dest<-dest+src2.ADC:带进位的加法.ADCdest,srcζdest÷dest+src+CF3.INc增量(+I).INCdest.dest÷dest+1.4.AAA:加法的ASCI【修正5.DAA:加法的十进制修正6.SUB:减法.SUBdest,src;dest<-dest-src7.SBB:带借位的减法.SBBdest,srcζdest÷dest-src-CF8.DEC:减量(-1).DECdest.dest÷dest-1.9.NEG:求补.NEGdest.dest<_dest(求补)+110.CMP比较.CMPdest,src.dest-src11.AAS减法的ASCn修正12.DAS减法的十进制修正13.MU1无符号数乘法14.IMU1整数乘法15.AAM乘法的ASCII修正16.D1V无符号数除法17.ID1V整数除法18.AAD除法的ASCI1修正19.CBW字节转换为字20.CWD字转换为字节位处理指令:1.AND逻辑与2.OR逻辑或3.NOT逻辑非4.XOR逻辑异或5.TEST测试6.SH1逻辑左移7.SA1算术左移8.SHR逻辑右移9.SAR算术右移10.Ro1循环左移11.ROR循环右移12.RC1通过CF循环左移13.RCR通过CF循环右移串操作指令1.MoVS(MoVSB,MOVSW)串传送(字节传送,字传送)2.CMPS(CMPSB,CMPSW)串比较(字节比较,字比较)3.STOS(STOSB,STOSW)存入串(存入字节,存入字)4.1oDS(1oDSR,1ODSW)取出串(取出字节,取出字)5.SCAS(SCASB,SCASW)扫描串(扫描字节,扫描字)6.REP重复操作7.REPE/REPZ等于/为零重第8.REPNE/REPNZ不等于/不为零重复串操作指令中寄存器和标志位的用途:1.SI源字符串的变址值2.D1目的字符串的变址值3.DS源字符串的段基值4.ES目的字符串的段基值5.CX重第次数计数器6.A1ZAXrSCAS扫描的扫描值,1ODS指令的目的操作数.STOS指令的源操作数7.ZF扫描/比较结束标志8.DF:DF=O,SI,DI自动增量.DF=1,SI,DI自动减量3.3程序设计的步骤1.分析课题2.确定算法3.画流程图4.编写程序5.上机调武修改分支结构程序是具有判断和转移功能的程序.1.判断--根据运算结果的状态标志进行判断.2.转移一-主要由条件转移指令来实现.循环程序由五部分组成:1.初始化部分2.循环工作部分3.循环修改部分4.循环控制部分5.循环结束部分循环程序设计要点:1.怎样把求解的问题变成循环结构的程序类型--怎样实现重免,即计算方案的循环.2.怎样使循环准确执行完毕,这就要注意循环控制部分的设计.子程序:如果在一个程序中有多个地方或在多个程序中都要用到同一段程序,可以把该程序段独立出来存放在内存的某一区域以供其他程序调用,这段程序称为子程序.参数传递一般有三种方法:1.寄存器传递2.用参数表传递3.用堆栈传递子程序嵌套:子程序中调用别的子程序称为嵌套,嵌套的层次只受堆栈空间的大小限制.子程序递归:子程序直接或间接地调用子程序自身,称为递归.DOS为程序设计者提供了许多可直接调用的功能子程序:1.磁盘的读写,控制2.内存管理,文件操作和目录操作3.基本输入输出管理,另外还有时间,日期等子程序.第四章半导体存储器的特点:1.速度快,存取时间可为ns级.2.集成化,3.非破坏性读出双极型存储器是用TT1电路制成的存储器,其特点是速度快,功耗不大,但集成度较低.单极型存储器是用MOS电路制成的存储器,其特点是集成度高,功耗低,价格便宜.RAM的特点是存储器中信息能读写,且对存储器任一存储单元进行读写操作所需的时间基本一样,RAM中的信息在关机后立即消失.ROM的特点是用户在使用时值能读出其中信息,不能修改和写入新的信息,存储单元中的信息由ROM制造厂在生产时一次性写入,ROM中的信息关机后不会消失.衡量半导体存储的优劣指标:存储容量,存储速度,可靠性和性能/价格比.HM6116是一中2048*8位的高速静态CMOS随机存取存储器.特点为:1.高速度2.低功耗3.与TT1兼容4.管脚引出与标准的2K*8b的芯片兼容5.完全静态.Inter2164是64K*1b的芯片,特点为:1.存取时间为150ns∕200ns2.低功耗3.每2ms需刷新一遍,每次刷新512个存储单元,2ms内需有128个刷新周期.在存储器芯片同CPU连接时要注意:1.CPU总线的负载能力问题2.CPU的时序同存储器芯片的存取速度的配合问题. 第五章。

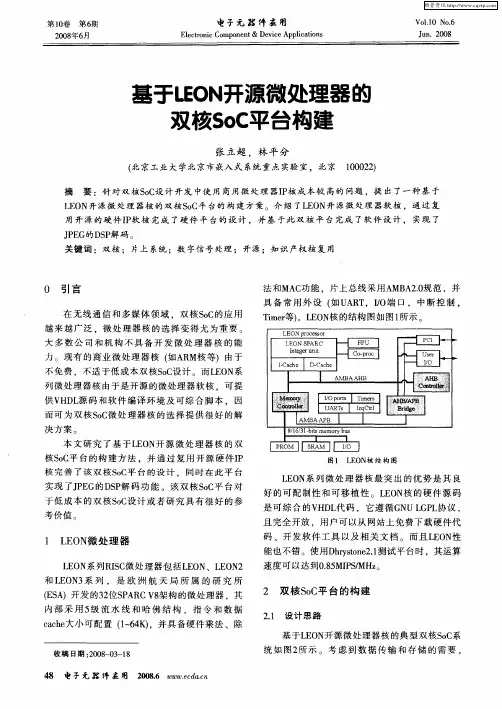

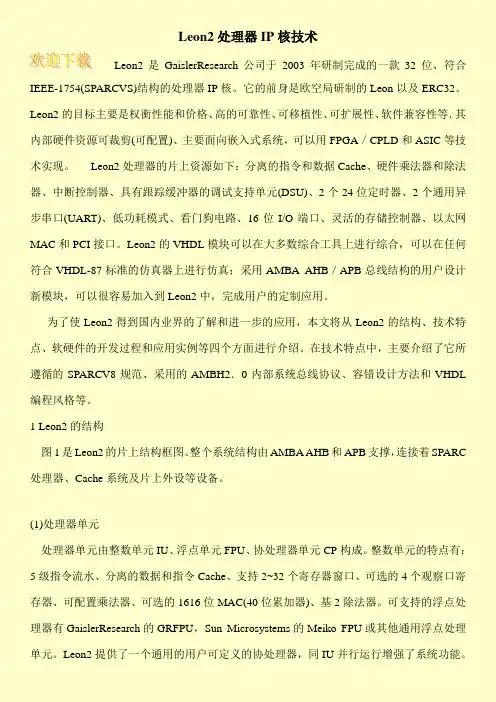

Leon2处理器IP核技术Leon2是GaislerResearch公司于2003年研制完成的一款32位、符合IEEE-1754(SPARCVS)结构的处理器IP核。

它的前身是欧空局研制的Leon以及ERC32。

Leon2的目标主要是权衡性能和价格、高的可靠性、可移植性、可扩展性、软件兼容性等.其内部硬件资源可裁剪(可配置)、主要面向嵌入式系统,可以用FPGA/CPLD和ASIC等技术实现。

Leon2处理器的片上资源如下:分离的指令和数据Cache、硬件乘法器和除法器、中断控制器、具有跟踪缓冲器的调试支持单元(DSU)、2个24位定时器、2个通用异步串口(UART)、低功耗模式、看门狗电路、16位I/O端口、灵活的存储控制器、以太网MAC和PCI接口。

Leon2的VHDL模块可以在大多数综合工具上进行综合,可以在任何符合VHDL-87标准的仿真器上进行仿真;采用AMBA AHB/APB总线结构的用户设计新模块,可以很容易加入到Leon2中,完成用户的定制应用。

为了使Leon2得到国内业界的了解和进一步的应用,本文将从Leon2的结构、技术特点、软硬件的开发过程和应用实例等四个方面进行介绍。

在技术特点中,主要介绍了它所遵循的SPARCV8规范、采用的AMBH2.0内部系统总线协议、容错设计方法和VHDL 编程风格等。

1 Leon2的结构图1是Leon2的片上结构框图。

整个系统结构由AMBA AHB和APB支撑,连接着SPARC 处理器、Cache系统及片上外设等设备。

(1)处理器单元处理器单元由整数单元IU、浮点单元FPU、协处理器单元CP构成。

整数单元的特点有:5级指令流水、分离的数据和指令Cache、支持2~32个寄存器窗口、可选的4个观察口寄存器、可配置乘法器、可选的1616位MAC(40位累加器)、基2除法器。

可支持的浮点处理器有GaislerResearch的GRFPU,Sun Microsystems的Meiko FPU或其他通用浮点处理单元。

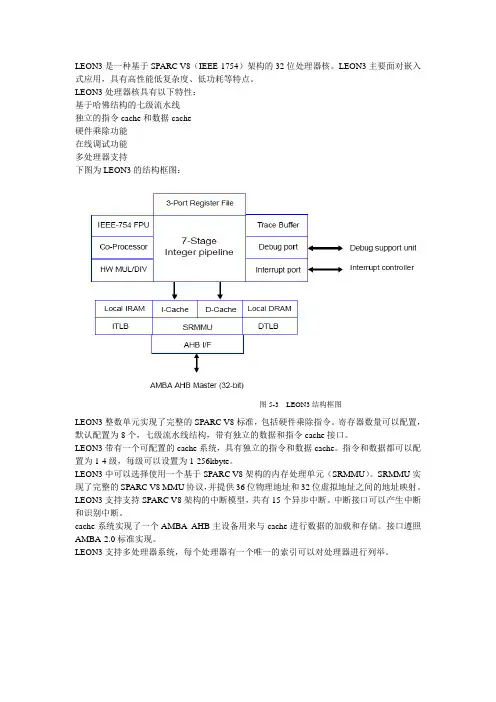

LEON3是一种基于SPARC V8(IEEE-1754)架构的32位处理器核。

LEON3主要面对嵌入式应用,具有高性能低复杂度、低功耗等特点。

LEON3处理器核具有以下特性:

基于哈佛结构的七级流水线

独立的指令cache和数据cache

硬件乘除功能

在线调试功能

多处理器支持

下图为LEON3的结构框图:

图5-3 LEON3 结构框图

LEON3整数单元实现了完整的SPARC V8标准,包括硬件乘除指令。

寄存器数量可以配置,默认配置为8个,七级流水线结构,带有独立的数据和指令cache接口。

LEON3带有一个可配置的cache系统,具有独立的指令和数据cache。

指令和数据都可以配置为1-4级,每级可以设置为1-256kbyte。

LEON3中可以选择使用一个基于SPARC V8架构的内存处理单元(SRMMU)。

SRMMU实现了完整的SPARC V8 MMU协议,并提供36位物理地址和32位虚拟地址之间的地址映射。

LEON3支持支持SPARC V8架构的中断模型,共有15个异步中断。

中断接口可以产生中断和识别中断。

cache系统实现了一个AMBA AHB主设备用来与cache进行数据的加载和存储。

接口遵照AMBA-2.0标准实现。

LEON3支持多处理器系统,每个处理器有一个唯一的索引可以对处理器进行列举。

200518M i crocontrollers &Em bedded Syst ems41.Leon2微处理器IP 核原理及应用u 中科院国家天文台 王宇舟 王二超摘 要介绍一款开源的、符合SPA RC V 8规范的、采用RISC 结构的32位处理器IP 核)))L eon2,它可以从互联网上免费下载使用。

L eon2是以VH DL 形式存在的软核、完全可综合、内部硬件资源可裁剪、主要面向嵌入式应用系统、可以用FPGA/CPL D 和A SIC 等技术实现。

文中介绍Leon2的结构、技术特点、软硬件的开发过程和一些应用实例。

关键词Leon2 SPA RC V 8 AM BA VH DL 交叉编译器引 言Leon2是Gaisler Research 公司于2003年研制完成的一款32位、符合IEEE 1754(SPA RCV8)结构的处理器IP 核。

它的前身是欧空局研制的Leon 以及ERC32。

Leon2的目标主要是权衡性能和价格、高的可靠性、可移植性、可扩展性、软件兼容性等。

其内部硬件资源可裁剪(可配置)、主要面向嵌入式系统,可以用FPGA /CPLD 和ASIC 等技术实现。

Leon2处理器的片上资源如下:分离的指令和数据Cache 、硬件乘法器和除法器、中断控制器、具有跟踪缓冲器的调试支持单元(DSU )、2个24位定时器、2个通用异步串口(U ART )、低功耗模式、看门狗电路、16位I/O 端口、灵活的存储控制器、以太网M AC 和PCI 接口。

Leon2的V HDL 模块可以在大多数综合工具上进行综合,可以在任何符合VH DL 87标准的仿真器上进行仿真;采用A M BA A HB/APB 总线结构的用户设计新模块,可以很容易加入到Leon2中,完成用户的定制应用。

Leon2在欧洲和美国都有众多的应用者;国内航天部771所和中科院国家天文台等单位正在研制基于L eon2的应用系统。

LEON 系列微处理器结构特点

LEON 处理器系列是欧洲航天局的下属的研究所开发的32 位微处理器,应用在航天局的各种ASIC 芯片内。

目前有LEON2,LEON3 系列。

LEON 系列处理器是一个可配置,可综合适于在

SOC 设计中应用的微处理器核。

LEON2 处理器是一个使用SPARC V8 指令集的32 位的RISC 处理器,它的源代码由可综合的VHDL 代码构成。

同时LEON2 的性能也很不错,使用Dhrystone2.1 的测试平台,LEON 可以达到大约0.85MIPS/MHz。

更大的好处是LEON 处理器是一个公开源代码,遵循GNU LGPL 协议。

任何人都可以其网站上免费下载其硬件代码和各种开发软件工具与相关文档。

并且在自己ASIC 项目中使用。

LENO2 的处理器具有以下的特点:

内部使用了5 级流水线,兼容SPARC V8 指令集。

基于LEON3的SoC平台构建及UART全双工通信验证段大高;王平丽【摘要】LEON3是一个可配置、可移植、高性能和开源的软核处理器,在工业领域和空间应用中得到广泛研究.论文基于LEON3软核构建了一种高性能、灵活的SoC硬件平台,并设计了UART全双工通信功能.首先介绍了LEON3开发环境硬件平台的搭建,并通过tsim-leon3模拟器,验证了LEON3 SoC的基本功能;其次研究LEON3的UART通信功能,并在LEON3 SoC硬件平台上进行了UART全双工通信实现.结果验证了基于LEON3的SoC平台的可行性,并实现了SoC的UART全双工通信功能,为SoC的开发提供一个良好的参考方案.【期刊名称】《机电产品开发与创新》【年(卷),期】2014(027)003【总页数】3页(P115-117)【关键词】LEON3;UART;tsim-leon3;SoC【作者】段大高;王平丽【作者单位】北京工商大学,计算机与信息工程学院,北京100048;北京工商大学,计算机与信息工程学院,北京100048【正文语种】中文【中图分类】TP39随着芯片设计技术的飞速发展,SoC已成为集成电路设计界的焦点,SoC的性能要求越来越高,规模也越来越大。

LEON系列微处理器是欧洲航天局(ESA)下属研究机构 Gaisler Research公司所开发和维护的,LEON3处理器是基于SPARCV8架构的32位精简指令集计算机微处理器,目的是摆脱对美国航空局的依赖,LEON3是一个可配置的、可移植的、高性能的、高可靠的软核处理器[1]。

它的源码是可综合的VHDL代码,并且是开源的,任何人都可以在其网站上免费下载其硬件代码和各种开发软件工具与文档。

由于LEON3具有良好的可移植性、可配置性和遵循GPL许可协议的开源性,这些特性保证系统SoC芯片的安全性,提供良好的性能和灵活的解决方案[2],也决定了在LEON3上进行嵌入式操作系统移植的特殊性,所以很适合SoC平台开发[3~5]。

摘要:随着集成电路设计水平和ic制造工艺水平的快速发展,在单芯片上集成微电子应用产品所需的所有功能的系统芯片(soc)得到广泛应用。

系统芯片(soc)开发的核心是微处理器ip 核,实际上多数公司和研究机构不具备开发自己的处理器的能力,较为普遍的做法是购买已成产品的微处理器ip核,但是这需要支付为数不少的使用许可费用。

还有另一种选择,即使用开放源代码的微处理器ip核。

本文介绍了leon系列微处理器的软核架构、在soc设计中的优势以及片上总线。

关键词:leon;可配置性;可移植性;amba

1leon软核架构介绍

leon软核是一个与sparc v8兼容的整数处理单元iu(integer unit),leon2是5级流水线,leon3是7级流水线。

leon3微处理器具有以下特点:

●七级流水线结构;

●具有硬件乘法/除法和mac功能;

●独立的指令和数据cache(哈佛结构);

●可根据需求灵活配置cache的容量;

●片上总线使用amba2.0规范,支持apb和ahb标准;

●具备一些片上常用外设(如uart、中断控制、i/o接口、实时时钟、看门狗等)。

leon3微处理器软核的可配置体系架构如图1所示。

除了关键的微处理器外,外围模块也是制约系统性能的重要因素,在本文主要介绍以下几个模块:

fpu和协处理器leon3提供浮点单元的接口和一个自定义的协处理器。

有两个可用的fpu 控制器,一个是用于高性能的grfpu,另一个是用于meiko fpu。

只要不存在数据或者资源的依赖,浮点处理器、协处理器以及整数单元的并行执行并不会阻碍操作。

内存管理单元mmu内存管理单元mmu(memory management unit)遵循所有的sparc v8的规范,实现了32位虚拟地址和36位物理存储器的映射。

mmu可配置多达64个完全关联tlb 入口,用于访问正在运行的硬件和软件代码,方便后期调试。

2leon在soc芯片开发中的优势

leon微处理器具有良好的综合性能,使用dhrystone 2.1测试平台对其进行测试时,其运算速度可以达到0.85 mips/mhz。

leon软核最突出的优势是其良好的可配置性和可移植性,以及遵循gpl许可证协议的开源性。

开源性基于gpl许可证协议,leon非容错版本软核ip提供vhdl源代码,仅是容错版本的leon软核需要商业授权。

源代码公开使研究者和开发者从根本上研究软核的细节从而定制满足具体应用的软核成为可能。

可配置性 leon软核有一套非常丰富的接口和运算单元ip核库,用户可以根据自己的需要对leon软核的绝大多数模块进行配置,以达到性能、功耗和面积的平衡和优化。

软核iu 可以配置流水线深度、地址和数据高速缓存;外围设备可以挂载在amba总线上;而硬件加速单元可以根据需求集成。

可移植性 leon软核通过层次分明的vhdl模型实现。

通过vhdl中特定的配置接口,leon 核的关键参数(例如修改cache的大小和组织方式,乘法器的生成,速度、芯片面积的调整以及容错方案的选择)都能够灵活的设置和移植。

3leon的总线系统

soc设计往往涉及到ip核的可移植性和设计复用。

这些ip可能是自己开发的,也有可能是来自第三方的。

要把这些不同的ip核组成一个soc系统,就需要这些ip核具有标准的接口,使用片上总线(ocb)就是解决这一问题的有效途径。

片上总线是基于以下原因而出现的:首先在soc设计中,确实需要一个好的、可靠的soc集成方法;其次,在大型的系统设计中需要有一个公用的接口规范来方便结构化设计,最后它还受到传统的微机总线,如pci、vme、isa 等系统集成方法的影响。

作为soc集成系统的互连结构,总线可以解决各个功能模块间的相互通信问题,包括数据格式、通信联络、时序、协议等方面,从而为设计人员免去相当大的精力去考虑如何将自己设计的功能模块和其它功能模块连接起来,使得ip模块集成起来更加方便。

amba(先进微控制器总线结构)提供了一种特殊的机制可以将risc处理器和ip核与外设集成,定义了找组总线:ahb(amba高性能总线),asb(amba系统总线)和apb(amba外设总线)。

一个典型的基于amba总线的系统框图如图2所示。

amba总线是一种层次化的总线结构,如图3所示。

从图中可以看出,一个由amba总线构成的片上系统可以归纳为以下三个部分:

1、总线主设备:任何一个功能ip核都可以成为amba总线架构中的ahb主设备,只要其提供ahb高速总线所需要的主设备接口。

而对于apb来说,它的主设备只有一个,即ahb- apb 总线桥。

2、总线从设备:相应的总线也存在从设备,任何一个功能ip核也可以成为amba总线架构中的从设备,同样的ip核也需提供amba总线架构(包括高速总线ahb,低速外设总线apb)所需的从设备接口。

3、总线互连模块:这是整个amba总线架构的核心部分,它负责完成数据、地址和控制信号的选择传输以及仲裁主设备分时占有总线的任务。

ahb 是一个高性能、高时钟频率的系统总线。

ahb作为高性能系统的中枢总线,它支持处理器、片外存储器与低功耗外设的高性能连接。

同时,ahb的设计使得系统集成和自动测试技术的设计流程都更加方便、有效。

ahb地址和数据总线独立,最多支持16个主模块和16个从模块,所有从模块都采用地址映射。

ahb主要包括以下一些特性:单个时钟边沿操作;非三态的实现方式;支持突发传输;支持分段传输;支持多个主控制器;可配置32位 ~ 128位总线宽度;支持字节、半字和字的传输。

4结束语

本文介绍了leon微处理器软核的体系架构及iu、fpu等单元,论述了leon微处理器自身的特点以及在soc芯片开发中的优势;说明了片上总线对soc芯片的重要性,具体说明了leon微处理器所应用的amba总线结构及各自的工作方式、特点。