引脚对照

- 格式:doc

- 大小:566.00 KB

- 文档页数:3

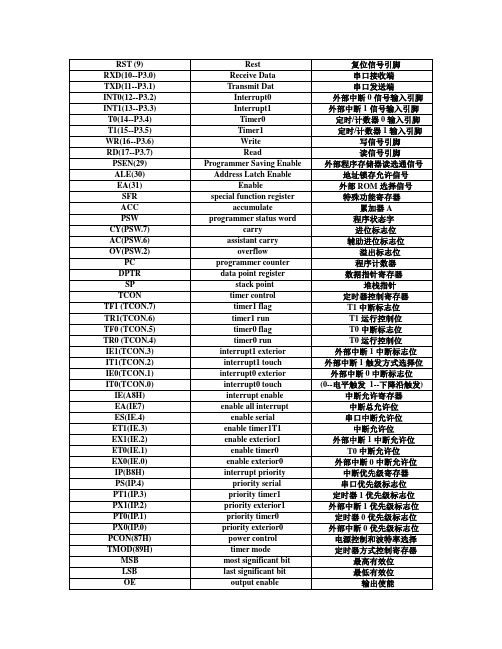

RST (9) Rest 复位信号引脚RXD(10--P3.0) Receive Data 串口接收端TXD(11--P3.1) Transmit Dat 串口发送端INT0(12--P3.2) Interrupt0 外部中断0信号输入引脚INT1(13--P3.3) Interrupt1 外部中断1信号输入引脚T0(14--P3.4) Timer0 定时/计数器0输入引脚T1(15--P3.5) Timer1 定时/计数器1输入引脚WR(16--P3.6) Write 写信号引脚RD(17--P3.7) Read 读信号引脚PSEN(29) Programmer Saving Enable 外部程序存储器读选通信号ALE(30) Address Latch Enable 地址锁存允许信号EA(31) Enable 外部ROM选择信号SFR special function register 特殊功能寄存器ACC accumulate 累加器APSW programmer status word 程序状态字CY(PSW.7) carry 进位标志位AC(PSW.6) assistant carry 辅助进位标志位OV(PSW.2) overflow 溢出标志位PC programmer counter 程序计数器DPTR data point register 数据指针寄存器SP stack point 堆栈指针TCON timer control 定时器控制寄存器TF1 (TCON.7) timer1 flag T1中断标志位TR1(TCON.6) timer1 run T1运行控制位TF0 (TCON.5) timer0 flag T0中断标志位TR0 (TCON.4) timer0 run T0运行控制位IE1(TCON.3) interrupt1 exterior 外部中断1中断标志位IT1(TCON.2) interrupt1 touch 外部中断1触发方式选择位IE0(TCON.1) interrupt0 exterior 外部中断0中断标志位IT0(TCON.0) interrupt0 touch (0--电平触发1--下降沿触发) IE(A8H) interrupt enable 中断允许寄存器EA(IE7) enable all interrupt 中断总允许位ES(IE.4) enable serial 串口中断允许位ET1(IE.3) enable timer1T1 中断允许位EX1(IE.2) enable exterior1 外部中断1中断允许位ET0(IE.1) enable timer0 T0中断允许位EX0(IE.0) enable exterior0 外部中断0中断允许位IP(B8H) interrupt priority 中断优先级寄存器PS(IP.4) priority serial 串口优先级标志位PT1(IP.3) priority timer1 定时器1优先级标志位PX1(IP.2) priority exterior1 外部中断1优先级标志位PT0(IP.1) priority timer0 定时器0优先级标志位PX0(IP.0) priority exterior0 外部中断0优先级标志位PCON(87H) power control 电源控制和波特率选择TMOD(89H) timer mode 定时器方式控制寄存器MSB most significant bit 最高有效位LSB last significant bit 最低有效位OE output enable 输出使能。

电子元件引脚定义对照

1. 引言

在电子设备的设计与制造中,了解电子元件引脚的定义和功能至关重要。

本文档提供了一个电子元件引脚定义对照表,以帮助读者快速了解常见电子元件的引脚定义。

2. 电子元件引脚定义对照表

3. 使用说明

本文档中提供的电子元件引脚定义对照表可用于以下场景:

- 新手研究:对于刚刚开始研究电子技术的人来说,了解电子元件引脚的定义和功能是非常基础的知识。

通过阅读本文档,他们可以迅速了解不同电子元件引脚的定义和功能。

- 设计与制造:电子工程师在设计与制造电子设备时需要合理地使用电子元件。

通过查阅本文档,他们可以快速找到合适的电子元件并了解其引脚定义,从而更好地完成项目。

4. 总结

电子元件引脚定义对照表是一个非常有用的参考资源,可以帮助读者快速了解常见电子元件的引脚定义和功能。

希望本文档能够为读者在电子技术研究和电子设备设计中提供帮助。

如需了解更多电子元件引脚定义和功能,请参考电子工程相关书籍和资料。

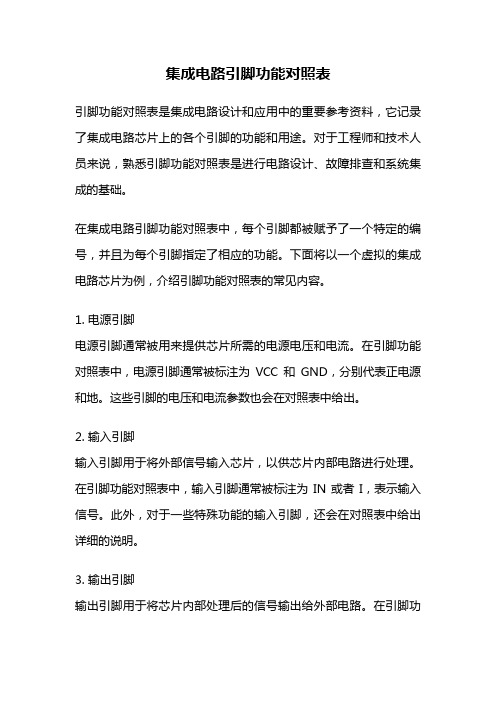

集成电路引脚功能对照表引脚功能对照表是集成电路设计和应用中的重要参考资料,它记录了集成电路芯片上的各个引脚的功能和用途。

对于工程师和技术人员来说,熟悉引脚功能对照表是进行电路设计、故障排查和系统集成的基础。

在集成电路引脚功能对照表中,每个引脚都被赋予了一个特定的编号,并且为每个引脚指定了相应的功能。

下面将以一个虚拟的集成电路芯片为例,介绍引脚功能对照表的常见内容。

1. 电源引脚电源引脚通常被用来提供芯片所需的电源电压和电流。

在引脚功能对照表中,电源引脚通常被标注为VCC和GND,分别代表正电源和地。

这些引脚的电压和电流参数也会在对照表中给出。

2. 输入引脚输入引脚用于将外部信号输入芯片,以供芯片内部电路进行处理。

在引脚功能对照表中,输入引脚通常被标注为IN或者I,表示输入信号。

此外,对于一些特殊功能的输入引脚,还会在对照表中给出详细的说明。

3. 输出引脚输出引脚用于将芯片内部处理后的信号输出给外部电路。

在引脚功能对照表中,输出引脚通常被标注为OUT或者O,表示输出信号。

对于一些特殊功能的输出引脚,也会在对照表中给出详细的说明。

4. 控制引脚控制引脚通常用于控制芯片的工作状态或者功能。

在引脚功能对照表中,控制引脚通常被标注为CTRL或者C,表示控制信号。

对于一些特殊功能的控制引脚,也会在对照表中给出详细的说明。

5. 时钟引脚时钟引脚用于提供芯片内部电路的时钟信号,以同步芯片的工作。

在引脚功能对照表中,时钟引脚通常被标注为CLK或者C,表示时钟信号。

对于一些特殊功能的时钟引脚,也会在对照表中给出详细的说明。

6. 复位引脚复位引脚用于将芯片的内部电路复位到初始状态。

在引脚功能对照表中,复位引脚通常被标注为RESET或者RST,表示复位信号。

对于一些特殊功能的复位引脚,也会在对照表中给出详细的说明。

7. 中断引脚中断引脚用于处理外部中断信号,以及向外部设备发送中断请求。

在引脚功能对照表中,中断引脚通常被标注为INT或者IRQ,表示中断信号。

实验八正弦信号发生器的设计一、实验目的1、学习用VHDL设计波形发生器和扫频信号发生器。

2、掌握FPGA对D/A的接口和控制技术,学会LPM_ROM在波形发生器设计中的实用方法。

二、实验仪器PC机、EDA实验箱一台Quartus II 6.0软件三、实验原理如实验图所示,完整的波形发生器由4部分组成:• FPGA中的波形发生器控制电路,它通过外来控制信号和高速时钟信号,向波形数据ROM 发出地址信号,输出波形的频率由发出的地址信号的速度决定;当以固定频率扫描输出地址时,模拟输出波形是固定频率,而当以周期性时变方式扫描输出地址时,则模拟输出波形为扫频信号。

•波形数据ROM中存有发生器的波形数据,如正弦波或三角波数据。

当接受来自FPGA的地址信号后,将从数据线输出相应的波形数据,地址变化得越快,则输出数据的速度越快,从而使D/A输出的模拟信号的变化速度越快。

波形数据ROM可以由多种方式实现,如在FPGA外面外接普通ROM;由逻辑方式在FPGA中实现(如例6);或由FPGA中的EAB模块担当,如利用LPM_ROM实现。

相比之下,第1种方式的容量最大,但速度最慢;,第2种方式容量最小,但速度最最快;第3种方式则兼顾了两方面的因素;• D/A转换器负责将ROM输出的数据转换成模拟信号,经滤波电路后输出。

输出波形的频率上限与D/A器件的转换速度有重要关系,本例采用DAC0832器件。

DAC0832是8位D/A转换器,转换周期为1µs,其引脚信号以及与FPGA目标器件典型的接口方式如附图2—7所示。

其参考电压与+5V工作电压相接(实用电路应接精密基准电压).DAC0832的引脚功能简述如下:•ILE(PIN 19):数据锁存允许信号,高电平有效,系统板上已直接连在+5V上。

•WR1、WR2(PIN 2、18):写信号1、2,低电平有效。

•XFER(PIN 17):数据传送控制信号,低电平有效。

•VREF(PIN 8):基准电压,可正可负,-10V~+10V.•RFB(PIN 9):反馈电阻端。

西门子串口引脚定义及协议使用串口通讯,又经常被称为点对点通讯或者PtP通讯,是工业设备中的一种非常通用的通讯方式,常用于获取相对远程采集设备的数据。

串行通信,通常利用RS232C或者RS485电气接口,实现ASCII码或者Modbus通讯;其特点是通信线路简单,成本较低,用于解决不同厂商产品之间节点少、数据量小、通讯速率低、实时性要求不高的场合,如过程仪表、变频器、连接扫描仪、条码阅读器等带有串行通讯接口的设备,CP卡加载通讯协议后,还可以和支持Modbus协议的现场仪表通讯。

为了实现设备相互通讯,通讯双方的通讯接口和通讯协议要一致,最基本的串行通讯的数据帧格式和波特率也要匹配。

西门子串行通讯支持的数据帧格式:·起始位:1位;·数据位:7/8位;·校验位:1位奇/偶校验位,或者没有校验位;·停止位:1/2位。

常用的串行数据接口有:RS232C 和RS485/422。

RS-232C、RS-422/485 标准只对接口的电气特性做出规定,而不涉及接插件、电缆或协议,在此基础上用户可以建立自己的高层通信协议。

一、RS232C接口RS-232C 是低速率的单端串行通讯,RS-232C 采取不平衡传输方式,即所谓单端通讯。

1.RS232C 通讯接口特点·RS-232采取不平衡传输方式,其收、发端的数据信号是相对于信号地,抗共模干扰能力差;·近距离通讯,最大通信距离15m;·只能用于点对点(即一对收/发设备)通讯。

2. RS232C 接口定义RS232C并未定义连接器的物理特性,不同类型的连接器引脚定义也各不相同,其中9针和25针的引脚定义对照,所示。

最为简单且常用的是三线制接法,即Txd,Rxd和地线三根,如上图中红色(2,3)和紫色(5)三个针脚。

二、RS422/485 接口RS-422/485 改进RS-232 通信距离短、速率低的缺点。

实验一二选一数据选择器VHDL设计Quartus II 6.0开发环境与EDA实验箱使用一实验目的1.熟悉在Quartus II 6.0环境下原理图输入方法。

2.熟悉Quartus II 6.0环境下编辑、编译综合、仿真的操作方法。

3、掌握利用EDA软件进行电路设计的详细流程;4、熟悉EDA实验箱的基本使用方法。

学会对实验板上的FPGA/CPLD进行编程下载,硬件验证自己的设计项目。

二实验仪器PC机、Quartus II 6.0软件三实验内容1.详细解读教材117页。

2.在QuartusⅡ上输入该设计的原理图,并进行编辑、编译、综合、适配、仿真。

3.给出其所有信号的时序仿真波形。

四实验原理及步骤1.启动Quartus II 6.0软件在桌面上双击Quartus II 6.0图标或者在开始—>所有程序—>Altera—> Quartus II 6.0,如下图2.建立工作库文件夹及工程任何一次设计都是一项工程(Project),所有此工程相关的所有设计文件都需要放在同一个文件夹里。

不同的设计放在不同的文件夹中。

在E盘下建立一个存放本次设计的工程文件夹,比如“shiyan1”。

注意不要使用中文文件夹,文件夹的存放路径也不要包含中文。

注意本实验室计算机C盘和D盘是重启后复原,不要将任何文件和文件夹放置在桌面或者C、D盘下。

初次打开Quartus II 6.0,会有如图提示:选择是的情况下,首先是新工程向导:介绍下一步下一步下一步,选择目标芯片,首先在Family栏选择ACEX1K系列,然后选择此系列的具体芯片:EP1K30TC144-3。

注意不要选成了EP1K30TC144-3。

下一步就点完成。

3.建立文本程序文件选择File菜单下的New或者直接点击工具栏中的新建图标,选择新建文件类型为VHDL File。

接下来另存文件:保存时需更改文件名与项目名称一样,注意保存在同一个工程文件夹下面。

附图3 实验电路结构图NO.0附图4 实验电路结构图NO.1附图5 实验电路结构图NO.2实实实实实实实NO.3实实实实实实实实实实实实实实实实实实实实实实实实D9D16D15D14D13D12D11D10D8D7D6D5D4D3D2D1PIO8PIO9PIO10PIO11PIO12PIO13PIO14PIO15S P E A K E R实实实12345678实实实实FPGA/CPLD PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7实1实2实3实4实5实6实7实8PIO15-PIO8PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16附图6 实验电路结构图NO.3附图7 实验电路结构图NO.4D1PIO8D2D3D4D5D6D7D8PIO9PIO10PIO11PIO12PIO15PIO14PIO13实实实实实实实NO.5S P E A K E R实实实FPGA/CPLD 实实实实12345678D16D15D14D13D12D11D10D9PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16实实实实实实实实实实实实实实实实实实实实实实实实PIO15-PIO8PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7实1实2实3实4实5实6实7实8附图8 实验电路结构图NO.5附图9 实验电路结构图NO.6D16D15D14D13D12D11D9D8PIO47D7PIO46D6PIO45D5PIO44D4PIO43D3PIO42D2PIO41PIO40D1NO.7实验电路结构图S P E A K E R扬声器FPGA/CPLD 目标芯片12345678PIO0PIO2PIO3PIO4PIO5PIO6PIO7单脉冲单脉冲单脉冲键1键2键3键4键5键6键7键8PIO47-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器附图10 实验电路结构图NO.7附图11 实验电路结构图NO.8附图12 实验电路结构图NO.9附图13 实验电路结构图NO.B实验电路结构图 N O .5AD 16D 15D 14D 13D 12D 11D 10D 9D 8D 7D 6D 5D 4D 3D 2D 1P I O 8J P 2(1/2,3/4)J P 2(5/6)P I O 8SPEAKER目标芯片F P G A /C P L D(23)(24)1216272610C L O C K 750K H Z A 750K H Z A F I T102C 30103C 29D A -5--+5D A 0--+5P I O 38P I O 37P I O 35C O M MD A W RC O M P ADE O C A D E N J P 22018161412108642191715131197531021V R 110K V C C +5V A I N 0A I N 1r e f (-)r e f (+)I N -1I N -06922257171415818192021E U 1A D C 0809P I O 16P I O 17P I O 18P I O 19P I O 20P I O 21P I O 22P I O 23P I O 32P I O 33P I O 35P I O 34m s b 2-12-22-32-42-52-62-7l s b 2-8E O C A D D -A A D D -B A D D -C A L E E N A B L E S T A R T扬声器P I O 39-P I O 36P I O 43-P I O 40P I O 47-P I O 4412345678数码数码数码数码数码数码数码数码译码器译码器译码器单脉冲单脉冲单脉冲P I O 0P I O 1P I O 2P I O 3P I O 4P I O 5P I O 6P I O 7P I O 15P I O 14P I O 13P I O 12P I O 11P I O 10P I O 9P I O 8键1键2键3键4键5键6键7键8附图14 实验电路结构图NO.5AD 8D 7D 6D 5D 4D 3D 2D 1译码器译码器译码器D 16D 15D 14D 13D 12D 11D 10D 9实验电路结构图 N O .5BV C C目标芯片F PG A /C P L D串行通讯接口接口电路J 75413P I O 45P I O 46P S /2接口单片机接口电路235接P C 机R S -232B 412M H Z A键复位P I O 11P I O 12P I O 13P I O 14SPEAKERA T 89C 2051E U 3P 34P 33P 32X 1X 2P 31P 30P 35R S TG N D P 37P 10P 11P 12P 13P 14P 15P 16P 17V C C 1234567891011121314151617181920P I O 15P I O 24P I O 25P I O 26P I O 27P I O 28P I O 29P I O 30P I O 31扬声器P I O 39-P I O 36P I O 43-P I O 40P I O 47-P I O 4412345678数码数码数码数码数码数码数码数码单脉冲单脉冲单脉冲P I O 0P I O 1P I O 2P I O 3P I O 4P I O 5P I O 6P I O 7P I O 15P I O 14P I O 13P I O 12P I O 11P I O 10P I O 9P I O 8键1键2键3键4键5键6键7键8附图15 实验电路结构图NO.5BD 16D 15D 14D 13D 12D 11D 10D 9D 1P I O 8D 2P I O 9D 3P I O 10D 4P I O 11D 5P I O 12D 6P I O 13D 7P I O 14D 8P I O 15译码器译码器译码器实验电路结构图 N O .5CF PG A /C P L DJ P 251p F C 27J P 2(C O M P )C O M PP I O 37L M 311V C C 10K-12+124823T L 082/1A I N 0A O U T5.1K102103+510K5.1K5.1KR 72765T L 082/2841+12-12D A 0--+5D A -5--+5滤波0滤波1F I TC O M M E U 2D A C 0832********J P 2(9,10)P I O 38D A W R 2W R 1F B93211I O U T 1I O U T 212/C S W R 2X F E R A G N D D G N D V R E F 8V C C20+5V C CD 0D 1D 2D 3D 4D 5D 6D 7765416151413P I O 24P I O 25P I O 26P I O 27P I O 28P I O 29P I O 30P I O 31P I O 43-P I O 40P I O 35-P I O 32P I O 23-P I O 20P I O 19-P I O 16目标芯片P I O 47-P I O 44译码器译码器P I O 15-P I O 812345678数码数码数码数码数码数码数码数码单脉冲单脉冲单脉冲P I O 0P I O 1P I O 2P I O 3P I O 4P I O 5P I O 6P I O 7键1键2键3键4键5键6键7键8附图16 实验电路结构图NO.5CD A C C1K REFS 1KREFSNO.5DPIO34PIO27SDASCL TEST NC NC NC PIO19PIO17PIO34PIO27GNDNC NC DOUTDIN SK CS 24CXX93CXXVCC87654321VCC GNDVCC 87654321VCC TLC549VCC PIO30PIO2987654321PIO28CSDOUT I/OCK VCC GNDREF-AIN REF+JSL141312111098765PIO26PIO24PIO25PIO31VCCLOADDACD DACC DACB DACA LDAC CLKDATA REFD REFC REFB REFA TLC5620GND VCCREFSS VCC REFSJTLJAVPIO19PIO18TLV1572PIO17SCLKVCC FS DO AINGND VREF PIO34CS 87654321VCC 4321REFSSREFINCLK VCC PIO17PIO34PIO198031VIN-VIN+CS 87654321DOUT GNDADC08031VCC ADCCD1PIO8D2D3D4D5D6D7D8PIO9PIO10PIO11PIO12PIO15PIO14PIO13实实实实实实实S P E A K E R实实实FPGA/CPLD 实实实实12345678D16D15D14D13D12D11D10D9PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16实实实实实实实实实实实实实实实实实实实实实实实实PIO15-PIO8实实实实实实实实实PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7实1实2实3实4实5实6实7实8附图17 实验电路结构图NO.5D附录2 GW48结构图信号名与芯片引脚对照表。

课程设计报告高速异步FIFO设计目录技术规范 (3)FIFO的功能描述 (3)FIFO的引脚定义 (3)总体方案设计 (4)电路设计方框图 (4)电路设计连接图 (4)电路模块及其功能简介 (4)电路设计思想 (5)仿真方案及其仿真激励源代码 (8)仿真方案 (8)仿真激励源代码 (8)电路描述代码 (9)功能仿真 (14)分块仿真 (14)双口RAM仿真 (14)读数据控制电路仿真 (15)写数据控制电路仿真 (16)锁存器电路仿真 (16)满空标志电路仿真 (17)总体仿真 (18)综合与布局布线 (18)综合布局布线报告 (19)报告数据分析 (19)时序仿真 (19)实验心得 (20)一、技术规范1、FIFO的功能描述高速异步FIFO(First In First out)深度为256,数据宽度为8位(最大可存储256byte),可实时给出FIFO的满空标志,并可实现数据的平滑输出,其写时钟为带间隔的100MHz,读时钟为5MHz,从而实现了FIFO的异步数据传输。

2、FIFO的应交定义(3)写数据控制器引脚对照表:(4)读数据控制器引脚对照表:二、总体设计方案1、电路设计方框图(如图2.1所示)图2.12、电路设计连接图(如图2.2所示)3、电路模块及其功能简介双口256*8bit的RAM:用于存储FIFO的缓冲数据写数据控制器:用于控制FIFO中数据的写时序操作FIFO 读数据控制器:用于控制FIFO数据中的读时序操作锁存器:用于锁存上一个clock时的读写地址指针FIFO满空标志电路:用于实时标志FIFO的满空状态4、电路设计思想设计高速异步FIFO,首先,考虑如何实现数据的先进先出问题;为了解决这个问题,设计中就必须有一个可用于随机存取的存储器,又要实现异步,即异步读写,所以本设计中存储器选择采用双口RAM;其次,考虑如何实现在不同时钟下,实现读数据和写数据,在设计中,使用独立电路模块,分别控制读写操作;最后,一个要考虑的问题也是本设计中的难点,即对于高速异步FIFO来说,如何高速、实时判断FIFO的满和空。

怎么看芯片的引脚芯片引脚是芯片上的金属引线,它们可以传输电信号、供电和连接其他设备。

对于初学者来说,了解芯片引脚是非常重要的,下面详细介绍如何看芯片引脚。

1. 查找芯片引脚图表:每个芯片都会有一个引脚图表,通常可以在芯片的数据手册或官方网站上找到。

这个图表会列出芯片的引脚编号、名称和功能。

在了解或使用芯片之前,务必查阅并对照引脚图表。

2. 确定引脚编号:在引脚图表中,每个引脚都会有一个编号。

引脚编号一般是从1开始递增,根据芯片的封装类型和封装形状,引脚的排序方式可能有所不同。

了解引脚的编号有助于插入和连接芯片。

3. 区分引脚的类型:芯片引脚通常可以分为几种类型,其中最常见的是电源引脚、输入引脚和输出引脚。

电源引脚用于提供芯片所需的电压和电流,输入引脚接收外部信号,输出引脚发送芯片生成的信号。

通过观察引脚图表或者根据引脚的功能来区分引脚的类型。

4. 关注引脚标记:有些芯片的引脚上会有特殊的标记,这些标记可以帮助用户更好地使用芯片。

例如,某些芯片可能在引脚上标记了一个特殊的标志或标识,表示该引脚具有特殊功能或需要特别注意。

此外,还可能有一些引脚标记表示该引脚的用途或功能。

5. 参考芯片封装类型:芯片的引脚也与其封装类型有关。

不同封装类型的芯片引脚布局也会有所不同。

常见的芯片封装类型有直插封装(DIP)、贴片封装(SMD)等。

如果能了解芯片的封装类型,并在引脚图表上查找相应的封装类型,就可以更准确地找到芯片的引脚。

总结:要看芯片的引脚,首先需要查找芯片的引脚图表,并了解引脚编号、类型、标记等信息。

同时,参考芯片的封装类型,可以更准确地理解芯片的引脚布局。

通过这些方法,可以对芯片引脚有一个初步的了解,并能正确使用芯片。