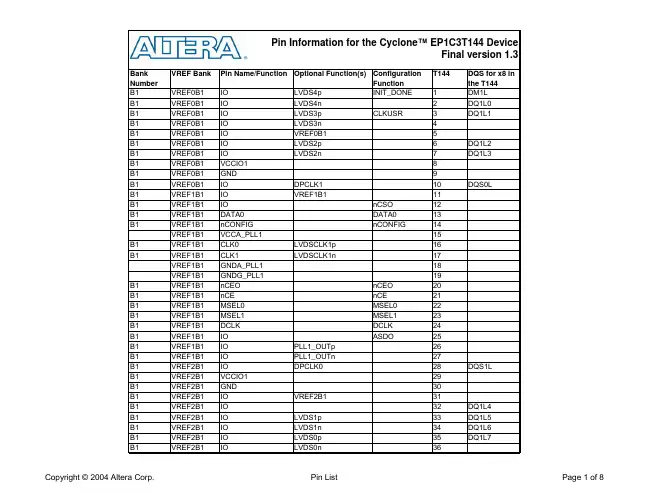

EP1C3T144C8芯片引脚对照表

- 格式:doc

- 大小:97.00 KB

- 文档页数:2

IC各脚功能.txt婚姻是键盘,太多秩序和规则;爱情是鼠标,一点就通。

男人自比主机,内存最重要;女人好似显示器,一切都看得出来。

【1】运放4558D(8脚)1:AMP OUT1 放大信号输出(1)2:IN1- 反相信号输入(1)3:IN1+ 同相信号输入(1)4:GND 接地5:IN2+ 同相信号输入(2)6:IN2- 反相信号输入(2)7:AMP OUT2 放大信号输出(2)8:Vcc 电源【2】功放TDA2822(8脚)1脚3脚左右输出5脚8脚左右反馈2脚4脚正负电源6脚7脚左右输入【3】音频处理SC7313与TM2313,用于车载影音系统(28脚)3路输入4声道输出【4】汽车专用4声道*40W集成运放驱动的OCL功放TDA7388与TDA7386(25脚)注:可用 7381 7382,TB2929HQ……7388和7850等多款IC,(此系列IC仅在于最后一个数字不同,功率不一样,而线路通用)11,12,14,15脚是输入端3,5脚后左7.9脚前左17.19脚前右21.23脚后右22脚:静音(此脚断会通电杂)【5】GPS模块各脚分布(32脚)注:天线处电压:3到3.3V1脚:右声道R2脚:左声道L3脚:地4脚:VB(蓝)5脚:VG(绿)6脚:VR(红)7脚:HS(开路白屏)8至11脚:空12:地13:DET(音频检测)14:空15:RST(复位)16:TXD(触摸)17至20:空21:D122:D223:CLK24:3V325:DEL26:CMD27:D328:D2【21到28是卡座】29至30:地31:ACC记忆32:电源B正(12V)【6】TM2313音频处理【7】BD3702音频处理【8】收音模块4730(24脚)1脚:dout(空,英文nc表示空)2脚: dfs(空)3脚:GPO3/DCLK(晶振脚)4脚:GPO2/INT(地)5脚:GPO1(电源串联1k接过来的电压)6脚至7脚:空8脚: FM天线9脚:RF天线(GND)10脚至11脚:空12脚 :AM天线13脚至14脚:GND15脚:RST(复位脚)16脚:SEN(通常接地)17脚:SCLK18脚:SDIO(DATA)19脚:RCLK(晶振脚)20脚至21脚:电源脚(VCC3.3V)22脚:GND23脚:音频(R)《通常用AR表示,全英文AUDIO即是AR》24脚:音频(L)《通常用AL表示,全英文AUDIO即是AL》【9】视频fms6502【10】SD卡(共9脚)(全名:SecureDigitalCard简称大卡)—安全数码卡1脚:CD DAT3 I/O/PP 卡监测数据位32脚:CMD PP 命令/回复3脚:Vss S 地4脚:Vcc S 供电电压【额定2.7至3.6V,一般机做定在3.3V】5脚:CLK I 时钟6脚:Css2 S 地7脚:DAT0 I/O/PP 数据位08脚:DAT1 I/O/PP 数据位19脚:DAT2 I/O/PP 数据位2注:TF卡(共8脚)(全名:TransFLash简称小卡,引脚定义同SD卡:只少一根地线,其它相同备注:TF卡可经SD卡套转换器后,当SD卡使用。

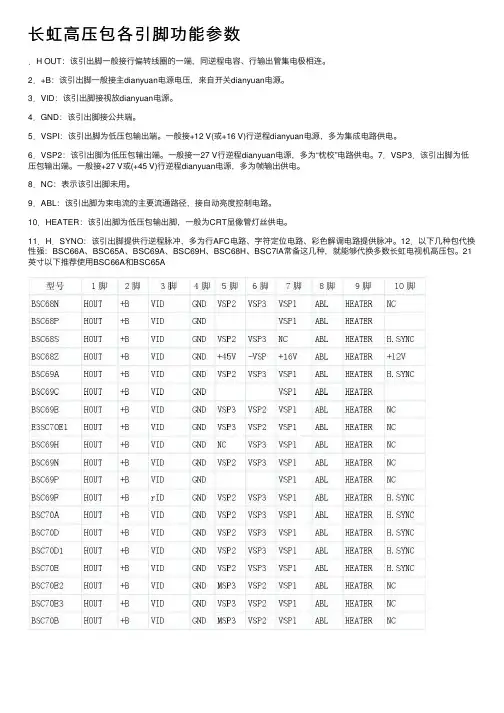

长虹⾼压包各引脚功能参数.H OUT:该引出脚⼀般接⾏偏转线圈的⼀端,同逆程电容、⾏输出管集电极相连。

2.+B:该引出脚⼀般接主dianyuan电源电压,来⾃开关dianyuan电源。

3.VID:该引出脚接视放dianyuan电源。

4.GND:该引出脚接公共端。

5.VSPI:该引出脚为低压包输出端。

⼀般接+12 V(或+16 V)⾏逆程dianyuan电源,多为集成电路供电。

6.VSP2:该引出脚为低压包输出端。

⼀般接⼀27 V⾏逆程dianyuan电源,多为“枕校”电路供电。

7.VSP3.该引出脚为低压包输出端。

⼀般接+27 V或(+45 V)⾏逆程dianyuan电源,多为帧输出供电。

8.NC:表⽰该引出脚未⽤。

9.ABL:该引出脚为束电流的主要流通路径,接⾃动亮度控制电路。

10.HEATER:该引出脚为低压包输出脚,⼀般为CRT显像管灯丝供电。

11.H.SYNO:该引出脚提供⾏逆程脉冲,多为⾏AFC电路、字符定位电路、彩⾊解调电路提供脉冲。

12.以下⼏种包代换性强:BSC66A、BSC65A、BSC69A、BSC69H、BSC68H、BSC7lA常备这⼏种,就能够代换多数长虹电视机⾼压包。

21英⼨以下推荐使⽤BSC66A和BSC65A长虹彩电⾏输出变压器的代换速查型号/脚位 1 2 3 4 5 6 7 8 9 10 备注(适⽤机型、机芯或⾏⼯作频率)BSC59A(单) C +B145V VID GND 12V -229V 20V ABL HEATER 46V 15.625KHZBSC59B(单) C +B145V VID GND 45V -260V 16V ABL HEATER 12V 15.625KHZ,代BSC68Z、62A BSC59T2B(单)VID C 131VPP +130V NC NC ABL GND 26V VHT 15.625KHZ,代BSC60SBSC60A(单) C VID +115V 28V 12V ABL 灯丝Nc Nc Nc 15.625khzBSC60AB(单) C +B115 VID GND 12V NC 12V ABL HEATER 137VPP 15.625khzBSC60C(单) C NC NC +B115 GND 14V NC ABL HEATER 127VPP 15.625khz,代BSC60C1BSC60CB(单)+B115 C VID GND -12 -119V 12V ABL HEATER 132VPP 15.625khzBSC60DB(单) C 120V VID GND 12V NC 47V ABL HEATER 142VPP 15.625khz,代BSC60DBSC60F(单) C +B115V VID GND -27V NC 15VABL HEATER 120VPP H2165K(B)、H21K58(B)、H21K60(B)、PF21B50、PF21B8、代BSC60F1 BSC60F1(单) C +B115V VID GND -27V NC 14V ABL HEATER 147VPP PF21B50(NC-9)可以60G BSC60G2(单)VID C 118VPP +B135V NC NC ABL GND HEATER 26V 15.625khz,代BSC60G2BBSC60G2B(单)VID C 118VPP +B135V NC 118V ABL GND HEATER 26V 15.625khzBSC60H(单) C +B115V VID GND 12V -118 42V ABL HEATER 142VPPBSC60H(B)(单)VIDC118VPP+B120NCNCBSC60H1(B)(单)VID C 130VPP +B120 NC NC ABL GND 25V BSC60HBBSC60H2(单) C +B115V VID GND 12V -109V 43V ABL HEATER 142VPPBSC60H3(单) C +B115V VID GND 9V 16V 45V ABL HEATER 133VPPBSC60H4(单) C +B115V VID GND 12V 16V 44V ABL HEATER 140VPPBSC60I(单) C +B115V VID GND NC NC 16V ABL HEATER 138VPPBSC60I(B)(单)VID2 C NC +B120V NC NC ABL GND 27.5V HEATER BSC60I1(B)与BSC60I(B)可互换BSC60I1(B)(单)VID C NC +B120 8V NC ABL GND 27V HEATER BSC60I1(B)与BSC60I(B)可互换BSC60J(单)VID C 132VPP +B130V NC NC ABL GND NC HEATER 可与BSC60J1、60H互换BSC60J2B VID C 118VPP +B115V NC NC ABL GND 22V HEATERBSC60K C +B115V VID GND -116V 12V 45V ABL HEATER 142VPP 66JBSC60K1B C +B115V VID GND 11V -121V 44V ABL HEATER 121VPPBSC60KB C +B115V VID GND 11V -121V 44V ABL HEATER 142VPP 可与BSC60K1B互换BSC60L C VID +B115V GND 30V 11V ABL HEATER NC NCBSC60N C +B130V VID GND NC NC 16V ABL HEATER 140VPPBSC60P C+B115VVIDGNDNC NC 15V ABL HEATER 134VPPBSC60P2 C +B115V VID GND NC 15V 25V ABL HEATER 140VPPBSC60P3 C +B115V VID GND NC NC 14V ABL HEATER 143VPPBSC60S VID C 136VPP +B130V NC NC ABL GND NC HEATER 可与BSC60T2互换BSC60T VID C 135VPP +B130V NC NC ABL GND NC HEATER 可与BSC60T2、BSC60T/U2互换BSC60U VID C 79VPP +B119V NC 25V ABL GND NC HEATERBSC60V1 VID C 138VPP +B130V NC 27V ABL GND NC HEATERBSC60W C +B115V VID GND 10V 14.5V 38.7V GND HEATER 123VPP SF1487DVBSC62A C +B135V VID GND 45V -225V 16V ABL HEATER 12V 59ABSC62B C +B115V VID GND 48V NC 19V ABL HEATER NCBSC62B2 C +B120V 14V GND GND -12V 11V ABL HEATER VIDBSC62CB +B116V C VID GND -12。

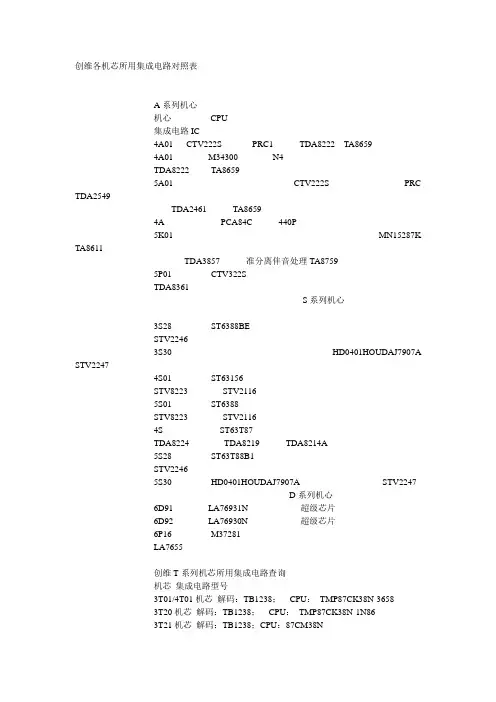

创维各机芯所用集成电路对照表A系列机心机心CPU集成电路IC4A01 CTV222S PRC1 TDA8222 TA86594A01 M34300 N4TDA8222 TA86595A01 CTV222S PRC TDA2549TDA2461 TA86594A PCA84C 440P5K01 MN15287K TA8611TDA3857 准分离伴音处理TA87595P01 CTV322STDA8361S系列机心3S28 ST6388BESTV22463S30 HD0401HOUDAJ7907A STV22474S01 ST63156STV8223 STV21165S01 ST6388STV8223 STV21164S ST63T87TDA8224 TDA8219 TDA8214A5S28 ST63T88B1STV22465S30 HD0401HOUDAJ7907A STV2247D系列机心6D91 LA76931N 超级芯片6D92 LA76930N 超级芯片6P16 M37281LA7655创维T系列机芯所用集成电路查询机芯集成电路型号3T01/4T01机芯解码:TB1238;CPU:TMP87CK38N-36583T20机芯解码:TB1238;CPU:TMP87CK38N-1N863T21机芯解码:TB1238;CPU:87CM38N3T30机芯21TB9000;CPU与解码为:TMP8803\TMP88233T30机芯21TM9000;CPU与解码为:TMP88033T30机芯一路A V;CPU与解码为:TMP88013T30/3T36机芯二路A V;CPU与解码为:TMP88033T30/3T36机芯一路A V;CPU与解码为:TMP88233T30/3T36机芯二路A V;CPU与解码为:TMP88233T36机芯CPU与解码为:TMP8803\TMP88234T20机芯解码:TB1238;CPU:TMP87CK38N-1N864T30机芯CPU与解码为:TMP8809;3路A V4T30/5T36机芯CPU与解码为:TMP8809;2路A V4T30机芯CPU与解码为:TMP8807/TMP88274T30/5T36机芯CPU与解码为:TMP8829新软件;3路AV4T36机芯CPU与解码为:TMP8803;2路A V4T36机芯CPU与解码为:TMP8823;2路A V5T03机芯CTV-2981;解码:TB1238;CPU:TMP87CK38N-36585T20机芯25Nl9000;解码:TB1240;CPU:TMP87CK38N-1R025T21机芯解码:TB1240;CPU:TMP87CS38N-3ED9(早期);CPU:TMP87CS38N-3G82(后期)5T25机芯解码:TB1240;CPU:TMP87CK38N-3G825T28机芯29SP9000;解码:TB1240;CPU:TMP87CK38N-4FP15T30机芯25NI9000;CPU与解码为:TMP8809\TMP88295T35机芯CPU与解码为:TMP8823;二路AV5T36机芯CPU与解码为:TMP8809\TMP8829创维D系列机芯所用集成电路查询机芯集成电路型号5D01机芯100Hz机型:2981-100;CPU:C87C766BRD;解码:TDA9143;5D20机芯CPU:ST92196A/B;解码:DPTV-66305D25机芯CPU:ST92196A/B;解码:DPTV-66305D25机芯34英寸;CPU:ST92196A/B;解码:DPTV-66305D26机芯29TIDP;CPU:ST92196A/B;解码:DPTV5D26机芯34TPDP;CPU:ST92196A/B;解码:DPTV5D28机芯34TIDP;CPU:ST92196A/B;解码:DPTV5D30机芯CPU:M37280/M37281;5D60机芯机型:29TBDA;CPU:MSP8849;解码:DPTV5D66机芯机型:29TBDP;CPU:MSP8849;解码:DPTV5D70机芯CPU:M37274;解码:VPC3230;变频:NV3205D76机芯CPU:M37274;解码:DPTV5D78机芯34TPDP;CPU:M37274;解码:DPTV5D90机芯解码:VPC32156D72机芯机型:29T68HD;CPU:M37274/M37281;解码:VPC3230;变频:PW12356D76机芯机型:34T66HD;CPU:M37274/M37281;解码:DPTV6D78机芯CPU:M372816D92机芯解码:LA76930;2004-05-26版本,行频:33.75K6D92机芯29英寸北京松下管;解码:LA76930;2004-05-26版本,行频:35K6D92机芯25英寸;解码:LA76930;2004-08-02版本;6路A V,行频:35K6D92机芯25英寸;解码:LA76930;2004-08-02版本;4路A V,行频:35K6D95机芯29英寸;解码:DVP004;CPU:S88496D95机芯34英寸;解码:DVP004;CPU:S88496D96机芯29英寸;解码:SVPV12;CPU:S8849创维I系列机芯所用集成电路查询机芯集成电路型号5I01机芯双频机;CPU:CCZ3005;解码:VPC32155I30机芯解码与CPU为:VCT3803创维M系列机芯所用集成电路查询机芯集成电路型号5M10机芯双频机;CPU:M37274;解码:VPC3210A6M20机芯29寸高清彩电系列;CPU:DS88C(P)4504;解码:DPTV-3D6M20机芯34寸高清彩电系列;CPU:DS88C(P)4504;解码:DPTV-3D6M23机芯34寸高清彩电系列:配松下管6M23机芯34寸高清彩电系列:配东芝管6M23机芯34寸高清彩电系列:配三星管创维P系列彩电机芯所用集成电路型号查询机芯集成电路型号3P10/4P10机芯解码:OM8838;CPU:MTV8803P20/4P20机芯解码:OM8838;CPU:KS88C83163P21机芯解码:OM8838PS;CPU:4749-Z00010-42\4749-Z00011-423P30机芯CPU与解码为:TDA9370PS-N23P30机芯CPU与解码为:TDA9370PS|N2|AI08433P30机芯CPU与解码为:TDA9370PS|N23P30机芯CPU与解码为:OM8370PS4P30机芯CPU与解码为:TDA9370PS-N2;四路A V输入4P30机芯CPU与解码为:TDA9370PS;二路A V输入4P30机芯CPU与解码为:TDA9370PS;一路A V输入4P36机芯29寸华飞管;CPU与解码为:TDA9370;一路A V输入5P03机芯CPU:47-Z00001-42到47-Z00007-42都为此机芯CPU,其中Z0003与Z0006为带丽音功能,可互换,另外其它的可互换。

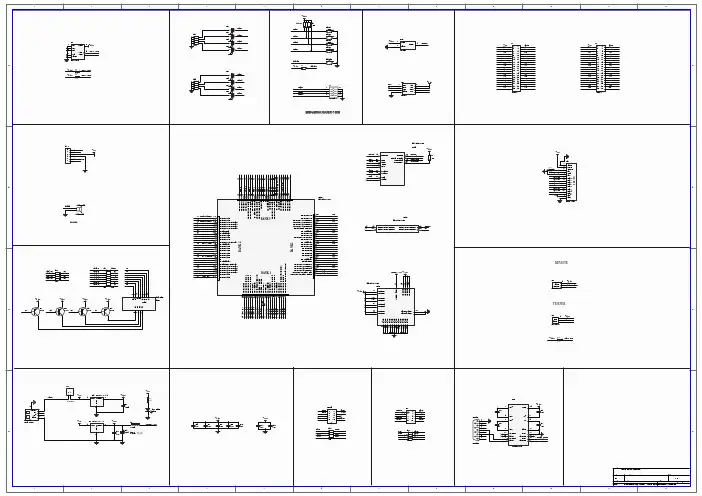

EP1C3T144FPGAdevelopboardmanual(开发板原理图)FPGA develop board manual ALTERA Cyclone EP1C3T144ALTERA Cyclone 系列的fpga是altera 公司针对底端用户推出的一个系列的fpga。

具有成本低,使用的方便的优点,规模从3000到20000LE。

这一块实验板用的EP1C3T144的芯片,有3000LE逻辑资源,另外还有13条M4K RAM (共6.5Kbyte),另外还有还有一个数字锁相环。

这些资源能够足够应付电子设计竞赛和日常教学的需要,也可以作为初学者入门学习fpga的工具。

1. 开发板介绍1.1. 总体介绍开发板的电路图,如附录所示,电路图一共可分为9个部分:电源部分、按键和LED、下载配置部分、复位部分、外部时钟、滤波电容、用户扩展接口、5 1单片机接口、FPGA 芯片。

1.2. 具体介绍1.2.1. 电源部分板子由外部提供5V电源,使用的圆头插座的封装,可以直接用5V的电源适配器插上使用,不需要直流稳压电源,FPGA的IO的电源是3.3V,内核的电压是1.5V,所以用上两个LEO,一个将5V转到3.3V,另一个将3.3V转到1.5V,加上一些滤波电容,板上的其他外设的电源均是3.3V,另外有3.3V的电源指示灯,表示电源是否正常,还有防反插二极管,防止电源反插,对器件造成损坏。

1.2.2. 按键和LED板上提供4个拨码按键和4个led,分别接到fpga的8个IO引脚上,具体的引脚可以参看电路图或者丝印。

对于初学者,按键和led 可以用外当成最简单的外设,用和来控制这些外设。

对于用该板作开发的用户来说,可以把按键当成键盘控制,而把led当成提示来用。

1.2.3. 下载配置部分大家都知道fpga是sram型的可编程逻辑器件,不像rom型可编程器件cpld那样,通过jtag就可以直接把代码固化片子里面。

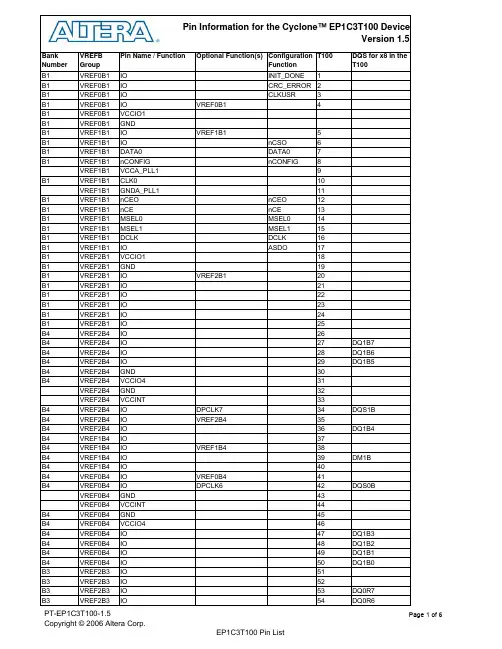

B1VREF0B1IO INIT_DONE1B1VREF0B1IO CRC_ERROR2B1VREF0B1IO CLKUSR3B1VREF0B1IO VREF0B14B1VREF0B1VCCIO1B1VREF0B1GNDB1VREF1B1IO VREF1B15B1VREF1B1IO nCSO6B1VREF1B1DATA0DATA07B1VREF1B1nCONFIG nCONFIG8VREF1B1VCCA_PLL19B1VREF1B1CLK010VREF1B1GNDA_PLL111B1VREF1B1nCEO nCEO12B1VREF1B1nCE nCE13B1VREF1B1MSEL0MSEL014B1VREF1B1MSEL1MSEL115B1VREF1B1DCLK DCLK16B1VREF1B1IO ASDO17B1VREF2B1VCCIO118B1VREF2B1GND19B1VREF2B1IO VREF2B120B1VREF2B1IO21B1VREF2B1IO22B1VREF2B1IO23B1VREF2B1IO24B1VREF2B1IO25B4VREF2B4IO26B4VREF2B4IO27DQ1B7 B4VREF2B4IO28DQ1B6 B4VREF2B4IO29DQ1B5 B4VREF2B4GND30B4VREF2B4VCCIO431VREF2B4GND32VREF2B4VCCINT33B4VREF2B4IO DPCLK734DQS1B B4VREF2B4IO VREF2B435B4VREF2B4IO36DQ1B4 B4VREF1B4IO37B4VREF1B4IO VREF1B438B4VREF1B4IO39DM1B B4VREF1B4IO40B4VREF0B4IO VREF0B441B4VREF0B4IO DPCLK642DQS0B VREF0B4GND43VREF0B4VCCINT44B4VREF0B4GND45B4VREF0B4VCCIO446B4VREF0B4IO47DQ1B3 B4VREF0B4IO48DQ1B2 B4VREF0B4IO49DQ1B1 B4VREF0B4IO50DQ1B0 B3VREF2B3IO51B3VREF2B3IO52B3VREF2B3IO53DQ0R7 B3VREF2B3IO54DQ0R6B3VREF2B3IO55DQ0R5 B3VREF2B3IO56DQ0R4 B3VREF2B3IO VREF2B357B3VREF2B3GND58B3VREF2B3VCCIO359B3VREF1B3CONF_DONE CONF_DONE60B3VREF1B3nSTATUS nSTATUS61B3VREF1B3TCK TCK62B3VREF1B3TMS TMS63B3VREF1B3TDO TDO64B3VREF1B3IO65DM0R B3VREF1B3CLK266B3VREF1B3TDI TDI67B3VREF1B3IO VREF1B368B3VREF0B3IO69DQ0R3 B3VREF0B3IO70DQ0R2 B3VREF0B3IO71DQ0R1 B3VREF0B3IO DPCLK472DQS0R B3VREF0B3GNDB3VREF0B3VCCIO3B3VREF0B3IO VREF0B373B3VREF0B3IO74DQ0R0 B3VREF0B3IO75B2VREF0B2IO76DQ1T0 B2VREF0B2IO77DQ1T1 B2VREF0B2IO78DQ1T2 B2VREF0B2IO79DQ1T3 B2VREF0B2VCCIO280B2VREF0B2GND81VREF0B2VCCINT82VREF0B2GND83B2VREF0B2IO DPCLK384DQS0T B2VREF0B2IO VREF0B285B2VREF1B2IO86B2VREF1B2IO87B2VREF1B2IO VREF1B288B2VREF1B2IO89B2VREF2B2IO90DM1T B2VREF2B2IO VREF2B291B2VREF2B2IO DPCLK292DQS1T VREF2B2VCCINT93VREF2B2GND94B2VREF2B2VCCIO295B2VREF2B2GND96B2VREF2B2IO97DQ1T4 B2VREF2B2IO98DQ1T5 B2VREF2B2IO DEV_OE99DQ1T6 B2VREF2B2IO DEV_CLRn100DQ1T7VCCIO[1..4]Power These are I/O supply voltage pins for banks 1 through 4. Each bank can support a different voltage level. VCCIO supplies power to the output buffers for all I/O standards. VCCIO also supplies power to the input buffers used for the LVTTL, LVCMOS, 1.5-V, 1.8-V, 2.5-V, and 3.3-V PCI I/O standards.VCCINT Power These are internal logic array voltage supply pins. VCCINT also supplies power to the input buffers used for the LVDS, SSTL2, and SSTL3 I/O standards.GNDGroundDevice ground pins. All GND pins should be connected to the board GND plane.VREF[0..2]B[1..4]I/O, Input Input reference voltage for banks 1-4. If a bank uses a voltage-referenced I/O standard, then these pins are used as the voltage-reference pins for the bank. If voltage reference I/O standards are not used in the bank, the VREF pins are available as user I/O pins.VCCA_PLL1Power Analog power for PLL1. The designer must connect this pin to 1.5 V, even if the PLL is not used.GNDA_PLL1Ground Analog ground for PLL1. The designer can connect this pin to the GND plane on the board.NCNo Connect No connect pins should not be connected on the board. They should be left floating.CONF_DONE Bidirectional (open-drain)This is a dedicated configuration status pin; it is not available as a user I/O pin.nSTATUS Bidirectional (open-drain)This is a dedicated configuration status pin; it is not available as a user I/O pin.nCONFIGInputDedicated configuration control input. A low transition resets the target device; a low-to-high transition begins configuration. All I/O pins tri-state when nCONFIG is driven low.DCLK Input (PS mode), Output (AS mode)In passive serial configuration mode, DCLK is a clock input used to clock configuration data from an external source into the Cyclone device. In active serial configuration mode, DCLK is a clock outputfrom the Cyclone device (the Cyclone device acts as master in this mode). This is a dedicated pin used for configuration.DATA0InputDedicated configuration data input pin.nCE Input Active-low chip enable. Dedicated chip enable input used to detect which device is active in a chain of devices. When nCE is low, the device is enabled. When nCE is high, the device is disabled.nCEOOutputOutput that drives low when device configuration is complete. During multi-device configuration, this pin feeds a subsequent device’s nCE pin.ASDO I/O, OutputActive serial data output from the Cyclone device. This output pin is utilized during active serial configuration mode. The Cyclone device controls configuration and drives address and control information out on ASDO. In passive serial configuration, this pin is available as a user I/O pin.nCSO I/O, OutputChip select output that enables/disables a serial configuration device. This output is utilized during active serial configuration mode. The Cyclone device controls configuration and enables the serial configuration device by driving nCSO low. In passive serial configuration, this pin is available as a user I/O pin.CRC_ERRORI/O, OutputActive high signal that indicates that the error detection circuit has detected errors in the configuration SRAM bits. This pin is optional and is used when the CRC error detection circuit is enabled.INIT_DONE I/O, Output (open-drain)This is a dual-purpose pin and can be used as an I/O pin when not enabled as INIT_DONE. When enabled, the pin indicates when the device has entered user mode. This pin can be used as a user I/Opin after configuration.CLKUSRI/O, InputOptional user-supplied clock input. Synchronizes the initialization of one or more devices. This pin can be used as a user I/O pin after configuration.DEV_CLRn I/O, InputDual-purpose pin that can override all clears on all device registers. When this pin is driven low, all registers are cleared; when this pin is driven high, all registers behave as defined in the design.DEV_OE I/O, Input Dual-purpose pin that can override all tri-states on the device. When this pin is driven low, all I/O pins are tri-stated; when this pin is driven high, all I/O pins behave as defined in the design.MSEL[1..0]Input Dedicated mode select control pins that set the configuration mode for the device.TMS Input This is a dedicated JTAG input pin.TDI Input This is a dedicated JTAG input pin.TCK Input This is a dedicated JTAG input pin.TDO Output This is a dedicated JTAG output pin.CLK0Input Dedicated global clock input.CLK2InputDedicated global clock input.Clock and PLL PinsSupply and Reference PinsConfiguration and JTAG PinsDPCLK[7, 6, 4, 3, 2]I/O Dual-purpose clock pins that can connect to the global clock network. These pins can be used for high fan-out control signals, such as clocks, clears, IRDY, TRDY, or DQS signals. These pins are also available as user I/O pins.DQS[0..1][L,R,T,B]I/O Optional data strobe signal for use in external memory interfacing. These pins also function as DPCLK pins; therefore, the DQS signals can connect to the global clock network. A programmable delay chain is used to shift the DQS signals by 90 or 72 degrees.DQ[0..7][L,R,T,B]I/O Optional data signal for use in external memory interfacing.DM[0..1][L,R,T,B]I/O Optional data mask output signal for use in external memory interfacing.Dual-Purpose External Memory Interface PinsPin Information for the Cyclone™ EP1C3T100 Device, ver 1.5VREF2B2VREF1B2VREF0B2B2V R E F 0B 1B 1B 3V R E F 0B 3V R E F 1B 1V R E F 1B 3PLL1V R E B 2B 1V R E B 2B 3B4VREF2B4VREF1B4VREF0B4Notes:1.This is a top view of the silicon die.2.This is a pictoral representation only to get an idea of placement on the device. Refer to the pin-list andthe Quartus II for exact locations.Version 1.5 Version Number Date Changes Made1.53/6/2006Added CRC_ERROR pin in Pin List and Pin Definitions。

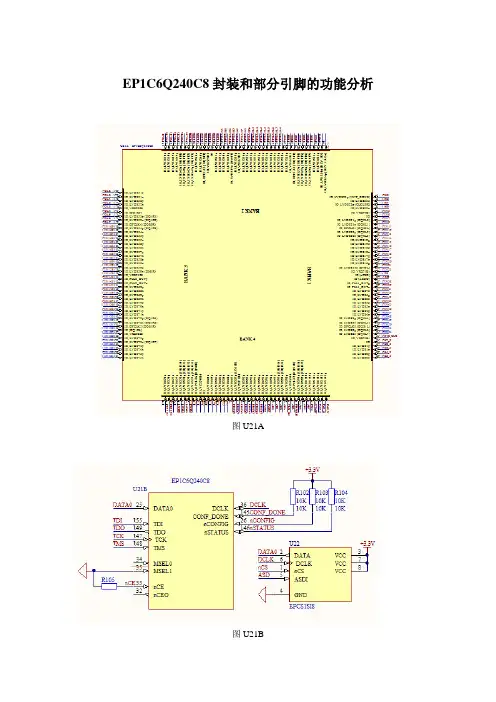

EP1C6Q240C8封装和部分引脚的功能分析图U21A图U21B图U21C图U21D第一部分:封装图U21A、U21B、U21C、U21D表示的是同一块芯片EP1C6Q240C8,有240个引脚,采用的是PQFP封装(即Plastic Quad Flat Package,塑料方块平面封装),PQFP封装的芯片的四周均有引脚,而且引脚之间距离很小,管脚也很细,一般大规模或超大规模集成电路采用这种封装形式。

用这种形式封装的芯片必须采用SMT(Surface Mount Technology,表面组装技术)将芯片边上的引脚与主板焊接起来。

对于SMT技术,个人理解,即表面组装技术,一般用来焊接一些引脚在几百以上的芯片,比如说BGA,PGA一般都采用这种技术;例如笔记本主板上的intel北桥芯片,一般都采用球形封装,又如比较古老的Intel 965底部球形引脚大约有600多个,现在笔记本流行用的P43、P45、P55、X58,从P43一代引脚多达几千个甚至更多,这样做的好处是节约面积,坏处是测试的时候比较麻烦,像BGA这种封装的芯片一般焊上去之后,顶部要引出几个接点,以防止在使用过程中坏掉,方便用万用表或者示波器来测试各个通路便于修理。

对于这几种类型的芯片,除了PQFP少数罕见的高手能手工焊接之外,一般都采用贴片机来进行专门的焊接工作.这里简单介绍一下这两种封装:PQFP/PFP封装具有以下特点1.适用于SMD表面安装技术在PCB电路板上安装布线。

2。

适合高频使用。

2.操作方便,可靠性高。

3.芯片面积与封装面积之间的比值较小。

4.Intel系列CPU中80286、80386和某些486主板采用这种封装形式.这里的SMD表示的是贴片组装器件;BGA球栅阵列封装到产品的功能性,当IC的频率超过100MHz时,传统封装方式可能会产生所谓的“CrossTalk (串扰)"现象,而且当IC的管脚数大于208 Pin时,传统的封装方式有其困难度。

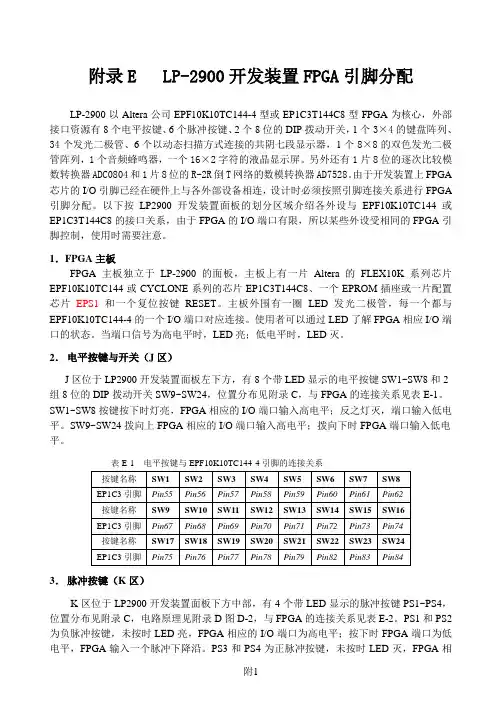

附录E LP-2900开发装置FPGA引脚分配LP-2900以Altera公司EPF10K10TC144-4型或EP1C3T144C8型FPGA为核心,外部接口资源有8个电平按键、6个脉冲按键、2个8位的DIP拨动开关,1个3×4的键盘阵列、34个发光二极管、6个以动态扫描方式连接的共阴七段显示器,1个8×8的双色发光二极管阵列,1个音频蜂鸣器,一个16×2字符的液晶显示屏。

另外还有1片8位的逐次比较模数转换器ADC0804和1片8位的R-2R倒T网络的数模转换器AD7528。

由于开发装置上FPGA 芯片的I/O引脚已经在硬件上与各外部设备相连,设计时必须按照引脚连接关系进行FPGA 引脚分配。

以下按LP2900开发装置面板的划分区域介绍各外设与EPF10K10TC144或EP1C3T144C8的接口关系,由于FPGA的I/O端口有限,所以某些外设受相同的FPGA引脚控制,使用时需要注意。

1.FPGA主板FPGA主板独立于LP-2900的面板,主板上有一片Altera的FLEX10K系列芯片EPF10K10TC144或CYCLONE系列的芯片EP1C3T144C8、一个EPROM插座或一片配置芯片EPS1和一个复位按键RESET。

主板外围有一圈LED发光二极管,每一个都与EPF10K10TC144-4的一个I/O端口对应连接。

使用者可以通过LED了解FPGA相应I/O端口的状态。

当端口信号为高电平时,LED亮;低电平时,LED灭。

2.电平按键与开关(J区)J区位于LP2900开发装置面板左下方,有8个带LED显示的电平按键SW1~SW8和2组8位的DIP拨动开关SW9~SW24,位置分布见附录C,与FPGA的连接关系见表E-1。

SW1~SW8按键按下时灯亮,FPGA相应的I/O端口输入高电平;反之灯灭,端口输入低电平。

SW9~SW24拨向上FPGA相应的I/O端口输入高电平;拨向下时FPGA端口输入低电平。

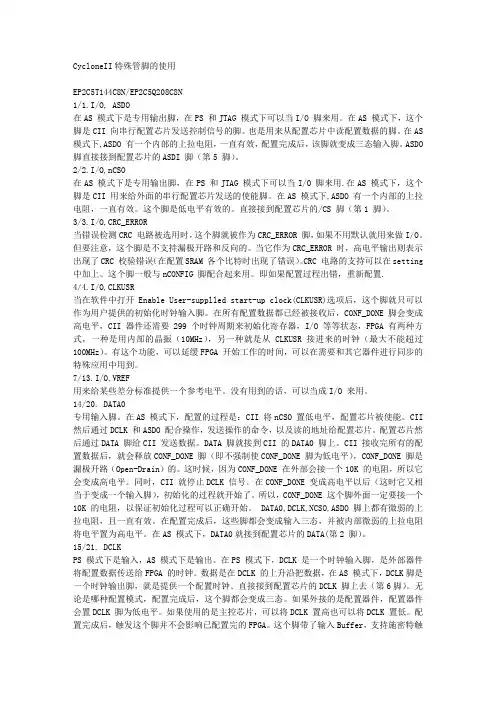

CycloneII特殊管脚的使用EP2C5T144C8N/EP2C5Q208C8N1/1.I/O, ASDO在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用。

在AS 模式下,这个脚是CII 向串行配置芯片发送控制信号的脚。

也是用来从配置芯片中读配置数据的脚。

在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效,配置完成后,该脚就变成三态输入脚。

ASDO 脚直接接到配置芯片的ASDI 脚(第5 脚)。

2/2.I/O,nCSO在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用.在AS 模式下,这个脚是CII 用来给外面的串行配置芯片发送的使能脚。

在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效。

这个脚是低电平有效的。

直接接到配置芯片的/CS 脚(第1 脚)。

3/3.I/O,CRC_ERROR当错误检测CRC 电路被选用时,这个脚就被作为CRC_ERROR 脚,如果不用默认就用来做I/O。

但要注意,这个脚是不支持漏极开路和反向的。

当它作为CRC_ERROR 时,高电平输出则表示出现了CRC 校验错误(在配置SRAM 各个比特时出现了错误)。

CRC 电路的支持可以在setting 中加上。

这个脚一般与nCONFIG 脚配合起来用。

即如果配置过程出错,重新配置.4/4.I/O,CLKUSR当在软件中打开Enable User-supplled start-up clock(CLKUSR)选项后,这个脚就只可以作为用户提供的初始化时钟输入脚。

在所有配置数据都已经被接收后,CONF_DONE 脚会变成高电平,CII 器件还需要299 个时钟周期来初始化寄存器,I/O 等等状态,FPGA 有两种方式,一种是用内部的晶振(10MHz),另一种就是从CLKUSR 接进来的时钟(最大不能超过100MHz)。

有这个功能,可以延缓FPGA 开始工作的时间,可以在需要和其它器件进行同步的特殊应用中用到。

高压包型号脚位查询大全机型国标型号脚位HV阳极夏普C-1811DK BSC24-010821-2,3-5-7-8-10,4-6-924KV夏普C-2011DK BSC24-010821-2,3-5-7-8-10,4-6-924KV夏普C-2010DK BSC24-010821-2,3-5-7-8-10,4-6-924KV夏普C-2091DK BSC24-010821-2,3-5-7-8-10,4-6-924KV夏普C-5405DK BSC25-121241-2-5-6-7-10,3-4-8,11-1225KV夏普C-5420DK BSC25-121241-2-5-6-7-10,3-4-8,11-1225KV夏普C-5404CK BSC25-121241-2-5-6-7-10,3-4-8,11-1225KV夏普C-5422CK BSC25-121241-2-5-6-7-10,3-4-8,11-1225KV虹美C5403BSC25-121241-2-5-6-7-10,3-4-8,11-1225KV虹美C5408-1BSC25-121241-2-5-6-7-10,3-4-8,11-1225KV夏普C-2001DK BSC24-010221-2,3-4-6-8-11,5-9-1024KV夏普C-2002SG BSC24-010221-2,3-4-6-8-11,5-9-1024KV夏普C-2002SC BSC24-010221-2,3-4-6-8-11,5-9-1024KV东芝298X8M BSC30-235151-2-3,4-5-6-7-9-1030KV东芝2840XH BSC29-235381-2-3,4-5-6-7-9-1029KV东芝28J52BSC25-236701-2-3,4-6-7-9-1025KV成都C37-851BSC22-0974A(83P)1-7,5-6,8-9-1022KV成都C47-351BSC24-09074(83P)1-7,5-6,8-9-1024KV孔雀KQ47-9BSC24-0974C(83P)1-2-7-8,5-6,8-9-1024KV金凤C44MZ BSC25-0974D(83P)1-7,5-6,8-9-1025KV成都C47-851B BSC25-0974B(83P)1-7,5-6,8-9-1024KV三洋CTP-3243BSC22-0189A(80P)1-2-4-10,5-7-822KV三洋CTP-3916BSC24-01089(80P)1-2-4-10,5-7-824KV三洋CTP-7922BSC25-09195(80P)1-2-3,7-9,5-625KV三洋CTP-3507BSC22-0135A(79P)1-2,4-5-6,7-822KV三洋CTP-3920BSC24-01035(79P)1-2,4-5-6,7-822KV三洋CTP-1309R BSC07-142871-2,3-4-5,7-87KV三洋CTP-3903BSC21-102261-2-4-10,5-6-721KV三洋CEP-6955-00BSC25-162361-3,4-5-8-1025KV三洋CTP-4507BSC21-102661-2-4-10,5-6-721KV三洋CEM-6022P-00B SC25-212211-2,3-4-5-625KV天鹅CS54-A3A BSC25-21366(A3-B)1-2,3-4-5-625KV三洋CEM2515C BSC27-095691-2-4,3-5-6-8-927KV三洋CMX2510C-00BSC24-23634(A4-4)1-2-4,5-8-9-1024KV三洋46B4FT-01BSC13-012391-2,4-5-6,7-813KV三洋CVP721FT BSC28-09464(T8BA-001-5-7.2-6-8-928KV日立C27SX1BSC29-235391-2,3-4-5-6-8-9-1029KV三元C-1411DF BSC22-040182-9,3-4-6-7-10,5-822KV夏普C-3700DK BSC22-120131-2-5-6-7-10,3-4-8,11-1222KV夏普CT-1438R BSC22-082191-2,3-4-6-8,5-9-1022KV夏普21D-CM BSC22-235701-2-9,3-4-6-7-922KV夏普21N52-E1BSC27-235851-2-5,3-6-8-927KV天鹅CS37-C1/4A BSC22-1168A1-2-4,2-6-822KV飞跃44C3Y3-1BSC24-110681-2-4,2-6-824KV金星C564BSC24-11068B1-2-4,2-6-824KV 夏普DV-2130EX BSC26-122531-2-5-6-7-10,3-4-826KV 夏普C-5406SPN/SPM BSC26-122551-3-6,2-5-7-8,4-1026KV 夏普16P-A60E BSC23-14224</TR>夏普C-1800DK BSC24-012461-2-7-8,3-4,5-6,10-1122KV 夏普C-1803DK BSC24-040161-3-6,2-7-8,4-5,10-1124KV 夏普C-1801DK BSC24-010821-2,3-5-7-8-10,4-6-924KV 夏普C-1805DK BSC24-030401-3-4,6-7-924KV 夏普C-1850CK BSC25-121241-2-5-6-7-10,3-4-8,11-1225KV 夏普C-202NK BSC24-010221-2,3-4-6-8-11,5-9-1024KV 松下TC-482D BSC22-05136A1-6-9,2-4-522KV 松下TC-25GF10R BSC31-235961-2-7,4-5-631KV 松下TC-25V40RQ BSC29-235761-2,3-4-5-629KV 松下TC-33V32H BSC27-236001-2,3-4-5,6-7-1027KV 松下TC-29VR BSC29-236141-2,3-4-5,6-7-1029KV 松下2188S(假)BSC25-216221-2,3-4-5-625KV 松下TC-2140BSC30-236351-2,4-5-7,6-8-929KV 熊猫DB47C3-1BSC24-05136(M11)1-6-9,2-4-524KV 松下TC-481D BSC22-141121-3-4,2-5-622KV 松下TC-430D BSC22-0646A(M12)1-2-3-4,6-8-922KV 松下TC-4230DD BSC24-06046(M12)1-2-3-4,6-8-924KV 松下TC-840D BSC24-061341-2-3-4,6-8-924KV 松下TC-1871DR BSC25-03106(M15L)1-2-7,3-5-6-9,4-1025KV 22"钻石BSC25-072351-2-3-4,6-8-925KV 松下TH14-N8R BSC22-062041-2-6-8,3-4-522KV 松下TC-875D BSC22-01280棕-红粗-兰粗,粉红白22KV 松下TC-M25C BSC26-162631-2-7,3-5-6-9,4-1026KV 松下TC-2188S/M B SC26-233911-2-10,3-5-725KV 松下TC-2188M BSC26-233921-2-10,3-5-727KV 松下TC-2588BSC28-23415(C150)1-2-10,3-5-728KV 松下TC-25D BSC28-23432(M15L)1-2-7,3-5-6-9,4-1028KV 西湖47CD3BSC24-01113(X56P)1-2-3-5,4-7-8-9-1024KV 三星2506BSC27-235831-2-3,4-5-6-7-9-1027KV 东芝2150XHC BSC26-235941-2-3,4-6-7-9-1026KV 东芝2950XHC BSC33-236411-2-3,4-5-6-7-9-1033KV 黄河HC44FS-1BSC24-02038(L851)1-2-3-5,4-6-1024KV 长城JTC371-2BSC24-0238A(L851)1-2-3-5,4-6-1022KV 凯歌4C3703BSC22-010501-2-3,4-7-8-9-1022KV 东芝C-1421Z BSC22-011001-2-3-4-5,6-9-1022KV 东芝C-1615C BSC22-031251-2-5,4--6-7-9-1022KV 东芝C-182E5C BSC24-030811-2-3-5,4-6-7-9-1024KV 东芝C-181R3C BSC25-041071-2-3-5,4-7-8-9-1025KV 东芝C-1821Z BSC24-010871-2-3-4-5-8,6-9-1024KV 东芝C-187D5C2BSC25-031911-2-3-5,4-6-7-9-1025KV 东芝C2038DH BSC24-011441-2-3-4-5-8,6-9-1024KV 东芝C-2120HC BSC25-031891-2-3,4-6-7-9-1025KV 东芝288X6M2BSC30-162421-2-3,4-6-7-9-1030KV东芝C-205D5C BSC23-023031-2-3-5,4-6-7-9-1023KV 东芝C-2506XH BSC28-233841-2-3,4-5-6-7-9-1028KV 东芝C-2104BSC25-033951-2-3,4-5-6-8-925KV 东芝C-2112SF BSC27-034921-2-3,4-6-7-9-1027KV 松下TC-29GF12G BSC32-23509(M17)1-2-7,3-4-532KV 松下TC21L3RQ BSC29-23553(MX1A)1-2,3-5-6-730KV 松下TC-25V/35HN/R BSC29-235561-2,3-4-5,6-7-1029KV 松下TC-2186BSC28-235681-2-7,3-5-6-9-1028KV 松下TC-29V30R BSC24-236211-2-3,4-6-7-9-1024KV 松下TLF15538F BSC28-236471-2-7,3-4-928KV 松下JH-29AIS BSC29-246481-2-3,4-5-6-829KV 松下TC-28WG25G BSC30-276881-2-8,3-4-5-730KV 松下TC-29V2H BSC26-236971-2,3-4-5,6-7-1027KV 松下TLF14628F BSC22-067281-3-4-5-8,2-622KV 松下BSC27-237441-2-10,3-4-5-6-727KV 松下TC-29GF-30BSC24-237531-2-3,4-5-6-7-9-1024KV 松下TC-AV29C BSC32-237541-2-7,3-6-932KV 100"松下投影TC100BSC30-015231-4-7-8-9,3-5-630KV 50"-100"松下投影P BSC28-075453-4,5-628KV 日立CRP-149D BSC22-01177A1-2,3-4-6,5-8,11-1222KV 日立CTK-216D BSC24-011771-2,3-4-6,5-8,11-1222KV 日立C29G67S BSC27-236031-2,3-4-5-6-8-9-1027KV 日立C21D8A BSC27-236181-2,3-5-6-8-9-1022KV 日立CRP-450D BSC22-10109(NP8)1-2-4,3-7-10,11-1222KV 日立CRP-451D BSC22-08103(NP82C)1-2,3-5-8-9,6-7-1022KV 福日HFC-1421BSC23-08102(NP82C211-4-5,2-3-6-8,9-1023KV 日立CAP-169D BSC23-081301-4-5,6-10,8-923KV 日立CPT-1801SF BSC25-08097(NP84C221-4-5,2-3-6-8,9-1025KV 日立CPT-1805BSC24-08008(NP84C201-5,2-3-4-6-8,9-1024KV 环宇CPS182BSC24-08006(NP82C4)1-5,2-3-4-6-8,9-1024KV 日立CPT-2057BSC24-01101(NP8C)1-2-4,3-7-10,11-1224KV 日立CMT-1910BSC25-16175(NP86C)1-2-5,3-4-6-8,9-1025KV 日立CEP-2085BSC25-081781-5,2-6-8,3-9,4-1025KV 日立CPT-2177SF/DU BSC25-08230(G7PN)1-5,2-3-4-6-8,9-1024KV 日立CEP-5322BSC25-102322-5,3-6,4-7-12,10-1125KV 日立SF-2403BSC28-082121-5,2-3-4-6-8,9-1028KV 日立CPT-1892BSC25-083331-5,3-4-6-8-9-1025KV 日立CMT2518BSC28-233821-2,3-5-6-8-9,4-1028KV 日立CPT-203BSC25-143991-2,3-4-6,5-8,11-1225KV 日立CPT-2059BSC25-194371-2-9,3-6-10,11-1225KV 日立C27SX1BSC29-235391-2,3-4-5-6-8-9-1029KV 日立C24CS1BSC27-236761-2,3-5-6-8-9-1027KV 日立C29ST1BSC29-235391-2,3-4-5-6-7-8-9-1030KV 爱美79A302-2BSC22-100301-7-9,2-5-6-10,3-4,11-1224KV 爱美DK9C3BSC24-100291-7-9-10,3-4,5-6,11-`1224KV 爱美DK9C2BSC24-100291-7-9-10,3-4,5-6,11-`1224KV 爱美K9121BSC24-100291-7-9-10,3-4,5-6,11-`1224KV爱美DK3C2BSC24-100291-7-9-10,3-4,5-6,11-`1224KV 爱美K9121BSC22-040261-2-3-4-5-6,8-9-1022KV 爱美79A307-1BSC22-040261-2-3-4-5-6,8-9-1025KV 爱美D9121BSC22-040261-2-3-4-5-6,8-9-1022KV 爱美79A307-2BSC22-040041-2-3-5-6,4-8-9-1022KV 爱美79A307-3BSC22-041611-2-3-5-6,4-8-9-1022KV 爱美79A302-5BSC22-041611-2-3-5-6,4-8-9-1022KV 爱美DK9C2-5K BSC22-041611-2-3-5-6,4-8-9-1022KV 爱美79A302-9BSC24-062981-2-3-6,4-5-10,8-924KV 爱美K9181BSC22-046791-2-3-4-5-6,8-9-1023KV 夏华XT-3701BSC22-040321-2-4-5-8,3-9-1022KV 夏华XT-3702A BSC22-040321-2-4-5-8,3-9-1022KV 夏华XT-3718BSC22-040321-2-4-5-8,3-9-1022KV 夏华KTB-3731BSC22-040321-2-4-5-8,3-9-1022KV 夏华XT-370A BSC22-040321-2-4-5-8,3-9-1022KV 夏华XT-3702BSC22-040321-2-4-5-8,3-9-1022KV 夏华XT-4201BSC22-040321-2-4-5-8,3-9-1022KV 夏华XT-5102BSC22-040321-2-4-5-8,3-9-1022KV 夏华XT-4701BSC22-041311-2-4-5-8,3-9-1024KV 夏华XT-4702BSC22-041311-2-4-5-8,3-9-1024KV 罗兰斯宝LS-4728BSC22-041311-2-4-5-8,3-9-1024KV 罗兰斯宝LS-4738R B SC22-041311-2-4-5-8,3-9-1024KV 罗兰斯宝LS-5128BSC22-041311-2-4-5-8,3-9-1024KV 罗兰斯宝LS-5138R B SC22-041311-2-4-5-8,3-9-1024KV 夏华XT-5125BSC22-041311-2-4-5-8,3-9-1024KV 夏华KT-5101BSC22-041311-2-4-5-8,3-9-1024KV 夏华XT-5102BSC22-041311-2-4-5-8,3-9-1024KV 夏华XT-5103BSC22-041311-2-4-5-8,3-9-1024KV 夏华XT-5124BSC22-041311-2-4-5-8,3-9-1024KV 夏华XT-5101BSC22-041311-2-4-5-8,3-9-1024KV 夏华XT-5140BSC22-041311-2-4-5-8,3-9-1024KV 百花MV-5186BSC22-041311-2-4-5-8,3-9-1024KV 美乐M2188BSC22-041311-2-4-5-8,3-9-1024KV 夏华XT-5670BSC22-041314-5-8,3-9-1024KV 夏华XT-5650BSC25-233521-2-3,4-6-7-9-1025KV 夏华XT-5601BSC25-233521-2-3,4-6-7-9-1025KV 夏华XT-5622BSC25-233521-2-3,4-6-7-9-1025KV 夏华XT-6698T BSC27-234611-2-3,4-6-7-9-1027KV 夏华XT-7103K BSC27-234611-2-3,4-6-7-9-1027KV 夏华XT-7102BSC27-234611-2-3,4-6-7-9-1027KV 夏华KT-5101I BSC25-255421-2-4-5-6-8,3-9-1025KV 夏华KT-5102I BSC25-255421-2-4-5-6-8,3-9-1025KV 夏华XT-5653BSC28-235511-2-3,4-6-7-9-1028KV 夏华XT-5103D BSC23-046821-2-4-5-8,3-9-1023KV 金凤TC2918BSC30-236441-2-3,4-5-6-7-9-1030KV 金凤TC2928BSC30-236441-2-3,4-5-6-7-9-1030KV 金凤TC2518BSC30-236441-2-3,4-5-6-7-9-1030KV德律风根TFK2006BSC20-140232月6日20KV德律风根TFK2016BSC20-140232月6日20KV德律风根TFL1400BSC20-140232月6日20KV德律风根TFL5000BSC23-140582月6日23KV德律风根TFL5016BSC23-140582月6日23KV德律风根TFL6016BSC23-140582月6日23KV德律风根GF6060X BSC23-140582月6日23KV德律风根2560BSC22-146112月6日22KVLZ174A100THLAT BSC24-235471-2-4-6,3-5-724KVTCF-7000TOTOKUTBSC24-235471-2-4-6,3-5-724KV MSUTFQA03BSC23-235491-2,5-619KVMSIFAK29BSC20-215651-2-3-4-5,9-1020 4275902500BSC20-215651-2-3-4-5,9-1020 TRNS-FB-3035A BSC21-195821-2-8,3-9,4-6-721 FEC003BSC21-195821-2-8,3-9,4-6-721 BSC-140224335BSC23-035901-2,3-9,4-5-6-823 11/ULZ6BSC23-035901-2,3-9,4-5-6-823 CMC1414AEL BSC23-215501-7-9,2-5-6-10,3-423 DCF-1580BSC23-215501-7-9,2-5-6-10,3-423 47F13-0120BSC23-015772-3-4-5,6-9-1023 MCFT-405BSC23-015772-3-4-5,6-9-1023 FEA237BSC19-235611-2-3-10,4-5-6-923 79A361-3BSC19-235611-2-3-10,4-5-6-923 TC-2131CH BSC25-042291-4-5-8,2-3-7-9-1025KVTC-2182H BSC25-042291-4-5-8,2-3-7-9-1025KVFS2189PDN BSC25-214521-2,3-4-5-625KVTC-2123CH BSC25-214521-2,3-4-5-625KVZ654-8B BSC25-214521-2,3-4-5-625KVZ654-8A BSC25-214521-2,3-4-5-625KVTC-5488PDH BSC25-235001-2-3,4-6-825KVTC-5460PDH BSC25-235281-2-3,4-6-825KVPJ60S BSC27-015811-2-3-4-5-8-9,6-1027KVCT-1823HD BSC24-041461-3-4,2-7-10,8-924KVCT-1832HB BSC24-041461-3-4,2-7-10,8-924KVCT-2030HD BSC24-041461-3-4,2-7-10,8-924KVCT-2032HD BSC24-041461-3-4,2-7-10,8-924KVCT-1415HD BSC24-063211-3-4,2-7-10,8-924KVCT-1811HD BSC26-012571-5-8,3-6-7-9,10-1126KVKV-G25T/RM-870BSC27-235931-2-3,4-5,6-8-927KV25T1/RM-870BSC27-235931-2-3,4-5,6-8-927KVT25MF1/RM-870BSC27-235931-2-3,4-5,6-8-927KVKV25MF1/RM-845PBSC27-236121-2-3,4-5,6-7-8-927KVKV25MN11/RM-845P B SC27-236121-2-3,4-5,6-7-8-927KVKV-25MF1/RM857BSC27-236121-2-3,4-5,6-7-8-927KVKV-25MF11/RM857BSC27-236121-2-3,4-5,6-7-8-927KVKV29MF1/RM-845PBSC27-236121-2-3,4-5,6-7-8-927KVKV29MH11/RM-845P B SC27-236121-2-3,4-5,6-7-8-927KVF29MF1/RM-845P BSC27-236121-2-3,4-5,6-7-8-927KV KV-F29MH11/RM-845BSC27-236121-2-3,4-5,6-7-8-927KV KV-29MH31/RM-845P BSC27-236121-2-3,4-5,6-7-8-927KV KV-621T1/RM870BSC27-036671-2-3,4-5,6-7-827KV KV-T21MF/RM870BSC27-036671-2-3,4-5,6-7-827KV KP-5020CH BSC29-011581月2日29KV KP-7220CH BSC29-011581月2日29KV KP-1572BSC29-011581月2日29KV Z247-6A BSC25-160841-2-4-5-8,3-6-1025KV TC-1802PDH BSC25-160841-2-4-5-8,3-6-1025KV 4710NC2-2BSC25-160841-2-4-5-8,3-6-1025KV CT-1802PDH BSC25-160841-2-4-5-8,3-6-1025KV CT-1803PDH BSC25-160841-2-4-5-8,3-6-1025KV CT-1803PD BSC25-160841-2-4-5-8,3-6-1025KV CT-1804PDH BSC25-160841-2-4-5-8,3-6-1025KV CT-1805PDH BSC25-160841-2-4-5-8,3-6-1025KV CT-1820P BSC25-160841-2-4-5-8,3-6-1025KV 4710NC2-2BSC25-160841-2-4-5-8,3-6-1025KV 4703DSX BSC25-160841-2-4-5-8,3-6-1025KV 4710NCR BSC25-160841-2-4-5-8,3-6-1025KV 4710PDSX BSC25-160841-2-4-5-8,3-6-1025KV CT-1802PDH BSC25-160841-2-4-5-8,3-6-1025KV 22AS BSC25-100692-7-8,4-5-6-1025KV CTV-2AS BSC25-100692-7-8,4-5-6-1025KV 14PS BSC22-211141-3-5-7,2-4-8-9-1022KV 14DS BSC22-211141-3-5-7,2-4-8-9-1022KV 14UP BSC22-211141-3-5-7,2-4-8-9-1022KV 14PS BSC22-211141-3-5-7,2-4-8-9-1022KV KV-14X BSC22-211141-3-5-7,2-4-8-9-1022KV 14DS BSC22-211141-3-5-7,2-4-8-9-1022KV 18PS BSC24-160101-3-5-7,2-4-6-8-924KV 18PS BSC24-160101-3-5-7,2-4-6-8-924KV KV-18X BSC24-160101-3-5-7,2-4-6-8-924KV KV-20X BSC24-160101-3-5-7,2-4-6-8-924KV 20PAS BSC24-160101-3-5-7,2-4-6-8-924KV 20PS BSC24-160101-3-5-7,2-4-6-8-924KV DC56-201A BSC24-070251-2-4,3-5-7-8-924KV EC-142T BSC22-0725A1-2-4,3-5-7-8-922KV HC-227D BSC26-063781-2-4,3-5-7-8-926KV HC-2214R BSC26-233891-2-3,4-5-6-8-1026KV BSC23-1804BSC27-054301-2-4,3-5-7-8-927KV HC-2104R-2BSC25-234791-2-3,4-5-6-8-1025KV CV-2118HP BSC25-234791-2-3,4-5-6-8-1025KV HC2808BR BSC29-235221-2-10,3-5-6-7-8-929KV HC-2108R BSC26-162921-2-3,4-5-6-8-1026KV HC-2140R BSC26-162921-2-3,4-5-6-8-1026KV HC-2500A BSC24-237401-2-3,4-5-6-8-1024KV22AX BSC25-100692-7-8,4-5-6-1025KV22DX BSC25-100692-7-8,4-5-6-1025KV20X BSC24-160101-3-5-7,2-4-6-8-924KV20PAS BSC24-160101-3-5-7,2-4-6-8-924KV20X BSC24-160101-3-5-7,2-4-6-8-924KV20PS BSC24-160101-3-5-7,2-4-6-8-924KV20PAS BSC24-160101-3-5-7,2-4-6-8-924KVDCS-2006ME BSC24-120451-4-6-7,2-3-5-8,10-1124KVC-2006PHN BSC24-120451-4-6-7,2-3-5-8,10-1124KVDCS-2050ME BSC24-120451-4-6-7,2-3-5-8,10-1124KVC-34P BSC24-120451-4-6-7,2-3-5-8,10-1124KVC4902BSC24-120451-4-6-7,2-3-5-8,10-1124KVC-2060PHB BSC24-120451-4-6-7,2-3-5-8,10-1124KVCPI2006BSC24-120451-4-6-7,2-3-5-8,10-1124KVDCS-2006ME BSC24-120451-4-6-7,2-3-5-8,10-1124KVDCS-2050ME BSC24-120451-4-6-7,2-3-5-8,10-1124KVC-34SP BSC24-120451-4-6-7,2-3-5-8,10-1124KVDCS-2006ME BSC24-120451-4-6-7,2-3-5-8,10-1124KVDCS-2050ME BSC24-120451-4-6-7,2-3-5-8,10-1124KVC-34SP BSC24-120451-4-6-7,2-3-5-8,10-1124KV</P><TD width=85 <TD width=117>BSC24<TD width=205>1-4-6-7,2-3-<TD width=45>24KV XC-528ZQ BSC24-120451-4-6-7,2-3-5-8,10-1124KVDCS-2006ME BSC24-120451-4-6-7,2-3-5-8,10-1124KV21LR BSC25-161841-6-7-9-10,2-3-4-525KVFA5133T BSC25-196012-7-8,4-5-6-10-11-1225KVCTO-93BSC25-170441-3,2-4-5-6,8-925KV20CTO6050/93Z BSC25-170441-3,2-4-5-6,8-925KV20CTO6050/93T BSC25-170441-3,2-4-5-6,8-925KV20CTO6050/93S BSC25-170441-3,2-4-5-6,8-925KV14CT2020/50S BSC22-172131-3-4-5-9,2-8,6-1022KV37612/V8944BSC23-173151-4,2-5,3-10,6-8,9-11,12-123KV18C-63666/96S BSC08-173571-2,3-4,5-6-7,8-9,10-11-128KVJVC AV-G29MX BSC24-277351-2-8,3-4-5-6-7-1024KV2123BSC26-033361-2-4,3-6-8-9-1026KV44C1BSC22-233801-2-3,4-5-6-822KV49C1BSC22-233801-2-3,4-5-6-822KV4C3701-1BSC21-102615-7-9,2-3,8-1021KV51-1A BSC25-082862-4-10-11,3-5-6-7-925KVC71J-1BSC29-233761-2-4,3-6-8-9-1029KVCC542BSC23-033941-2-3,4-5-6-7-923KVCD37-1A BSC21-102615-7-9,2-3,8-1021KVCD37-2BSC24-014341-2-3-5,4-7-8-9-1024KVCF93222 KFS-60676BSC26-043691-2-4-9,3-5-7-8-1026KV西湖7190HZ BSC21-201621-3-6,4-5,7-8-921KVJVC7190S/N BSC21-201621-3-6,4-5,7-8-921KVJVC7885JM BSC21-201621-3-6,4-5,7-8-921KV龙江7255TM BSC22-011192-11-12,3-4-7-9,5-6-8-1022KV成都7255D BSC22-011192-11-12,3-4-7-9,5-6-8-1022KV 天鹅7255JM BSC22-011192-11-12,3-4-7-9,5-6-8-1022KV JVC7245HC BSC22-011192-11-12,3-4-7-9,5-6-8-1022KV JVC7255JM BSC22-011192-11-12,3-4-7-9,5-6-8-1022KV JVC VM-14PSN(P)BSC22-132031-3,4-5,6-7-822KV 金凤C-37-4BSC22-201551-3,4-5,6-7-1022KV 金凤C-37-6BSC22-201551-3,4-5,6-7-1022KV 金凤C-37-6B BSC22-201551-3,4-5,6-7-1022KV 上海Z237-1BSC22-201551-3,4-5,6-7-1022KV 上海237-1A BSC22-201551-3,4-5,6-7-1022KV 北京836BSC22-201551-3,4-5,6-7-1022KV 龙江C37G-1BSC22-201551-3,4-5,6-7-1022KV 龙江Z237-1A BSC22-201551-3,4-5,6-7-1022KV 沈阳7185SY BSC22-201551-3,4-5,6-7-1022KV 沈阳7196SY BSC22-201551-3,4-5,6-7-1022KV 沈阳7195SY BSC22-201551-3,4-5,6-7-1022KV 天鹅CS37-V2A BSC22-201551-3,4-5,6-7-1022KV 海燕CS37-2BSC22-201551-3,4-5,6-7-1022KV 海燕7185XA BSC22-201551-3,4-5,6-7-1022KV 成都C37-844BSC22-201551-3,4-5,6-7-1022KV 三元37SYC-2BSC22-201551-3,4-5,6-7-1022KV 凯歌4C3702-1BSC22-201551-3,4-5,6-7-1022KV 如意SGC-3702BSC22-201551-3,4-5,6-7-1022KV 如意SGC-3702-1BSC22-201551-3,4-5,6-7-1022KV 如意SC-37A BSC22-201551-3,4-5,6-7-1022KV 春风14C-1BSC22-201551-3,4-5,6-7-1022KV 春风14C-2BSC22-201551-3,4-5,6-7-1022KV 春风37XC1(B)BSC22-201551-3,4-5,6-7-1022KV 襄阳37XC1(B)BSC22-201551-3,4-5,6-7-1022KV 百乐37CD3BSC22-201551-3,4-5,6-7-1022KV 天鹅CS37-V1BSC22-201551-3,4-5,6-7-1022KV 百花DC56BSC22-201551-3,4-5,6-7-1022KV 北京837BSC22-20155A1-3,4-5,6-7-1022KV 北京837-1BSC22-20155A1-3,4-5,6-7-1022KV 北京838BSC22-20155A1-3,4-5,6-7-1022KV 黄河HC37-2BSC22-20155A1-3,4-5,6-7-1022KV 长城JTC-371BSC22-20155A1-3,4-5,6-7-1022KV 长城JTC-371A BSC22-20155A1-3,4-5,6-7-1022KV 长城JTC-513-2BSC22-20155A1-3,4-5,6-7-1022KV 西湖37CD7BSC22-20155A1-3,4-5,6-7-1022KV 西湖37CD7A BSC22-20155A1-3,4-5,6-7-1022KV 海燕CSC-1535BSC22-20155A1-3,4-5,6-7-1022KV JVC7175J BSC22-20155A1-3,4-5,6-7-1022KV JVC7175JM BSC22-20155A1-3,4-5,6-7-1022KV JVC7185JM BSC22-20155A1-3,4-5,6-7-1022KV 星牌7175BSC22-20155A1-3,4-5,6-7-1022KV 日立投影2435071BSC26-236711-2,3-4-5-6-8-9-1027KV东芝C-218D6C BSC25-031891-2-3,4-6-7-9-1025KV 东芝C-219D5C BSC25-031891-2-3,4-6-7-9-1025KV 东芝C-219RC9BSC25-031891-2-3,4-6-7-9-1025KV 东芝289X6M BSC30-162421-2-3,4-6-7-9-1030KV 东芝C-2806XH BSC28-233841-2-3,4-5-6-7-9-1028KV 东芝C-2128KTV BSC25-033951-2-3,4-5-6-8-925KV 东芝C-2125BSC25-033951-2-3,4-5-6-8-925KV 孔雀KQ37-39BSC22-0974A(83P)1-7,5-6,8-9-1022KV 孔雀37-39-1BSC22-0974A(83P)1-7,5-6,8-9-1022KV 昆仑S373BSC22-0974A(83P)1-7,5-6,8-9-1022KV 昆仑S375BSC22-0974A(83P)1-7,5-6,8-9-1022KV 昆仑CTP3904BSC22-0974A(83P)1-7,5-6,8-9-1022KV 三洋CTP-3904BSC22-0974A(83P)1-7,5-6,8-9-1022KV 三洋CTP-3904M BSC22-0974A(83P)1-7,5-6,8-9-1022KV 三洋CTP-3905BSC22-0974A(83P)1-7,5-6,8-9-1022KV 三洋CTP-3905A BSC22-0974A(83P)1-7,5-6,8-9-1022KV 三洋CTP-3905-00BSC22-0974A(83P)1-7,5-6,8-9-1022KV 三洋CTP-3905H BSC22-0974A(83P)1-7,5-6,8-9-1022KV 乐华TC-482D BSC22-05136A1-6-9,2-4-522KV 乐华TC-484QD BSC22-05136A1-6-9,2-4-522KV 熊猫DB37C1BSC22-05136A1-6-9,2-4-522KV 熊猫DB37C2BSC22-05136A1-6-9,2-4-522KV 熊猫DB37C3BSC22-05136A1-6-9,2-4-522KV 昆仑S372BSC22-05136A1-6-9,2-4-522KV 美乐37CD340QD BSC22-05136A1-6-9,2-4-522KV 青岛37CD340QDX BSC22-05136A1-6-9,2-4-522KV 青岛37CD445QDX BSC22-05136A1-6-9,2-4-522KV 青岛TC-484QD BSC22-05136A1-6-9,2-4-522KV 松下TC-684D BSC22-05136A1-6-9,2-4-522KV 昆仑TC-684D BSC22-05136A1-6-9,2-4-522KV 泰山TS37C3BSC22-05136A1-6-9,2-4-522KV 美乐DS37C-1BSC22-05136A1-6-9,2-4-522KV 松下TC-25GF12G BSC31-235961-2-7,4-5-631KV 松下TC-33V32HN BSC27-236001-2,3-4-5,6-7-1027KV 松下TC-29VIR BSC29-236141-2,3-4-5,6-7-1029KV 松下TC-2140S BSC30-236351-2,4-5-7,6-8-929KV 松下TC-2150R BSC30-236351-2,4-5-7,6-8-929KV 松下TC-2150RS BSC30-236351-2,4-5-7,6-8-929KV 熊猫DB47C3-2BSC24-05136(M11)1-6-9,2-4-524KV 熊猫DB47C5-1BSC24-05136(M11)1-6-9,2-4-524KV 昆仑TC817D/T BSC24-05136(M11)1-6-9,2-4-524KV 泰山TS47C3BSC24-05136(M11)1-6-9,2-4-524KV 泰山TS47C4BSC24-05136(M11)1-6-9,2-4-524KV 泰山CS47C4BSC24-05136(M11)1-6-9,2-4-524KV 金凤C47S1BSC24-05136(M11)1-6-9,2-4-524KV 金凤C47S2A BSC24-05136(M11)1-6-9,2-4-524KV 长虹47CJ1BSC24-05136(M11)1-6-9,2-4-524KV长虹47CJ2BSC24-05136(M11)1-6-9,2-4-524KV 美乐47CB840G/A BSC24-05136(M11)1-6-9,2-4-524KV 美乐47DS47C-3A BSC24-05136(M11)1-6-9,2-4-524KV 青岛TC-818QD BSC24-05136(M11)1-6-9,2-4-524KV 青岛47CD840QD BSC24-05136(M11)1-6-9,2-4-524KV 青岛47CD400P BSC24-05136(M11)1-6-9,2-4-524KV 松下TC-810DH BSC24-05136(M11)1-6-9,2-4-524KV 松下TC-816BSC24-05136(M11)1-6-9,2-4-524KV 松下TC-817BSC24-05136(M11)1-6-9,2-4-524KV 西湖51CD5BSC24-0238A(L851)1-2-3-5,4-6-1022KV 宇航CJ51AV BSC24-0238A(L851)1-2-3-5,4-6-1022KV 韶峰SFC51-4BSC24-0238A(L851)1-2-3-5,4-6-1022KV 长城JTC513BSC24-0238A(L851)1-2-3-5,4-6-1022KV 黄河HC51-3BSC24-0238A(L851)1-2-3-5,4-6-1022KV 黄河HC51-5BSC24-0238A(L851)1-2-3-5,4-6-1022KV 长城JTC513B BSC24-0238A(L851)1-2-3-5,4-6-1022KV 上海Z247-5A BSC24-0238A(L851)1-2-3-5,4-6-1022KV 上海Z247-5B BSC24-0238A(L851)1-2-3-5,4-6-1022KV 北京8306BSC24-0238A(L851)1-2-3-5,4-6-1022KV 北京8306-3BSC24-0238A(L851)1-2-3-5,4-6-1022KV 长城JTC474-3BSC24-0238A(L851)1-2-3-5,4-6-1022KV 东芝C-1431ZT BSC22-010501-2-3,4-7-8-9-1022KV 东芝C-1631Z BSC22-010501-2-3,4-7-8-9-1022KV 东芝C-182D5C BSC24-030811-2-3-5,4-6-7-9-1024KV 东芝C-187D5C3BSC24-030811-2-3-5,4-6-7-9-1024KV 东芝C-202D5C BSC24-030811-2-3-5,4-6-7-9-1024KV 东芝C-202R5C BSC24-030811-2-3-5,4-6-7-9-1024KV 红岩SC-473BSC24-09074(83P)1-7,5-6,8-9-1024KV 黄山AH4724C-1BSC24-09074(83P)1-7,5-6,8-9-1024KV 日声RS88P BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5903H BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5903J BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5904P BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5904W BSC24-35J09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5904JH BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5904SZ BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5905M BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5905GS BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5905GS-00BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5906BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5906I BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5906J BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5920BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-59208BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5921GS BSC24-09074(83P)1-7,5-6,8-9-1024KV 华日C47J-3BSC24-02038(L851)1-2-3-5,4-6-1024KV 华日C47J-3A BSC24-02038(L851)1-2-3-5,4-6-1024KV华日C47J-3B BSC24-02038(L851)1-2-3-5,4-6-1024KV 华日C47J-3C BSC24-02038(L851)1-2-3-5,4-6-1024KV 星海46CJ2BSC24-02038(L851)1-2-3-5,4-6-1024KV 北京8306-3Y BSC24-02038(L851)1-2-3-5,4-6-1024KV 长风CFC47-2BSC24-02038(L851)1-2-3-5,4-6-1024KV 长风CFC47-3BSC24-02038(L851)1-2-3-5,4-6-1024KV 长风CFC47-5BSC24-02038(L851)1-2-3-5,4-6-1024KV 长风CFC47-5AR BSC24-02038(L851)1-2-3-5,4-6-1024KV 井冈山CJ47-1BSC24-02038(L851)1-2-3-5,4-6-1024KV 上海Z247-5C BSC24-02038(L851)1-2-3-5,4-6-1024KV 上海Z249-1A BSC24-02038(L851)1-2-3-5,4-6-1024KV 赣新KG-5186BSC24-02038(L851)1-2-3-5,4-6-1024KV 宇航NTC-50BSC24-02038(L851)1-2-3-5,4-6-1024KV 宇航游戏机DYJ51-L BSC24-02038(L851)1-2-3-5,4-6-1024KV 黄河HC51-1A BSC24-02038(L851)1-2-3-5,4-6-1024KV 三洋CTP-5928BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5928M BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5934BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5935J BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5938A BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5941BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5942BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-5946BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-59438BSC24-09074(83P)1-7,5-6,8-9-1024KV 孔雀KQ47-39-5BSC24-09074(83P)1-7,5-6,8-9-1024KV 孔雀KQ49-39-1BSC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-69500-00B SC24-09074(83P)1-7,5-6,8-9-1024KV 三洋CTP-69510-00B SC24-09074(83P)1-7,5-6,8-9-1024KV 黄山AH5161BSC24-09074(83P)1-7,5-6,8-9-1024KV JVC7695BSC25-131471-3,2-4-5,7-8-925KV 莺歌C47-1BSC25-131471-3,2-4-5,7-8-925KV 莺歌C47-2BSC25-131471-3,2-4-5,7-8-925KV 莺歌C47-3BSC25-131471-3,2-4-5,7-8-925KV 莺歌C47-4BSC25-131471-3,2-4-5,7-8-925KV 莺歌C47-7BSC25-131471-3,2-4-5,7-8-925KV 春风C47-1BSC25-131471-3,2-4-5,7-8-925KV 春风C51-1BSC25-131471-3,2-4-5,7-8-925KV 莺歌C51-1BSC25-131471-3,2-4-5,7-8-925KV 山茶C51-1BSC25-131471-3,2-4-5,7-8-925KV 飞天SC-C51D-CT BSC25-131471-3,2-4-5,7-8-925KV 飞天SC-C51D-HS-A B SC25-131471-3,2-4-5,7-8-925KV 菊花C513BSC25-131471-3,2-4-5,7-8-925KV 沈阳SDC51-4BSC25-131471-3,2-4-5,7-8-925KV 海燕CS47-2AV BSC25-131471-3,2-4-5,7-8-925KV 天鹅CS47-6BSC25-131471-3,2-4-5,7-8-925KV 天鹅7695VPNM BSC25-131471-3,2-4-5,7-8-925KV 龙江C47G-1BSC25-131471-3,2-4-5,7-8-925KV龙江7695VPJM BSC25-131471-3,2-4-5,7-8-925KV 沈阳SDC47-1C BSC25-131471-3,2-4-5,7-8-925KV 沈阳SDC47-2BSC25-131471-3,2-4-5,7-8-925KV 沈阳SDC47-4BSC25-131471-3,2-4-5,7-8-925KV 沈阳SDC47-10BSC25-131471-3,2-4-5,7-8-925KV 沈阳SDC47-10M BSC25-131471-3,2-4-5,7-8-925KV 沈阳7685SY BSC25-131471-3,2-4-5,7-8-925KV 沈阳7695PSY BSC25-131471-3,2-4-5,7-8-925KV 菊花C471A BSC25-131471-3,2-4-5,7-8-925KV 龙江7697VGSP BSC23-13147A1-3-9,2-4-5,7-823KV 龙江7698VPJM BSC23-13147A1-3-9,2-4-5,7-823KV 沈阳SDC47-4M BSC23-13147A1-3-9,2-4-5,7-823KV 如意SGC4703BSC23-13147A1-3-9,2-4-5,7-823KV 如意SGC4703D BSC23-13147A1-3-9,2-4-5,7-823KV 山茶SC-C47E BSC23-13147A1-3-9,2-4-5,7-823KV 春风C47-2B BSC23-13147A1-3-9,2-4-5,7-823KV 春风C47-3BSC23-13147A1-3-9,2-4-5,7-823KV 春风7697PCS BSC23-13147A1-3-9,2-4-5,7-823KV 春风7698VPGS BSC23-13147A1-3-9,2-4-5,7-823KV 北京839-2BSC23-13147A1-3-9,2-4-5,7-823KV JVC7697BSC23-13147A1-3-9,2-4-5,7-823KV JVC7669B BSC23-13147A1-3-9,2-4-5,7-823KV JVC8305BSC23-13147A1-3-9,2-4-5,7-823KV 海燕CS51E-5BSC23-13147A1-3-9,2-4-5,7-823KV 海燕CS51E-5AV BSC23-13147A1-3-9,2-4-5,7-823KV 海燕CS51E-6-R BSC23-13147A1-3-9,2-4-5,7-823KV 沈阳SDCY51-1BSC23-13147A1-3-9,2-4-5,7-823KV 沈阳SDCY51-2BSC23-13147A1-3-9,2-4-5,7-823KV 沈阳SDC54-1BSC23-13147A1-3-9,2-4-5,7-823KV 沈阳SDC54-2BSC23-13147A1-3-9,2-4-5,7-823KV 海燕SC47E-6A-R BSC23-13147A1-3-9,2-4-5,7-823KV 海燕CS47-2BSC24-13147D1-3,2-4-5,7-8-924KV 龙江C47G-2PS BSC24-13147E1-3-9,2-4-5,7-824KV 北京8305-2D1BSC24-13147E1-3-9,2-4-5,7-824KV 北京8305-2PS BSC24-13147E1-3-9,2-4-5,7-824KV 海燕CS47E-6-AV BSC24-13147E1-3-9,2-4-5,7-824KV 菊花C472BSC24-13147E1-3-9,2-4-5,7-824KV 上海Z656-2A BSC24-13147E1-3-9,2-4-5,7-824KV 上海Z656-3A BSC24-13147E1-3-9,2-4-5,7-824KV 北京8313BSC24-13147E1-3-9,2-4-5,7-824KV 长虹C2161BSC25-13147F1-2-6,3-4-7-8-925KV 长虹2163BSC25-13147F1-2-6,3-4-7-8-925KV 长虹CK53A BSC25-13147F1-2-6,3-4-7-8-925KV 长虹2162BSC25-13147F1-2-6,3-4-7-8-925KV 长虹CK53B2BSC25-13147F1-2-6,3-4-7-8-925KV 长虹CK56B2BSC25-13147F1-2-6,3-4-7-8-925KV 龙江7696VGSP BSC24-012002-10,3-6-8,4-5-7-924KV沈阳7696SY BSC24-012002-10,3-6-8,4-5-7-924KV 春风C47-2BSC24-012002-10,3-6-8,4-5-7-924KV JVC7696BSC24-012002-10,3-6-8,4-5-7-924KV 黄山AH5151C/R BSC24-09074(83P)1-7,5-6,8-9-1024KV 成都C51-851BSC24-09074(83P)1-7,5-6,8-9-1024KV 孔雀KQ51-39BSC24-09074(83P)1-7,5-6,8-9-1024KV 孔雀KQ51-39-1BSC24-09074(83P)1-7,5-6,8-9-1024KV 燕舞CSC1547BSC24-01113(X56P)1-2-3-5,4-7-8-9-1024KV 燕舞CSL-1547BSC24-01113(X56P)1-2-3-5,4-7-8-9-1024KV 华日C47J1BSC24-01113(X56P)1-2-3-5,4-7-8-9-1024KV 华日C47J-2BSC24-01113(X56P)1-2-3-5,4-7-8-9-1024KV 星海46CJ1BSC24-01113(X56P)1-2-3-5,4-7-8-9-1024KV 星海47CJ1BSC24-01113(X56P)1-2-3-5,4-7-8-9-1024KV 东芝C1831Z BSC24-01113(X56P)1-2-3-5,4-7-8-9-1024KV 东芝HC47-2BSC24-01113(X56P)1-2-3-5,4-7-8-9-1024KV 888ND-8601BSC24-01113(X56P)1-2-3-5,4-7-8-9-1024KV 西湖47CD4BSC24-01113(X56P)1-2-3-5,4-7-8-9-1024KV 长城JTC471-2A BSC24-01113(X56P)1-2-3-5,4-7-8-9-1024KV 长城JTC471-2BSC24-01113(X56P)1-2-3-5,4-7-8-9-1024KV 长城JTC471-2F BSC24-01113(X56P)1-2-3-5,4-7-8-9-1024KV 长城JTC471-Z BSC24-01113(X56P)1-2-3-5,4-7-8-9-1024KV 黄河HC47-1BSC24-01113(X56P)1-2-3-5,4-7-8-9-1024KV 黄河HC47-2BSC24-01113(X56P)1-2-3-5,4-7-8-9-1024KV 黄河HC47-4BSC24-01113(X56P)1-2-3-5,4-7-8-9-1024KV 上海Z251-2A BSC24-02038(L851)1-2-3-5,4-6-1024KV 长城JTC511BSC24-02038(L851)1-2-3-5,4-6-1024KV 赣新KG-5401BSC24-02038(L851)1-2-3-5,4-6-1024KV 井冈山CT53FS BSC24-02038(L851)1-2-3-5,4-6-1024KV 长城JTC474-3A BSC24-0238A(L851)1-2-3-5,4-6-1022KV 黄河HC37-3BSC24-0238A(L851)1-2-3-5,4-6-1022KV 华日C37J-3BSC24-0238A(L851)1-2-3-5,4-6-1022KV 华日C37J-3A BSC24-0238A(L851)1-2-3-5,4-6-1022KV 宇航KTC37J-1BSC24-0238A(L851)1-2-3-5,4-6-1022KV 宇航KTC37J-2BSC24-0238A(L851)1-2-3-5,4-6-1022KV 黄河HC47-5BSC24-0238A(L851)1-2-3-5,4-6-1022KV 黄河47-6BSC24-0238A(L851)1-2-3-5,4-6-1022KV 星海51CJ2BSC24-0238A(L851)1-2-3-5,4-6-1022KV 长风C51-3B BSC24-0238A(L851)1-2-3-5,4-6-1022KV </TBODY></TABLE><BSC24-0238A(L851)1-2-3-5,4-6-1022KV 三洋CTP-3905G BSC22-0974A(83P)1-7,5-6,8-9-1022KV 三洋CTP-3905Z BSC22-0974A(83P)1-7,5-6,8-9-1022KV 三洋CTP-3905GK BSC22-0974A(83P)1-7,5-6,8-9-1022KV 三洋CTP-390GS BSC22-0974A(83P)1-7,5-6,8-9-1022KV 三洋CTP-3933BSC22-0974A(83P)1-7,5-6,8-9-1022KV 三洋CTP-3934BSC22-0974A(83P)1-7,5-6,8-9-1022KV 三洋CTP-3964BSC22-0974A(83P)1-7,5-6,8-9-1022KV 三洋CTP-4903BSC22-0974A(83P)1-7,5-6,8-9-1022KV三洋CTP-4903JH BSC22-0974A(83P)1-7,5-6,8-9-1022KV 三洋CTP-4905BSC22-0974A(83P)1-7,5-6,8-9-1022KV 三洋CTP-4933BSC22-0974A(83P)1-7,5-6,8-9-1022KV 三洋CTP-4935BSC22-0974A(83P)1-7,5-6,8-9-1022KV 三洋CTP-4940BSC22-0974A(83P)1-7,5-6,8-9-1022KV 三洋CTP-4940-00BSC22-0974A(83P)1-7,5-6,8-9-1022KV 春笋CSD371BSC22-0974A(83P)1-7,5-6,8-9-1022KV 孔雀KQ51-39-3BSC24-09074(83P)1-7,5-6,8-9-1024KV 金鹊47DC1BSC24-09074(83P)1-7,5-6,8-9-1024KV 金鹊SC-851BSC24-09074(83P)1-7,5-6,8-9-1024KV 松下TC-819BSC24-05136(M11)1-6-9,2-4-524KV 松下TC-819BSC24-05136(M11)1-6-9,2-4-524KV 松下TC-866BSC24-05136(M11)1-6-9,2-4-524KV 松下TC-877BSC24-05136(M11)1-6-9,2-4-524KV 乐华TC-848KD BSC24-05136(M11)1-6-9,2-4-524KV 乐华TC-848KDH BSC24-05136(M11)1-6-9,2-4-524KV 乐华TC462-1ED BSC24-05136(M11)1-6-9,2-4-524KV 松下TC-201D BSC24-05136(M11)1-6-9,2-4-524KV 松下TC-216BSC24-05136(M11)1-6-9,2-4-524KV 松下TC-217BSC24-05136(M11)1-6-9,2-4-524KV 松下TC-218BSC24-05136(M11)1-6-9,2-4-524KV 松下TC-219BSC24-05136(M11)1-6-9,2-4-524KV 牡丹TC-818D BSC24-05136(M11)1-6-9,2-4-524KV 牡丹TC-47C3A BSC24-05136(M11)1-6-9,2-4-524KV 牡丹TC-47C3C BSC24-05136(M11)1-6-9,2-4-524KV 牡丹TC-47C3BSC24-05136(M11)1-6-9,2-4-524KV 牡丹TC-47C4BSC24-05136(M11)1-6-9,2-4-524KV 牡丹TC-47C5BSC24-05136(M11)1-6-9,2-4-524KV 牡丹TC-210D BSC24-05136(M11)1-6-9,2-4-524KV 牡丹TC-217P BSC24-05136(M11)1-6-9,2-4-524KV 牡丹TC-218BSC24-05136(M11)1-6-9,2-4-524KV 牡丹TC-218D BSC24-05136(M11)1-6-9,2-4-524KV 牡丹51C2BSC24-05136(M11)1-6-9,2-4-524KV 牡丹51C4BSC24-05136(M11)1-6-9,2-4-524KV 牡丹51C5BSC24-05136(M11)1-6-9,2-4-524KV 牡丹51C6BSC24-05136(M11)1-6-9,2-4-524KV 牡丹51C7BSC24-05136(M11)1-6-9,2-4-524KV 青岛51CD1BSC24-05136(M11)1-6-9,2-4-524KV 泰山TS51C6BSC24-05136(M11)1-6-9,2-4-524KV 乐华TC511KD BSC24-05136(M11)1-6-9,2-4-524KV 乐华TC511KDH BSC24-05136(M11)1-6-9,2-4-524KV 乐华219KD BSC24-05136(M11)1-6-9,2-4-524KV 金凤C51S BSC24-05136(M11)1-6-9,2-4-524KV 新星51C-2BSC24-05136(M11)1-6-9,2-4-524KV 长虹CJ46BSC24-05136(M11)1-6-9,2-4-524KV 松下TC-688BSC24-06046(M12)1-2-3-4,6-8-924KV 松下TC-688H BSC24-06046(M12)1-2-3-4,6-8-924KV。

EP1k30TC144引脚说明

(1)在列表中未出现的其他管脚为用户I/O管脚。

(2)该引脚是专用引脚,不能用作用户I/O管脚。

(3)如果该引脚不用做器件级信号或配置功能,则可用作用户I/O。

(4)配置后该引脚可以用作用户I/O。

(5)该引脚在用户模式时为三态。

(6)可选择的JTAG引脚TRST管脚在144个引脚的TQFP封装中并不使用。

(7)这个管脚驱动ClockLock和ClockBoost电路。

(8)这个管脚显示了ClockLock和ClockBoost电路的状态。

当ClockLock和ClockBoost电路锁定在输入时钟上或产生内部时钟时,LOCK为高电平;否则输出低电平。

该引脚是可选择的,当不使用该引脚时,该引脚可以用作用户I/O。

(9)该引脚是锁相环ClockLock和ClockBoost电路的电源和地。

为了保证一定的噪声阻抗,该电源和地应该和器件所使用的其他电源和地之间进行隔离。

如果不使用锁相环,该引脚应该连接到VCCINT或GNDINT。

(10)用户I/O引脚,包括专门的输入信号,专门的时钟引脚和所有的I/O引脚。

Altera Cyclone 系列FPGA从根本上针对低成本进行设计。

这些低成本器件具有专业应用特性,例如嵌入式存储器、外部存储器接口和时钟管理电路等。

Cyclone系列FPGA是成本敏感大批量应用的最佳方案。

如果需要进一步进行系统集成,可以考虑密度更高的Cyclone II FPGA和Cyclone III FPGA。

这些Cyclone新系列巩固了Altera在大批量、低成本应用方案中上的领先优势。

抢先一步,立即使用所有需要的工具——您现在就可以启动Cyclone FPGA设计。

Altera流行的Nios II 系列嵌入式处理器以及全套的知识产权(IP)组合都可以用于Cyclone FPGA开发。

现在,您还可以免费下载受到客户欢迎的Quartus II 网络版软件。

ASIC的低成本替代方案Cyclone FPGA是目前ASIC应用的低成本替代方案。

作为系统设计人员,您面临很多挑战,包括越来越大的成本压力和越来越复杂的设计,新出现的标准,以及越来越短的设计周期等。

ASIC 开发涉及到大量的工程资源,设计仿真和验证,需要进行多次重制。

利用其系统级集成功能,Cyclone FPGA系列避免了ASIC昂贵的NRE负担,降低了订购量和产品推迟带来的风险。

采用Cyclone FPGA系列,您的大批量应用现在可以采用价格相当的可编程解决方案(与ASIC相比)。

支持新市场和应用新的市场发展趋势,例如世界标准、平台融合、交互性以及技术改进等,不断推动了对高性价比方案的需求。

Cyclone系列FPGA的价格和功能满足了市场对创新的需求,通过产品迅速面市来确定领先优势。

消费类、通信、计算机外设、工业和汽车等低成本大批量应用市场都可以使用Cyclone FPGA。

Cyclone的性能特性Cyclone器件的性能足以和业界最快的FPGA进行竞争。

Cyclone FPGA综合考虑了逻辑、存储器、锁相环(PLL)和高级I/O接口,是价格敏感应用的最佳选择。