常用芯片管脚分布以及功能表

- 格式:docx

- 大小:1.38 MB

- 文档页数:11

LED显示屏常用器件的介绍1.IC的管脚功能IC芯片分别:74HC245、74HC595、74HC138、74HC04、4953。

各IC管脚功能如下:A: 74HC245功能是放大及缓冲。

20 和1接电源(+5V)19脚和10脚接电源地(GND)当电源是以上接时:输入脚分别为2、3、4、5、6、7、8、9。

输出脚分别为11、12、13、14、15、16、17、18注:2脚输入时,18脚输出。

其它脚以此类推。

B:74HC138功能是8选1译码器,输出为8行。

控制行数据。

第8脚GND,电源地。

第15脚VCC,电源正极第1-3脚A、B、C,输入脚。

第4-6脚选通输入端,(一般第5脚为EN )9-15脚和第7脚输出端。

C:74HC595功能是8位串入串、并出移位寄存器。

控制列数据。

16脚和10脚接电源(+5V),13脚和8脚接电源地(GND)。

列信号输出脚:1、2、3、4、5、6、7、15。

第一列输出脚为7脚,以此类推。

另第八列输出脚为15脚。

数据信号输入脚(Din)为14,数据信号输出脚(Din)为9。

锁存信号脚(L)为12脚,移位信号脚为11脚。

D:74HC04功能是六带缓冲反相器,控制使零信号(EN)。

15脚接电源(+5V),7脚电源地(GND)。

信号输入脚为:1、3、5、9、11、13。

信号输出脚为:2、4、6、8、10、12。

E:4953行管功能是开关作用,每个行管控制2行。

1脚和3脚接电源(+5V)。

信号输入脚:2、4。

信号输出脚:5、6、7、8。

5脚和6脚为一组输入,7脚和8脚、5脚和6脚为一组输出。

TB62726与5026 5024 16126 的作用:LED驱动芯片,16位移位锁存器。

第1脚GND,电源地。

第24脚VCC,电源正极第2脚DATA,串行数据输入第3脚CLK,时钟输入.第4脚STB,锁存输入.第23脚输出电流调整端,接电阻调整第22脚DOUT,串行数据输出第21脚EN,使能输入第5-12脚和13-20脚驱动输出端。

LED显示屏常用器件的介绍1.IC的管脚功能IC芯片分别:74HC245、74HC595、74HC138、74HC04、4953。

各IC管脚功能如下:A: 74HC245功能是放大及缓冲。

各引脚如图20 和1接电源(+5V)19脚和10脚接电源地(GND)当电源是以上接时:输入脚分别为2、3、4、5、6、7、8、9。

输出脚分别为11、12、13、14、15、16、17、18注:2脚输入时,18脚输出。

其它脚以此类推。

B:74HC138功能是8选1译码器,输出为8行。

控制行数据。

各引脚如图第8脚GND,电源地。

第15脚VCC,电源正极第1-3脚A、B、C,输入脚。

第4-6脚选通输入端,(一般第5脚为EN )9-15脚和第7脚输出端。

C:74HC595功能是8位串入串、并出移位寄存器。

控制列数据。

各引脚如图16脚和10脚接电源(+5V),13脚和8脚接电源地(GND)。

列信号输出脚:1、2、3、4、5、6、7、15。

第一列输出脚为7脚,以此类推。

另第八列输出脚为15脚。

数据信号输入脚(Din)为14,数据信号输出脚(Din)为9。

锁存信号脚(L)为12脚,移位信号脚为11脚。

D:74HC04功能是六带缓冲反相器,控制使零信号(EN)。

各引脚如下图15脚接电源(+5V),7脚电源地(GND)。

信号输入脚为:1、3、5、9、11、13。

信号输出脚为:2、4、6、8、10、12。

E:4953行管功能是开关作用,每个行管控制2行。

1脚和3脚接电源(+5V)。

信号输入脚:2、4。

信号输出脚:5、6、7、8。

5脚和6脚为一组输入,7脚和8脚、5脚和6脚为一组输出。

TB62726与5026 5024 16126的作用:LED驱动芯片,16位移位锁存器。

第1脚GND,电源地。

第24脚VCC,电源正极第2脚DATA,串行数据输入第3脚CLK,时钟输入.第4脚STB,锁存输入 .第23脚输出电流调整端,接电阻调整第22脚DOUT,串行数据输出第21脚EN,使能输入第5-12脚和13-20脚驱动输出端。

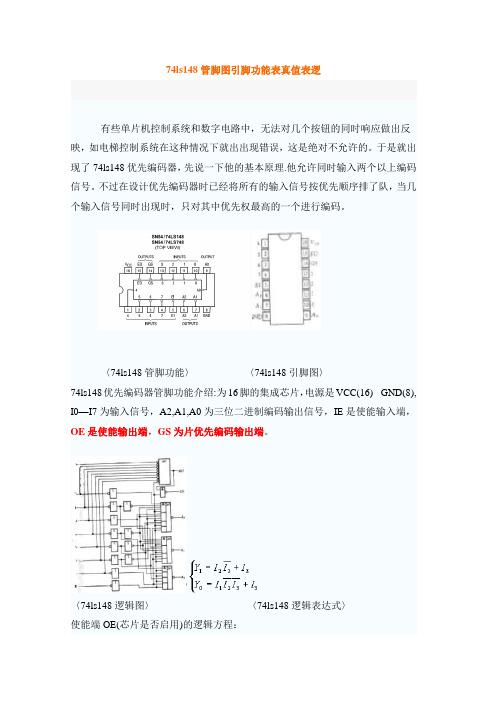

74ls148管脚图引脚功能表真值表逻

有些单片机控制系统和数字电路中,无法对几个按钮的同时响应做出反映,如电梯控制系统在这种情况下就出出现错误,这是绝对不允许的。

于是就出现了74ls148优先编码器,先说一下他的基本原理.他允许同时输入两个以上编码信号。

不过在设计优先编码器时已经将所有的输入信号按优先顺序排了队,当几个输入信号同时出现时,只对其中优先权最高的一个进行编码。

〈74ls148管脚功能〉〈74ls148引脚图〉

74ls148优先编码器管脚功能介绍:为16脚的集成芯片,电源是VCC(16) GND(8), I0—I7为输入信号,A2,A1,A0为三位二进制编码输出信号,IE是使能输入端,OE是使能输出端,GS为片优先编码输出端。

〈74ls148逻辑图〉〈74ls148逻辑表达式〉

使能端OE(芯片是否启用)的逻辑方程:

<74ls148真值表>

由74ls148真值表可列输出逻辑方程为:

A2 = (I4+I5+I6+I7)IE

A1 = (I2I4I5+I3I4I5+I6+7)·IE

A0 = (I1I2I4I6+I3I4I6+I5I6+I7)·IE

用两个74ls148优先编码器芯片扩展为十六线-四线优先编码器的电路连线图。

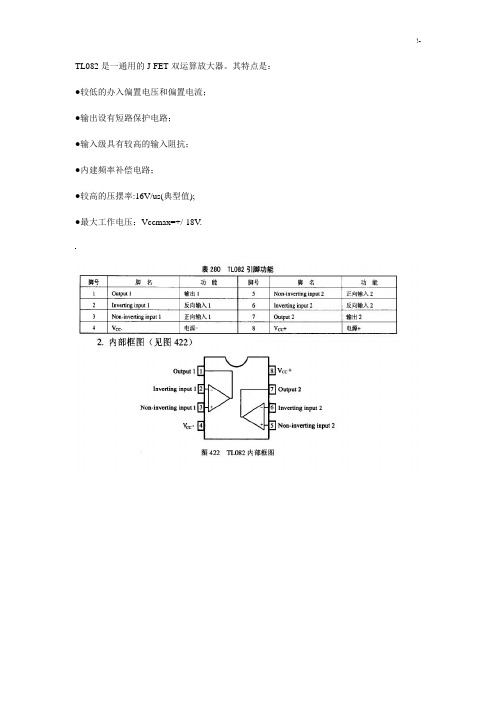

TL082是一通用的J-FET双运算放大器。

其特点是:●较低的办入偏置电压和偏置电流;●输出设有短路保护电路;●输入级具有较高的输入阻抗;●内建频率补偿电路;●较高的压摆率:16V/us(典型值);●最大工作电压:Vccmax=+/-18V.TL082典型应用电路LM324LM324引脚图简介:LM324系列器件为价格便宜的带有真差动输入的四运算放大器。

与单电源应用场合的标准运算放大器相比,它们有一些显著优点。

该四放大器可以工作在低到3.0伏或者高到32伏的电源下,静态电流为MC1741的静态电流的五分之一。

共模输入范围包括负电源,因而消除了在许多应用场合中采用外部偏置元件的必要性。

每一组运算放大器可用图1所示的符号来表示,它有5个引出脚,其中“+”、“-”为两个信号输入端,“V+”、“V-”为正、负电源端,“Vo”为输出端。

两个信号输入端中,Vi-(-)为反相输入端,表示运放输出端Vo的信号与该输入端的位相反;Vi+(+)为同相输入端,表示运放输出端Vo的信号与该输入端的相位相同。

LM324的引脚排列见图2。

参数描述:运放类型:低功率放大器数目:4 带宽:1.2MHz 针脚数:14 工作温度范围:0°C to +70°C 封装类型:SOIC 3dB带宽增益乘积:1.2MHz 变化斜率:0.5V/μs 器件标号:324 器件标记:LM324AD 增益带宽:1.2MHz 工作温度最低:0°C 工作温度最高:70°C 放大器类型:低功耗温度范围:商用电源电压最大:32V 电源电压最小:3V 芯片标号:324 表面安装器件:表面安装输入偏移电压最大:7mV 运放特点:高增益频率补偿运算逻辑功能号:324 额定电源电压, +:15V LM324的特点: 1.短路保护输出 2.真差动输入级 3.可单电源工作:3V-32V 4.低偏置电流:最大100nA 5.每封装含四个运算放大器。

74ls373引脚图管脚功能表74ls373是常用的地址锁存器芯片,它实质是一个是带三态缓冲输出的8D触发器,在单片机系统中为了扩展外部存储器,通常需要一块74ls373芯片,(1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态);(2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态.锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。

当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。

当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端C为高电平时,输出Q0~Q7 状态与输入端D1~D7状态相同;当C发生负的跳变时,输入端D0~D7 数据锁入Q0~Q7。

51单片机的ALE信号可以直接与74LS373的C连接。

74ls373与单片机接口:1D~8D为8个输入端。

1Q~8Q为8个输出端。

G是数据锁存控制端;当G=1时,锁存器输出端同输入端;当G由“1”变为“0”时,数据输入锁存器中。

OE为输出允许端;当OE=“0”时,三态门打开;当OE=“1”时,三态门关闭,输出呈高阻状态。

在MCS-51单片机系统中,常采用74LS373作为地址锁存器使用,其连接方法如上图所示。

其中输入端1D~8D接至单片机的P0口,输出端提供的是低8位地址,G端接至单片机的地址锁存允许信号ALE。

输出允许端OE接地,表示输出三态门一直打开。

<74LS00引脚图>74l s00 是常用的2输入四与非门集成电路,他的作用很简单顾名思义就是实现一个与非门。

Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输入四正与非门 74LS00│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GND74LS00真值表:A=1 B=1 Y=0A=0 B=1 Y=1A=1 B=0 Y=1A=0 B=0 Y=174HC138基本功能74LS138 为3 线-8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其74LS138工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

74LS138的作用:利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS138图74ls138译码器内部电路3线-8线译码器74LS138的功能表备注:这里的输入端的三个A0~1有的原理图中也用A B C表示(如74H138.pdf中所示,试用于普中科技的HC-6800 V2.2单片机开发板)。

<74ls138功能表>74LS138逻辑图无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。

如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出74ls138逻辑图由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

74ls161引脚图与管脚功能表资料

74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:

<74ls161引脚图>

管脚图介绍:

时钟CP和四个数据输入端P0~P3

清零/MR

使能CEP,CET

置数PE

数据输出端Q0~Q3

以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)

<74LS161功能表>

从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。

74LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

74LS11——3输入端3与门管脚图及逻辑功能表

74LS20——4输入端双与非门管脚图及逻辑功能表

74LS21——4输入端双与门管脚图及逻辑功能表

74LS27——3输入端三或非门管脚图及逻辑功能表

74LS42——BCD/十进制译码器管脚图及逻辑功能表

74LS138——3-8线译码器管脚图及逻辑功能表

74LS139——双2-4线译码器管脚图及逻辑功能表

74LS148——8-3线优先编码器管脚图及逻辑功能表

74LS151——八选一数据选择器管脚图及逻辑功能表

74LS153——双4选1数据选择器管脚图及逻辑功能表

74LS47——4线7段显示译码器,低电平有效,驱动共阳数码管

74LS55——双4输入与或非门

74LS54——4-2-3与或非门

74LS08——2

输入4与门。

系列芯片引脚图及逻辑

功能表

Document serial number【NL89WT-NY98YT-NC8CB-NNUUT-NUT108】

74LS11——3输入端3与门管脚图及逻辑功能表

74LS20——4输入端双与非门管脚图及逻辑功能表

74LS21——4输入端双与门管脚图及逻辑功能表

74LS27——3输入端三或非门管脚图及逻辑功能表

74LS42——BCD/十进制译码器管脚图及逻辑功能表74LS138——3-8线译码器管脚图及逻辑功能表

74LS139——双2-4线译码器管脚图及逻辑功能表

74LS148——8-3线优先编码器管脚图及逻辑功能表

74LS151——八选一数据选择器管脚图及逻辑功能表

74LS153——双4选1数据选择器管脚图及逻辑功能表

74LS47——4线7段显示译码器,低电平有效,驱动共阳数码管

74LS55——双4输入与或非门

74LS54——4-2-3与或非门

74LS08——2输入4与门。