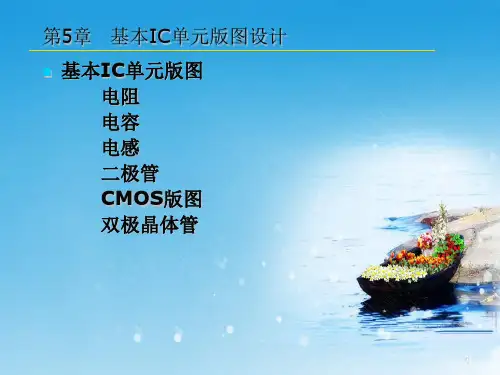

IC版图设计-第五章

- 格式:ppt

- 大小:1.68 MB

- 文档页数:34

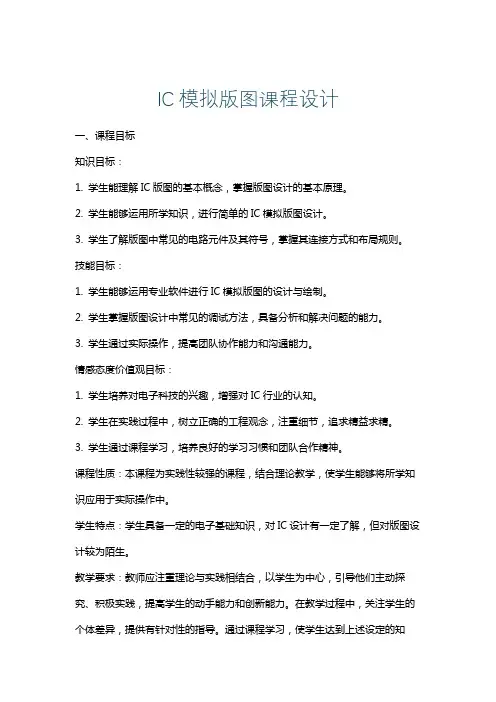

IC模拟版图课程设计一、课程目标知识目标:1. 学生能理解IC版图的基本概念,掌握版图设计的基本原理。

2. 学生能够运用所学知识,进行简单的IC模拟版图设计。

3. 学生了解版图中常见的电路元件及其符号,掌握其连接方式和布局规则。

技能目标:1. 学生能够运用专业软件进行IC模拟版图的设计与绘制。

2. 学生掌握版图设计中常见的调试方法,具备分析和解决问题的能力。

3. 学生通过实际操作,提高团队协作能力和沟通能力。

情感态度价值观目标:1. 学生培养对电子科技的兴趣,增强对IC行业的认知。

2. 学生在实践过程中,树立正确的工程观念,注重细节,追求精益求精。

3. 学生通过课程学习,培养良好的学习习惯和团队合作精神。

课程性质:本课程为实践性较强的课程,结合理论教学,使学生能够将所学知识应用于实际操作中。

学生特点:学生具备一定的电子基础知识,对IC设计有一定了解,但对版图设计较为陌生。

教学要求:教师应注重理论与实践相结合,以学生为中心,引导他们主动探究、积极实践,提高学生的动手能力和创新能力。

在教学过程中,关注学生的个体差异,提供有针对性的指导。

通过课程学习,使学生达到上述设定的知识、技能和情感态度价值观目标。

二、教学内容1. 版图设计基础理论:- 版图基本概念、版图设计流程及规范。

- 版图中常见的电路元件、符号及其连接方式。

- 版图布局规则及注意事项。

2. 版图设计实践操作:- 使用专业软件进行版图设计的基本操作。

- 简单IC模拟版图的设计与绘制。

- 版图设计中常见问题的调试与解决。

3. 教学案例分析:- 分析典型IC模拟版图案例,了解版图设计的实际应用。

- 学习优秀版图设计技巧,提高自身设计水平。

教学内容安排与进度:第一周:版图设计基础理论、软件操作介绍。

第二周:版图中常见电路元件及其连接方式、布局规则。

第三周:实际操作练习,进行简单IC模拟版图设计。

第四周:版图设计案例分析,总结经验,提高设计能力。

教材章节及内容:第一章:版图设计基础1.1 版图基本概念1.2 版图设计流程及规范1.3 版图中常见的电路元件及符号第二章:版图设计实践2.1 专业软件操作2.2 简单IC模拟版图设计2.3 版图调试与问题解决第三章:教学案例分析3.1 典型IC模拟版图案例3.2 优秀版图设计技巧教学内容确保科学性和系统性,结合实际教学需求,注重理论与实践相结合,使学生能够循序渐进地掌握版图设计相关知识。

目录目录 (1)第一章绪论 (1)1.1 版图设计 (1)1.1.1设计流程 (1)1.1.2设计步骤 (1)1.1.3 设计规则及验证 (1)1.2 标准单元版图设计 (2)1.2.1标准单元版图设计简介及历史 (2)1.2.2标准单元版图设计的意义 (2)第二章触发器介绍 (4)2.1 触发器简介 (4)2.2 主从D触发器的工作原理 (4)第三章0.35um工艺主从D触发器的设计 (6)3.1主从D触发器电路图的设计步骤及电路图 (6)3.1.1 设计步骤 (6)3.1.2 电路图 (6)3.2主从D触发器版图的设计步骤及电路图 (7)3.2.1 设计步骤 (7)3.2.2 版图 (7)3.3 DRC和LVS验证方法和结果 (8)第四章CMOS SRAM 单元介绍 (9)4.1 CMOS SRAM单元介绍 (9)4.1.1 CMOS SRAM单元原理 (9)4.1.2 CMOS SRAM单元的工作原理 (9)4.1.3 CMOS SRAM 单元的设计方法 (9)4.2 单个CMOS SRAM电路原理图 (10)第五章CMOS SRAM单元0.35um工艺版图设计 (12)5.1 单个CMOS SRAM 单元 (12)5.1.1单个CMOS SRAM 单元的设计步骤及电路图 (12)5.1.2 单个CMOS SRAM 单元的版图 (13)5.2 DRC和LVS验证方法和结果 (14)5.3 2位×8位CMOS SRAM阵列版图的设计步骤及DRC验证 (15)心得体会 (16)参考文献 (17)第一章绪论1.1 版图设计版图设计是一组相互套合的图形,各层版图相应不同的工艺步骤,每层版图用不同的图案来表示,版图与所制备的工艺密切相关。

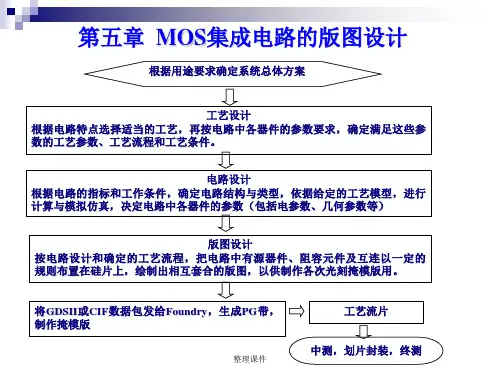

1.1.1设计流程版图设计是创建工程制图的精确的物理描述的过程,而这一物理描述遵守由制造工艺、设计流程以及仿真显示为可行的性能要求所带来的一系列约束。

1.1.2设计步骤具体设计步骤如下:系统设计,逻辑设计,电路图设计,版图设计,版图后仿真验证。

第5章CMOS 版图设计基础集成电路设计基础庄奕琪主讲2004.8~2004.12本章概要基本概念 CMOS 版图入门 设计规则 基本工艺层版图 FET 版图尺寸的确定 CMOS 版图设计方法 标准单元版图 设计层次化5.1 基本概念版图设计的定义设计目的Layout design:定义各工艺层图形的形状、尺寸以及不同工艺层的相对位置。

设计内容布局:安排各个晶体管、基本单元、复杂单元在芯片上的位置布线:设计走线,实现管间、门间、单元间的互连尺寸确定:确定晶体管尺寸(W、L)、互连尺寸(宽度)以及晶体管与互连之间的相对尺寸等5.1 基本概念版图设计的目标满足电路功能、性能指标、质量要求尽可能节省面积,以提高集成度,降低成本尽可能缩短连线,以减少复杂度,缩短延时、改善可靠性5.1 基本概念EDA工具的作用版图编辑规定各个工艺层上图形的形状、尺寸、位置(Layout Editor)规则检验版图与电路图一致性检验(LVS,Layout VersusSchematic)设计规则检验(DRC,Design Rule Checker)电气规则检验(ERC,Electrical Rule Checker)布局布线Place and route,自动给出版图布局与布线5.1 基本概念曼哈顿形状EDA工具允许画各种形状的图形,但大多数版图设计成为直角三角形的组合,称之为“曼哈顿几何形状”。

nWell pWell nSelectpSelect Metal2Via ActiveContactPoly Polycontact Metal15.2 CMOS 版图入门CMOS工艺层常用图形Magenta Metal2金属2Black Via 通孔Overglass覆盖玻璃2Glue Metal1金属1Black Polycontact 多晶接触Black Activecontact 有源区接触Green nSelect n 选择Green pSelect p 选择Red Poly 多晶Green Active 有源区Yellow nwell n 阱本书图形常用颜色符号名称N 阱双层金属化C MO S 工艺版次5.2 CMOS 版图入门CMOS掩膜版次5.2 CMOS版图入门2个nFET串联两个串联的nFET(有1个n+区被共享)5.2 CMOS版图入门3个nFET串联三个串联的nFET(有2个n+区被共享)技巧:能共用的区域一定要共用,共用n+或p+区优先于共用栅区5.2 CMOS版图入门2个nFET并联两个并联的nFET方案1:有1个n+区被共享,有源区面积较小,但互连线较长方案2:n+区全部被分开,有源区面积较大,但互连线较短原理图的画法最好与版图相对应5.2 CMOS版图入门非门(1)方案1输入、输出左右出5.2 CMOS 版图入门非门(2)方案2输入、输出上下出A A’np-substrate Field Oxide p +n +In Out GND V DD (a) Layout(b) Cross-Section along A-A’A A’5.2 CMOS 版图入门非门(3)方案3电源、地左右出5.2 CMOS版图入门非门相邻两个独立非门相邻共享电源、共享地5.2 CMOS版图入门非门串联两个非门串联共享电源、地、源、漏5.2 CMOS版图入门传输门带反相驱动器的传输门5.2 CMOS版图入门NAND22输入与非门5.2 CMOS版图入门NOR22输入或非门5.2 CMOS版图入门NOR3/NAND33输入与非门和或非门请观察AND与OR电路与版图的对称性5.3 设计规则基本概念 设计规则(DR,Design Rules)因IC制造水平对版图几何尺寸提出的限制要求 设计人员与工艺人员之间的接口版图设计必须无条件服从的准则设计规则的分类⎪⎪⎩⎪⎪⎨⎧离周边最短距离最短露头最小间距最小宽度绝对值)拓扑设计规则(⎪⎪⎩⎪⎪⎨⎧====λλλλλh d l t n s m w 离周边最短距离最短露头最小间距最小宽度相对值)设计规则(λ由IC 制造厂提供,与具体的工艺类型有关,m 、n 、l 、h 为比例因子,与图形类型有关。

第五章全定制IC设计(Calibre版图验证)在第三、四章已经介绍了电路图和版图的绘制(使用Cadence公司IC5141的Virtuoso Layout Editor),版图验证(使用Diva)和HSPICE后仿真(通过IC5141的ADE界面)。

目前,Calibre工具已经被众多设计公司、单元库、IP开发商和晶圆代工厂采用,作为深亚微米集成电路的物理验证工具,Calibre工具已经被集成到Cadence公司的Virtuoso Layout Editor 设计环境中。

本章将以十进制计数器为例(使用CSM 0.35um CMOS工艺),介绍Calibre验证工具的使用方法,并介绍XP平台下的HSPICE版图后仿真方法。

5.1 十进制计数器DRC(CSM 0.35um CMOS工艺)计数器是数字系统中应用最广泛的基本时序逻辑构件,本章以十进制计数为例,介绍Calibre验证工具的使用方法。

根据十进制计数器的构成原理,十进制计数器可由与非门,异或门和D触发器来表示一位十进制数的四位二进制编码。

分析步骤一般是:根据十进制加法计数器状态表画出卡诺图。

(1)由卡诺图得到表示该计数器工作状态的状态方程。

(2)由状态方程得到计数器的状态转换表(3)判断计数器的功能。

在前面的章节中已经学习了电路图与版图的绘制,在进行十进制计数器电路图的绘制时,首先绘制底层电路包括反相器,与非门,异或门及传输门等的Schematic, Symbol。

然后,调用单元电路画出十进制计数器的电路图。

绘制电路版图时,应先绘制底层电路对应的版图,并用Calibre进行相应的DRC,LVS,再画出整个电路版图。

十进制计数器的设计方法与逻辑电路图与电路图的绘制可参照第六章的实验七,版图绘制方法可参见第四章的4.1节。

版图绘制好后,为了保证版图能正确制出,在正式流片之前还必须作一些其他的工作,例如Design Rule Checking (DRC)。