DDS电路设计

- 格式:doc

- 大小:708.50 KB

- 文档页数:14

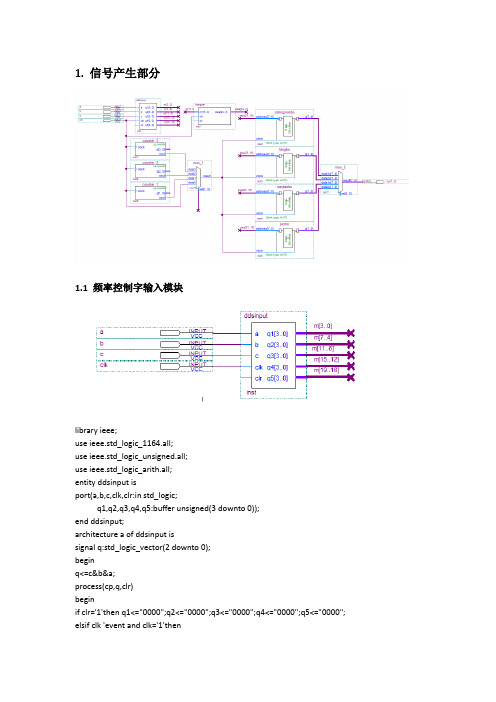

1. 信号产生部分1.1 频率控制字输入模块library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity ddsinput isport(a,b,c,clk,clr:in std_logic;q1,q2,q3,q4,q5:buffer unsigned(3 downto 0));end ddsinput;architecture a of ddsinput issignal q:std_logic_vector(2 downto 0);beginq<=c&b&a;process(cp,q,clr)beginif clr='1'then q1<="0000";q2<="0000";q3<="0000";q4<="0000";q5<="0000"; elsif clk 'event and clk='1'thenDDS信号信号发生器电路设计case q iswhen"001"=>q1<=q1+1;when"010"=>q2<=q2+1;when"011"=>q3<=q3+1;when"100"=>q4<=q4+1;when"101"=>q5<=q5+1;when others=>NULL;end case;end if;end process;end a;1.2 相位累加器模块library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity xiangwei isport(m:in std_logic_vector(19 downto 0);clk,clr:in std_logic;data:out std_logic_vector(23 downto 0)); end xiangwei;architecture a of xiangwei issignal q:std_logic_vector(23 downto 0);beginprocess(clr,clk,m,q)beginif clr='1'then q<="000000000000000000000000"; elsif (clk'event and clk='1')thenq<=q+m;end if;data<=q;end process;end a;向学壮2013083540202. ROM数据存储器3. 数码管显示部分3.1 七段数码管显示模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL ;ENTITY led7seg_1 ISPORT ( A : IN STD_LOGIC_VECTOR(1 DOWNTO 0);LED7S : OUT STD_LOGIC_VECTOR(12 DOWNTO 0) ) ; END ;DDS信号信号发生器电路设计ARCHITECTURE one OF led7seg_1 ISBEGINPROCESS( A )BEGINCASE A ISWHEN "00" => LED7S <= "0000000011111";WHEN "01" => LED7S <= "0100100011111";WHEN "10" => LED7S <= "1111001011111";WHEN "11" => LED7S <= "0010010011111";WHEN OTHERS => NULL ;END CASE ;END PROCESS ;END ;4. 总电路图a,b,c是改变波形频率key_1选择波形,有锯齿波、三角波、方波、正弦波。

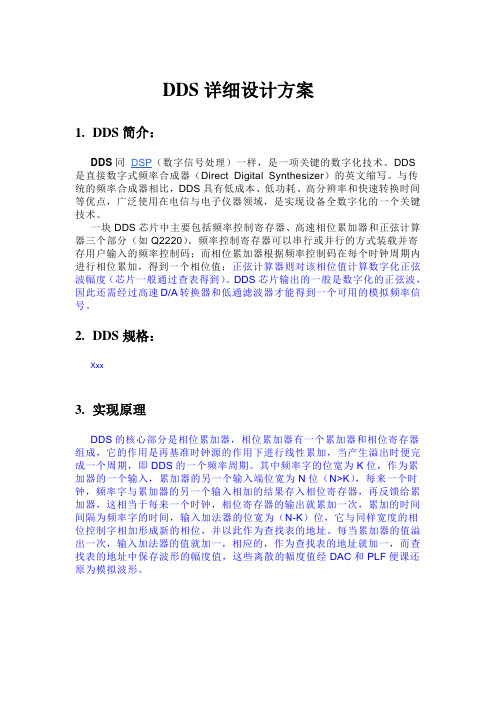

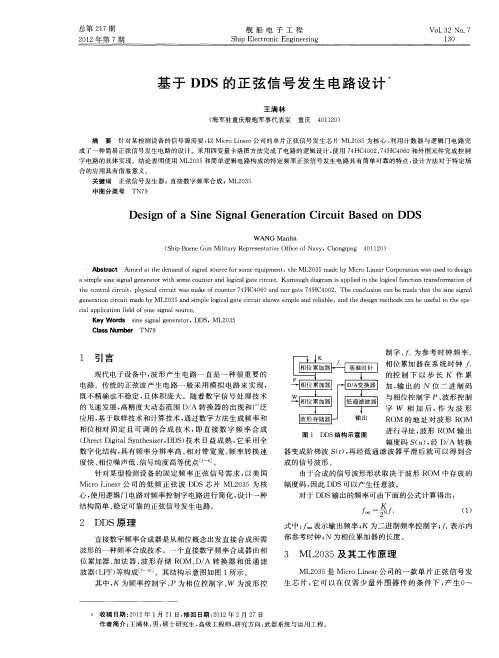

DDS详细设计方案1.DDS简介:DDS同DSP(数字信号处理)一样,是一项关键的数字化技术。

DDS 是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。

与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。

一块DDS芯片中主要包括频率控制寄存器、高速相位累加器和正弦计算器三个部分(如Q2220)。

频率控制寄存器可以串行或并行的方式装载并寄存用户输入的频率控制码;而相位累加器根据频率控制码在每个时钟周期内进行相位累加,得到一个相位值;正弦计算器则对该相位值计算数字化正弦波幅度(芯片一般通过查表得到)。

DDS芯片输出的一般是数字化的正弦波,因此还需经过高速D/A转换器和低通滤波器才能得到一个可用的模拟频率信号。

2.DDS规格:Xxx3.实现原理DDS的核心部分是相位累加器,相位累加器有一个累加器和相位寄存器组成,它的作用是再基准时钟源的作用下进行线性累加,当产生溢出时便完成一个周期,即DDS的一个频率周期。

其中频率字的位宽为K位,作为累加器的一个输入,累加器的另一个输入端位宽为N位(N>K),每来一个时钟,频率字与累加器的另一个输入相加的结果存入相位寄存器,再反馈给累加器,这相当于每来一个时钟,相位寄存器的输出就累加一次,累加的时间间隔为频率字的时间,输入加法器的位宽为(N-K)位,它与同样宽度的相位控制字相加形成新的相位,并以此作为查找表的地址。

每当累加器的值溢出一次,输入加法器的值就加一,相应的,作为查找表的地址就加一,而查找表的地址中保存波形的幅度值,这些离散的幅度值经DAC和PLF便课还原为模拟波形。

4.Verilog HDL源代码Verilog HDL代码为:module DDS (//inputsys_clk,sys_rst_n,fword,pword,//outputda_clk,da_data);//input portsinput sys_clk ; //system clock;input sys_rst_n ; //system reset, low is active; input [WIDTH1-1:0] fword ; //输入频率字input [WIDTH2-1:0] pword ; //输入相位字//output portsoutput [SIZE-1:0] da_data ; //DA 数据output da_clk ; //DA 时钟//reg definereg [WIDTH1-1:0] fword_r ;reg [WIDTH2-1:0] pword_r ;reg [WIDTH1-1:0] freq_count ;reg [WIDTH2-1:0] rom_addr ;//wire define//parameter defineparameter WIDTH1 = 32;parameter WIDTH2 = 12;parameter SIZE = 10;/******************************************************************** ************************************* Main Program*********************************************************************** ***********************************/assign da_clk = sys_clk ;always @(posedge sys_clk or negedge sys_rst_n) beginif (sys_rst_n ==1'b0) beginfword_r <= 32'h0000;endelsefword_r <= fword;endalways @(posedge sys_clk or negedge sys_rst_n) beginif (sys_rst_n ==1'b0) beginpword_r <= 12'h0000;endelsepword_r <= pword;endalways @(posedge sys_clk or negedge sys_rst_n) beginif (sys_rst_n ==1'b0) beginfreq_count <= 32'h0000;endelsefreq_count <= freq_count + fword_r; //频率控制器endalways @(posedge sys_clk or negedge sys_rst_n) beginif (sys_rst_n ==1'b0) beginrom_addr <= 32'h0000;endelserom_addr <= freq_count[31:20] + pword_r; //相位控制器endROM DDS_ROM_U0 (.address (rom_addr) ,.clock (sys_clk) ,.q (da_data));endmodule//end of RTL code5.日积月累Xxx6.综合出的电路DDS代码综合出的电路如下:注意:波形文件存在Project\DDS\wave_file下面。

基于dds技术的模拟频率调制电路设计及fpga实现DDS技术是一种数字信号处理技术,它可以实现高精度、高速度的频率合成和调制。

基于DDS技术的模拟频率调制电路设计及FPGA实现,可以实现高精度、高速度的模拟信号调制,具有广泛的应用前景。

一、基于DDS技术的模拟频率调制电路设计1. DDS技术原理DDS技术是一种数字信号处理技术,它通过数字信号处理器(DSP)或FPGA实现对数字信号的频率合成和调制。

DDS技术的核心是相位累加器和数字控制振荡器(NCO),相位累加器用于累加相位,NCO 用于产生数字信号。

DDS技术的优点是可以实现高精度、高速度的频率合成和调制,同时可以实现频率和相位的任意调制。

2. 模拟频率调制电路设计基于DDS技术的模拟频率调制电路设计,需要实现以下几个模块:(1)数字控制振荡器(NCO)模块:用于产生数字信号,可以通过改变NCO的频率和相位实现数字信号的频率和相位调制。

(2)数字信号处理器(DSP)模块:用于对输入信号进行数字信号处理,包括滤波、采样、量化等。

(3)模拟信号输出模块:用于将数字信号转换为模拟信号输出。

3. 模拟频率调制电路设计流程(1)确定调制信号的频率范围和精度要求。

(2)设计数字控制振荡器(NCO)模块,确定NCO的频率和相位控制方式。

(3)设计数字信号处理器(DSP)模块,包括滤波、采样、量化等。

(4)设计模拟信号输出模块,将数字信号转换为模拟信号输出。

(5)进行电路仿真和调试,优化电路性能。

二、基于DDS技术的模拟频率调制电路FPGA实现1. FPGA技术原理FPGA是一种可编程逻辑器件,可以实现数字电路的设计和实现。

FPGA的核心是可编程逻辑单元(PLU)和可编程互连网络(PCN),PLU用于实现逻辑功能,PCN用于实现逻辑单元之间的连接。

2. 模拟频率调制电路FPGA实现基于DDS技术的模拟频率调制电路FPGA实现,需要实现以下几个模块:(1)数字控制振荡器(NCO)模块:用于产生数字信号,可以通过FPGA实现NCO的频率和相位控制。

---------------------------------------------------------------范文最新推荐------------------------------------------------------ 基于DSP的DDS信号发生器硬件设计+电路图摘要在21世纪的今天,基于DSP的信号发生器以其编程的高度灵活性,波形的高精度与高稳定性等特点而脱颖而出,具有极大的应用价值和广泛的应用前景。

本文利用高性能DSP芯片加上合理的外围控制电路构成基于DSP的DDS信号发生器,完成电压监测电路的硬件设计工作。

通过对DDS的相应介绍采用查表法实现正弦波的产生,采用高速微处理器实现DDS。

然后完成硬件芯片的选型(TMS320LF2407)和硬件电路的设计工作。

硬件设计主要有核心控制模块电路、片选电路、串行通信电路、AD转换电路及信号采集电路,以此实现硬件电路完成接收上位机的控制信号,采集外部电压信号处理后送给上位机,实现对电压的监控。

关键词:信号发生器,DDS,电压监控,硬件设计11870毕业设计说明书(论文)外文摘要1 / 10TitleDDS signal generator hardware design based on DSPAbstractIn the 21st century,the DSP signal generator stand out for its high degree of flexibility of the programming waveforms, high precision and high stability characteristics, shows great value and broad application prospects.This article takes use of high performance DSP chip with peripheral control circuit DSP-based DDS signal generator,complete the hardware design of the voltage monitoring circuit.Achieve the generation of sine wave with look-up table method corresponding introduction of DDS.Then complete selection of hardware chip(TMS320LF2407)and hardware design.The hardware design mainly consists of core control module circuit, chip select circuit, the serial communication circuit, AD converter circuit and the signal acquisition circuit,In order to achieve the hardware circuit to complete the PC to receive the control signal.The acquisition of an external---------------------------------------------------------------范文最新推荐------------------------------------------------------voltage signal processing to give the host computer,in order to monitoring the voltage.Key words: signal generator,DDS,voltage monitoring,hardware design4.4 PC机与DSP的点对点的串行通信接口244.5 输入输出接口254.5.1A/D的接口254.5.2电压信号采样电路265电路设计中注意的问题28致谢30参考文献313 / 10附录硬件电路原理图321 绪论1.1 信号发生器简介信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广泛的应用。

AD9854想必大家都在为AD9854没有电路图,没有资料而头疼吧。

我这里有一份AD9854ASQ的资料,里面有可以用的程序原理图PCB 码原希望对大家有帮助。

现在把我的设计法出来供大家使用参考。

原理图和PCB图为AD9854外围电路!以下是AD9854的控制程序!//#include <reg51f.h>#include "sst89x5xxrd2.h"#include <intrins.h>#define USE_KEY 0#define uchar unsigned char#define uint unsigned int#define schar signed char#define sint signed int#define ulong unsigned long int//须主程序定义的参数/sbit ADDR0 =P2^0; //sbit ADDR1 =P2^1; //sbit ADDR2 =P2^2; //sbit ADDR3 =P2^3; //sbit ADDR4 =P2^4; //sbit ADDR5 =P2^5; ///sbit AD_FUD =P3^7; //UP_DATA sbit RUN =P3^2;sbit WR_LOW =P3^5; // WRsbit MASTER_RESET=P3^3;bit bdata F_Flag,OneSec_Flag,Re_Flag,P_Flag;//uchar SecOne;uchar Time_count;uchar AD_Addr;uchar dats;uchar TAB_Data[40];////初始化串口。

配置定时器// voidinitial_system(){EA = 0;TMOD=0x21; //初始化定时器0PCON=0x00;SCON=0x50;TH0 = 0xdc; //10毫秒定时, 采用晶体11.0592 定时器0,方式1 TL0 = 0x00;TH1 = 0xfd; //波特率9600 采用晶体11.0592 定时器1,方式1 TL1 = 0xfd;TR0 =1; //开启定时器0TR1 =1; //开启定时器0ET0 =1; //时钟0ES =0; //开串口中断EA = 1 ; // 使能所有中断}void Timer0() interrupt 1 using 3{TH0 = 0xdc; //10毫秒采用晶体11.0592 定时器0,方式1TL0 = 0x00;SecOne++;if(SecOne>200) //计时1秒钟{SecOne=0x00;OneSec_Flag=1;RUN=~RUN;}}//void AD9854_delay(int time){int i;for(i = 0; i < time; i++){_nop_();_nop_();_nop_();_nop_();}}void TAB_DataWord(){TAB_Data[0]=0x00; //00H Phase Adjust Register #1 <13:8> (Bits 15, 14 don't care) Phase #1 相位为0TAB_Data[1]=0x00; //01H Phase Adjust Register #1 <7:0> 01HTAB_Data[2]=0x00; //02H Phase Adjust Register #2 <13:8> (Bits 15, 14 don't care) Phase #2 相位为0TAB_Data[3]=0x00; //03H Phase Adjust Register #1 <7:0> 03H//100MTAB_Data[4]=0X31; //Frequency Tuning Word 1 <47:40>//623795E0184ATAB_Data[5]=0X1B; //Frequency Tuning Word 1 <39:32>TAB_Data[6]=0xE6; //Frequency Tuning Word 1 <31:24>TAB_Data[7]=0xE6; //Frequency Tuning Word 1 <23:16>TAB_Data[8]=0x53; //Frequency Tuning Word 1 <15:8>TAB_Data[9]=0x86; //Frequency Tuning Word 1 <7:0>//FTW2TAB_Data[10]=0x31; //Frequency Tuning Word 2 <47:40TAB_Data[11]=0x1B; //Frequency Tuning Word 2 <39:32>TAB_Data[12]=0xE6; //Frequency Tuning Word 2 <31:24>TAB_Data[13]=0xE6; //Frequency Tuning Word 2 <23:16>TAB_Data[14]=0x53; //Frequency Tuning Word 2 <15:8>TAB_Data[15]=0x86; //Frequency Tuning Word 2 <7:0> //500KHZ//FTWTAB_Data[16]=0x01; //Delta Frequency Word <47:40>TAB_Data[17]=0x47; //Delta Frequency Word <39:32>TAB_Data[18]=0xAE; //Delta Frequency Word <31:24>TAB_Data[19]=0x14; //Delta Frequency Word <23:16>TAB_Data[20]=0x7A; //Delta Frequency Word <15:8>TAB_Data[21]=0xE1; //Delta Frequency Word <7:0> 三角波 //频率为0//UpclokTAB_Data[22]=0x00; //Update Clock <31:24>TAB_Data[23]=0x00; //Update Clock <23:16>TAB_Data[24]=0x00; //Update Clock <15:8>TAB_Data[25]=0xF0; //Update Clock <7:0> //系统出现寄存器更新信号reg. Int UpdateClk.=0;外部更新TAB_Data[26]=0x00; //Ramp Rate Clock <19:16> (Bits 23, 22, 21, 20 don't care)TAB_Data[27]=0x00; //Ramp Rate Clock <15:8>TAB_Data[28]=0x00; //Ramp Rate Clock <7:0>TAB_Data[29]=0x10; //Don't Care(0),Don't Care(0),Don't Care(0),Comp PD(1),Reserved_Always Low(0),QDAC PD(0),DAC PD(0),DIG PD(0).TAB_Data[30]=0x20; //Don't Care(0),PLL Range(1),Bypass PLL(1),Ref Mult 4(0),RefMult 3(0),Ref Mult 2(0),Ref Mult 1(0),Ref Mult 0(0).TAB_Data[31]=0x10; //CLR ACC1(0),CLR ACC2(0),Triangle(0)(三角波),SRC QDAC(0),Mode2(0),Mode 1(0),Mode 0(0),Int Update Clk(0). 注意TAB_Data[32]=0x50; //Don't Care(0),Bypass_Inv_Sinc(0),OSK EN(0),OSK INT(0),Don't Care(0),Don't Care(0),LSB First(0),SDO_Active(0).TAB_Data[33]=0x00; //Output Shape Key I Mult <11:8> (Bits 15, 14, 13, 12 don't care)TAB_Data[34]=0x0F; //Output Shape Key I Mult <7:0>TAB_Data[35]=0x00; //Output Shape Key Q Mult <11:8> (Bits 15, 14, 13, 12 don't care)TAB_Data[36]=0x0F; //Output Shape Key Q Mult <7:0>TAB_Data[37]=0xFF; //Output Shape Key Ramp Rate <7:0>TAB_Data[38]=0x00; //QDAC <11:8> (Bits 15, 14, 13, 12 don't care)TAB_Data[39]=0x0F; //QDAC <7:0> (Data is required to be in twos complement format) }void AD9854_ParallelSendByte(uchar addr,uchar data1){// WR_LOW=0; //lhyaddr WR_LOW=WRB_nop_();P2=addr&0x3F;_nop_();P1=data1;WR_LOW=0; //lhyaddr WR_LOW=WRB_nop_();WR_LOW=1;_nop_();_nop_();WR_LOW=0; //lhyaddr WR_LOW=WRB}data0=*(SWord+i);AD9854_ParallelSendByte(Special_addr,data0); AD9854_delay(5);}}void Init9854(void){WR_LOW=0;AD_FUD=0;MASTER_RESET=0;}//void main(void){ uchar i;MASTER_RESET=0;initial_system(); //系统初始化Init9854();TAB_DataWord();MASTER_RESET=0;_nop_();_nop_();_nop_();_nop_();MASTER_RESET=1;AD9854_delay(30);_nop_();_nop_();_nop_();_nop_();_nop_();MASTER_RESET=0;_nop_();_nop_();_nop_();_nop_();_nop_();_nop_();_nop_();_nop_();_nop_();_nop_();AD9854_delay(500);AD9854_delay(500);AD9854_delay(500);for (i=0;i<40;i++){dats=TAB_Data[i];AD_Addr=i;AD9854_ParallelSendByte(AD_Addr,dats); }_nop_();AD_FUD=0;_nop_();_nop_();_nop_();AD_FUD=1;AD9854_delay(80);_nop_();_nop_();AD_FUD=0;while(1){if(OneSec_Flag==1){_nop_();_nop_();_nop_();AD9854_delay(80);_nop_();_nop_();_nop_();AD9854_delay(80);_nop_();for (i=0;i<40;i++){dats=TAB_Data[i];AD_Addr=i;AD9854_ParallelSendByte(AD_Addr,dats); }_nop_();AD_FUD=0;_nop_();_nop_();AD9854_delay(80);AD_FUD=1;_nop_();AD9854_delay(80); _nop_();_nop_();AD_FUD=0;OneSec_Flag=0; }_nop_();_nop_();}}。

0.2Hz-300MHz时钟发生器设计岳增祥:201122070441朱典全:201121070442况逸群:201121070507肖新川:201121250109吴龙辉:201121070421一.设计要求频率分辨率:0.1Hz频率范围:0.2Hz—300MHz输出电平:CMOS和ECL电平二.设计方案在本设计中,我们选用STM32F103VCT 6作为主控芯片来控制DDS的步进频率和其他外设;AD9912作为DDS芯片,以此产生300MHz高精度方波信号;由于DDS芯片的比较器输出方波信号为HSTL信号,为了兼容COMS和ECL 电平输出,使用了MAX系列电平转换芯片来进行电平转换,以实现COMS和ECL电平的输出;为了保证电源的可靠性,采用了LM7805来提供5V电源,采用TI公司的高精度、低压差的线型稳压电源TPS78233和TPS78218来产生器件所需的3.3V和1.8V的电压;为了方便调试和增加实用性,我们采用键盘和LCD 来进行频率输入和显示。

根据要求,我们设计了系统原理图,如图1所示。

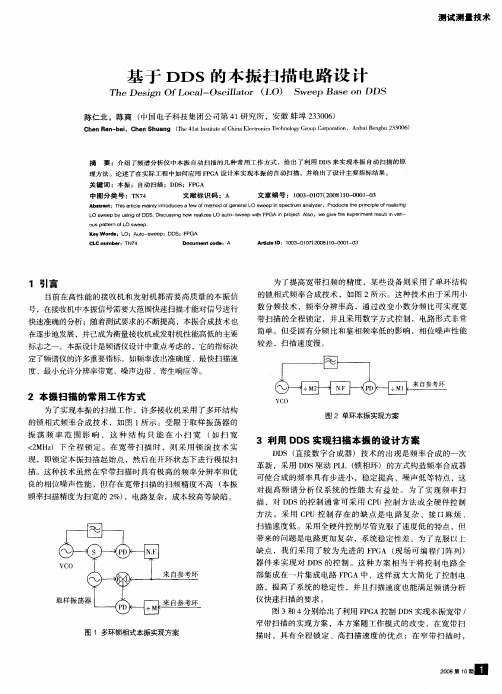

图1 系统原理图三.工作原理1、频率源DDS直接数字式频率合成器DDS(Direct Digital Synthesizer),实际上是一种分频器:通过编程频率控制字来分频系统时钟(SYSTEM CLOCK)以产生所需要的频率。

DDS 有两个突出的特点,一方面,DDS工作在数字域,一旦更新频率控制字,输出的频率就相应改变,其跳频速率高;另一方面,由于频率控制字的宽度宽(48bit 或者更高),频率分辨率高。

DDS 的内部结构如图2所示,它主要分成3 部分:相位累加器,相位幅度转换,数模转换器(DAC)。

图2 DDS内部结构图DDS的基本原理是利用采样定理,通过查表法产生波形。

DDS的结构有很多种,其基本的电路原理如图3所示。

图3 DDS基本电路原理图相位累加器由N位加法器与N位累加寄存器级联构成。

以FPGA为基础的DDS控制电路设计方案详解FPGA是一种可编程逻辑设备,可以实现数字电路的设计和控制。

FPGA可用于设计频率合成器,其中直接数字频率合成(DDS)是一种常见的应用。

DDS是一种用于产生多种频率信号的技术,它使用数字控制寄存器来生成高精度的数字频率控制。

以下是以FPGA为基础的DDS控制电路设计方案的详细解释:1. 整体架构设计:FPGA DDS控制电路的整体架构包括一个相位累加器(phase accumulator)、一个频率控制字寄存器(frequency control word register)和一个查找表(look-up table)。

相位累加器用于生成相位控制信号,频率控制字寄存器用于存储频率控制信息,查找表用于将相位信息转换为实际的输出信号。

2.相位累加器设计:相位累加器是DDS控制电路的核心部分,它通过累加相位控制字来生成输出信号。

相位累加器通常由一个计数器和一个累加器组成。

计数器用于产生一个固定的时钟信号,累加器用于累加相位控制字。

相位控制字决定了相位累加器的累加速度,从而决定了输出信号的频率。

相位累加器的输出信号将作为查找表的输入信号。

3.频率控制字寄存器设计:频率控制字寄存器用于存储频率控制信息。

频率控制信息可以来自外部输入或来自FPGA内部的控制逻辑,例如通过串行接口输入到FPGA中。

频率控制字寄存器将频率控制信息转换为相位控制字,并将相位控制字输入到相位累加器中。

4.查找表设计:查找表用于将相位信息转换为实际的输出信号。

查找表是一个存储器单元,其中包含了预先计算好的正弦波形数据。

查找表根据输入的相位信息,从存储器中读取对应的正弦波形数据,并将数据作为输出信号输出。

查找表的大小取决于输出信号的需求精度,较大的查找表会提供更高的输出精度。

5.时钟和状态控制:DDS控制电路通常需要一个高精度的时钟信号来驱动相位累加器和频率控制字寄存器。

时钟信号的频率和相位可以通过FPGA内部的时钟控制器进行调整。

DDS 电路设计

摘要

本文介绍了DDS的原理,给出了用Altera Cyclone 1 EP1CQ240C8 FPGA芯片实现直接数字频率合成器的工作原理、设计思路、电路结

构和仿真结果以及频谱纯度分析。

关键词:直接数字频率合成(DDS);现场可编程门阵列(FPGA);相位累加器

一、DDS原理概述

1、DDS在基本原理

框图如图所示。

它主要由标准参考频率源、相位累加器、波形存储器、数/模转换器、低通平滑滤波器等构成。

其中,参考频率源一般是一个高稳定度的晶体振荡器,其输出信号用于DDS中各部件同步工作。

DDS的实质是对相位进行可控等间隔的采样。

为实现全数字化的频率可调的频率合成器,本系统基于FPGA采用Verilog HDL设计而成直接数字频率合成器(DDS)。

系统由加法器、累加寄存器、波形存储器、D/A转换器、低通滤波器构成。

在FPGA 里面做到的是D/A转换器之前的部分。

图一DDS原理图

DDS系统的核心是相位累加器,它由一个N位累加器与N位相位寄存器构成。

时钟脉冲每触发一次,累加器便将频率控制数据与相位寄存器输出的累加相位数据相加,然后把相加后的结果送至相位寄存器的数据输入端。

相位寄存器将累加器在上一个时钟作用后所产生的新相位数据反馈到累加器的输入端,以使加法器在下一个时钟的作用下继续与频率控制数据相加。

这样,相位累加器在参考时钟的作用下将进行线性相位累加,当相位累加器累加满时,就会产生一次溢出,以完成一个周期性的动作,这个周期就是DDS合成信号的一个频率周期,相位累加器的溢出频率就是DDS输出的信号频率。

2、DDS参数计算

相位寄存器每经过2N/M 个f c 时钟后回到初始状态,相应地正弦查询表经过一个循环回到初始位置,整个DDS 系统输出一个正弦波。

输出正弦波频率:

2

N

C out

f

f M •

=

本设计中,N=10,M 为位宽为32的频率控制字,fc=20Mhz

二、DDS 电路结构设计

1、电路描述

接口信号

名称 位宽 方向 描述 备注 freq 32 输入 输入频率字

reset 1 输入 复位 高电平异步复位 clock 1 输入 时钟 上升沿有效 sinout 8

输出

输出波形

2补码格式

2、电路结构

DDS 模块RTL Viewer

累加器ACC模块RTL Viewer

ROM模块RTL Viewer

三、DDS电路仿真结果

1、Quartus时序仿真

设定时序分析工具为Class timing analyzer tool,观察电路最大运行频率fMAX

用二补码格式观察

2、Modelsim时序仿真

参考时钟fc=20Mhz

(1)当freq =

32'b0000_0001_0000_0000_0000_0000_0000_0000; Modelsim仿真波形如图fo = 78Khz

(2)当freq =

32'b0000_0010_0000_0000_0000_0000_0000_0000; Modelsim仿真波形如图fo = 156Khz

(3)当freq =

32'b0000_0100_0000_0000_0000_0000_0000_0000; Modelsim仿真波形如图fo =

(4)当freq =

32'b0000_1000_0000_0000_0000_0000_0000_0000; Modelsim仿真波形如图fo = 625Khz

四、频谱纯度分析

(原始信号)频率控制字为32'h08000000

时间

01234

5678910x 10

6

X: 6.25e+005Y: 89.17

(幅度-频率曲线)频率控制字为32'h08000000

频率/Hz

幅度/d B

(原始信号)频率控制字为32'h04000000

时间

x 10

6

(幅度-频率曲线)频率控制字为32'h04000000

频率/Hz

幅度/d B

200

40060080010001200

(原始信号)频率控制字为32'h02000000

时间

x 10

6

(幅度-频率曲线)频率控制字为32'h02000000

频率/Hz

幅度/d B

(原始信号)频率控制字为32'h01000000

时间

01234

5678910x 10

6

(幅度-频率曲线)频率控制字为32'h01000000

频率/Hz

幅度/d B

可见,随着频率控制字的减小,频谱的杂散现象越来越严重。

这是由相位截断所造成的。

五、代码附录

1、dds 模块(顶层模块)

2、acc 模块

3

*另外,为了做频谱分析,避免数据制式转换带来的麻烦,写ROM的时候,我又在原来的正弦波基础上加了个直流分量。

等到要从Modelsim中读取数据再导入到matlab的时候,我又把这个直流分量减去。

因为没有找到很好的解决数据制式问题的办法,所以我就用这个办法也能从matlab中再把波形还原出来。

Testbench

参考文献

[1]张厥盛,曹丽娜.锁相与频率合成技术[M].成都:电子科技大学出版社

[2]Altera Corporation,2001

[3]夏宇闻Verilog 数字系统设计教程[M].北京航空航天大学出版社.2003。