第1章+集成电路制造工艺

- 格式:ppt

- 大小:1.87 MB

- 文档页数:55

第一部分考试试题第0章绪论1.什么叫半导体集成电路?2.按照半导体集成电路的集成度来分,分为哪些类型,请同时写出它们对应的英文缩写?3.按照器件类型分,半导体集成电路分为哪几类?4.按电路功能或信号类型分,半导体集成电路分为哪几类?5.什么是特征尺寸?它对集成电路工艺有何影响?6.名词解释:集成度、wafer size、die size、摩尔定律?第1章集成电路的基本制造工艺1.四层三结的结构的双极型晶体管中隐埋层的作用?2.在制作晶体管的时候,衬底材料电阻率的选取对器件有何影响?。

3.简单叙述一下pn结隔离的NPN晶体管的光刻步骤?4.简述硅栅p阱CMOS的光刻步骤?5.以p阱CMOS工艺为基础的BiCMOS的有哪些不足?6.以N阱CMOS工艺为基础的BiCMOS的有哪些优缺点?并请提出改进方法。

7. 请画出NPN晶体管的版图,并且标注各层掺杂区域类型。

8.请画出CMOS反相器的版图,并标注各层掺杂类型和输入输出端子。

第2章集成电路中的晶体管及其寄生效应1.简述集成双极晶体管的有源寄生效应在其各工作区能否忽略?。

2.什么是集成双极晶体管的无源寄生效应?3. 什么是MOS晶体管的有源寄生效应?4. 什么是MOS晶体管的闩锁效应,其对晶体管有什么影响?5. 消除“Latch-up”效应的方法?6.如何解决MOS器件的场区寄生MOSFET效应?7. 如何解决MOS器件中的寄生双极晶体管效应?第3章集成电路中的无源元件1.双极性集成电路中最常用的电阻器和MOS集成电路中常用的电阻都有哪些?2.集成电路中常用的电容有哪些。

3. 为什么基区薄层电阻需要修正。

4. 为什么新的工艺中要用铜布线取代铝布线。

5. 运用基区扩散电阻,设计一个方块电阻200欧,阻值为1K的电阻,已知耗散功率为20W/c㎡,该电阻上的压降为5V,设计此电阻。

第4章TTL电路1.名词解释电压传输特性开门/关门电平逻辑摆幅过渡区宽度输入短路电流输入漏电流静态功耗瞬态延迟时间瞬态存储时间瞬态上升时间瞬态下降时间瞬时导通时间2. 分析四管标准TTL与非门(稳态时)各管的工作状态?3. 在四管标准与非门中,那个管子会对瞬态特性影响最大,并分析原因以及带来那些困难。

1-1什么是集成电路?解:集成电路是通过一系列特定的平面制造工艺,将晶体管、二极管等有源器件和电阻、电容等无源器件,按照一定的电路互联关系,“集成”在一块半导体单晶片上,冰封装在一个保护外壳内,能执行特定功能的复杂电子系统。

1-2集成电路制造的主要工艺有哪些?解:重复清洗、氧化、化学气相淀积、金属化、光刻、刻蚀、掺杂和平坦化。

1-3画出集成电路中电阻、电容、二极管、晶体管、场效应晶体管和CMOS反相器的结构图。

1-4半导体工艺经历了哪几种工艺发展过程?现在采用的是哪种工艺技术?解:(1)1952年肖克莱发明了生产型晶体管,其特点是在晶体管生长过程中形成NPN型晶体管。

(2)同年萨拜提出了合金结型晶体管,其原理是将铟球放置在锗片的两边,在高温下溶解锗而形成两个PN结。

(3)1954年贝尔实验室提出了采用气相扩散方法形成台面型结型晶体管。

(4)1960年,硅平面结型晶体管的发明;(5)1954年库尔特提出了用PN结来隔离集成电路中的各个晶体管和其他元件。

(6)1959年仙童公司的罗伯特提出了用平面工艺来制作硅集成电路。

现在采用的是硅平面工艺技术;1-5芯片制造包括哪几个阶段?简要描述各个阶段。

解:(1)硅片制备;将硅从沙中提炼并纯化,形成半导体级硅的多晶硅。

(2)芯片制造;硅片到达硅片制造厂,经过清洗、成膜、光刻、刻蚀、和掺杂(扩散、离子注入)等主要工艺之后,加工成的硅片具有永久刻蚀在硅片上的完整的集成电流。

(3)掩膜板制作;掩膜版中包括构成芯片的各层图形结构,现在最常用的掩膜版技术是石英玻璃涂敷,在石英玻璃掩膜版表面的洛层上形成芯片各层结构图形。

(4)装配与封装;芯片制造完成后,封装之前芯片要经过测试/挑选进行单个芯片的电学测试,拣选出合格芯片和不合格芯片,并作出标识,合格芯片包装在保护壳内。

(5)终测;为了确保芯片的功能,要对每个被封装的集成电路进行测试,以保障芯片的电学和环境特性参数满足要求。

集成电路设计与制造技术作业指导书第1章集成电路设计基础 (3)1.1 集成电路概述 (3)1.1.1 集成电路的定义与分类 (3)1.1.2 集成电路的发展历程 (3)1.2 集成电路设计流程 (4)1.2.1 设计需求分析 (4)1.2.2 设计方案制定 (4)1.2.3 电路设计与仿真 (4)1.2.4 布局与布线 (4)1.2.5 版图绘制与验证 (4)1.2.6 生产与测试 (4)1.3 设计规范与工艺限制 (4)1.3.1 设计规范 (4)1.3.2 工艺限制 (4)第2章基本晶体管与MOSFET理论 (5)2.1 双极型晶体管 (5)2.1.1 结构与工作原理 (5)2.1.2 基本特性 (5)2.1.3 基本应用 (5)2.2 MOSFET晶体管 (5)2.2.1 结构与工作原理 (5)2.2.2 基本特性 (5)2.2.3 基本应用 (5)2.3 晶体管的小信号模型 (5)2.3.1 BJT小信号模型 (6)2.3.2 MOSFET小信号模型 (6)2.3.3 小信号模型的应用 (6)第3章数字集成电路设计 (6)3.1 逻辑门设计 (6)3.1.1 基本逻辑门 (6)3.1.2 复合逻辑门 (6)3.1.3 传输门 (6)3.2 组合逻辑电路设计 (6)3.2.1 组合逻辑电路概述 (6)3.2.2 编码器与译码器 (6)3.2.3 多路选择器与多路分配器 (6)3.2.4 算术逻辑单元(ALU) (7)3.3 时序逻辑电路设计 (7)3.3.1 时序逻辑电路概述 (7)3.3.2 触发器 (7)3.3.3 计数器 (7)3.3.5 数字时钟管理电路 (7)第4章集成电路模拟设计 (7)4.1 放大器设计 (7)4.1.1 放大器原理 (7)4.1.2 放大器电路拓扑 (7)4.1.3 放大器设计方法 (8)4.1.4 放大器设计实例 (8)4.2 滤波器设计 (8)4.2.1 滤波器原理 (8)4.2.2 滤波器电路拓扑 (8)4.2.3 滤波器设计方法 (8)4.2.4 滤波器设计实例 (8)4.3 模拟集成电路设计实例 (8)4.3.1 集成运算放大器设计 (8)4.3.2 集成电压比较器设计 (8)4.3.3 集成模拟开关设计 (8)4.3.4 集成模拟信号处理电路设计 (8)第5章集成电路制造工艺 (9)5.1 制造工艺概述 (9)5.2 光刻工艺 (9)5.3 蚀刻工艺与清洗技术 (9)第6章硅衬底制备技术 (10)6.1 硅材料的制备 (10)6.1.1 硅的提取与净化 (10)6.1.2 高纯硅的制备 (10)6.2 外延生长技术 (10)6.2.1 外延生长原理 (10)6.2.2 外延生长设备与工艺 (10)6.2.3 外延生长硅衬底的应用 (10)6.3 硅片加工技术 (10)6.3.1 硅片切割技术 (10)6.3.2 硅片研磨与抛光技术 (10)6.3.3 硅片清洗与检验 (10)6.3.4 硅片加工技术的发展趋势 (11)第7章集成电路中的互连技术 (11)7.1 金属互连 (11)7.1.1 金属互连的基本原理 (11)7.1.2 金属互连的制备工艺 (11)7.1.3 金属互连的功能评价 (11)7.2 多层互连技术 (11)7.2.1 多层互连的原理与结构 (11)7.2.2 多层互连的制备工艺 (11)7.2.3 多层互连技术的挑战与发展 (11)7.3.1 铜互连技术 (12)7.3.2 低电阻率金属互连技术 (12)7.3.3 低电阻互连技术的发展趋势 (12)第8章集成电路封装与测试 (12)8.1 封装技术概述 (12)8.1.1 封装技术发展 (12)8.1.2 封装技术分类 (12)8.2 常见封装类型 (12)8.2.1 DIP封装 (12)8.2.2 QFP封装 (13)8.2.3 BGA封装 (13)8.3 集成电路测试方法 (13)8.3.1 功能测试 (13)8.3.2 参数测试 (13)8.3.3 可靠性测试 (13)8.3.4 系统级测试 (13)第9章集成电路可靠性分析 (13)9.1 失效机制 (13)9.2 热可靠性分析 (14)9.3 电可靠性分析 (14)第10章集成电路发展趋势与展望 (14)10.1 先进工艺技术 (14)10.2 封装技术的创新与发展 (14)10.3 集成电路设计方法学的进展 (15)10.4 未来集成电路的发展趋势与挑战 (15)第1章集成电路设计基础1.1 集成电路概述1.1.1 集成电路的定义与分类集成电路(Integrated Circuit,IC)是指在一个半导体衬底上,采用一定的工艺技术,将一个或多个电子电路的组成部分集成在一起,以实现电子器件和电路的功能。

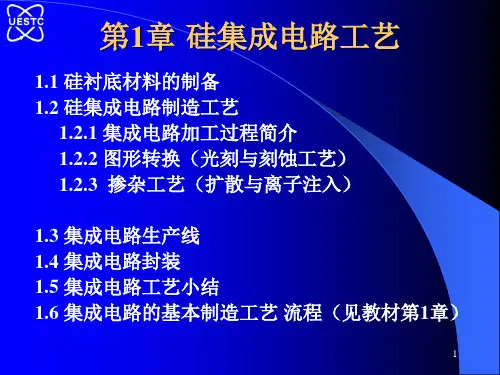

集成电路制造工艺第1章绪论1.1 课题背景在过去的的几十年里,一个以计算机、互联网、无线通信和全球定位系统为组成部分的信息社会逐渐形成。

这个信息社会的核心部分是由众多内建于系统中的细小集成电路(IC)芯片支持和构成的。

集成电路广泛应用于生活中的各个领域—诸如消费类产品、家庭用品、汽车、信息技术、电信、媒体、军事和空间应用。

结合纳米技术,持续不断的研究和开发即将使得集成电路更小和更强有力。

在可见的未来,计算机的尺寸将缩小到指甲盖大小,达到集成电路在尺寸、速度、价格及功耗方面实际可能的极限。

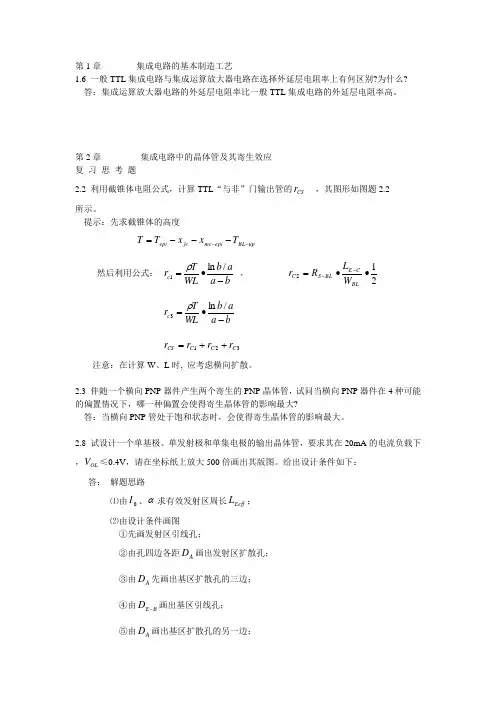

1.2 集成电路制造工艺发展概况随着硅平面工艺技术的不断完善和发展,到1958年,诞生了第一块集成电路,也就是小规模集成电路(SSL);到了20世纪60年代中期,出现了中规模集成电路(MSL);20世纪70年代前期,出现了大规模集成电路(LSL);20世纪70年代后期又出现了超大规模集成电路(VLSL);到了20世纪90年代就出现了特大规模集成电路(ULSL)。

集成电路的制造工艺流程十分复杂,而且不同的种类、不同的功能、不同的结构的集成电路,其制造工艺的流程也不一样。

人们常常以最小线宽(特征尺寸)、硅晶圆片的直径和动态随机存取存储器(DRAM)的容量,来评价集成电路制造工艺的发展水平。

在表1-1中列出了从1995年到2010年集成电路的发展情况和展望。

表1-1 集成电路的发展情况和展望年代1995 1998 2001 2004 2007 2010 特征尺寸/um 0.35 0.25 0.18 0.13 0.09 0.065DRAM容量/bit 64M 256M 1G 4G 16G 64G微处理器尺寸/mm²250 300 360 430 520 620DRAM尺寸/mm²190 280 420 640 960 1400 逻辑电路晶体管密度(晶体管数)/个4M 7M 13M 25M 50M 90M 高速缓冲器/(bit/cm²)2M 6M 20M 50M 100M 300M最大硅晶圆片直径/mm 200 200 300 300 400 400第2章半导体集成电路制造工艺流程2.1 概括本章以大量精美的图片、图表及具体详实的数据详细描述了集成电路制造的全过程。

半导体工艺及芯片制造复习资料简答题与答案第一章、半导体产业介绍1 .什么叫集成电路?写出集成电路发展的五个时代及晶体管的数量?(15分)集成电路:将多个电子元件集成在一块衬底上,完成一定的电路或系统功能。

集成电路芯片/元件数 无集成1 小规模(SSI )2到50 中规模(MSI )50到5000 大规模(LSI )5000到10万 超大规模(VLSI ) 10万至U100万 甚大规模(ULSI ) 大于100万 产业周期1960年前 20世纪60年代前期 20世纪60年代到70年代前期 20世纪70年代前期到后期 20世纪70年代后期到80年代后期 20世纪90年代后期到现在2 .写出IC 制造的5个步骤?(15分)Wafer preparation (硅片准备)Wafer fabrication (硅片制造)Wafer test/sort (硅片测试和拣选)Assembly and packaging (装配和封装)Final test (终测)3 .写出半导体产业发展方向?什么是摩尔定律?(15分)发展方向:提高芯片性能一提升速度(关键尺寸降低,集成度提高,研发采用新材料),降低功耗。

提高芯片可靠性一严格控制污染。

降低成本——线宽降低、晶片直径增加。

摩尔定律指:IC 的集成度将每隔一年翻一番。

1975年被修改为:IC 的集成度将每隔一年半翻一番。

4 .什么是特征尺寸CD ? (10分)最小特征尺寸,称为关键尺寸(Critical Dimension, CD ) CD 常用于衡量工艺难易的标志。

5.什么是 More moore 定律和 More than Moore 定律?(10 分)“More Moore”指的是芯片特征尺寸的不断缩小。

从几何学角度指的是为了提高密度、性能和可靠性在晶圆水平和垂直方向上的特征尺寸的继续缩小。

与此关联的3D结构改善等非几何学工艺技术和新材料的运用来影响晶圆的电性能。

集成电路试题库半导体集成电路典型试题绪论1、什么叫半导体集成电路?【答案:】通过⼀系列的加⼯⼯艺,将晶体管,⼆极管等有源器件和电阻,电容等⽆源元件,按⼀定电路互连。

集成在⼀块半导体基⽚上。

封装在⼀个外壳内,执⾏特定的电路或系统功能。

2、按照半导体集成电路的集成度来分,分为哪些类型,请同时写出它们对应的英⽂缩写【答案:】⼩规模集成电路(SSI),中规模集成电路(MSI),⼤规模集成电路(VSI),超⼤规模集成电路(VLSI),特⼤规模集成电路(ULSI),巨⼤规模集成电路(GSI)3、按照器件类型分,半导体集成电路分为哪⼏类?【答案:】双极型(BJT)集成电路,单极型(MOS)集成电路,Bi-CMOS型集成电路。

4、按电路功能或信号类型分,半导体集成电路分为哪⼏类?【答案:】数字集成电路,模拟集成电路,数模混合集成电路。

5、什么是特征尺⼨?它对集成电路⼯艺有何影响?【答案:】集成电路中半导体器件的最⼩尺⼨如MOSFET的最⼩沟道长度。

是衡量集成电路加⼯和设计⽔平的重要标志。

它的减⼩使得芯⽚集成度的直接提⾼。

6、名词解释:集成度、wafer size、die size、摩尔定律?【答案:】7、分析下⾯的电路,指出它完成的逻辑功能,说明它和⼀般动态组合逻辑电路的不同,分析它的⼯作原理。

【答案:】该电路可以完成NAND逻辑。

与⼀般动态组合逻辑电路相⽐,它增加了⼀个MOS管M kp,它可以解决⼀般动态组合逻辑电路存在的电荷分配的问题。

对于⼀般的动态组合逻辑电路,在评估阶段,A=“H” B=“L”, 电荷被OUT处和A处的电荷分配,整体的阈值下降,可能导致OUT的输出错误。

该电路增加了⼀个MOS管M kp,在预充电阶段,M kp导通,对C点充电到V dd。

在评估阶段,M kp截⾄,不影响电路的正常输出。

8、延迟时间【答案:】时钟沿与输出端之间的延迟第1章集成电路的基本制造⼯艺1、四层三结的结构的双极型晶体管中隐埋层的作⽤【答案:】减⼩集电极串联电阻,减⼩寄⽣PNP管的影响2、在制作晶体管的时候,衬底材料电阻率的选取对器件有何影响【答案:】电阻率过⼤将增⼤集电极串联电阻,扩⼤饱和压降,若过⼩耐压低,结电容增⼤,且外延时下推⼤3、简单叙述⼀下pn结隔离的NPN晶体管的光刻步骤【答案:】第⼀次光刻:N+隐埋层扩散孔光刻第⼆次光刻:P隔离扩散孔光刻第三次光刻:P型基区扩散孔光刻第四次光刻:N+发射区扩散孔光刻第五次光刻:引线孔光刻第六次光刻:反刻铝4、简述硅栅p阱CMOS的光刻步骤【答案:】P阱光刻,光刻有源区,光刻多晶硅,P+区光刻,N+区光刻,光刻接触孔,光刻铝线5、以p阱CMOS⼯艺为基础的BiCMOS的有哪些不⾜【答案:】NPN晶体管电流增益⼩,集电极串联电阻⼤,NPN管的C极只能接固定电位6、以N阱CMOS⼯艺为基础的BiCMOS的有哪些优缺点?并请提出改进⽅法【答案:】⾸先NPN具有较薄的基区,提⾼了其性能:N阱使得NPN管C极与衬底断开,可根据电路需要接任意电位。

第一章VLS知识点VLS(Very Large Scale integration)是指非常大规模集成电路技术,是现代集成电路技术的重要分支。

VLS技术的发展使得集成电路的规模大大增加,功能更加强大,性能更加优越。

本章将介绍VLS知识点的基础知识、设计原理、工艺和应用等方面的内容。

一、基础知识1.集成电路:将多个电子元件(如电晶体、电阻、电容等)集成到单个半导体晶片上的电路。

其主要特点是占用空间小、功耗低、可重复使用。

2.VLSI:非常大规模集成电路,是将成百上千个晶体管集成到一个微小的硅晶片上,使电路规模大大增加。

二、设计原理1.逻辑门电路:是通过逻辑门(与门、或门、非门等)来实现不同逻辑功能的电路。

逻辑门的输出结果仅与输入信号的逻辑关系有关。

2. 布尔代数:在逻辑门电路中,常用布尔代数来描述逻辑关系。

布尔代数是由数学家乔治·布尔(George Boole)创立的一种数学运算方法,用于描述逻辑关系和逻辑运算。

3.时序逻辑:逻辑电路的输出是由输入信号和时钟信号共同决定的。

时钟信号用于控制逻辑电路的工作时序。

三、工艺1.MOSFET:金属-氧化物-半导体场效应晶体管,是VLSI集成电路中常用的基本元件。

其主要特点是体积小、功耗低、噪声低、可靠性高。

2.CMOS:互补金属-氧化物-半导体技术,是一种集成电路制造工艺。

CMOS技术结合了NMOS(n型金属-氧化物-半导体场效应晶体管)和PMOS (p型金属-氧化物-半导体场效应晶体管)技术,具有功耗低、可靠性高的特点。

3.焊接技术:用于将船到的芯片和印刷电路板进行连接的一种技术。

常用的焊接技术有手工焊接、自动焊接、贴片焊接等。

4.接触孔技术:用于在不同层次的芯片之间进行电连接的一种技术。

接触孔技术将不同层次的芯片通过金属导线进行连接,实现不同层次之间的信号传输。

四、应用1.通信领域:VLSI技术的快速发展使得通信设备的功能大大增强。

在通信领域中,VLSI技术被广泛应用于芯片设计、信号处理、调制解调器等方面。