流水线技术

- 格式:ppt

- 大小:2.06 MB

- 文档页数:98

流⽔线技术概述本⽂是对流⽔线技术地基本概念、冒险处理、硬件实现的基本概述。

⾸先我们介绍流⽔线的⼯作原理、组成要求、分类和性能指标,接下来讨论流⽔线的冒险处理,最后我们以MIPS为例,介绍流⽔线数据通路和控制器的实现。

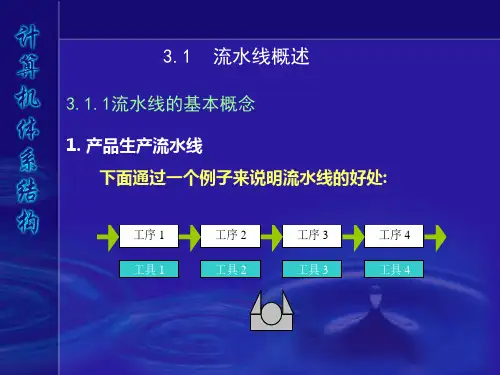

⽬录1. 流⽔线概念针对串⾏执⾏过程中的冗余和瓶颈,我们提出,可以将指令执⾏过程划分为多个阶段,各个阶段可以同时处理操作,这样,每条指令按序通过各段,不同指令的执⾏过程重叠,得到的就是流⽔线。

流⽔线由多个功能段按序组成。

例如,在RISC中,通常包括IF,ID,EX,MEM,WB五个功能段,⽽在CISC中,通常包括IF,ID,OF,EX,WB五个功能段。

理想状况下,流⽔线可以对程序执⾏起到显著的加速作⽤。

例如,有n条指令在m段流⽔线上执⾏,串⾏执⾏的时间为mnt,⽽采⽤流⽔线后,其执⾏时间为(m+n-1)t。

流⽔线在组成上,有三个基本要求。

第⼀,各个段的操作要相互独⽴、相互分离。

因此,每个段的源数据必须来⾃时序部件,结果也要存到时序部件。

实现上,我们设置段间寄存器,其中保存本段的所有后续段需要的本段的数据、地址、命令等。

第⼆,各个流⽔段的操作要同步执⾏。

实现上,我们会设置公共拍时钟,使得段间寄存器被同时写⼊。

拍时钟的周期需要取为各个段长的最⼤值。

第三,各个流⽔段的操作必须⽆冲突,以保证结果正确。

具体⽽⾔,就是消除冒险。

实现上,通过增设部件和控制器,来消除各种冒险。

流⽔线可以按其属性进⾏多种分类。

按处理的级别,可以分为操作级流⽔线、指令级流⽔线、处理机级流⽔线。

按功能,可以分为单功能和多功能流⽔线。

多功能流⽔线的各流⽔段可以进⾏不同的连接,从⽽完成不同的功能。

按⼯作⽅式,可以分为静态流⽔线和动态流⽔线。

静态流⽔线在进⾏功能切换时,必须排空。

显然,动态流⽔线⼀定是多功能流⽔线。

按结构,可以分为线性流⽔线和⾮线性流⽔线。

所谓⾮线性流⽔线,就是其中有部件的复⽤。

按流⼊流出的次序,可以分为顺序流⽔线和乱序流⽔线。

高性能计算中的流水线技术分析随着科技的发展和数据量的不断增长,高性能计算成为当代信息技术领域的重要组成部分。

在高性能计算中,流水线技术起到了至关重要的作用。

本文将从流水线的定义、原理、优势和应用等方面进行深入分析。

一、流水线的定义和原理流水线技术是一种将一个复杂的任务分为多个子任务,通过多个阶段分别处理的技术。

它的运行原理是将输入的任务划分成若干个阶段,每个阶段处理一个任务,并通过将每个任务传递给下一个阶段,实现任务的并行处理。

流水线技术可以提高系统的整体性能和处理效率。

二、流水线技术的优势1. 提高处理效率:流水线技术能够将复杂任务分解成多个简单任务,在每个阶段都能并行处理多个任务,从而提高整体的处理效率。

2. 实现指令重叠:在流水线中,每个阶段都可以同时处理不同的任务,从而实现指令的重叠执行,提高了系统的吞吐量。

3. 减少资源闲置:由于流水线技术可以同时处理多个任务,并且每个阶段都可以开始下一个任务,所以能够减少资源的闲置时间,提高系统的利用率。

三、流水线技术的应用1. CPU设计中的流水线技术:在计算机的CPU设计中,流水线技术广泛应用。

将计算机指令划分为取指令、译码、执行、写回等阶段,并在每个阶段同时处理指令,提高了CPU的计算性能。

2. 图像处理中的流水线技术:在图像处理领域,流水线技术可以将图像处理任务划分为多个阶段,如图像读取、图像滤波、图像增强等,并通过并行处理,快速完成大规模的图像处理任务。

3. 云计算系统中的流水线技术:在云计算系统中,流水线技术可以将用户请求的处理过程划分为多个阶段,如请求接收、请求解析、资源分配等,并将每个阶段分别处理,提高了系统的响应速度和处理能力。

四、流水线技术的挑战和解决方案1. 数据依赖:在流水线中,不同任务之间可能存在依赖关系,导致任务的执行顺序发生变化,从而影响并行处理效果。

解决方案是通过增加冲突检测和处理的机制,在保证数据一致性的前提下实现最大程度的并行处理。

流水线技术流水线技术是一种用于大规模生产的高效生产方式,它通过将生产过程分解为多个简单的工序,并分配给不同的工人或机器进行操作,从而实现生产效率的最大化。

本文将详细介绍流水线技术的起源、原理、应用以及对生产效率和产品质量的影响。

流水线技术最早起源于工业革命时期,主要应用于制造业。

在流水线生产中,产品的生产过程被分解为一系列相互依赖且独立的工序,产品沿着流水线依次经过每个工序,每个工序负责完成特定的任务。

工人或机器在每个工序上分别进行相应的操作,使产品逐步加工完毕,最终得到成品。

流水线生产的原理主要有两个方面。

首先是工序的分解,也就是将复杂的生产过程分解为多个简单的工序,每个工序负责单一的操作。

这样一来,每个工人或机器只需专注于完成自己的任务,能够更加快速、高效地完成工作。

其次是工序之间的协调和协作。

每个工序的完成时间需要与下一个工序的开始时间相协调,确保产品能够顺利地在流水线上流动,避免出现停顿或浪费。

流水线技术在多个行业中得到了广泛应用。

最早应用流水线技术的行业是汽车制造业。

通过流水线技术,汽车生产的每个环节都被细分为多个工序,从焊接、喷涂到组装,每个工序专门由一台机器或一名工人负责,大大提高了汽车制造的效率。

此外,流水线技术还被应用于食品加工、电子制造、石油化工等行业,帮助这些行业提高了生产效率,降低了生产成本。

流水线技术对生产效率和产品质量有着明显的影响。

首先,流水线技术可以提高生产效率,减少生产周期。

由于每个工序负责单一的任务,工人或机器在相同时间内可以完成更多的产品加工,从而大大提高了生产效率。

其次,通过流水线技术,可以降低生产成本。

由于生产效率的提高,单位产品的生产成本会大幅下降,从而提高了企业的竞争力。

最后,流水线技术有助于提高产品质量。

每个工序专门由一台机器或一名工人完成,可以有效控制产品质量,减少人为因素对产品质量的影响。

然而,流水线技术也存在一些问题和挑战。

首先,流水线生产往往需要大规模投资,并且需要高度标准化的产品和生产工艺。

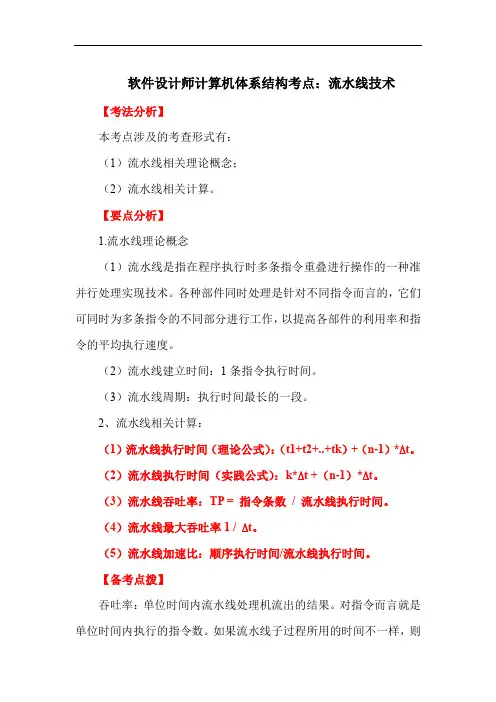

软件设计师计算机体系结构考点:流水线技术【考法分析】本考点涉及的考查形式有:(1)流水线相关理论概念;(2)流水线相关计算。

【要点分析】1.流水线理论概念(1)流水线是指在程序执行时多条指令重叠进行操作的一种准并行处理实现技术。

各种部件同时处理是针对不同指令而言的,它们可同时为多条指令的不同部分进行工作,以提高各部件的利用率和指令的平均执行速度。

(2)流水线建立时间:1条指令执行时间。

(3)流水线周期:执行时间最长的一段。

2、流水线相关计算:(1)流水线执行时间(理论公式):(t1+t2+..+tk)+(n-1)*∆t。

(2)流水线执行时间(实践公式):k*∆t +(n-1)*∆t。

(3)流水线吞吐率:TP = 指令条数/ 流水线执行时间。

(4)流水线最大吞吐率1 / ∆t。

(5)流水线加速比:顺序执行时间/流水线执行时间。

【备考点拨】吞吐率:单位时间内流水线处理机流出的结果。

对指令而言就是单位时间内执行的指令数。

如果流水线子过程所用的时间不一样,则吞吐率P应为(最长子过程的倒数)。

流水线开始工作,需要经过一段时间才能达到最大吞吐率。

【相关考题】1.下列关于流水线方式执行指令的叙述中,不正确的是()。

A.流水线方式可提高单条指令的执行速度B.流水线方式下可同时执行多条指令C.流水线方式提高了各部件的利用率D.流水线方式提高了系统的吞吐率2.流水线的吞吐率是指单位时间流水线处理的任务数,如果各段流水的操作时间不同,则流水线的吞吐率是()的倒数。

A. 最短流水段操作时间B. 各段流水的操作时间总和C. 最长流水段操作时间D. 流水段乘以最长流水段操作时间。

流水线技术流水线技术是一种高效的生产工艺,能够大大提高生产效率和降低成本。

它被广泛应用于各种制造行业,如汽车制造、电子产品制造、食品加工等。

本文将对流水线技术的原理、优势和应用进行详细介绍。

一、流水线技术原理流水线技术的核心原理是将整个生产过程划分为若干个连续的独立工作站,每个工作站负责完成一项具体的任务或工序。

产品在流水线上按照固定的顺序经过各个工作站,每个工作站只需完成相应的工序,然后将产品传递给下一个工作站。

流水线技术的顺序流程可以按照产品的不同特性和工艺要求来设计。

有些产品需要按照指定的工序顺序进行处理,而有些产品则需要在流水线上经过多个不同的工作站进行加工,以达到最终的成品要求。

二、流水线技术的优势1. 提高生产效率:通过将生产过程进行细分并利用并行处理,流水线技术可以大大提高生产效率。

工作站之间的协调和衔接使得产品在不间断流动的情况下进行加工,从而减少了非价值增加的等待时间。

2. 降低生产成本:在流水线上,人力资源的利用更加高效,无需每个工人都掌握所有工序的技能,只需要专注于自己所负责的工序。

这不仅可以提高工人的专注度,还可以降低培训成本。

3. 简化管理:流水线技术可以将复杂的制造过程分解成若干个简单的工序,每个工序由专人负责,使得生产管理更加简化。

管理者只需监控整个流水线的运行情况和协调各个工序的衔接,而不需要详细了解每个具体工序的细节。

4. 质量可控性强:流水线上的每个工序都可以进行专门的检测和控制,确保产品在各个工序中的质量。

一旦出现质量问题,可以及时追溯到具体的工序和责任人,以便进行纠正和改进。

三、流水线技术的应用1. 汽车制造:汽车生产过程中各个工序的高度标准化和流程化使得流水线技术成为汽车制造的理想选择。

从焊接、涂装到总装,每个工作站都有专业的操作人员,确保汽车制造过程的高效和质量。

2. 电子产品制造:电子产品制造过程中需要经过多个工序,如组装、焊接、测试等。

流水线技术可以有效地管理这些工序,提高生产效率和保证产品质量。

第3章流水线技术3.1解释下列术语流水线:将一个重复的时序过程,分解成为若干个子过程,而每一个子过程都可有效地在其专用功能段上与其它子过程同时执行。

单功能流水线:指流水线的各段之间的连接固定不变、只能完成一种固定功能的流水线。

多功能流水线:指各段可以进行不同的连接,以实现不同的功能的流水线。

静态流水线:指在同一时间内,多功能流水线中的各段只能按同一种功能的连接方式工作的流水线。

当流水线要切换到另一种功能时,必须等前面的任务都流出流水线之后,才能改变连接。

动态流水线:指在同一时间内,多功能流水线中的各段可以按照不同的方式连接,同时执行多种功能的流水线。

它允许在某些段正在实现某种运算时,另一些段却在实现另一种运算。

部件级流水线:把处理机中的部件进行分段,再把这些部件分段相互连接而成。

它使得运算操作能够按流水方式进行。

这种流水线也称为运算操作流水线。

处理机级流水线:又称指令流水线。

它是把指令的执行过程按照流水方式进行处理,即把一条指令的执行过程分解为若干个子过程,每个子过程在独立的功能部件中执行。

处理机间流水线:又称为宏流水线。

它是把多个处理机串行连接起来,对同一数据流进行处理,每个处理机完成整个任务中的一部分。

前一个处理机的输出结果存入存储器中,作为后一个处理机的输入。

线性流水线:指各段串行连接、没有反馈回路的流水线。

数据通过流水线中的各段时,每一个段最多只流过一次。

非线性流水线:指各段除了有串行的连接外,还有反馈回路的流水线。

顺序流水线:流水线输出端任务流出的顺序与输入端任务流入的顺序完全相同。

乱序流水线:流水线输出端任务流出的顺序与输入端任务流入的顺序可以不同,允许后进入流水线的任务先完成。

这种流水线又称为无序流水线、错序流水线、异步流水线。

吞吐率:在单位时间内流水线所完成的任务数量或输出结果的数量。

流水线的加速比:使用顺序处理方式处理一批任务所用的时间与按流水处理方式处理同一批任务所用的时间之比。

数据流水线技术在企业业务中的作用亚马逊、微软等科技巨头都在持续投入人力和物力,以进一步提升数据中心及互联网等关键领域中的计算效率。

数据流水线技术作为这些工作中的一个关键要素,正为企业的业务带来了诸多益处。

在本文中,我们将探讨数据流水线技术在企业业务中的作用。

1. 什么是数据流水线技术数据流水线技术,即将工作流分割成不同功能阶段,将不同的任务分配给不同的模块,从而实现高效的任务处理。

在当前的计算机系统中,数据流水线技术已被广泛应用。

例如,当你打开电脑上的浏览器,输入网址,就会启动一系列的数据流水线开始处理这次浏览请求。

2. 数据流水线技术在企业业务中的应用数据流水线技术在企业及商业应用中也有大量应用。

它可以被用于构建数据处理管道,帮助企业优化处理数据的效率。

2.1 增加应用性能数据流水线技术可以将任务切割为不同的单元,减少单个模块的处理压力。

这将使企业的处理速度更快,并能够同时处理多个任务。

该技术还可以使企业更快地完成周期性任务,例如每周的账单生成或每月的客户报告制作。

增强应用性能的另一个好处是提高整个企业的生产力,从而为企业带来更多收益。

例如,当数据分析部门可以更快地处理数据时,他们可以更快地预测销售趋势或客户需求,进而改进企业的产品或服务。

2.2 精简整个工作流程企业需要执行的工作往往涉及大量数据的处理和分析。

将整个工作流定义和矩阵化的过程,可以使企业更高效地分解任务并协调不同阶段之间的工作。

该技术可以帮助企业更好地管理数据收集、处理和报告等任务,并确保各阶段能够协调一致地执行。

2.3 预防错误处理在某些情况下,企业的处理流程可能会出错,会导致整个工作流程中所有阶段的任务被影响。

为了避免这种情况,企业可以通过使用数据流水线技术增加冗余、并行处理及错误处理机制来降低错误发生概率。

例如,当数据分析师需要处理一个大型数据集时,可以将任务切分为多个组件,并在步骤开始和结束时进行检查来确保数据完整性。

使用数据流水线技术可减少硬件或软件问题导致的错误处理,提高数据准确性和时间效率。