arm_3 中断 异常处理 输入输出口

- 格式:ppt

- 大小:813.00 KB

- 文档页数:61

Arm的中断处理流程1:芯片输入管脚,按照中断的配置发生变化,(比如产生上升沿),arm芯片内部就会检测到中断。

2:ARM要求中断向量表必须放置在从0开始、连续8×4字节的空间内。

所以地址空间“0x00000000-0x00000032”就是所谓的中断向量表。

3:arm检测到中断后,会根据中断的类型强行设置PC寄存器的值。

把当前cpsr的内容保存到spsr_mode . 然后改变cpsr得内容。

(并且把相应的irq或者fiq设置为1,以禁止中断)中断的类型如下表:比如,这个时候来的是复位中断,则IP寄存器的值为0x00000000, 如果来的是IRQ中断则设置IP寄存器的值为 0x00000018。

注意上述中断信号的产生, cpsr 内容的保存,cpsr自动更改,PC寄存器值的设置,都是arm硬件自动完成。

4: arm CPU接下来就会从“IP寄存器所指的地址”内取指令,比如IP内的值是0x00000018,则会从地址 0x00000018 内取指令。

5:中断向量表的内容是我们先前设置好的。

假设是一个IRQ , 0x00000018处的指令为:B INT_IRQ;则代码跳到 INT_IRQ 处的程序执行。

6:INT_IRQ;; /* This Code is to fix a bug in the ARM Core */;STMDB sp!, {r1}MRS r1, SPSRTST r1, #I_BITLDMIA sp!, {r1}SUBNES pc,lr,#4; //保存环境; /* End ARM Core Fix */STMDB sp!, {a1 - v7, fp, ip, lr} ; Save context…… //里面会进行某些状态位判断,以确定具体是哪个中断,然后调用相应处理程序//恢复环境INT_IRQ_EXITLDMIA sp!, {a1 - v7, fp, ip, lr} ; Restore contextSUBS pc, lr, #4 ; Return to interrupted codeEND ; end file7:What happens if an interrupt occurs as it is being disabled?Applies to:If an interrupt is received by the core during execution of an instruction that disables interrupts, the ARM7 family will still take the interrupt. This occurs for both IRQ and FIQ interrupts.For example, consider the follow instruction sequence:MRS r0, cpsrORR r0, r0, #I_Bit:OR:F_Bit ;disable IRQ and FIQ interruptsMSR cpsr_c, r0If an IRQ interrupt is received during execution of the MSR instruction, then the behavior will be as follows:The IRQ interrupt is latchedThe MSR cpsr, r0 executes to completion setting both the I bit and the F bit in the CPSRThe IRQ interrupt is taken because the core was committed to taking the interrupt exception before the I bit was set in the CPSR. The CPSR (with the I bit and F bit set) is moved to the SPSR_irq上面是arm的一个bug。

ARM 体系中异常中断种类及处理办法在ARM 体系中,通常有以下3 种方式控制程序的执行流程:

•在正常程序执行过程中,每执行一条ARM 指令,程序计数器寄存器(PC)的值加4 个字节;每执行一条Thumb 指令,程序计数器寄存器(PC)的值加2 个字节。

整个过程是顺序执行。

•通过跳转指令,程序可以跳转到特定的地址标号处执行,或者跳转到特定的子程序处执行。

其中,B 指令用于执行跳转操作;BL 指令在执行跳转操作的同时,保存子程序的返回地址;BX 指令在执行跳转操作的同时,根据目标地址的最低位可以将程序状态切换到Thumb 状态;BLX 指令执行3 个操作:跳转到目标地址处执行,保存了子程序的返回地址,根据目标地址的最低位可以将程序状态切换到Thumb 状态。

•当异常中断发生时,系统执行完当前指令后,将跳转到相应的异常中断处理程序处执行。

在当异常中断处理程序执行完成后,程序返回到发生中断的指令的下一条指令处执行。

在进入异常中断处理程序时,要保存被中断的程序的执行现场,在从异常中断处理程序退出时,要恢复被中断的程序的执行现场。

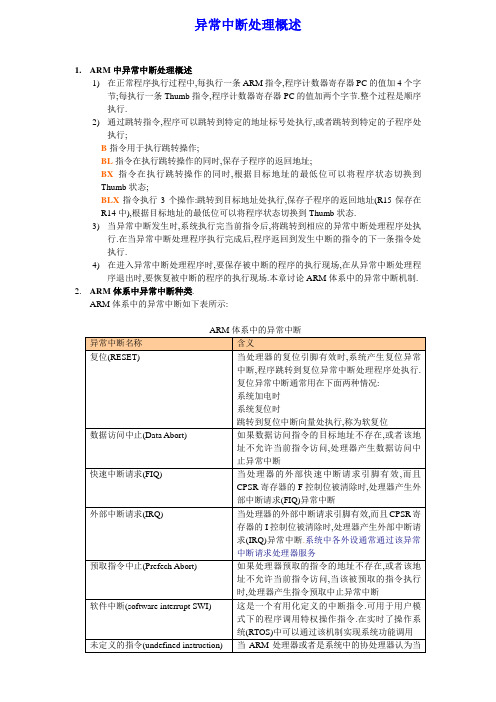

异常中断处理概述1.ARM中异常中断处理概述1)在正常程序执行过程中,每执行一条ARM指令,程序计数器寄存器PC的值加4个字节;每执行一条Thumb指令,程序计数器寄存器PC的值加两个字节.整个过程是顺序执行.2)通过跳转指令,程序可以跳转到特定的地址标号处执行,或者跳转到特定的子程序处执行;B指令用于执行跳转操作;BL指令在执行跳转操作的同时,保存子程序的返回地址;BX指令在执行跳转操作的同时,根据目标地址的最低位可以将程序状态切换到Thumb状态;BLX指令执行3个操作:跳转到目标地址处执行,保存子程序的返回地址(R15保存在R14中),根据目标地址的最低位可以将程序状态切换到Thumb状态.3)当异常中断发生时,系统执行完当前指令后,将跳转到相应的异常中断处理程序处执行.在当异常中断处理程序执行完成后,程序返回到发生中断的指令的下一条指令处执行.4)在进入异常中断处理程序时,要保存被中断的程序的执行现场,在从异常中断处理程序退出时,要恢复被中断的程序的执行现场.本章讨论ARM体系中的异常中断机制.2.ARM体系中异常中断种类.ARM体系中的异常中断如下表所示:3.中断向量表中指定了各异常中断及其处理程序的对应关系.它通常存放在存储地址的低端.在ARM体系中,异常中断向量表的大小为32字节.其中,每个异常中断占据4个字节大小,保留了4个字节空间.每个异常中断对应的中断向量表的4.通过这两种指令,程序将跳转到相应的异常中断处理程序处执行.当几个异常中断同时发生时,就必须按照一定的次序来处理这些异常中断.在ARM 中通过给各异常中断富裕一定的优先级来实现这种处理次序.当然有些异常中断是不坑能同时发生的,如指令预取中止异常中断和软件中断(SWI)异常中断是有同一条指令的执行触发的,他们是不可能同时发生的.处理器执行某个特定的异常中断的过程中,称为处理器处于特定的中断模式.各异常中断的中断向量地址以及中断的处理优先级如表2所示.4.异常中断使用的寄存器各异常中断对应着一定的处理器模式.应用程序通常运行在用户模式下.ARM中的处理器模式如表3所示.各种不同的处理器模式可能有对应于该处理器模式的物理寄存器组,如表4所示,其中,R13_svc表示特权模式下的R13寄存器,R13_abt表示中止模式下的R13寄存器,其余的各寄存器名称含义类推.表4 各处理器模式的物理寄存器组如果异常中断处理程序中使用它自己的物理寄存器之外的其它寄存器,异常中断处理程序必须保存和恢复这些寄存器.在表4中各物理寄存器的名称(如R13_svc等)在ARM汇编语言中并没有被预定义.用户使用这些寄存器时,必须使用伪操作RN来定义这些名称.如可以通过下面操作定义寄存器名称R13_svc:R13_svc RN R13一.进入和退出异常中断的过程1.ARM处理器对异常中断的相应过程ARM处理器对异常中断的响应过程如下:a.保存处理器当前状态,中断屏蔽位以及各条件标志位.只是通过将当前程序状态寄存器CPSR的内容保存到将要执行的异常总段对应的SPSR寄存器中实现的.各异常中断有自己的物理SPSR寄存器.b.设置当前程序CPSR中相应的位.包括设置CPSR中的位,使处理器进入相应的执行模式;设置CPSR中的位,禁止IRQ:当进入FIQ模式时,禁止FIQ中断.c.将寄存器LR_mode(R14)设置成返回地址,R14从R15中得到PC的备份.d.将程序计数器值PC设置成该异常中断的中断向量地址,从而跳转到相应的异常中断处理程序处执行.上述的处理器对异常中断的相应过程可以用如下的伪代码描述.e.响应复位异常中断.当处理器的复位引脚有效时,处理器中止当前指令.当处理器的复位引脚变成无效时,处理器开始执行下面的操作.R14_svc = UNPREDICTABLE valueSPSR_svc = UNPREDICTABLE valueCPSR[4:0] = 0b10011 //进入特权模式CPSR[5] = 0 //切换到ARM状态CPSR[6] = 1 //禁止FIQ异常中断CPSR[7] = 1 //禁止IRQ中断If high vectors configured thenPC = 0xffff0000ElsePC = 0x00000000f.响应未定义指令异常中断处理器相应未定义指令异常中断时的处理过程如下面的伪代码所示.R14_und = address of next instruction after the undefined instructionSPSR_und = CPSRCPSR[4:0] = 0b11011 //进入未定义指令异常中断模式CPSR[5] = 0 //切换到ARM状态CPSR[6] = 1 //禁止FIQ异常中断CPSR[7] = 1 //禁止IRQ中断If high vectors configured thenPC = 0xffff0004ElsePC = 0x00000004g.响应SWI异常中断处理器相应SWI异常中断时的处理过程如下面的伪代码所示.R14_svc = address of next instruction after the SWI instructionSPSR_svc = CPSRCPSR[4:0] = 0b10011 //进入特权模式CPSR[5] = 0 //切换到ARM状态CPSR[6] = 1 //禁止FIQ异常中断CPSR[7] = 1 //禁止IRQ中断If high vectors configured thenPC = 0xffff0008ElsePC = 0x00000008h.响应指令预取中止异常中断.处理器相应指令预取中止异常会总段时的处理过程如下面的伪代码所示.R14_abt = address of the aborted instruction + 4SPSR_abt = CPSRCPSR[4:0] = 0b10111 //进入指令预取中止模式CPSR[5] = 0 //切换到ARM状态CPSR[6] = 1 //禁止FIQ异常中断CPSR[7] = 1 //禁止IRQ中断If high vectors configured thenPC = 0xffff000cElsePC = 0x0000000ci.响应数据访问中止异常中断处理器相应数据访问中止异常中断时的处理过程如下面的伪代码所示.R14_abt = address of the aborted instruction + 8SPSR_abt = CPSRCPSR[4:0] = 0b10111 //进入数据访问中止模式CPSR[5] = 0 //切换到ARM状态CPSR[6] = 1 //禁止FIQ异常中断CPSR[7] = 1 //禁止IRQ中断If high vectors configured thenPC = 0xffff0010ElsePC = 0x00000010j.响应IRQ异常中断处理器相应IRQ异常总段时的处理过程如下面的伪代码所示.R14_irq = address of next instruction to be executed + 4SPSR_irq = CPSRCPSR[4:0] = 0b10010 //进入IRQ异常中断模式CPSR[5] = 0 //切换到ARM状态CPSR[6] = 0 //打开FIQ异常中断CPSR[7] = 1 //禁止IRQ中断If high vectors configured thenPC = 0xffff0018ElsePC = 0x00000018k.响应FIQ异常中断处理器相应FIQ异常中断时的处理过程如下面的伪代码所示.2.从异常中断处理程序种返回基本操作:1)恢复被中断的程序的处理器状态,即将SPSR_mode寄存器内容复制到当前程序状态寄存器CPSR中。

单片机指令的中断输入和输出控制在单片机的程序设计中,中断输入和输出控制是非常重要的一部分。

中断输入可以使得单片机能够在特定的事件发生时立即做出相应的处理,而输出控制则可以让单片机与外部设备进行有效的交互。

本文将详细介绍单片机指令的中断输入和输出控制相关的知识。

1. 中断输入中断输入是指当特定的事件发生时,单片机可以立即中断正在执行的程序,执行特定的中断服务程序。

这样可以提高系统的实时响应能力,使得单片机可以及时地对外部事件做出相应。

在单片机的中断输入中,有两个重要概念,即中断源和中断向量表。

中断源是指能够触发中断的事件或信号源,比如定时器溢出、外部中断引脚状态改变等。

当中断源发生时,会向单片机发送中断请求信号,让单片机进入中断服务程序。

中断向量表则是一张记录不同中断源对应的中断服务程序地址的表格。

当中断请求发生时,单片机会根据中断源的编号在中断向量表中查找对应的中断服务程序的入口地址,并跳转到该地址开始执行中断服务程序。

2. 输出控制输出控制是指通过单片机的输出端口,控制与之连接的外部设备的状态或行为。

利用单片机的输出控制,可以实现对灯光、蜂鸣器、电机等外部设备的控制。

在单片机的输出控制中,需要了解的概念是输出端口和控制寄存器。

输出端口是单片机上的一个或多个引脚,通过这些引脚可以向外部设备发送电平信号。

每个输出端口都有一个对应的控制寄存器,用于设置引脚输出的电平值。

控制寄存器中的位控制引脚的输出状态,一般包括设置引脚为输出模式或输入模式,设置引脚输出高电平还是低电平等功能。

通过对输出端口的设置和控制寄存器的配置,可以实现对外部设备的状态或行为进行控制。

3. 单片机指令的中断输入和输出控制在单片机的编程中,为了实现中断输入和输出控制功能,需要掌握一些相关的指令和编程技巧。

首先是中断输入方面,单片机一般提供了一些专门的中断指令,如"使能中断"、"屏蔽中断"、"清除中断标志位"等指令。

ARM处理器异常模式只要正常的程序流被暂时中止,处理器就进入异常模式。

例如响应一个来自外设的中断。

在处理异常之前,ARM7TDMI 内核保存当前的处理器状态,这样当处理程序结束时可以恢复执行原来的程序。

如果同时发生两个或更多异常,那么将按照固定的顺序来处理异常,详见“异常优先级”部分。

关于“异常的入口和出口处理”:如果异常处理程序已经把返回地址拷贝到堆栈,那么可以使用一条多寄存器传送指令来恢复用户寄存器并实现返回。

关于“进入异常”:在异常发生后,ARM7TDMI内核会作以下工作:1.在适当的LR中保存下一条指令的地址,当异常入口来自:ARM状态,那么ARM7TDMI将当前指令地址加4或加8复制(取决于异常的类型)到LR中;为Thumb状态,那么ARM7TDMI将当前指令地址加4或加8 (取决于异常的类型)复制到LR中;异常处理器程序不必确定状态。

2.将CPSR复制到适当的SPSR中;3. 将CPSR模式位强制设置为与异常类型相对应的值;4.强制PC从相关的异常向量处取指。

ARM7TDMI内核在中断异常时置位中断禁止标志,这样可以防止不受控制的异常嵌套。

注:异常总是在ARM状态中进行处理。

当处理器处于Thumb 状态时发生了异常,在异常向量地址装入PC时,会自动切换到ARM状态。

关于“退出异常”:当异常结束时,异常处理程序必须:1.将LR中的值减去偏移量后存入PC,偏移量根据异常的类型而有所不同;2.将SPSR的值复制回CPSR;3.清零在入口置位的中断禁止标志。

注:恢复CPSR的动作会将T、F和I位自动恢复为异常发生前的值。

下面利用,图示来演示“进入异常”过程:1. 程序在系统模式下运行用户程序,假定当前处理器状态为Thumb状态、允许IRQ中断;2. 用户程序运行时发生IRQ中断,硬件完成以下动作:(1)将CPSR寄存器内容存入IRQ模式的SPSR寄存器(2)置位I位(禁止IRQ中断)(3)清零T位(进入ARM状态)(4)设置MOD位,切换处理器模式至IRQ模式(5)将下一条指令的地址存入IRQ模式的LR寄存器(6)将跳转地址存入PC,实现跳转图示“退出异常”过程:在异常处理结束后,异常处理程序完成以下动作:(1)将SPSR寄存器的值复制回CPSR寄存器;(2)将LR寄存的值减去一个常量后复制到PC寄存器,跳转到被中断的用户程序。

ARM处理器中断处理的编程实现中断是指外部事件打断正在执行的程序,并暂时转去执行与该事件有关的处理程序。

在ARM处理器上,中断处理是通过中断向量表和中断服务程序来实现的。

下面是ARM处理器中断处理的编程实现的主要内容。

1.中断向量表的设置在ARM处理器中,中断向量表是一个保存中断服务程序地址的表。

每个中断号对应一个中断服务程序的地址,当发生中断时,处理器会跳转到相应中断号对应的中断服务程序。

中断向量表必须存储在内存中,并且要先设置好才能使得中断处理正常工作。

为了设置中断向量表,需要将每个中断号对应的中断服务程序的地址写入到相应的中断向量表项中。

具体的实现方式根据不同的ARM架构有所不同。

以ARM Cortex-M系列处理器为例,中断向量表的每个向量表项占用4个字节,存储中断服务程序的地址。

下面是使用C语言设置中断向量表的示例代码:```c//声明中断向量表typedef void (*interrupt_handler_t)(void);//中断服务程序声明void interrupt_handler1(void);void interrupt_handler2(void);...//中断向量表__attribute__ ((section(".isr_vector")))const interrupt_handler_t interrupt_vector_table[] =interrupt_handler1, // 中断号0对应的中断服务程序interrupt_handler2, // 中断号1对应的中断服务程序...```2.中断服务程序的编写中断服务程序负责处理中断的具体逻辑。

当中断发生时,处理器会跳转到对应中断号的中断服务程序进行处理。

中断服务程序必须具有固定的格式和规范,以确保在中断发生时能正常执行。

中断服务程序的编写一般包括以下几个步骤:-保存寄存器状态:由于中断服务程序会暂时打断正在执行的程序,需要在进入中断服务程序时保存当前的寄存器状态,以便中断处理完成后能够正确恢复现场。