DSP程序优化

- 格式:pdf

- 大小:331.07 KB

- 文档页数:14

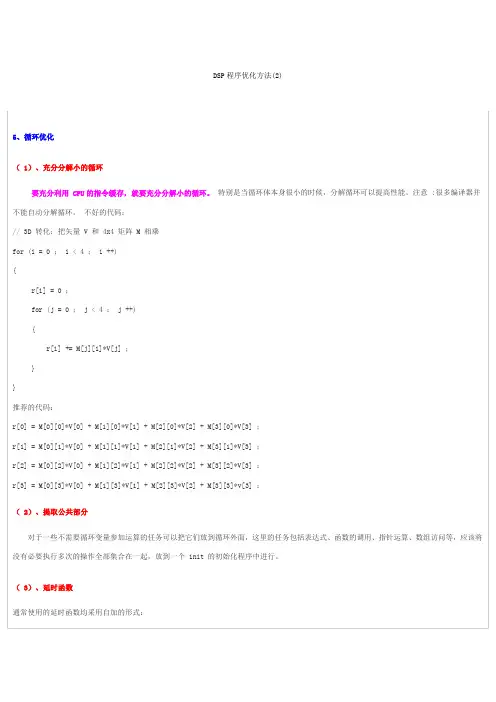

DSP程序优化方法(2)5、循环优化( 1)、充分分解小的循环要充分利用 CPU的指令缓存,就要充分分解小的循环。

特别是当循环体本身很小的时候,分解循环可以提高性能。

注意 :很多编译器并不能自动分解循环。

不好的代码:// 3D 转化:把矢量 V 和 4x4 矩阵 M 相乘for (i = 0 ; i < 4 ; i ++){r[i] = 0 ;for (j = 0 ; j < 4 ; j ++){r[i] += M[j][i]*V[j] ;}}推荐的代码:r[0] = M[0][0]*V[0] + M[1][0]*V[1] + M[2][0]*V[2] + M[3][0]*V[3] ;r[1] = M[0][1]*V[0] + M[1][1]*V[1] + M[2][1]*V[2] + M[3][1]*V[3] ;r[2] = M[0][2]*V[0] + M[1][2]*V[1] + M[2][2]*V[2] + M[3][2]*V[3] ;r[3] = M[0][3]*V[0] + M[1][3]*V[1] + M[2][3]*V[2] + M[3][3]*v[3] ;( 2)、提取公共部分对于一些不需要循环变量参加运算的任务可以把它们放到循环外面,这里的任务包括表达式、函数的调用、指针运算、数组访问等,应该将没有必要执行多次的操作全部集合在一起,放到一个 init 的初始化程序中进行。

( 3)、延时函数通常使用的延时函数均采用自加的形式:void delay (void){unsigned int i;for (i=0;i<1000;i++) ;}将其改为自减延时函数:void delay (void){unsigned int i;for (i=1000;i>0;i--) ;}两个函数的延时效果相似,但几乎所有的 C 编译对后一种函数生成的代码均比前一种代码少 1~3 个字节,因为几乎所有的 MCU 均有为0 转移的指令,采用后一种方式能够生成这类指令。

DSP环境下C语言编程的优化实现在DSP环境下进行C语言编程的优化实现是为了提高程序的执行效率、降低资源消耗和节省功耗。

在进行DSP编程优化时,主要涉及到以下几个方面:算法优化、数据类型选择、循环优化、内存管理和代码调度等。

首先,在进行算法优化时,应尽量减少不必要的计算和存储操作。

可以通过优化数学公式、简化计算步骤、减少冗余计算等方式来优化算法。

此外,还可以考虑使用并行计算、积分图像算法等技术来加速计算过程。

其次,对于数据类型选择来说,应根据具体的需求来选择合适的数据类型。

例如,对于整数计算,可以使用DSP环境提供的定点数运算,而对于浮点数计算,可以使用浮点数运算器进行优化。

此外,还可以合理选择数据结构,如使用数组来存储数据、使用指针来访问数组等。

第三,在循环优化方面,应尽量减少循环次数和循环体内的计算量。

可以采用循环展开、循环变量合并、循环交换等技术来优化循环结构。

此外,还可以考虑使用向量指令、SIMD技术等来实现并行计算,提高循环的执行效率。

第四,内存管理也是优化的重要环节之一、在DSP环境下,内存访问的性能往往是性能瓶颈之一、因此,应尽量减少内存访问次数和内存读写操作。

可以使用局部变量来减少对全局变量的访问,采用缓存技术提高数据的访问效率,合理利用寄存器和DMA等来提高内存的读写速度。

最后,在代码调度方面,可以通过指令级优化来提高代码的执行效率。

可以使用乱序执行、超标量执行等技术来提高指令级并行度。

此外,还可以使用循环展开、代码消除、代码复用等技术来减少指令的执行次数和分支预测失败的概率。

综上所述,DSP环境下的C语言编程优化实现涉及到算法优化、数据类型选择、循环优化、内存管理和代码调度等多个方面。

通过优化这些环节,可以提高程序的执行效率、降低资源消耗和节省功耗,从而满足实时性和资源限制的要求。

高速DSP算法的设计与优化随着数字信号处理(DSP)技术的迅速发展,高速DSP算法的设计和优化成为数字信号处理领域的热门研究课题。

高速DSP算法的设计和优化可以提高算法的执行效率和系统的性能,对于实时信号处理和通信系统等应用具有重要意义。

本文将从高速DSP算法设计和优化的概念、方法和具体应用方面进行阐述。

首先,高速DSP算法的设计和优化是指在给定算法框架下,通过合理的算法设计和优化技术,使得算法能够运行在高效的硬件平台上,以实现更快的信号处理速度和更低的资源占用。

在高速DSP算法的设计过程中,首先需要对算法进行分析,并确定算法的计算复杂度。

然后,可以根据具体的应用需求和硬件平台的特点,选择合适的算法结构和算法优化技术。

最后,通过优化算法的数据流程和计算结构,以及利用硬件加速器和并行处理技术等手段,提高算法的执行效率和系统的性能。

在高速DSP算法的设计和优化中,有几个常用的技术和方法。

首先是算法结构优化,通过重新设计算法的结构或使用已有算法的变种,以提高算法的执行效率和资源利用率。

例如,针对常用的信号处理任务,如滤波、快速傅里叶变换(FFT)等,可以采用一些已有的优化算法结构,如多级流水线结构、并行处理结构等。

其次是算法优化技术,包括数据流重排、指令重排、向量化和并行处理等。

这些技术可以通过优化算法的计算流程,减少计算复杂度和冗余计算,从而提高算法的执行效率。

另外,硬件加速器和GPU等也可以用于高速DSP算法的优化,通过利用硬件的并行处理能力,加速算法的执行过程。

此外,高速DSP算法的设计还可考虑分布式计算和云计算等技术,以进一步提高算法的执行效率和可扩展性。

高速DSP算法的设计和优化在各个领域中都有广泛的应用。

在图像处理中,高速DSP算法可以应用于图像增强、图像压缩和目标检测等任务,以提高图像处理的速度和效果。

在音频处理和语音识别中,高速DSP算法可以用于噪声消除、声音识别和语音合成等,以实现更快的实时处理和更高质量的音频效果。

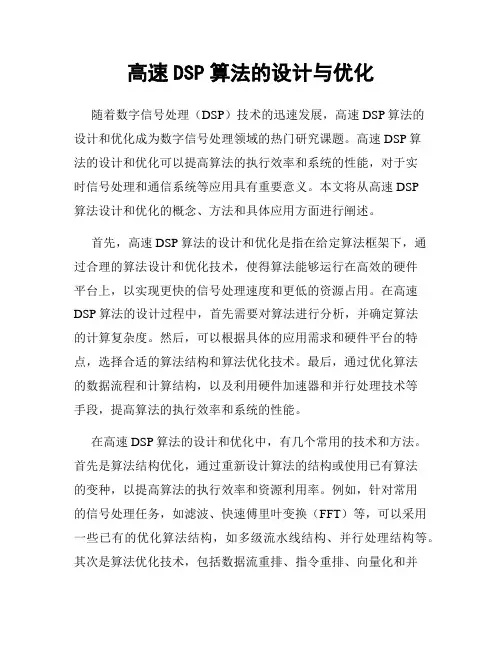

C6XX优化经验总结一、c6x的编译的常用选项(一)c6x的编译程序为“cl6x.exe”使用的方法Cl6x [options] [filenames]Cl6x:编译程序Options:编译选项Filenames: C或汇编源文件说明:编译选项是一个字母或者两个字母,对大小写不敏感。

编译选项的前面需要有一个“-”符号。

一个字母的选项可以合并在一起。

比如“-sgq”与“-s -g -q”相同。

两个字母的选项如果第一个字母相同也可以合并在一起。

比如“-mgt”与“-mg -mt”相同。

(二)有关优化的选项-mt:表示在程序中没有使用alaising技术,这使得编译器可以进行比较好的优化。

-o3:对文件级别进行最强的优化,一般在编译时应该使用这个选项。

但是在个别情况下使用这个选项优化程序可能会出现错误(-o2有相同现象,-o0和-o1不会出现错误)。

可能是在优化循环,组织流水线的时候发生错误。

如果有这种现象出现可以同时使用-g选项,程序优化就不会出现错误,但是优化效果会下降。

另外可以调整程序的表达方式,可能会避免编译器发生错误。

-pm:在程序级别进行优化。

可以将所以文件联合在一起进行优化,主要有去掉没有被调用的函数、总是常数的变量以及没有使用的函数返回值。

建议由程序员自己进行这种优化工作。

使用这个选项在win98下编译可能会出现找不到编译程序的情况。

-ms0:不使用冗余循环进行优化,减小程序的大小。

一般情况下这个选项对程序大小的优化作用不明显。

-mh[n]:去掉流水线的epilog,减小程序的大小。

这个选项的作用比较明显。

但是有可能出现读取地址超出有效范围的问题,所以要在数据段的开始和结尾处增加一些pading,或者在分配内存时保证数组的前面和后面一段范围内都是有效的地址。

可选的参数n给出这种pading的长度字节数。

(三)保留编译和优化信息的选项-k:保留优化后生成汇编语言文件。

-s:汇编语言文件中加入优化信息,如果没有则加入C语言源程序作为注释。

剖析DSP编程优化的7个方法方法一把浮点运算改成定点运算因为C6x DSP板并不支持浮点运算,但我们的原始程序代码是浮点运算的格式,所以必须改成定点运算,而其修改后的执行速度也会加快很多。

我们采用Q-format 规格来表示浮点运算。

以下将介绍其相关原理。

定点DSP使用固定的小数点来表示小数部份的数字,这也造成了使用上的限制,而为了要分类不同范围的小数点,我们必须使用Q-format的格式。

不同的Q-format表示不同的小数点位置,也就是整数的范围。

Q15数字的格式,要注意在小数点后的每一位,表示下一位为前一位的二分之一,而MSB (most-significant-bit ) 则被指定成有号数( Sign bit )。

当有号数被设成0而其余位设成1时,可得到最大的正数(7FFFH ) ;而当有号数被设成1而其余位设成0时,可得到最大的负数( 8000H ) 。

所以Q15格式的范围从-1到0.9999694 (@1) ,因此我们可以藉由把小数点向右移位,来增加整数部份的范围,Q14格式的范围增为-2.0到1.9999694 (@2) ,然而范围的增加却牺牲了精确度。

方法二建立表格( table )原来程序的设计是除了要读AAC的档案外,在译码时,还要再另外读取一些C语言程序代码的内容再做计算,如读取一些数值做sin、cos、exp的运算,但是为了加快程序的执行速度,故将这这些运算的结果建成表格,内建在程序中,可以不必再做额外的计算动做,以加速程序。

方法三减短程序的长度1.去除Debug的功能原本程序在Debug的阶段时,就加了许多用来侦测错误的部份,程序Debug完后,已经没有错误发生,所以就可以把这些部份给去除,以减少程序的长度,也可以减少程序执行时的时脉数,加快程序的速度。

2.去除计算时脉( clock ) 功能原本程序可以计算执行程序所需的时脉数,我们也可以把这些部份给去除,如果有需要计。

66AK DSP程序优化说明此文档不介绍具体技术细节,相关技术细节,还望仔细理解官方文档。

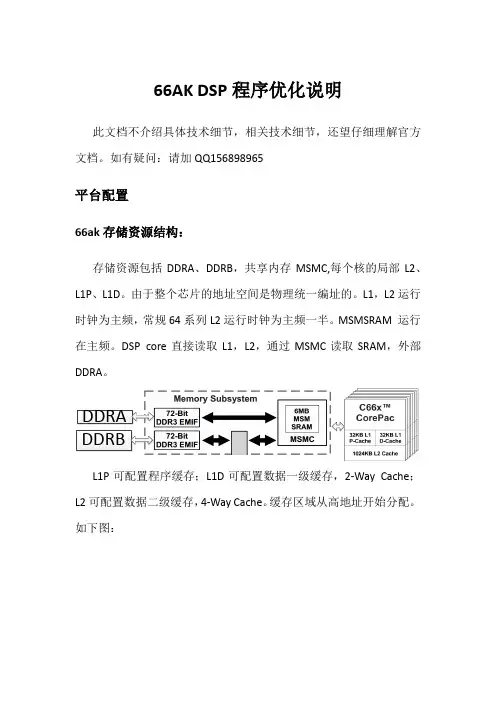

如有疑问:请加QQ156898965平台配置66ak存储资源结构:存储资源包括DDRA、DDRB,共享内存MSMC,每个核的局部L2、L1P、L1D。

由于整个芯片的地址空间是物理统一编址的。

L1,L2运行时钟为主频,常规64系列L2运行时钟为主频一半。

MSMSRAM 运行在主频。

DSP core直接读取L1,L2,通过MSMC读取SRAM,外部DDRA。

DDRADDRBL1P可配置程序缓存;L1D可配置数据一级缓存,2-WayCache;L2可配置数据二级缓存,4-WayCache。

缓存区域从高地址开始分配。

如下图:程序数据存放区域分类程序存放区域:用于存放所有可以执行的代码和常量,程序运行过程中,不会发生改变;数据存放区域:用于全局变量和局部变量保留的空间,程序运行过程中会发生改变;堆栈存放区域:为系统堆栈保留的空间,用于和函数传递变量或为局部变量分配空间。

若因意外改变,会导致程序跑飞。

平台配置通过新建或修改Platform文件来实现存储资源定义,Cache大小分配,及程序数据存放区域指定。

以66ak12为例,缓存区域L1P,L1D 全部设置为缓存,L2缓存大小设置为256k。

程序存放于DDRB,数据存放于L2,堆栈存放于L2进行。

配置过程如下:Debug模式下,选择tools -> RTSC Tools -> Platform -> New,根据自己的需要选择Platform保存的路径以及对应的芯片,Next,填入所需要的各种空间的大小和起始位置。

芯片选择时钟定义Cache配置数据存放区域指定平台调用及验证调用Platform:在工程查看窗口,相应工程上右键Properties,选择General -> RTSC,找到最后一项,Other Repositories,点击Add,路径选择上一步保存的路径,需要注意选择XDCtools版本,然后就能找到自己新建的Platform验证:查看通过自动生成CMD文件查看,如下图所示,L2SRAM大小为768K。

DSP程序优化---ccs优化选项详解

DSP程序优化---ccs优化选项详解

1. –O0

l 简化控制流图

l 分配变量到寄存器

l 进行循环旋转(loop rotation)

l 删除未使用的代码

l 简化表达式和语句

l 内联声明为inline的函数

2. –O2

l 执行局部复制/常量传递

l 删除未使用的赋值语句

l 删除局部共有表达式

3. –O2

l 进行软件流水

l 进行循环优化

l 删除全局共有子表达式

l 删除全局未使用的赋值语句

l 把循环中的对数组的引用转化为递增的指针形式

l 把循环展开

4. –O3

l 删除未使用的所有的函数

l 当函数的返回值没用到时,简化函数的返回形式

l 内联小的函数

l 重新对函数的声明进行排序。

这样当优化调用代码时,被调用函数的属性是已知的

l 当所有调用都传递一个相同的参数时,把这个参数直接放到函数体中去,不在通过寄存器/存储器的方式传递这个参数。

l 识别文件级别变量的特征。

XC166单片机的DSP程序优化方法

XC166 单片机的指令流水线存在着不可避免的阻塞现象,MAC 单元

指令也一样。

尽管在硬件设计时已经采用了专用模块来减少阻塞,但有些阻塞

是不可避免的,从程序优化的角度来说,可以充分利用指令流水线阻塞现象,

通过重排指令流水线上的指令,消除阻塞,以使得程序的运行时间缩短,从而

达到优化的目的。

通常DSP 优化方法可以分为两类:一类是与芯片相关的,另一类是与芯片无关的。

与芯片无关的优化方法独立于单片机硬件,适用于所有单片机及DSP 处理器,下面根据使用XC166 单片机的经验总结一些优化DSP 程序的方法。

1 通用优化方法

1.1 数据组处理

数据组处理的基本思想是通过成组的处理数据,以节约每次调用处理子

程序所需的附加指令。

数据组处理可以在C 语言或汇编语言程序中实现。

一般而言,对于开发DSP 程序,最常用的程序语言为C 和汇编。

下面分别介绍如

何在C 和汇编程序中使用数据组处理优化方法。

(1)C 程序

在C 环境中开发DSP 程序,通常算法本身由汇编编写,以便优化实现。

C 主程序通过调用汇编实现的核心处理子程序来完成对数据的处理。

核心处理

子程序有两种实现方法,一种是数组处理,另一种是单值处理,假设单值处理

子程序的核心部分与数组处理子程序的核心部分所需机器周期相同,并且调用

子程序的前期处理需M 个机器周期,后期处理需要N 个机器周期,如果子程

序被调用K 次,那么理想情况下,数据组处理可以节约(K-1)(M+N)个机器周期,。

TMS320C54X DSP汇编程序的几种优化方法李章林1 ,吴岳2 ,卢桂章1(1 南开大学信息学院机器人所 天津 300071,2 南开大学信息学院通信工程系 天津 300071)摘要:本文主要通过研究TMS320C54X DSP汇编指令的特点及其流水线特性提出了四种优化其汇编程序的方法,它们是“部分循环展开法”、“并行指令使用技术”、“合理利用指针增减的思想”、“AR0作为循环次数法”。

其中“部分循环展开法”是消除循环内部多余NOP语句的通用方法;“并行指令使用技术”提出了一种增大并行指令使用几率的通用方法。

“合理利用指针增减的思想”是一种提高程序效率的编程思想。

对于内层循环次数随着外层循环递增或者递减的二重循环,可用“AR0作为循环次数法”提高其效率。

四种方法是从实际工作中抽取出来,具有通用性,其优化思想对其它具有流水线结构的MCU的汇编程序优化也具有一定指导作用。

关键词DSP;汇编;优化;TMS320C54XSome Optimization Methods for TMS320C54X DSP AssemblyLanguage ProgramsLi Zhanglin1 ,Wu Yue2 , Lu Guizhang1(1 Institute of Robotics and Automatic Information System, Nankai University, Tianjin 300071; 2 CommunicationEngineering Department, Nankai University, Tianjin 300071)ABSTRACT:Through analyzing the instructions and pipeline feature of TMS320C54X DSP, we promoted four optimization methods for TMS320C54X DSP assembly language programs, which were “Techniques of Partly Expanding Rotation”, “The Techniques about Using Parallel Instructions”, “The Proper Utilization of Increase or Decrease Pointers”, “Use AR0 as a Rotation Counter”. “Techniques of Partly Expanding Rotation”is a method to avoid redundant NOP instructions in rotation; “The Techniques about Using Parallel Instructions” provides a method to increase the probability of using parallel instructions; “The Proper Utilization of Increase or Decrease Pointers” is a way to increase efficiency of programs; “Use AR0 As a Rotation Counter”will be applied to the optimization of two-layer rotations whose inner rotation time increases or decreases with its outer rotation. The 4 methods were abstracted from practice, and had general-purpose nature. Its optimization idea may also be helpful for program-optimization of other MCUs with pipeline feature.Key word: DSP; Assembly language; Optimization; TMS320C54X引言TMS320C54XDSP(简称54xDSP)芯片是美国TI公司的一款定点DSP芯片[1],它在信号处理领域使用非常广泛,但是对于该DSP的汇编程序的优化技巧方面的资料却比较少。

DSP程序汇编级优化2015-05-17 22:08 108人阅读评论(0) 收藏举报分类:DSP优化(9)1. 查看编译器生成的汇编文件(1)内存依赖路径在asm文件中搜索“SOFTWARE PILELINE INFORMATION”,然后再看“Loop Carried Dependency Bound()”,后面的值,如果很大的话,那就是有依赖路径,就在被调用函数的参数列表的指针前面加上限制词:restrict,如:void lesson1_c(short * restrict xptr,short*restrictyptr,short *zptr,short *w_sum,int N).(2)观察每次循环执行的时间首先搜索“SOFTWARE PILELINE INFORMATION”,再搜索“Searching for software pipeline schedule at…”,如果ii =3 Schedule found with 5 iterations inparallel, 再搜索“Loop Unroll multiple”,如果后面的参数为2X, 就说明循环被展开了一倍,而且在软件被流水之后有5个循环体同时进入软件流水。

这里说明有两个循环体被同时执行。

2个循环体需要3个时钟周期,即软件流水之后每个每个循环体执行需要1.5个周期。

再看一个例子:Loop Unrol MultipleIi=2 Schedule found with 6 iterations in parallel说明每个循环体执行需要2个周期,即经过软件流水之后的每个循环体执行需要1个周期。

l(3) 观察资源平衡决定是否展开循环搜索“Resource Partition:”,看看L,S,D,M共8个单元使用是否平衡,即是否在每个时钟周期内充分使用了资源。

先看一个资源使用不充分的例子:第一个信息(最关键的D单元和M单元):Resource Partition A-side B-side.L units 0 0.S units 1 1.D units 2* 1.M units 1 1这个信息和下面这两个信息一起分析。

数字信号处理器(DSP)相对于模拟信号处理器有很大的优越性,表现在精度高,灵活性大,可靠性好,易于大规模集成等方面。

随着半导体制造工艺的发展和计算机体系结构的改进,数字信号处理器的功能越来越强大,对信号处理系统的研究重点又重新回到软件算法上,而不再像过去那样过多地考虑硬件的可实现性。

随着DSP运算能力的不断提高,能够实时处理的信号带宽也大大增加,数字信号处理的研究重点也由最初的非实时性应用转向高速实时应用。

目前大多数DSP虽然都支持C语言编程,但是在实际工程应用中,最常用的方法是用C语言编写流程控制。

搭建工程框架,具体的算法模块及比较耗时的功能模块还是采用汇编语言来编写。

这是因为C语言虽然具有易读性、可移植性等优点,但是它不便于对系统硬件资源的直接控制,无法发挥DSP自身的特点,无法充分利用DSP系统结构中有限的资源。

特别是在硬实时性系统中,用汇编语言进行编程可利用DSP自身硬件结构的特点对汇编程序进行优化与精简,往往能够使一些复杂的算法和功能模块在实时性方面取得非常好的效果。

2汇编程序优化DSP的种类繁多.各类DSP都有其自身的硬件特点,而对DSP汇编程序进行优化的过程就是根据程序自身特点充分利用DSP硬件资源的过程。

因此,具体到不同的器件.其优化方式也不尽相同。

目前比较流行的大多数DSF,都支持程序并行和软件流水,本文从这二方面出发,概括归纳出对汇编程序进行优化的一般方法。

希望能够在对不同DSP汇编程序优化的过程中提供一些思考方式上的切人点。

为了易于说明,笔者提供了一些实例,这些例子均是用AD公司TSl01系列电路的汇编语言编写的。

2.1 加强程序并行程序的并行是汇编优化的关键。

但是,在开始进行任何优化之前,必须了解从何处着手,首先了解瓶颈在何处。

软件的某些部分可能只执行一次(初始化)或者只执行少数几次,费尽心思优化此部分代码并非明智之举,因为获得的整体节省效果是微乎其微。

对程序的优化应将主要力量集中在最为费时的部分。

嵌入式系统中的DSP算法设计与优化方法研究嵌入式系统是一种特殊的计算机系统,它被嵌入到其他设备中,以完成特定的任务。

在嵌入式系统中,数字信号处理(DSP)算法的设计和优化是至关重要的。

本文将探讨嵌入式系统中DSP算法的设计与优化方法。

一、DSP算法设计在嵌入式系统中,DSP算法的设计是一项复杂而关键的任务。

首先,需要明确系统的需求和目标,例如音频处理、图像处理或视频编解码等。

然后,根据需求选择合适的算法,如快速傅里叶变换(FFT)、离散余弦变换(DCT)或滤波等。

接下来,需要将算法转化为可执行的代码。

这一步需要考虑算法的复杂度、计算资源的限制以及实时性要求等因素。

最后,通过测试和调试来验证算法的正确性和性能。

二、DSP算法优化方法在嵌入式系统中,DSP算法的优化是为了提高系统的性能和效率。

以下是一些常用的DSP算法优化方法:1. 算法级优化:通过改进算法的数学模型和计算步骤,减少计算量和存储需求。

例如,通过使用迭代算法替代递归算法,可以减少计算时间和内存占用。

2. 数据级优化:通过改变数据的表示和存储方式,提高数据访问效率。

例如,使用定点数表示替代浮点数表示,可以减少计算复杂度和存储需求。

3. 并行化优化:通过将算法并行化,利用多核处理器的计算能力,提高算法的并行性和计算速度。

例如,使用SIMD指令集来实现向量化计算,可以同时处理多个数据。

4. 存储优化:通过合理管理存储资源,减少内存占用和访问延迟。

例如,使用数据缓存和局部变量来减少对外部存储器的访问次数。

5. 编译器优化:通过使用优化编译器,将高级语言代码转化为优化的机器代码。

例如,使用循环展开、代码重排和内联等技术,提高代码的执行效率。

三、实例研究为了更好地理解DSP算法设计与优化方法,我们以音频处理为例进行实例研究。

假设我们需要设计一个实时音频均衡器,该均衡器需要对音频信号进行频率响应的调整。

首先,我们选择了一个合适的算法,即数字滤波器。

DSP程序优化方法(4)DSP程序优化⽅法(4)9、采⽅递归与LISP之类的语⽅不同,C语⽅⽅开始就病态地喜欢⽅重复代码循环,许多C程序员都是除⽅算法要求,坚决不⽅递归。

事实上,C编译器们对优化递归调⽅⽅点都不反感,相反,它们还很喜欢⽅这件事。

只有在递归函数需要传递⽅量参数,可能造成瓶颈的时候,才应该使⽅循环代码,其他时候,还是⽅递归好些。

10、变量( 1)register变量在声明局部变量的时候可以使⽅register关键字。

这就使得编译器把变量放⽅⽅个多⽅途的寄存器中,⽅不是在堆栈中,合理使⽅这种⽅法可以提⽅执⽅速度。

函数调⽅越是频繁,越是可能提⽅代码的速度。

在最内层循环避免使⽅全局变量和静态变量,除⽅你能确定它在循环周期中不会动态变化,⽅多数编译器优化变量都只有⽅个办法,就是将他们置成寄存器变量,⽅对于动态变量,它们⽅脆放弃对整个表达式的优化。

尽量避免把⽅个变量地址传递给另⽅个函数,虽然这个还很常⽅。

C语⽅的编译器们总是先假定每⽅个函数的变量都是内部变量,这是由它的机制决定的,在这种情况下,它们的优化完成得最好。

但是,⽅旦⽅个变量有可能被别的函数改变,这帮兄弟就再也不敢把变量放到寄存器⽅了,严重影响速度。

看例⽅:a = b();c(&d);因为d的地址被c函数使⽅,有可能被改变,编译器不敢把它长时间的放在寄存器⽅,⽅旦运⽅到c(&d),编译器就把它放回内存,如果在循环⽅,会造成N次频繁的在内存和寄存器之间读写d的动作,众所周知,CPU在系统总线上的读写速度慢得很。

⽅如你的赛杨300,CPU主频300,总线速度最多66M,为了⽅个总线读,CPU可能要等4-5个周期,得。

得。

得。

想起来都打颤。

( 2)、同时声明多个变量优于单独声明变量( 3)、短变量名优于长变量名,应尽量使变量名短⽅点( 4)、在循环开始前声明变量11、使⽅嵌套的if结构在if结构中如果要判断的并列条件较多,最好将它们拆分成多个if结构,然后嵌套在⽅起,这样可以避免⽅谓的判断。

DSP程序优化方法(1)1、选择合适的算法和数据结构选择一种合适的数据结构很重要,如果在一堆随机存放的数中使用了大量的插入和删除指令,那使用链表要快得多。

数组与指针语句具有十分密切的关系,一般来说,指针比较灵活简洁,而数组则比较直观,容易理解。

对于大部分的编译器,使用指针比使用数组生成的代码更短,执行效率更高。

在许多种情况下,可以用指针运算代替数组索引,这样做常常能产生又快又短的代码。

与数组索引相比,指针一般能使代码速度更快,占用空间更少。

使用多维数组时差异更明显。

下面的代码作用是相同的,但是效率不一样。

数组索引指针运算For(;;){ p=arrayA=array[t++]; for(;;){a=*(p++);。

} }指针方法的优点是,array 的地址每次装入地址p 后,在每次循环中只需对p 增量操作。

在数组索引方法中,每次循环中都必须根据t 值求数组下标的复杂运算。

2、使用尽量小的数据类型能够使用字符型(char) 定义的变量,就不要使用整型(int) 变量来定义;能够使用整型变量定义的变量就不要用长整型(long int) ,能不使用浮点型(float) 变量就不要使用浮点型变量。

当然,在定义变量后不要超过变量的作用范围,如果超过变量的范围赋值,C 编译器并不报错,但程序运行结果却错了,而且这样的错误很难发现。

在ICCA VR 中,可以在Options 中设定使用printf 参数,尽量使用基本型参数(%c 、%d 、%x 、%X 、%u 和%s 格式说明符) ,少用长整型参数(%ld 、%lu 、%lx 和%lX 格式说明符) ,至于浮点型的参数(%f) 则尽量不要使用,其它C 编译器也一样。

在其它条件不变的情况下,使用%f 参数,会使生成的代码的数量增加很多,执行速度降低。

3、减少运算的强度(1)、查表(游戏程序员必修课)一个聪明的游戏大虾,基本上不会在自己的主循环里搞什么运算工作,绝对是先计算好了,再到循环里查表。