教案MOS构成基本逻辑门电路

- 格式:docx

- 大小:28.53 KB

- 文档页数:4

MOS管及简单CMOS逻辑门电路原理图现代单片机主要是采用C MOS工艺制成的。

1、MOS管 MOS管又分为两种类型:N型和P型。

如下图所示:以N型管为例,2端为控制端,称为“栅极”;3端通常接地,称为“源极”;源极电压记作Vss,1端接正电压,称为“漏极”,漏极电压记作VDD。

要使1端与3端导通,栅极2上要加高电平。

对P型管,栅极、源极、漏极分别为5端、4端、6端。

要使4端与6端导通,栅极5要加低电平。

在CMOS工艺制成的逻辑器件或单片机中,N型管与P型管往往是成对出现的。

同时出现的这两个CMO S2、CMOS逻辑电平高速CMOS电路的电源电压VDD通常为+5V;Vss接地,是0V。

高电平视为逻辑“1”,电平值的范围为:VDD的65%~VDD(或者VDD-1.5V~VDD)低电平视作逻辑“0”,要求不超过V DD的35%或0~1.5V。

+1.5V~+3.5V应看作不确定电平。

在硬件设计中要避免出现不确定电平。

近年来,随着亚微米技术的发展,单片机的电源呈下降趋势。

低电源电压有助于降低功耗。

VDD为3.3V的CMO S器件已大量使用。

在便携式应用中,VDD为2.7V,甚至1.8V的单片机也已经出现。

将来电源电压还会继续下降,降到0.9V,但低于VDD的35%的电平视为逻辑“0”,高于VDD的65%的电平视为逻辑“1”的规律仍然是适用的。

3、非门非门(反向器)是最简单的门电路,由一对CMO S管组成。

其工作原理如下:A端为高电平时,P型管截止,N型管导通,输出端C的电平与Vss保持一致,输出低电平;A端为低电平时,P型管导通,N型管截止,输出端C的电平与VDD一致,输出高电平。

4、与非门与非门工作原理:①、A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与V DD 一致,输出高电平。

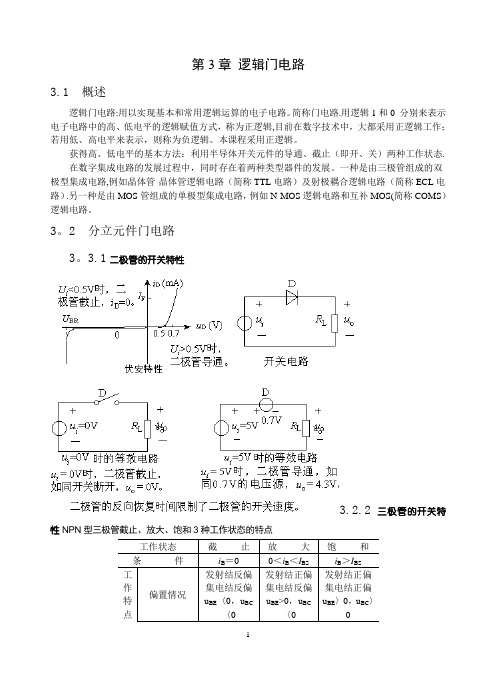

第3章逻辑门电路3.1 概述逻辑门电路:用以实现基本和常用逻辑运算的电子电路。

简称门电路.用逻辑1和0 分别来表示电子电路中的高、低电平的逻辑赋值方式,称为正逻辑,目前在数字技术中,大都采用正逻辑工作;若用低、高电平来表示,则称为负逻辑。

本课程采用正逻辑。

获得高、低电平的基本方法:利用半导体开关元件的导通、截止(即开、关)两种工作状态.在数字集成电路的发展过程中,同时存在着两种类型器件的发展。

一种是由三极管组成的双极型集成电路,例如晶体管-晶体管逻辑电路(简称TTL电路)及射极耦合逻辑电路(简称ECL电路).另一种是由MOS管组成的单极型集成电路,例如N-MOS逻辑电路和互补MOS(简称COMS)逻辑电路。

3。

2 分立元件门电路3。

3.1二极管的开关特性3.2.2三极管的开关特性NPN型三极管截止、放大、饱和3种工作状态的特点工作状态截止放大饱和条件i B=0 0<i B<I BS i B>I BS工作特点偏置情况发射结反偏集电结反偏u BE〈0,u BC〈0发射结正偏集电结反偏u BE>0,u BC〈0发射结正偏集电结正偏u BE〉0,u BC〉集电极电流i C=0 i C=βi B i C=I CSce间电压u CE=V CC u CE=V CC-i C R cu CE=U CES=0.3Vce间等效电阻很大,相当开关断开可变很小,相当开关闭合3.2。

3二极管门电路1、二极管与门2、二极管或门u A u B u Y D1D20V 0V 0V 5V 5V 0V 5V 5V0V4。

3V4。

3V4.3V截止截止截止导通导通截止导通导通3。

2.4三极管非门3。

2。

5组合逻辑门电路1、与非门电路2、或非门电路3.3 集成逻辑门电路一、TTL与非门1、电路结构(1)抗饱和三极管作用:使三极管工作在浅饱和状态。

因为三极管饱和越深,其工作速度越慢,为了提高工作速度,需要采用抗饱和三极管。

构成:在普通三极管的基极B和集电极C之间并接了一个肖特基二极管(简称SBD)。

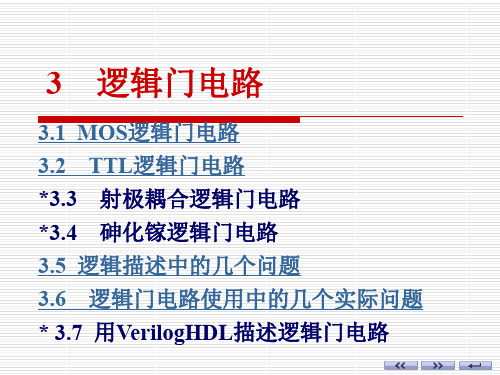

3逻辑门电路3.1 MOS逻辑门电路3.2TTL逻辑门电路*3.3射极耦合逻辑门电路*3.4砷化镓逻辑门电路3.5逻辑描述中的几个问题3.6逻辑门电路使用中的几个实际问题* 3.7用VerilogHDL描述逻辑门电路3.逻辑门电路教学基本要求:1.了解半导体器件的开关特性。

2.熟练掌握基本逻辑门(与、或、与非、或非、异或门)、三态门、OD门(OC门)和传输门的逻辑功能。

3.学会门电路逻辑功能分析方法。

4.掌握逻辑门的主要参数及在应用中的接口问题。

3.1 MOS逻辑门3.1.1数字集成电路简介3.1.2逻辑门的一般特性3.1.3MOS开关及其等效电路3.1.4CMOS反相器3.1.5CMOS逻辑门电路3.1.6CMOS漏极开路门和三态输出门电路3.1.7CMOS传输门3.1.8CMOS逻辑门电路的技术参数1 . 逻辑门:实现基本逻辑运算和复合逻辑运算的单元电路。

2. 逻辑门电路的分类二极管门电路三极管门电路 TTL 门电路MOS 门电路 PMOS 门 CMOS 门逻辑门电路分立门电路集成门电路NMOS 门 3.1.1 数字集成电路简介1.CMOS 集成电路:广泛应用于超大规模、甚大规模集成电路4000系列 74HC 74HCT 74VHC 74VHCT 速度慢与TTL 不兼容 抗干扰 功耗低74LVC 74VAUC 速度加快 与TTL 兼容 负载能力强 抗干扰 功耗低速度两倍于74HC 与TTL 兼容 负载能力强 抗干扰 功耗低低(超低)电压 速度更加快 与TTL 兼容 负载能力强 抗干扰功耗低74系列74LS 系列74AS 系列74ALS2.TTL 集成电路:广泛应用于中、大规模集成电路3.1.1 数字集成电路简介3.1.2 逻辑门电路的一般特性1. 输入和输出的高、低电平v O v I 驱动门 G 1负载门 G 2 11 输出高电平的下限值 V OH(min)输入低电平的上限值V IL(max)输入高电平的下限值V IL(min) 输出低电平的上限值 V OH(max)输出高电平+ V D D V O H ( m in )V O L ( m ax )G 1 门 v O 范围v O输出低电平输入 高电平 V I H ( m in ) V I L ( m ax )+ V D D 0 G 2 门 v I范围 输入低电平v IV NH —当前级门输出高电平的最小值时允许负向噪声电压的最大值。

半导体物理mos结构课程设计一、课程目标知识目标:1. 理解半导体的基本性质,掌握半导体材料的分类及特点。

2. 学习MOS(金属-氧化物-半导体)结构的原理,了解其工作方式和应用领域。

3. 掌握MOS电容的特性,了解其在集成电路中的作用。

技能目标:1. 能够运用所学知识分析半导体器件的基本原理。

2. 学会使用相关软件或仪器进行MOS结构的模拟和测试,提高实践操作能力。

3. 能够运用所学知识解决实际问题,培养创新思维和团队合作能力。

情感态度价值观目标:1. 培养学生对半导体物理的兴趣,激发学生探索科学的精神。

2. 增强学生的环保意识,认识到半导体技术在可持续发展中的重要性。

3. 培养学生的团队协作精神,提高沟通与表达能力。

课程性质:本课程为高二年级物理选修课程,以理论教学和实践操作相结合的方式进行。

学生特点:高二学生已具备一定的物理知识基础,具有较强的逻辑思维能力和动手操作能力。

教学要求:结合学生特点,注重理论与实践相结合,提高学生的实际操作能力和解决问题的能力。

通过课程学习,使学生能够达到上述课程目标,为后续相关课程打下坚实基础。

二、教学内容1. 半导体物理基础:包括半导体的基本性质、能带理论、杂质和缺陷等概念,重点讲解半导体材料的分类及特点。

教材章节:第一章《半导体物理基础》2. MOS结构原理:介绍MOS结构的组成、工作原理及其在集成电路中的应用。

教材章节:第三章《金属-氧化物-半导体(MOS)结构》3. MOS电容特性:分析MOS电容的C-V特性、阈值电压等参数,探讨其在集成电路中的作用。

教材章节:第三章《金属-氧化物-半导体(MOS)结构》4. 实践操作:利用相关软件或仪器进行MOS结构的模拟和测试,观察MOS 电容的特性,培养学生动手能力和实践操作技能。

教学安排与进度:1. 第一周:半导体物理基础(2课时)2. 第二周:MOS结构原理(2课时)3. 第三周:MOS电容特性(2课时)4. 第四周:实践操作(2课时)教学内容确保科学性和系统性,注重理论与实践相结合,通过以上教学安排,使学生全面掌握半导体物理及MOS结构的相关知识。

教案MOS构成基本逻辑门电路一、教学目标1.理解MOS管的基本工作原理;2.掌握MOS管构成基本逻辑门电路的方法;3.能够设计和组装MOS管构成的基本逻辑门电路;4.掌握基本逻辑门电路的真值表和运算规律。

二、教学重点1.MOS管的基本工作原理;2.MOS管构成基本逻辑门电路的方法;3.基本逻辑门电路的真值表和运算规律。

三、教学难点1.MOS管的基本工作原理;2.基本逻辑门电路的真值表和运算规律的理解。

四、教学准备1.已学习过MOS管的基本知识;2.准备好教材、实验器材和实验电路板。

五、教学步骤1.复习MOS管的基本工作原理。

2.引导学生了解MOS管构成基本逻辑门电路的方法。

-构成与门电路:将N沟道MOS管的漏极连接到电源VDD,源极接地,输入信号经过电阻连接到栅极,输出信号从漏极输出。

-构成或门电路:将P沟道MOS管的漏极连接到电源VDD,源极接地,输入信号经过电阻连接到栅极,输出信号从漏极输出。

-构成非门电路:将N沟道MOS管的漏极连接到电源VDD,源极接地,输入信号经过电阻连接到栅极,输出信号从漏极输出。

-构成与非门电路:将P沟道MOS管的漏极连接到电源VDD,源极接地,输入信号经过电阻连接到栅极,输出信号从漏极输出。

3.演示MOS管构成基本逻辑门电路的过程。

-将N沟道MOS管和P沟道MOS管按照逻辑门的要求连接到电源和地,输入信号连接到栅极,输出信号从漏极输出。

4.学生自己动手制作MOS管构成的基本逻辑门电路。

5.分组进行实验。

-组员分别负责制作不同的基本逻辑门电路。

-测试各组制作的电路是否正常工作。

6.总结基本逻辑门电路的真值表和运算规律。

-给学生阐述并总结与门电路、或门电路、非门电路和与非门电路的真值表和运算规律。

七、教学效果反馈1.学生完成实验报告。

2.学生进行课堂讨论。

-学生分享自己制作基本逻辑门电路的经验和心得。

八、教学延伸1.完成扩展实验设计。

-学生自行设计并制作其他逻辑门电路。

上一讲内容回顾:

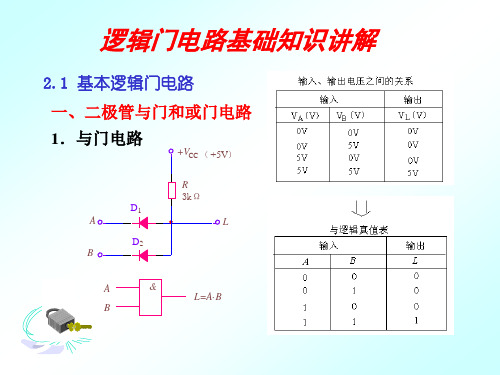

二极管与门及或门

二极管与门

二极管或门

NPN型三极管反相器电路非门及工作原理

二极管和三极管构成与非门及或非门

V DD

u i

u o

R D

→u u

i

A

o

Y

A

Y

电压关系表

u

I

/V u O/V

0V

DD

V

DD

真值表

1

1

A Y

3. 分立元件二极管和MOS管构成与非及或非门

4. CMOS集成逻辑门电路

一.CMOS反相器工作原理

当NMOS管和PMOS管成对出现在电路中,且二者在工作中互补,称为CMOS管;

基本电路组成与工作原理

电压传输特性和电流传输特性

AB段:u I<U thN,T N截止、T P导通,u O=V DD、i D0,功耗极小;

BC段:u I>U thN,T N开始导通,u O略下降;

CD段:u I=0.5V DD,T N、T P均导通,u O↓→i D↑=i Dmax;

DE、EF段:与BC、AB段对应,且T N、T P的状态与之相

反,T N截止→导通;T P导通→截止;

输入端噪声容限

在保证电路输出高或低电平为规定值的条件下,前一个门的输出作为后一个门的输入,其电平的允许波动的最大范围称为输入端噪声容限;

CMOS反相器的静态输入输出特性

①输入特性

因为MOS管的栅极和衬底之间存在着以SiO2为介质的输入电容,而绝缘介质非常薄,极易被击穿,所以应采取保护措施;

以74HC输入端保护电路输入特性为例介绍

在正常的输入信号范围内,即–0.7V<v I<V DD+0.7V,输入电流i I≈0;

在–0.7V~V DD+0.7V以外的区域,保护电路中的二极管已进入导通状态;

二极管导通时也限制了电容两端电压的增加,这非常利于提高工作速度;

注意:由于门电路输入端的的输入阻抗极高,若有静电感应会在悬空的输入端产生不定的电位,故CMOS门电路的输入端不允许悬空;

②输出特性

输出低电平V OL时

输出高电平V OH时

考虑到芯片功耗发热等因素74HC系列CMOS门最大输出电流±4mA;

CMOS反相器的动态特性

①传输延迟时间

②交流噪声容限

噪声电压作用时间越短、电源电压越高,交流噪声容限越大;

③动态功耗

反相器从一种稳定状态突然变到另一种稳定状态的过程中,将产生附加的功耗,即为动态功耗;

PMOS、NMOS同时导通所消耗的瞬时导通功耗P T

负载电容充放电所消耗的功率P C

结论:为减小功耗需要减小C L、V DD和f,特别是需要减小V DD;与动态功耗相比,静态时总有一个管子处于夹断状态,故功耗极小,可忽略不计;。