Verilog HDL 之 顺序脉冲发生器

- 格式:doc

- 大小:16.00 KB

- 文档页数:2

1.简单门电路的设计二输入与非门module nand_2(y,a,b);output y;input a,b;nand(y,a,b);endmodule二输入异或门module nand_2(y,a,b);output y;input a,b;reg y;always @(a,b)begincase({a,b})2’b00:y=1;2’b01:y=1;2’b10:y=1;2’b11:y=0;default:y=’bx;endcaseendendmodule二输入三态门module eda_santai(dout,din,en); output dout;input din,en;reg dout;alwaysif (en) dout<=din;else dout<=’bz;endmodule3-8译码器的设计module yimaqi(S1,S2,S3,A,Y); input S1;wire S1;input S2;wire S2;input S3;wire S3;input [2:0]A;wire [2:0]A;output[7:0]Y;reg [7:0]Y;reg s;always@(S,S1,S2,S3)begins<=S2|S3;Y <=8'b1111_1111;else if(S)Y <=8'b1111_1111;elsecase(A)3'b000:Y<=11111110;3'b001:Y<=11111101;3'b010:Y<=11111011;3'b011:Y<=11110111;3'b100:Y<=11101111;3'b101:Y<=11011111;3'b110:Y<=10111111;3'b111:Y<=01111111;endcaseendendmodule2.8-3编码器的设计module banjiaqi(a,b,count,sum);input a;wire a;input b;wire b;output count;wire count;output sum;wire sum;assign {count,sum}=a+b;endmodule4. D触发器的设计module Dchufaqi ( Q ,CLK ,RESET ,SET ,D ,Qn ); input CLK ;wire CLK ;input RESET ;wire RESET ;input SET ;wire SET ;input D ;wire D ;output Q ;reg Q ;output Qn ;wire Qn ;assign Qn = ~Q ;always @ ( posedge CLK or negedge SET or negedge RESET ) beginif ( !RESET)Q <= 0 ;else if ( ! SET)Q <= 1;else Q <= D;endendmodule5. 1位半加法器的设计module banjiafaqi(a,b,sum,count);input a;wire a;input b;wire b;output sum;wire sum;output count;wire count;assign {count,sum}=a+b;endmodule6. 4位计数器的设计module sihisjishuqi(CLK,RESET,out);input CLK;wire CLK;input RESET;wire RESET;output[3:0] out;reg[3:0] out;always @ ( posedge CLK or negedge RESET )beginif(!RESET)out<=4'b0000;elsebeginout<=out+1;if(out==4'b1010)out<=4'b0000;endendendmodule7.分频时序逻辑电路的设计module eda_fp_even(clk_out,clk_in,rst); input clk_in;input rst;wire rst;output clk_out;reg clk_out;reg [1:0]cnt;parameter N=6;always @(posedge clk_in or negedge rst) beginif(!rst)beginclk_out<=0;cnt<=0;endelsebegincnt<=cnt+1;if(cnt==N/2-1)beginclk_out=!clk_out;cnt<=0;endendendendmodule8.7段显示译码器的设计module eda_scan_seven(clk,dig,y,rst); input clk;wire clk;input rst;wire rst;output[7:0] dig;wire[7:0] dig;output [7:0]y;wire [7:0]y;reg clkout;reg [19:0]cnt;reg [2:0]wei;reg [3:0]duan;reg [6:0]Y_r;reg [7:0]dig_r;assign y = {1'b1,(~Y_r[6:0])};assign dig =~dig_r;parameter period= 1000000;always@(posedge clk or negedge rst) beginif(!rst)cnt<=0;else begincnt<=cnt+1;if(cnt==(period>>1)-1)clkout<=#1 1'b1;else if(cnt==period-1)beginclkout<=#1 1'b0;cnt<=#1 1'b0;endendendalways@(posedge clkout or negedge rst ) beginif(!rst)wei<=0;elsewei<=wei+1;endalways @(wei) //数码管选择begincase ( wei )3'b000 :begindig_r <= 8'b0000_0001;duan <= 1;end3'b001 :begindig_r <= 8'b0000_0010;duan<= 3;end3'b010 :begindig_r <= 8'b0000_0100;duan<= 5;end3'b011 :begindig_r <= 8'b0000_1000;duan <= 7;end3'b100 :begindig_r <= 8'b0001_0000;duan<= 9;end3'b101 :begindig_r <= 8'b0010_0000;duan<= 11;end3'b110 :begindig_r <= 8'b0100_0000;duan <= 13;end3'b111 :begindig_r <= 8'b1000_0000;duan<= 15;endendcaseendalways @ ( duan ) //译码begincase ( duan )0: Y_r = 7'b0111111; // 01: Y_r = 7'b0000110; // 12: Y_r = 7'b1011011; // 23: Y_r = 7'b1001111; // 34: Y_r = 7'b1100110; // 45: Y_r = 7'b1101101; // 56: Y_r = 7'b1111101; // 67: Y_r = 7'b0100111; // 78: Y_r = 7'b1111111; // 89: Y_r = 7'b1100111; // 910: Y_r = 7'b1110111; // A11: Y_r = 7'b1111100; // b12: Y_r = 7'b0111001; // c13: Y_r = 7'b1011110; // d14: Y_r = 7'b1111001; // E15: Y_r = 7'b1110001; // Fdefault: Y_r = 7'b0000000;endcaseendendmodule9.数据选择器的设计module eda_8xuanyi (A,D0,D1,D2,D3,D4,D5,D6,D7,G,Y); input D0,D1,D2,D3,D4,D5,D6,D7,G;input [2:0]A;wire [2:0]A;output Y;reg Y;always @(A, G)beginif (G==0)Y<=0;elsecase(A)3'b000:Y=D0;3'b001:Y=D1;3'b010:Y=D2;3'b011:Y=D3;3'b100:Y=D4;3'b101:Y=D5;3'b110:Y=D6;3'b111:Y=D7;endcaseendendmodule10.数据锁存器的设计module e da_suocunqi(q,d,oen,g); output[7:0] q;//数据输出端input[7:0] d;//数据输入端input oen,g;//三态控制端reg[7:0] q;always @(*)beginif (oen)beginq<="z";endelsebeginif(g)q<=d;elseq<=q;endendendmodule11.数据寄存器的设计module eda_jicunqi(r,clk,d,y); input r,clk;input [7:0]d;wire [7:0]d;output [7:0]y;reg [7:0]y;always @ (posedge clk or negedge r) beginif(!r)y<=8'b00000000;elsey<=d;endendmodule12.顺序脉冲发生器的设计module eda_shunxu(clk,clr,q);input clk,clr;output [7:0]q;reg [7:0]q;always @ ( posedge clk or posedge clr ) beginif ( clr==1)beginq<=8'b00000000; //赋初值endelsebeginif(q==0)q<=8'b00000001;elseq<=q<<1; //给初值进行移位endendendmodule13.1位全加法器的设计module quanjiaqi(a,b,sum,count,cin); input a;wire a;input b;wire b;input cin;wire cin;output sum;wire sum;output count;wire count;assign{sum,count}=a+b+cin; endmodule15.键控Led灯的设计module eda_led(led,key);input key;output led;reg led_out;assign led<=led_out;always@(key)beginif(key)led_out<=1;else if(!key)led_out<=0;endendmodule16.双向移位寄存器的设计module eda_yiweijicunqi( left_right ,load ,clr ,clk ,DIN ,DOUT );input left_right ;wire left_right ;input load ;wire load ;input clr ;wire clr ;input clk ;wire clk ;input [3:0] DIN ;wire [3:0] DIN ;output [3:0] DOUT ;wire [3:0] DOUT ;reg [3:0] data_r;assign DOUT = data_r ;always @ (posedge clk or posedge clr or posedge load)//敏感变量,看真值表beginif(clr==1)data_r <= 0;//判断是否清零else if (load )data_r<=DIN;//判断是否装载数据//判断进行左移位还是右移位elsebeginif(left_right)data_r<=DIN<<1;elsedata_r<=DIN>>1;endendendmodule17.8-3优先编码器的设计module youxianbianma( A ,I ,GS ,EO ,EI ); input [7:0] I ;wire [7:0] I ;input EI ;wire EI ;output [2:0] A ;reg [2:0] A ;output GS ;reg GS ;output EO ;reg EO ;always @ ( I or EI )if ( EI )beginA <= 3'b111;GS <= 1;EO <= 1;endelse if (I==8'b11111111)beginA <= 3'b111;GS <= 1;EO <= 0;endelse if ( I==8'b11111110 )beginA <= 3'b111;GS <= 0;EO <= 1;endelse if ( I==8'b1111110x )beginA <= 3'b110;GS <= 0;EO <= 1;endelse if ( I==8'b111110xx )beginA <= 3'b101;GS <= 0;EO <= 1;endelse if ( I==8'b11110xxx )beginA <= 3'b100;GS <= 0;EO <= 1;endelse if ( I==8'b1110xxxx )beginA <= 3'b011;GS <= 0;EO <= 1;endelse if ( I==8'b110xxxxx )beginA <= 3'b010;GS <= 0;EO <= 1;endelse if ( I==8'b10xxxxxx )beginA <= 3'b001;GS <= 0;EO <= 1;endelse if ( I==8'b0xxxxxxx )beginA <= 3'b000;GS <= 0;EO <= 1;endendmodule18.数据分配器的设计module shujufenpeiqi(y0,y1,y2,y3,din,a); output y0,y1,y2,y3;//4??êy?Yí¨μàinput din;//êy?Yê?è?input [1:0] a;reg y0,y1,y2,y3;always @(din,a)beginy0=0;y1=0;y2=0;y3=0; //3?ê??ˉ£á?case(a)00:y0=din;01:y1=din;02:y2=din;03:y3=din;endcase end endmodule。

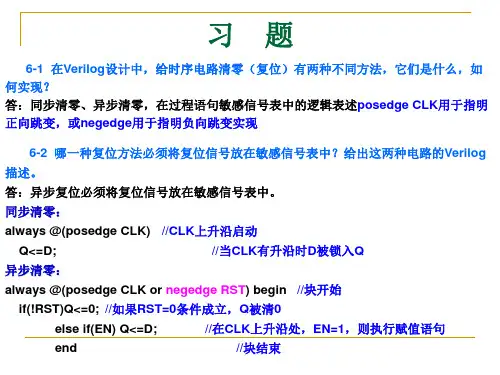

6-1 在Verilog设计中,给时序电路清零(复位)有两种不同方法,它们是什么,如何实现?答:同步清零、异步清零,在过程语句敏感信号表中的逻辑表述posedge CLK用于指明正向跳变,或negedge用于指明负向跳变实现6-2 哪一种复位方法必须将复位信号放在敏感信号表中?给出这两种电路的Verilog 描述。

答:异步复位必须将复位信号放在敏感信号表中。

同步清零:always @(posedge CLK) //CLK上升沿启动Q<=D; //当CLK有升沿时D被锁入Q异步清零:always @(posedge CLK or negedge RST) begin //块开始if(!RST)Q<=0; //如果RST=0条件成立,Q被清0else if(EN) Q<=D;//在CLK上升沿处,EN=1,则执行赋值语句end//块结束6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制数中含1的数量。

module Statistics8(sum,A); output[3:0]sum;input[7:0] A;reg[3:0] sum;integer i;always @(A)beginsum=0;for(i=0;i<=8;i=i+1) //for 语句if(A[i]) sum=sum+1;else sum=sum;endendmodule module Statistics8(sum,A); parameter S=4;output[3:0]sum;input[7:0] A;reg[3:0] sum;reg[2*S:1]TA;integer i;always @(A)beginTA=A; sum=0;repeat(2*S)beginif(TA[1])sum=sum+1;TA=TA>>1;endendendmodulerepeat循环语句for循环语句module Statistics8(sum,A);parameter S=8;output[3:0]sum;input[7:0] A;reg[S:1] AT;reg[3:0] sum;reg[S:0] CT;always @(A) beginAT={{S{1'b0}},A}; sum=0; CT=S;while(CT>0) beginif(AT[1])sum=sum+1;else sum=sum;begin CT= CT-1; AT=AT>>1; end end endendmodule6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制数中含1的数量。

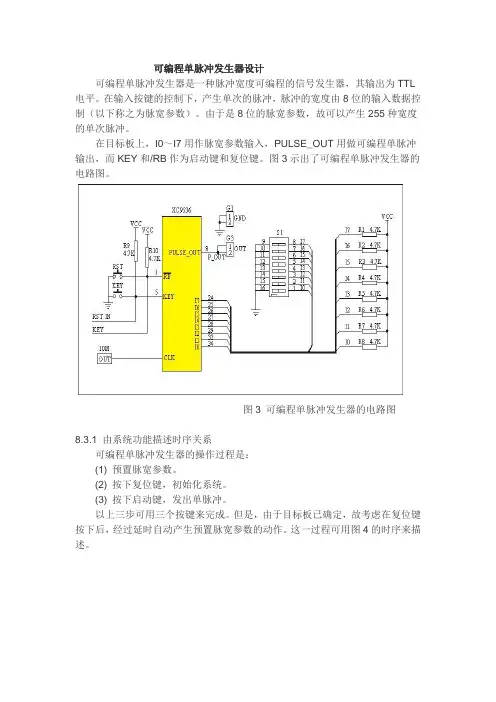

可编程单脉冲发生器设计可编程单脉冲发生器是一种脉冲宽度可编程的信号发生器,其输出为TTL 电平。

在输入按键的控制下,产生单次的脉冲,脉冲的宽度由8位的输入数据控制(以下称之为脉宽参数)。

由于是8位的脉宽参数,故可以产生255种宽度的单次脉冲。

在目标板上,I0~I7用作脉宽参数输入,PULSE_OUT用做可编程单脉冲输出,而KEY和/RB作为启动键和复位键。

图3示出了可编程单脉冲发生器的电路图。

图3 可编程单脉冲发生器的电路图8.3.1 由系统功能描述时序关系可编程单脉冲发生器的操作过程是:(1) 预置脉宽参数。

(2) 按下复位键,初始化系统。

(3) 按下启动键,发出单脉冲。

以上三步可用三个按键来完成。

但是,由于目标板已确定,故考虑在复位键按下后,经过延时自动产生预置脉宽参数的动作。

这一过程可用图4的时序来描述。

图4 可编程单脉冲发生器的时序图图中的/RB为系统复位脉冲,在其之后自动产生LOAD脉冲,装载脉宽参数N。

之后,等待按下/KEY键。

/KEY键按下后,单脉冲P_PULSE便输出。

在此,应注意到:/KEY的按下是与系统时钟CLK不同步的,不加处理将会影响单脉冲P_PULSE的精度。

为此,在/KEY按下期间,产生脉冲P1,它的上跳沿与时钟取得同步。

之后,在脉宽参数的控制下,使计数单元开始计数。

当达到预定时间后,再产生一个与时钟同步的脉冲P2。

由P1和P2就可以算出单脉冲的宽度Tw。

8.3.2 流程图的设计根据时序关系,可以做出图5所示的流程图。

在系统复位后,经一定的延时产生一个预置脉冲LOAD,用来预置脉宽参数。

应该注意:复位脉冲不能用来同时预置,要在其之后再次产生一个脉冲来预置脉宽参数。

为了产生单次的脉冲,必须考虑到在按键KEY有效后,可能会保持较长的时间,也可能会产生多个尖脉冲。

因此,需要设计一种功能,使得当检测到KE Y有效后就封锁KEY的再次输入,直到系统复位。

这是本设计的一个关键所在。

verilog写脉冲展宽电路概述及解释说明1. 引言1.1 概述在现代电子设备和数字系统中,脉冲展宽电路起着重要的作用。

它可以将一个输入信号的短暂脉冲扩展为持续一段时间的高电平输出信号。

这种功能对于许多应用来说是必不可少的,例如触发器、计时器、通信系统以及各种数字逻辑电路等。

本文将详细介绍脉冲展宽电路的定义、原理以及Verilog语言编写脉冲展宽电路的方法。

通过阐述Verilog编程语言的概述和基本语法规则,读者可以更好地理解和实现脉冲展宽电路。

1.2 文章结构本文共分为五个部分进行论述。

第一部分为引言,主要概述了文章要探讨的内容和目的。

第二部分介绍了脉冲展宽电路的定义、意义以及常见应用场景。

第三部分向读者简要介绍了Verilog编程语言,包括其概述、库函数介绍以及代码基本结构和语法规则。

第四部分详细描述了脉冲展宽电路的Verilog设计与实现方法,包括设计思路和步骤、关键模块分析与设计要点,以及实例演示和仿真结果分析。

最后一部分为结论与总结,对Verilog脉冲展宽电路的重要性和应用前景进行总结陈述,并提出了本文所提出的设计方法的优势、不足以及改进建议等内容。

1.3 目的本文的目的是介绍脉冲展宽电路及其在数字系统中的重要性和应用前景。

通过对Verilog编程语言的简介和具体实现方法的讲解,读者可以深入了解该电路的设计原理和实现过程,并能够运用Verilog语言进行脉冲展宽电路的设计与仿真。

通过阅读本文,读者将会掌握以下几个方面:- 掌握脉冲展宽电路的定义、意义以及常见应用场景;- 了解Verilog编程语言概述,包括库函数介绍和基本语法规则;- 理解脉冲展宽电路的Verilog设计思路、步骤以及关键模块分析与设计要点;- 学会使用Verilog语言进行脉冲展宽电路的实例演示和仿真,并能分析相关结果;- 总结对Verilog脉冲展宽电路设计方法和优势、不足的认识,并提出改进建议。

通过本文的学习和实践,读者将对脉冲展宽电路的设计与应用有更深入的理解,并能够掌握Verilog语言进行相关工程实现。

基于FPGA的时序脉冲发生器设计颜丽;王伟【摘要】In the design of realization to the timing pulse generator, field programmable gate array was used to change the traditional methods of design, and made modifying and debugging hardware more facilitate. The working principle of a standard binary counter formed timing pulse generator was analyzed comprehensively, the improving method was take to eliminate the predominance of "competition - adventure" produce by the standard binary counter formed timing pulse generator, Johnson counter was used as the counter of a timing pulse generator counter, and used of the SR function method further simplify the circuit, thereby timing pulse interference presents a method to eliminate reasonable. The reasonable method to eliminate the "competition - adventure"interference of timing pulse was taken.%本文在实现时序脉冲发生器的设计中,利用现场可编程门阵列改变了传统设计方法,进一步方便了对硬件的修改与调试。

顺序脉冲发生器的常用设计方法

顺序脉冲发生器是一种常用的电子电路,它可以按照预设的顺序输出一系列脉冲信号。

顺序脉冲发生器的设计方法有很多种,下面我将介绍其中几种常用的设计方法。

一、基于计数器的顺序脉冲发生器

基于计数器的顺序脉冲发生器是一种简单常用的设计方法。

它的原理是利用计数器的计数功能,按照预设的计数顺序输出脉冲信号。

具体实现时,可以使用可编程逻辑器件(如FPGA、CPLD)或者集成电路(如74LS90)来实现计数器功能。

通过设置计数器的初始值、计数方向、计数模式等参数,可以实现不同的顺序脉冲输出。

二、基于时序控制的顺序脉冲发生器

基于时序控制的顺序脉冲发生器是一种更加灵活的设计方法。

它的原理是利用时序控制电路,按照预设的时序输出脉冲信号。

具体实现时,可以使用时序控制器(如555定时器、可编程时钟芯片)或者微控制器来实现时序控制功能。

通过设置时序控制器的参数,可以实现不同的顺序脉冲输出。

三、基于状态机的顺序脉冲发生器

基于状态机的顺序脉冲发生器是一种更加高级的设计方法。

它的原理是利用状态机的状态转移功能,按照预设的状态转移顺序输出脉冲信号。

具体实现时,可以使用可编程逻辑器件(如FPGA、CPLD)或者微控制器来实现状态机功能。

通过设置状态机的状态转移表、状态转移条件等参数,可以实现不同的顺序脉冲输出。

以上是三种常用的顺序脉冲发生器的设计方法。

不同的设计方法各有优缺点,具体应用时需要根据实际情况选择合适的设计方法。

顺序脉冲发生器实验顺序脉冲发生器实验一、实验目的1. 了解顺序脉冲发生器的工作原理:2. 掌握顺序发生器的VHDL 描述方法:3. 学会用EDA 语言进行程序设计。

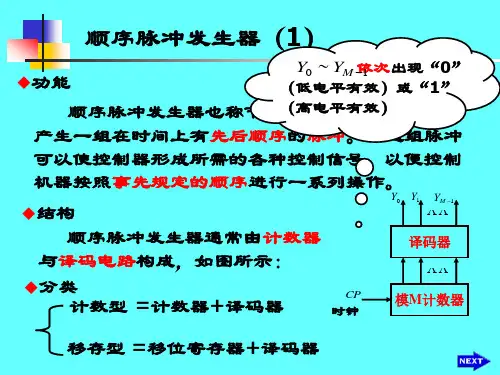

二、实验原理在数控装置和数字计算机中,往往需要机器按照人们事先规定的顺序进行运算和操作,这就要求控制电路不仅能正确的发出各种控制信号,而且要求这些控制信号在时间上有一定的先后顺序,能完成这样功能的电路称为顺序脉冲发生器。

顺序脉冲发生器通常由计数器与译码电路构成,如图所示:而脉冲发生器的种类分别有技数型和移存型两种,这里我们只做最简单的计数型脉冲发生器。

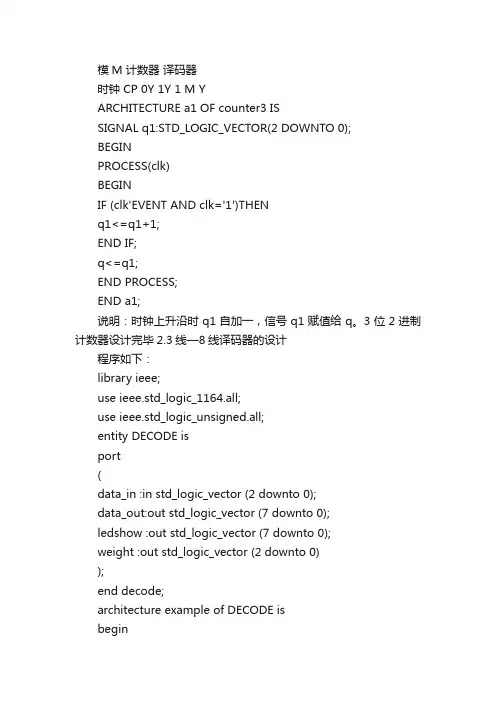

图中的模M 计数器取三位二进制计数器、译码器用三线-八线译码器来实现本次的顺序脉冲发生器。

当时钟脉冲CP 的上升沿到来时,三位二进制计数器输出自加一,输出由000—111八种不同的状态。

然后计数器输出的三位二进制数作为3线—8线译码器中的输入,由译码器来实现对三位二进制数对应输出信号的翻译。

三、实验过程1.设计3位2进制计数器:程序如下:LIBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_unsigned.all;ENTITY counter3 ISPORT( clk : IN STD_LOGIC;q : OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END counter3;模M 计数器译码器时钟 CP 0Y 1Y 1 M YARCHITECTURE a1 OF counter3 ISSIGNAL q1:STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINPROCESS(clk)BEGINIF (clk'EVENT AND clk='1')THENq1<=q1+1;END IF;q<=q1;END PROCESS;END a1;说明:时钟上升沿时q1自加一,信号q1赋值给q。

PWM信号发⽣器(verilog)module pwmgen(clk,rst,ce,addr,write,wrdata,read,bytesel,rddata,pwm); input clk,rst,ce;input [1:0]addr;input write,read;input[31:0]wrdata;output[31:0]rddata;input[31:0]bytesel;output pwm;reg[31:0]clk_div_reg,duty_cycle_reg;reg control_reg;reg clk_div_reg_sel,duty_cycle_reg_sel,control_reg_sel;reg[31:0]pwm_cnt,rddata;reg pwm;wire pwm_ena;//地址译码always@(addr)beginclk_div_reg_sel<=0;duty_cycle_reg_sel<=0;control_reg_sel<=0; case(addr)2'b00:clk_div_reg_sel<=1;2'b01:duty_cycle_reg_sel<=1;2'b10:control_reg_sel<=1;default:beginclk_div_reg_sel<=0;duty_cycle_reg_sel<=0;control_reg_sel<=0;endendcaseend//时钟寄存器always@(posedge clk or negedge rst)beginif(rst==1'b0)clk_div_reg=0;elsebeginif(write & ce & clk_div_reg_sel)beginif(bytesel[0])clk_div_reg[7:0]=wrdata[7:0];if(bytesel[1])clk_div_reg[15:8]=wrdata[15:8];if(bytesel[2])clk_div_reg[23:16]=wrdata[23:16];if(bytesel[3])clk_div_reg[31:24]=wrdata[31:24];endendend//周期占空⽐寄存器always@(posedge clk or negedge rst)beginif(rst==1'b0)duty_cycle_reg=0;elsebeginif(write&ce&duty_cycle_reg_sel)if(bytesel[0])duty_cycle_reg[7:0]=wrdata[7:0];if(bytesel[1])duty_cycle_reg[15:8]=wrdata[15:8];if(bytesel[2])duty_cycle_reg[23:16]=wrdata[23:16];if(bytesel[3])duty_cycle_reg[31:24]=wrdata[31:24];endendend//控制寄存器always@(posedge clk or negedge rst)beginif(rst==1'b0)control_reg=0;elsebeginif(write & ce & control_reg_sel)beginif(bytesel[0])control_reg=wrdata[0];endendend//读寄存器always@(addr or read or clk_div_reg or duty_cycle_reg or control_reg or ce) beginif(read & ce)case(addr)2'b00:rddata<=clk_div_reg;2'b01:rddata<=duty_cycle_reg;2'b10:rddata<=control_reg;default:rddata=32'h8888;endcaseendassign pwm_en=control_reg;//计数控制电路always@(posedge clk or negedge rst)beginif(rst==1'b0)pwm_cnt=0;elsebeginif(pwm_en)beginif(pwm_cnt>=clk_div_reg)pwm_cnt<=0;elsepwm_cnt<=pwm_cnt+1;endelsepwm_cnt<=0;endend//输出控制寄存器always@(posedge clk or negedge rst)beginif(rst==1'b0);elsebeginif(pwm_en)if(pwm_cnt<=duty_cycle_reg) pwm<=1'b1;elsepwm<=1'b0;endelsepwm<=1'b0;endendendmodule。

1.实验任务设计并制作一个脉冲序列发生器,周期性的产生脉冲序列101011010101。

2.实验目的通过本次设计,进一步熟悉多谐振荡器、计数器、数据选择器的用法,掌握脉冲序列发生器的设计方法。

3.参考电路(1)设计方案周期性脉冲序列发生器的实现方法很多,可以由触发器构成,可以由计数器外加组合逻辑电路构成,可以有GAL构成,也可以由CPLD\FPGA构成等等。

本设计采用由计数器加多路数据选择器的设计法案,脉冲序列发生器原理框图如(1)图所示。

图(1)脉冲序列发生器原理框图(2)参考设计脉冲序列发生器需要一个时钟信号,可采用由TTL非门和石英晶体振荡器构成的串联式多谐振荡器产生时钟信号,如图(2)所示。

主电路部分如图(3)所示,图中74LS161和与非门构成十二进制计数器,为脉冲序列的宽度为12位。

4.实验内容按照实验要求设计电路,确定元器件型号和参数;用Multisim进行仿真,列出实验数据,画出输出信号及其他关键信号的波形;对实验数据和电路的工作情况进行分析,得出实验结论;写出收获和体会。

图(2)时钟信号产生电路图(3)主电路图多谢振荡器介绍多谐振荡器是一种自激振荡电路。

因为没有稳定的工作状态,多谐振荡器也称为无稳态电路。

具体地说,如果一开始多谐振荡器处于0状态,那么它在0状态停留一段时间后将自动转入1状态,在1状态停留一段时间后又将自动转入0状态,如此周而复始,输出矩形波。

图6.4.1 对称式多谐振荡器电路对称式多谐振荡器是一个正反馈振荡电路[图6.4.1,]。

和是两个反相器,和是两个耦合电容,和是两个反馈电阻。

只要恰当地选取反馈电阻的阻值,就可以使反相器的静态工作点位于电压传输特性的转折区。

上电时,电容器两端的电压和均为0。

假设某种扰动使有微小的正跳变,那么经过一个正反馈过程,迅速跳变为,迅速跳变为,迅速跳变为,迅速跳变为,电路进入第一个暂稳态。

电容和开始充电。

的充电电流方向与参考方向相同,正向增加;的充电电流方向与参考方向相反,负向增加。

顺序脉冲发生器单元7 顺序脉冲发生器及其应用7-1 基本理论: 顺序脉冲发生器原理在数控装置和数字计算机中,往往需要机器按照人们事先规定的顺序进行运算和操作,这就要求控制电路不仅能正确的发出各种控制信号,而且要求这些控制信号在时间上有一定的先后顺序,能完成这样功能的电路称为顺序脉冲发生器。

F7-1 异步计数器构成顺序脉冲发生器顺序脉冲发生器一般由计数器和译码器两部分组成。

1. 异步计数器构成的顺序脉冲发生器图F7-1是异步计数器构成的顺序脉冲发生器。

Y0=/Q2• /Q1• /Q0 Y1= /Q2 •/Q1 •Q0 Y2=/Q2• Q1 •/Q0 Y3=/Q2• Q1• Q0 Y4=Q2•/Q1 •/Q0顺序脉冲发生器输出串脉冲Y0、Y1、Y2、Y3、Y4的周期由计数器的进制决定,控制执行机构操作时间的长短由驱动计数器的时钟CLK脉冲的周期决定。

由异步计数器构成的分配器有可能在输出端产生竞争冒险现象。

在图F7-1的电路中,由于时钟到来时,各触发器不是同时翻转,每当有两个以上的触发器翻转,就会产生冒险干扰。

如当计数器从001变为010时,若触发器UIA先翻转为0,U2A后翻转为1,那么将出现一个短暂的000状态,Y0将出现一个窄脉冲。

这种冒险干扰脉冲,如不加以抑制或消除,就可能造成误动作。

CLKQ0Q1Q2Y012345678Y1Y2Y3Y4顺序脉冲发生器的时序图顺序脉冲发生器波形图要克服竞争冒险现象,通常的是改变计数器的电路形式,如采用环形计数器、扭环计数器。

2. 由扭环计数器构成的顺序脉冲发生器图F7-2是数控插补器中的顺序脉冲发生器电路。

在数控中做插补运算时,每走一步,都要进行以下四个节拍:判别、进给、运算、判别,这四个节拍分别用t1 、t2、t3、t4表示。

其波形图如下。

根据时序图可以看出,有11个计数状态。

需要六位扭环计数器,构成11进制计数器。

1clkt1t2t3t42345678910111213插补器的时序图其状态表如后表。

verilog 脉冲计算Verilog脉冲计算脉冲信号广泛应用于数字电路设计和通信系统中。

其特点是信号短暂且突然变化,广泛用于触发器、计数器、时钟信号等方面。

在Verilog中,我们可以使用各种技术来计算和处理脉冲信号。

本文将介绍Verilog中的脉冲计算,并提供一些常用的技巧和实例。

在Verilog中,我们可以使用非阻塞赋值语句(<=)来进行脉冲计算。

非阻塞赋值语句将在一个时间步骤中同时更新所有变量的值,而阻塞赋值语句(=)则是按顺序执行的。

脉冲计算通常需要使用时钟信号和触发器来实现。

以下是一个简单的例子:```verilogmodule pulse_calc(input wire clk,input wire reset,output reg pulse);reg [3:0] counter;always @(posedge clk or posedge reset) beginif (reset)counter <= 4'b0;else if (counter == 4'b1111)counter <= 4'b0;elsecounter <= counter + 1;endalways @(posedge clk) beginpulse <= (counter == 4'b0001);endendmodule```在上面的例子中,我们定义了一个名为`pulse_calc`的模块,其中包含一个时钟信号`clk`、复位信号`reset`和一个输出脉冲信号`pulse`。

我们使用一个4位的计数器`counter`来计算脉冲信号的频率。

在`always`块中,我们使用了两个敏感列表。

第一个敏感列表包含时钟信号和复位信号,这是为了对计数器进行复位操作。

如果复位信号`reset`为高电平,则将计数器`counter`重置为0,否则按照顺序递增。