编码器的设计

- 格式:doc

- 大小:1.25 MB

- 文档页数:20

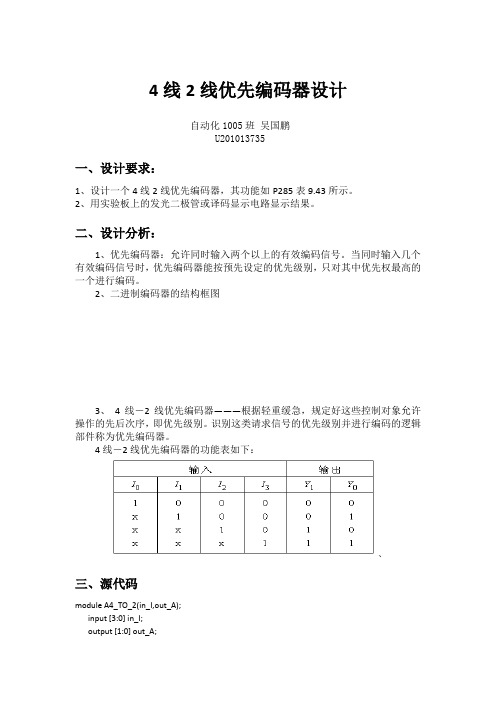

4线2线优先编码器设计自动化1005班吴国鹏U201013735一、设计要求:1、设计一个4线2线优先编码器,其功能如P285表9.43所示。

2、用实验板上的发光二极管或译码显示电路显示结果。

二、设计分析:1、优先编码器:允许同时输入两个以上的有效编码信号。

当同时输入几个有效编码信号时,优先编码器能按预先设定的优先级别,只对其中优先权最高的一个进行编码。

2、二进制编码器的结构框图3、4线-2线优先编码器―――根据轻重缓急,规定好这些控制对象允许操作的先后次序,即优先级别。

识别这类请求信号的优先级别并进行编码的逻辑部件称为优先编码器。

4线-2线优先编码器的功能表如下:、三、源代码module A4_TO_2(in_I,out_A);input [3:0] in_I;output [1:0] out_A;reg [1:0] out_A;always @(in_I)begincase(in_I)4'b0001 : out_A=2'b00;4'b0010 : out_A=2'b01;4'b0011 : out_A=2'b01;4'b0100 : out_A=2'b10;4'b0101 : out_A=2'b10;4'b0110 : out_A=2'b10;4'b0111 : out_A=2'b10;4'b1000 : out_A=2'b11;4'b1001 : out_A=2'b11;4'b1010 : out_A=2'b11;4'b1011 : out_A=2'b11;4'b1100 : out_A=2'b11;4'b1101 : out_A=2'b11;4'b1110 : out_A=2'b11;4'b1111 : out_A=2'b11;endcaseendendmodule四、仿真波形。

通信原理课程设计报告HDB3编码器的设计班级:通信05-2班指导教师:***学号:15号**:***设计日期:2007年11月26日至2007年11月30日第一章 HDB3码概述及产生背景现代通信借助于电和光来传输信息,数字终端产生的数字信息是以“1”和“0”两种状态位代表的随机序列,他可以用不同形式的电信号表示,以构造不同形式的数字信号。

在一般的数字通信系统中首先将消息变为数字基带信号,称为信源编码,经过调制后进行传输,在接收端先进行解调恢复为基带信号,再进行解码转换为消息。

HDB3码是AMI码的改进型,HDB3码又叫三阶高密度双极性码,是基带电信设备之间进行基带传输的主要码型之一。

该码具有以下特点:(1) 无直流分量,功率谱密度与AMI码类似。

(2) 解决了AMI码长连‘0’且提取信号的困难的问题。

(3) 具有内在检错能力。

由此可见,HDB3码是一种优良码,目前是广泛应用于基带传输的接口码。

在一般的数字通信系统中首先将消息变为数字基带信号,其次,传输码型中应含有定时时钟信息,以利于收端定时时钟的提取,再次,实际传输系统常希望在不中断通信的前提下,能监视误码,如果传输码型有一定的规律性,那么就可以根据这一规律性来检测传输质量,以便做到自动监测,因此,传输码型应具有一定的误码检测能力。

HDB3码就是具有误码检测能力的一种码。

第2章设计原理及步骤2.1 HDB3编码器的设计原理2.1.1 引言数字基带信号的传输是数字通信系统的重要组成部分。

在数字通信中,有些场合可不经过载波调制和解调过程,而对基带信号进行直接传输。

采用AMI码的信号交替反转,有可能出现四连零现象,这不利于接收端的定时信号提取。

而HDB3码因其无直流成份、低频成份少和连0个数最多不超过三个等特点,而对定时信号的恢复十分有利。

针对数字基带传输系统中HDB3信号的特点,采用基于CPLD/FPGA 的VHDL语言,在Max+plusⅡ的环境中,实现HDB3数字基带信号的调制、解调器.仿真结果表明,实现的HDB3基带信号调解器,系统简单、可靠,通过此系统能够方便地将原始信息流转换成HDB3基带信号。

线性分组码编码器设计1.引言2.线性分组码的基本原理线性分组码是由生成矩阵和校验矩阵组成的。

生成矩阵用于将数据进行编码,而校验矩阵用于检测和纠正错误。

生成矩阵是一个m×n的矩阵,其中n是数据位的数量,m是冗余位的数量。

生成矩阵的每一行表示一个码字,通过将生成矩阵与数据矩阵相乘,可以得到编码后的数据。

校验矩阵是一个n×m的矩阵,用于对编码后的数据进行检测和纠正。

3.线性分组码编码器的设计步骤3.1确定数据位数和冗余位数:根据实际应用需求确定数据位的数量和冗余位的数量。

3.2生成生成矩阵和校验矩阵:根据数据位数和冗余位数生成相应的生成矩阵和校验矩阵。

3.3将生成矩阵和校验矩阵存储在编码器中。

3.4输入数据:将待编码的数据输入到编码器中。

3.5编码:将输入的数据与生成矩阵进行矩阵乘法运算,得到编码后的数据。

3.6输出数据:将编码后的数据输出。

4.线性分组码编码器的性能分析线性分组码编码器的性能主要与生成矩阵和校验矩阵有关。

生成矩阵的选择决定了编码器的纠错能力,校验矩阵的选择决定了编码器的错误检测和纠正能力。

通常情况下,生成矩阵和校验矩阵都需要满足一些特定的性质,如生成矩阵需要满秩,校验矩阵需要是生成矩阵的逆。

5.线性分组码编码器的应用总结:线性分组码编码器是一种常见的错误检测和纠正编码方法。

它通过生成矩阵和校验矩阵来对数据进行编码,并能够检测和纠正多位错误。

线性分组码编码器的设计步骤包括确定数据位数和冗余位数、生成生成矩阵和校验矩阵、将生成矩阵和校验矩阵存储在编码器中、输入数据、编码和输出数据。

线性分组码编码器广泛应用于通信和存储领域,提高了通信和存储的可靠性。

PCM编码器设计PCM(脉冲编码调制)编码器是一种将模拟信号转换为数字信号的设备。

它用于音频和视频编码中,可以将连续时间的模拟信号转换为离散时间的数字信号,以便进行存储、传输和处理。

1.采样频率选择:选择适当的采样频率来采集原始模拟信号。

常用的采样频率有44.1kHz、48kHz和96kHz等。

选择适当的采样频率可以平衡信号的质量和文件的大小。

2.量化位数选择:选择适当的量化位数来描述采样信号的离散级别。

通常使用8位、16位或24位量化位数。

较高的量化位数可以提高信号的动态范围和信噪比,但需要更多的存储空间和传输带宽。

3. 量化器设计:采用适当的算法和电路设计一个精确的量化器,将连续模拟信号映射到离散级别。

一个常用的量化算法是线性二进制量化(linear binary quantization),它将输入信号划分为离散的级别,并将其映射到用二进制表示的编码值。

4. 压缩编码设计:设计一个有效的编码器,将量化后的信号进行进一步的压缩。

常用的压缩编码算法有Huffman编码和Lempel-Ziv编码等。

这些算法根据信号的统计特性和出现概率来对信号进行编码,以减少编码后的数据量。

5.错误纠正设计:为了增加PCM数据的可靠性,在编码过程中可以添加纠错码,以便在传输或存储过程中,能够检测和纠正部分错误。

常用的错误纠正编码包括海明码和循环冗余校验码(CRC)等。

6.附加功能设计:可以根据具体需求添加一些附加功能,如音频增强、降噪、立体声编码等。

这些功能可以提高音频质量,增加用户体验。

7.性能评估和优化:设计完成后,需要对PCM编码器的性能进行评估和优化。

包括信号质量评估、压缩率评估和编码速度评估等。

同时可以根据评估结果对设计进行优化,以改进性能。

总的来说,设计一个PCM编码器需要考虑采样频率、量化位数、量化器设计、压缩编码设计、错误纠正设计、附加功能设计、性能评估和优化等因素。

通过合理的设计和优化,可以实现高质量的PCM编码器,提高音频和视频编码的效率和质量。

基于FPGA汉明码编译码器设计汉明码是一种能够检测和纠正错误的编码方式。

在FPGA(Field Programmable Gate Array)中,我们可以使用FPGA来设计并实现一个基于(7,4)汉明码的编码器和解码器。

1.编码器设计:编码器将4位数据编码为7位汉明码。

下面是一个基于FPGA的(7,4)汉明码编码器的设计步骤:-设置一个4位输入端口和一个7位输出端口。

-创建一个4×7的矩阵,用于存储所有可能输入与对应汉明码的关系。

每行代表一个输入,每列代表一个汉明码位。

-在FPGA中,使用逻辑门(如XOR门和AND门)来实现矩阵的功能。

根据矩阵,依次设计逻辑门电路来计算每个汉明码位。

例如,对于第一个汉明码位,使用四个输入位的异或门计算出结果。

-将每个汉明码位的结果输出到对应的输出端口。

2.解码器设计:解码器将7位汉明码解码为4位数据。

下面是一个基于FPGA的(7,4)汉明码解码器的设计步骤:-设置一个7位输入端口和一个4位输出端口。

-创建一个7×4的矩阵,用于存储所有可能的汉明码与对应的输出数据的关系。

每行代表一个汉明码,每列代表一个输出数据位。

-同样,使用逻辑门来实现矩阵的功能。

根据矩阵,依次设计逻辑门电路来计算每个输出数据位。

例如,对于第一个数据位,使用七个输入位的与门计算出结果。

-将每个输出数据位的结果输出到对应的输出端口。

3.性能分析和优化:可以通过FPGA的资源利用率和时钟频率等指标对设计进行性能评估。

通过仔细设计逻辑电路,合理分配资源和优化电路,可以提高编码器和解码器的性能。

可以考虑使用并行计算、流水线等技术来提高时钟频率和减少时延。

另外,还可以在FPGA中使用多个编码器和解码器来实现更高级的错误检测和纠正功能。

可以考虑使用更高级的汉明码,如(15,11)汉明码或(31,26)汉明码,来提高错误检测和纠正能力。

可以结合其他编码技术,如校验和,奇偶校验等,来增加冗余度和提高系统的可靠性。

如何设计简单的编码器与解码器设计简单的编码器与解码器是数字通信系统中的重要任务之一。

编码器的作用是将输入信号转换为编码信号,而解码器则是将编码信号还原为原始输入信号。

在本文中,将介绍如何设计一个简单但高效的编码器与解码器。

一、编码器设计编码器的设计需要根据具体的应用场景和要求进行选择,常见的编码器包括哈弗曼编码、差分编码、相位编码等。

这里以差分编码为例进行说明。

差分编码是一种通过记录信号的差异来进行编码的方法。

其基本原理是将当前信号与前一个信号进行差异比较,将差异结果作为编码输出。

这种方法能够在一定程度上降低信号传输过程中的干扰和噪声影响。

差分编码器的设计步骤如下:1. 初始化:设定前一个信号的初始值为0。

2. 读取输入信号:获取当前输入信号的数值。

3. 计算差异:将当前输入信号与前一个信号进行相减,得到差异值。

4. 输出编码:将差异值作为编码输出。

5. 更新前一个信号:将当前输入信号作为下一次的前一个信号。

二、解码器设计解码器的设计需要与编码器相对应,以确保能够正确还原编码信号。

差分解码器的设计步骤如下:1. 初始化:设定前一个信号的初始值为0,用于解码信号还原。

2. 读取编码信号:获取当前编码信号的数值。

3. 还原差异:将编码信号作为差异值还原出当前信号的数值。

4. 输出解码信号:将还原的当前信号作为解码输出。

5. 更新前一个信号:将还原的当前信号作为下一次的前一个信号。

三、代码实现下面给出一种简单的编码器与解码器的Python代码实现。

以差分编码为例:```python# 编码器def encoder(input_signal):prev_signal = 0encoded_signal = []for signal in input_signal:diff = signal - prev_signalencoded_signal.append(diff)prev_signal = signalreturn encoded_signal# 解码器def decoder(encoded_signal):prev_signal = 0decoded_signal = []for diff in encoded_signal:signal = diff + prev_signaldecoded_signal.append(signal)prev_signal = signalreturn decoded_signal# 示例input_signal = [1, 3, 5, 7, 9]encoded_signal = encoder(input_signal) decoded_signal = decoder(encoded_signal) print("输入信号:", input_signal)print("编码信号:", encoded_signal) print("解码信号:", decoded_signal)```以上代码实现了对输入信号进行差分编码和解码的功能。

正交编码器解码器电路设计论文正交编码器解码器电路设计论文正交编码器是一种常见的电子元器件,主要用于数字信号的传输与处理。

它可以将输入的数字信号进行编码,从而提高信号的稳定性和可靠性。

同时,正交编码器还能实现信号的高速传输和多路复用等功能,因此在通信领域得到了广泛的应用。

然而,正交编码器的应用还面临着一些挑战,例如编码解码效率低下、噪声干扰等问题。

为了解决这些问题,研究者们开展了大量的工作,并提出了各种改进的算法和电路设计方案。

本文将介绍其中一种常见的正交编码器解码器电路设计,并分析其原理、特点和优缺点。

一、正交编码器电路设计正交编码器的原理是利用两路正交的信号进行编码,即对输入信号进行正交幅度调制,将其转化成两路正交的信号。

这两路信号分别称为I路和Q路,可以分别表示输入信号的正弦和余弦分量。

通过这种方式,可以大幅度提高信号的抗干扰能力和可靠性。

在正交编码器电路中,采用的是相移键控调制器(PSK)的电路结构。

具体来说,输入信号首先进入相移器,经过相移后与本振信号进行混频,然后通过低通滤波器进行滤波,得到I路和Q路的信号。

最终,两路信号分别经过叠加器进行加法运算,得到编码后的输出信号。

二、正交解码器电路设计与正交编码器相对应,正交解码器是将编码后的信号进行解码的关键设备。

它主要包括正交解调器和解调后继电路两部分。

其中,正交解调器是用于将输入信号进行解调的电路,解调后继电路则是将信号解调后进行滤波、逆变等处理。

正交解调器电路可以分为两类,一类是折叠式解调器,另一类是二相式解调器。

折叠式解调器的主要特点是简单、易于实现。

它采用的是对称反相器和滤波器的组合,可以将编码后的信号进行解调,并得到I路和Q路的信号。

但是,由于其存在折叠现象,会导致信号的失真和抗干扰能力不足。

因此,在高频率和高精度的情况下,折叠式解调器的应用范围有限。

相比之下,二相式解调器则可以更好地解决失真和抗干扰能力的问题。

它采用的是两路相差90度的解调信号,可以实现正交解调。

HDB3码编码器设计HDB3编码器是一种常用的数字编码方案,用于传输数字信号时提高码元传输效率和信号传输质量。

HDB3编码器使用了高度密集的编码方式,将4位二进制数据编码成5位二进制码元。

HDB3编码规则如下:1.将输入的二进制数据按照顺序分组,每组四位。

2.检测每组中连续出现的0的数量。

如果连续零的数量达到四个,则执行步骤3,否则执行步骤43.在连续的四个零前插入特殊位。

特殊位是0011或1100,根据上一个特殊位的类型来决定。

-如果前一个特殊位是0011,则在四个零前插入1100特殊位。

-如果前一个特殊位是1100,则在四个零前插入0011特殊位。

4.如果没有连续零序列,根据下列规则编码:-如果当前输入位为1,则输出+1码元(0100)。

-如果当前输入位为0,则输出-1码元(0000)。

-如果输入位的累计数量达到四个,则对其奇偶性进行判断。

-如果四个输入位的奇偶性相同,则输出反转码元(000V);其中V是有电平变化的码元(0或1),用来解决直流偏置的问题。

-如果四个输入位的奇偶性不同,则使用和上一个输出码元相同的码元。

基于以上规则,我们可以设计一个HDB3编码器的逻辑电路。

以下是一个可能的设计:1.首先,我们需要一个计数器来记录连续零的数量。

计数器的初始值为零。

2.创建一个4位寄存器,用于存储最近四个输入位的数据。

3.创建一个类型寄存器,用于存储上一个特殊位的类型。

初始值可以设定为0,表示上一个特殊位为1100。

4.创建一个输出寄存器,用于存储当前输出码元。

5.实现一个逻辑电路来根据输入的二进制数据判断要执行的操作。

-如果连续零的数量达到四个,判断上一个特殊位的类型。

-如果上一个特殊位是0011,则将1100特殊位插入到输入码元中,并将类型寄存器更新为1-如果上一个特殊位是1100,则将0011特殊位插入到输入码元中,并将类型寄存器更新为0。

-将连续零的数量重置为0。

-如果连续零的数量没有达到四个,根据输入位的奇偶性执行操作。

同步编码器程序设计在通信系统中,同步编码器是一个重要的组成部分。

它用于确保数据在传输过程中保持同步,避免出现相位和时间上的误差。

这篇文章将详细介绍同步编码器的程序设计。

一、概述同步编码器的主要任务是捕获并处理输入信号,以确保信号的发送和接收端保持同步。

它的主要工作流程包括:检测信号的起始和结束位置、将信号分解成比特流,并将这些比特流进行排序。

通过这种方式,同步编码器可以在信号出现相位和时间上的误差时,及时发现并修正这些问题。

二、程序设计1.初始化:在程序开始运行之前,需要对同步编码器进行初始化。

这包括设置各种参数,如阈值、排序算法等。

此外,还需要对输入信号的特性进行评估,以确定合适的初始化值。

2.检测起始和结束位置:同步编码器需要能够准确地检测输入信号的起始和结束位置。

这通常需要使用到滑动窗口技术,通过比较窗口内信号的幅度、频率、相位等信息,来确定信号的起始和结束位置。

3.比特流处理:在确定了信号的起始和结束位置后,需要将信号分解成比特流。

这一过程通常需要使用到数字信号处理技术,如傅里叶变换、小波变换等。

通过这些技术,可以将信号分解成一系列离散的数字信号,这些数字信号就是比特流。

4.排序:在比特流处理完成后,需要对这些比特流进行排序。

这一过程通常需要使用到哈希表、二叉树等数据结构,以确保比特流的顺序正确。

同时,也需要考虑到各种干扰因素,如时钟抖动、相位误差等,以确保排序结果的准确性。

5.输出:最后,需要将排序后的比特流输出到相应的设备或系统中。

这通常需要使用到网络协议,如TCP/IP、UDP等,以确保数据的传输效率和质量。

三、算法优化为了提高同步编码器的性能和效率,可以对上述算法进行优化。

具体来说,可以尝试以下几种方法:1.分布式处理:将同步编码器分成多个子模块,每个子模块负责一部分数据处理任务。

这样可以提高同步编码器的并行处理能力,减少处理时间。

2.硬件加速:利用硬件加速器(如FPGA、ASIC等)来加速同步编码器的处理过程。

《简易旋转编码器的制作》作业设计方案一、设计目标本设计旨在帮助学生了解旋转编码器的工作原理,并通过实际操作制作一个简易的旋转编码器,提高学生对电子原理的理解和实践能力。

二、设计原理旋转编码器是一种用于测量旋转角度的传感器,通常由一个旋转轴和两个输出信号组成。

当旋转编码器旋转时,两个输出信号的相位差会发生变化,通过检测相位差的变化可以确定旋转角度。

三、设计材料1. Arduino开发板2. 旋转编码器3. 毗连线4. 电阻5. LED灯四、设计步骤1. 毗连旋转编码器到Arduino开发板,将A相和B置信号分别毗连到数字引脚2和3上。

2. 编写Arduino代码,通过读取A相和B置信号的状态来确定旋转方向和角度,并将结果输出到串口监视器。

3. 将LED灯毗连到Arduino开发板的数字引脚13上,用于指示旋转编码器的工作状态。

4. 通过旋转编码器,观察LED灯的闪烁情况,验证旋转编码器的工作原理。

5. 调整旋转编码器的旋转角度,观察串口监视器的输出结果,确认旋转编码器的准确性。

五、设计评估学生可以通过以下方式评估自己的设计:1. 确认旋转编码器的工作原理是否清晰。

2. 检查Arduino代码是否正确编写,旋转角度是否准确输出。

3. 观察LED灯的闪烁情况,验证旋转编码器的工作状态。

4. 调整旋转编码器的旋转角度,检查串口监视器的输出结果是否符合预期。

六、设计拓展学生可以根据自己的兴趣和能力对设计进行拓展,例如:1. 添加LCD显示屏,实时显示旋转角度。

2. 将旋转编码器与舵机结合,实现旋转角度控制舵机的功能。

3. 设计一个简易的旋转编码器模拟器,帮助其他同砚理解旋转编码器的工作原理。

通过本设计,学生不仅可以掌握旋转编码器的工作原理,还可以提高自己的动手能力和创造力,为将来的进修和工作打下坚实的基础。

4线-2线编码器的设计实验目的1. 利用Cadence 软件完成一个4线-2线编码器的设计;2. 完成编码器的瞬态仿真、最高工作频率和功耗的性能指标测试;3. 学会自底向上地设计基于组合逻辑电路的编码器的设计;4. 掌握创建符号的步骤;5. 掌握编码器设计和仿真的步骤;6. 学会设置仿真参数,从而加深对Cadence 软件仿真的熟悉度。

实验原理编码和译码的问题在日常生活中经常遇到,数字系统中存储或者处理的信息,常常是用二进制码表示的。

用一个二进制代码表示特定含义的信息称为编码,具有编码功能的逻辑电路称为编码器,图1所示为二进制编码器的结构图,它有n 位二进制码输出,与2n 个输入相对应。

本次专业技能训练我们设计了一个普通的4线-2线编码器。

图1二进制编码器的结构图4线-2线编码器真傎表如表1所示:P 0 Y 0 P 1 Y 1 P 2n -1 Yn-1. . . . . . . .表14个输入P 0 到P 3 为高电平有效信号,输出是两个二进制代码Y 1 Y 0,任何时刻P 0~P 3中只能有一个取值为1,并且有一组对应的二进制码输出。

除表中的4种取值组合有效外,其余12种组合所对应的输出均应为0。

对于输入或输出变量,凡取1值的用原变量表示,取0值的用反变量表示,由真值表可以得到如下逻辑表达式:Y 1=32103210I I I I I I I I +Y 0=32103210I I I I I I I I +根据逻辑表达式画出逻辑图,如下图2所示:图2 4线-2线编码器逻辑图输 入 输 出 P 0 P 1 P 2 P 3 Y 1 Y 0 1 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 1 0 0 0 0 1 1 1实验内容及结果本文的设计思路是首先完成4线-2线编码器所需要的各个模块的电路原理图设计,再将其创建成可以调用的符号,最后按照图2的编码器逻辑图完成首4线-2线编码器的设计。

首先需要创建一个库(如:08063224)与各个视图单元inv、 nand4 、nor2和 encode;注意在新建各个视图单元文件时应该都是建到08063224库文件里,不然会提示文件位置报错。

其次按照要求完成编码器的瞬态工作频率功耗等前仿真。

实验的内容及结果具体如下:1.反相器原理图及其符号的创建开启虚拟机,进入Red Hat Linux后,点击CIW窗口的file→new→library,由此可创建库08063224(用来存放单元视图的文件夹)。

将库文件的路径设置在cadence目录下,Name栏输入库名08063224,右侧Technology File栏中选择Attach to an existing techfile,点击窗口OK。

然后再点击file→new→cellview,创建一个单元视图文件夹inv,Library Name 选取为08063224,Cell Name可自定义为inv,设置view name为schematic,设置tool为composer schematic,点击OK,此时便弹出Schematic Editing空白窗口。

输入反相器设计原理图的结果如下图3所示:图3 反相器原理图具体的操作步骤:①添加元件:在原理编辑窗口中,选择Add→Intance,打开Intance窗口,点击Browse按钮,弹出Library Browser窗口,在Library一栏中选择gpdk180,Cell一栏选择pmos,Cellview一栏选择symbol,都选好后并且设置pmos的宽长为4U就可以点击close,将Library Brower窗口关闭,此时Add Instance 窗口的Cell和View栏就会被填好,就可以将pmos管添加到原理编辑窗口中了。

同样可添加nmos管,并且设置nmos的宽长为2U。

添加Source和Ground,在Library一栏中选analoglib,Cell一栏中选vcc,Cellview一栏中选symbol。

添加Ground与添加Source的方法相同。

②添加Pin :点击Add→pin,会出现 Add pin 窗口,在Pin Names 栏中输入in, Direction设置为 input ,完成输入端的添加;同理再添加一个输出管脚,在Pin Names 栏中输入out, Direction设置为output完成输出端的添加。

③连线:点击 Add→Wire(Narrow),将应该要连线的地方连接起来,点击即可。

若需要移动的时候也是先选中,按M再点击到相应的位置,切记不能有拖动的操作。

④检查并保存,在画完原理图后,需要检查原理图是否有错,点击Design→Check and Save,然后就可在CIW窗口中观察是不有错或警告。

生成的反相器符号结果如下图4所示:图4 反相器符号具体的操作步骤:①在Schematic中,点击Design→Create Cellview→From Cellview弹出Cell From Cellview 窗口,图中Library Name 和Cell Name 会自动填写我们所要创建符号的原理图名称,点击OK,弹出 Symbol Generation Option窗口,在填好各项后进入Symbol Editing 窗口编辑符号。

②点击Add→shape,可通过其中的Line和Circle各项来编辑符号形状,结果如上图4所示。

③点击Design→Check and Save,可在CIW窗口中观察是不有错或警告,检查并保存编辑好的符号。

2.四输入与非门原理图及其符号的创建在CIW窗口点击file→new→cellview,创建一个单元视图文件夹nand4,Library Name选取为08063224,Cell Name自定义为nand4,设置view name 为schematic,设置tool为composer schematic,点击OK即可。

输入的四输入与非门设计原理图结果如下图5所示:图5 四输入与非门原理图先添加元件,在analogLib库中选择vcc与gnd各一个,按照图添加所需元件。

在gpdk180库中选择pmos与noms各4个, 并且设置pmos的宽长为4U,nmos 的宽长为2U。

然后添加输入输出管脚,再进行连线。

生成的四输入与非门符号结果如下图6所示,操作步骤和创建反相器的符号方法相似。

图6 四输入与非门符号3.二输入或非门原理图及其符号的创建二输入或非门原理图设计:在CIW窗口,点击file→new→cellview创建一个单元视图文件夹nor2,Library Name选取为08063224,Cell Name自定义为nor2,设置view name为schematic,设置tool为composer schematic,点击OK即可,打开电路原理图设计窗口。

添加元件在gpdk180中选择两个pmos和两个nmos,在analoglib库中选择vcc和gnd各一个,即按下图7所示添加所须元件;添加输入端管脚为a、b;输出端管脚为y;连线,按设计的原理图连线。

检查电路结构与连线,使用check and save 图标检验查错,修改并存档。

输入的二输入或非门设计原理图结果如下图7所示:图7 或非门设计原理图创建符号:从原理图打开逻辑符号窗口,同创建反相器符号方法,对符号进行编辑,最终形成nor2逻辑符号如图8所示:图8二输入或非门符号4.利用设计好的符号设计顶层4-2线编码器原理图电路结构:构成4-2线编码器的电路形式主要有非门、四输入与非门结构和二输入或非门结构,CMOS结构的4-2线编码器电路如图9所示:添加输入pin为P0、P1、P2和P3;输出pin为Y1与Y0。

图9 4-2线编码器原理图5.4-2线编码器的瞬态仿真在设计好的4-2线编码器原理图编辑窗口,点击Tools→Analog Environment,弹出Analog Design Environment ,首先设置库的路径,点击Setup →Model libraries,然后点击Browse,将库路径设为/home/irio/ /gpdk180/models/spectre/gpdk.scs,将Section 设为stat。

然后点击Setup→Stimuli,在弹出的Setup Analog Stimuli窗口,设置4个输入参数P0、P1、P2、P3和Global Sources,参数设置方法如下图10—13所示:(在设置这些参数时都要点击Enabled和Change使得参数从OFF状态变到ON状态)图10输入参数P0的设置图11 输入参数P1的设置图12 输入参数P2的设置图13 输入参数P3的设置①点击Analyses→Choose,选择分析类型为Tran瞬态分析,Stop Time 仿真时间参数设置16n,并选中moderate和Enabled。

②点击Output→Save All,选择输出,输出信号选择allpub,器件电流选择all,点击OK。

此时我们再将输出结果选中,操作步骤:Outputs→To Be Plotted→Select On Schematic。

在原理图中选中输入端P0、P1、P2、P3和输出端Y1和Y2,再返回仿真的界面如图14所示。

图14 瞬态仿真窗口③点击Simulation→Nelist and Run,进行仿真,点击后会弹出Welcome to Spectre窗口,点击OK就开始仿真。

如果提示有错误,就需要查找错误并修改原理图。

若无错误,运行后就会弹出仿真波形如图15所示。

图15 瞬态仿真波形图直流分析创建新的单元视图Pnvfz,并调用实验三中生成的反相器符号来连接反相器的仿真电路,输入原理图步骤同实验二。

只是现在单元视图中多了一个反相器的符号,同时直流分析需要对电路外加一个激励。

具体电路图如图4所示。

图4 反相器直流分析原理图此时Vcc不需要再进行设值,而是要对外接激励V0设置为1.8V,对V1进行直流扫描和参数设置:点击Select Component,选择电路图中的V1,弹出Select Component Parameter窗口,选中窗口中dc,点击OK。

运行后仿真波形如图5所示。

注意:仿真波形中Net2为输入电压,out为输出电压。

6.4线-2线编码器的最高工作频率仿真同时直流分析需要对电路外加一个激励。

Y1的最高工作频率:2.0000GP1的最高工作频率:0.998G P2的最高工作频率:0.998GP3的最高工作频率:0.998G 最终的最高工作频率波形:7.4线-2线编码器的功耗仿真最终的电流的值:0.00112A 也即1.1286mA P=UI=1.8V*I=0.00203148W结果分析问题分析1. 在原理图设计时连线一定不能十字相交,否则在进行check and save 操作后CIW窗口会出现警告,但可以丁相交。