全差分运放

- 格式:docx

- 大小:213.30 KB

- 文档页数:6

全差分运算放大器设计全差分运放(Fully-Differential Amplifier,简称FDA)是一种特殊的运放,它具有两个差动输入和两个差动输出。

全差分运放具有许多优点,包括良好的共模抑制和电源抑制比,适用于高精度传感器信号放大、功率放大和模拟信号处理等领域。

在这篇文章中,我将介绍全差分运放的设计原理和步骤。

首先,我们需要确定设计的要求和规范。

这包括增益要求、带宽要求、电源电压和输入输出电阻等参数。

根据这些要求,我们可以选择合适的运放器件和电路拓扑。

全差分运放的常见电路拓扑有两级差分放大器、共射共源放大器和增益交换放大器等。

在这里,我们以两级差分放大器为例进行设计。

第一步是选择运放器件。

我们需要根据设计要求选择适合的运放器件,可以根据其增益带宽积、供电电压范围和失调电流等参数进行选择。

一般来说,我们可以选择低失调电流、高增益带宽积和低电压噪声的器件。

第二步是确定电路拓扑。

在两级差分放大器中,第一级是差分放大器,第二级是共射共源放大器。

差分放大器的作用是提供高输入阻抗和共模抑制比,共射共源放大器的作用是提供电流放大和驱动能力。

由于这两级放大器要分别满足不同的要求,我们可以选择不同的放大倍数和器件参数来优化电路性能。

第三步是确定偏置电路。

偏置电路的作用是提供恒定的工作电流,这可以通过电流源和电阻网络来实现。

偏置电流的选择要根据运放器件的要求和特点,可以使用恒流源或电流反馈等方法来实现。

第四步是确定反馈电路。

反馈电路的作用是控制放大倍数和增益稳定性,可以使用电阻、电容或者电流源等元件来实现。

选择适当的反馈方式可以减小失调电压和非线性,提高性能。

第五步是进行电路仿真和优化。

通过电路仿真,我们可以验证设计的性能和满足要求。

优化可以通过调整电路参数和进行迭代仿真来实现,以达到设计要求。

第六步是进行电路布局和线路板设计。

在设计布局时,要注意分离放大器电路和干扰源,减少电源和信号线的串扰。

线路板设计要保证差分信号走线的对称性和阻抗匹配,以提高传输性能。

综合课程设计研究报告课题名称:全差分两级运放研究人员:指导教师:王向展宁宁201 年1月1日微电子与固体电子学院目录一、绪论 (1)(一)研究工作的背景与意义 (1)(二)国内外现状分析 (1)二、研究目标、研究内容与技术指标 (1)(一)研究目标 (2)(二)研究内容 (2)(三)关键技术 (2)(四)技术指标 (3)三、电路工作原理 (3)(一)电路结构理论 (4)(二)关键电路模块 (4)(三)非理想效应 (5)四、电路设计与仿真 (6)(一)电路设计方案 (6)(二)电路设计结构 (9)(三)电路仿真及结果 (10)五、全文总结与展望 (12)参考文献 (13)一、绪论(一)研究工作的背景与意义随着模拟集成电路技术的发展,高速、高精度运算放大器得到广泛应用。

全差分运算放大器在输入动态范围、抑制共模信号和噪声的能力等方面,较单端输出运放有很大优势,成为应用很广的电路单元。

另外,全差分输出时的输出电压信号幅度比单端输出时增大一倍,这对低电源电压供电的现代CMOS电路尤为重要,因为这可以扩大输出信号的动态范围。

因此,本文讨论并设计了满足一定要求的全差分运算放大器。

(二)国内外现状分析从第一颗运算放大器IC问世到现在,运算放大器技术已经在半导体制造工艺和电路设计两方面取得了巨大进展。

在大约40年的发展过程中,IC制造商们利用上述先进技术设计出了近乎“完美”的放大器。

虽然什么是理想放大器很难有一个精确定义,但它却为模拟设计工程师提供了一个目标。

理想放大器应该无噪声、具有无穷大增益、无穷大输入阻抗、零偏置电流以及零失调电压,它还应该不受封装尺寸限制,不占用空间。

上述这些,都是许多教科书为了得到简单的传递函数而做出的种种假设。

未来放大器市场增长的驱动力主要有三方面:其一,便携式应用的低功耗要求将推动具有低操作电源电压/电流的放大器增长;其二,高分辨率应用需要能降低噪声和失真度的放大器;其三,由于性能和价格压力持续上扬,因此能够集成其他功能的放大器前景乐观。

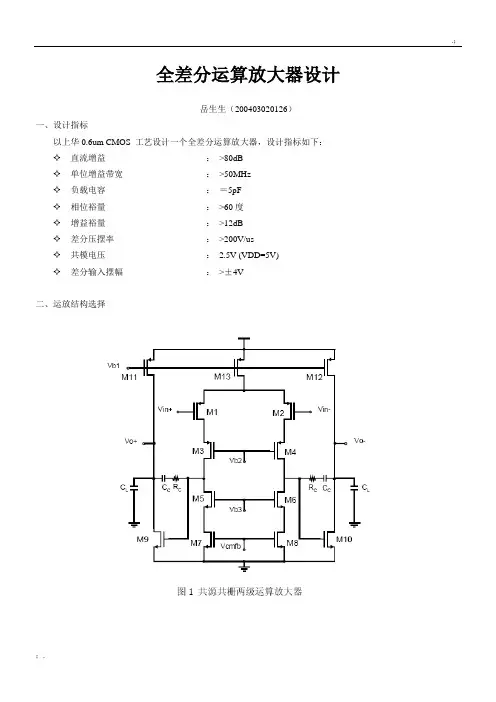

全差分运算放大器设计岳生生(200403020126)一、设计指标以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下:✧直流增益:>80dB✧单位增益带宽:>50MHz✧负载电容:=5pF✧相位裕量:>60度✧增益裕量:>12dB✧差分压摆率:>200V/us✧共模电压:2.5V (VDD=5V)✧差分输入摆幅:>±4V二、运放结构选择运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。

如图2所示;(b )折叠共源共栅,folded-cascode 。

如图3所示;(c )共源共栅,telescopic 。

如图1的前级所示。

本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT NV之和小于0.5V ,输出端的所有PMOS管的,DSAT PV之和也必须小于0.5V 。

对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。

另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。

考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。

两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。

三、性能指标分析1、 差分直流增益 (Adm>80db)该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益1351113571135135753()m m m o o o o o m m m m o o o o m m g g gg gg G A R r rr r g g r r r r=-=-=-+第二级增益92291129911()m o o o m m o o gg G AR r rgg=-=-=-+整个运算放大器的增益:4135912135753911(80)10m m m m overallo o o o m m o o dB g g g gAA A g g g gr r r r ==≥++2、 差分压摆率 (>200V/us )转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。

全差分运放和差分运放全差分运放和差分运放是两种常用的运放电路,它们在信号放大和滤波等应用中起到重要的作用。

全差分运放(fully differential amplifier)是一种能够对差分信号进行放大的运放电路。

它由两个对称的差动输入端和两个对称的差动输出端组成。

差动输入端的两个信号引脚接收两个输入信号,输出端的两个信号引脚输出差分信号。

全差分运放的输入电压与输出电压之间的关系可以通过增益来描述,一般用差模增益和共模增益来定义。

差模增益表示输出信号与差分输入信号之间的关系,而共模增益表示输出信号与共模输入信号之间的关系。

全差分运放广泛应用于差分信号放大、滤波、模拟信号处理等领域。

差分运放(differential amplifier)是一种基本的运放电路,它由一个差动输入端和一个单端输出端组成。

差模输入信号作用在差动输入端,通过运放电路的放大作用,将差模输入信号转换为单端输出信号。

差分运放的特点是输入和输出都是差模信号,能够对差模信号进行放大。

差分运放在信号放大、滤波、串扰抑制等领域有重要的应用。

全差分运放和差分运放在应用中有许多相似之处,但也有一些区别。

首先,全差分运放有两对差动输入接口和差动输出接口,而差分运放只有一对差动输入接口和单端输出接口。

其次,差分运放只能放大差模信号,而全差分运放可以同时放大差模信号和共模信号。

此外,全差分运放具有更高的抗干扰能力和更低的共模幅度输出,因此在一些对共模干扰要求较高的应用中常常使用全差分运放。

综上所述,全差分运放和差分运放是常见的运放电路,它们在信号放大、滤波和抗干扰等应用中发挥着重要作用。

全差分运放具有双差动输入输出和较好的共模抑制能力,而差分运放则主要用于差模信号放大。

选择适合的运放电路需要根据具体应用需求来确定。

全差分运放的等效模型

全差分运放是一种常用的电子元件,用于放大电压信号。

它的等效模型可以简单描述如下:

全差分运放包含两个输入端和一个输出端。

它的输入端分别为非反相输入端(+)和反相输入端(-),输出端为差分输出端。

在等效模型中,我们可以将全差分运放看作是一个差分放大器。

差分放大器的原理是利用两个输入端的电压差来放大信号。

非反相输入端和反相输入端的电压差越大,输出信号的放大倍数就越大。

全差分运放的等效模型可以用一个放大倍数来表示。

这个放大倍数可以通过输入电压和输出电压之间的比值来计算。

放大倍数越大,信号的放大效果就越好。

全差分运放还可以通过调节反馈电阻来改变放大倍数。

通过选择合适的反馈电阻,我们可以实现不同的放大倍数,以适应不同的应用需求。

除了放大电压信号,全差分运放还可以用于滤波、积分、微分等功能。

通过调整输入信号和反馈电阻的组合,我们可以实现不同的功能。

全差分运放在各个领域都有广泛的应用。

在音频处理领域,它可以用于音频信号的放大和处理。

在通信领域,它可以用于信号的放大

和传输。

在仪器仪表领域,它可以用于信号的放大和测量。

全差分运放是一种常用的电子元件,用于放大电压信号。

它的等效模型可以简单描述为差分放大器。

通过调整输入信号和反馈电阻的组合,我们可以实现不同的放大倍数和功能。

它在各个领域都有广泛的应用。

全差分运放电路的设计全差分运放电路是一种常用的放大电路,它可以在信号采集和信号处理中起到很大的作用。

全差分运放电路通过将信号输入分为两个互为相反的信号,从而抵消共模干扰,提高系统的抗干扰能力,实现高质量的信号放大。

本文将会详细介绍全差分运放电路的设计方法和注意事项。

首先,全差分运放电路由运放、电阻和电容器组成。

一般情况下,有两种常见的全差分运放器设计:非反馈输出型和反馈输出型。

对于非反馈输出型的全差分运放电路,其输出电压与输入电压成正比。

这种设计方式适用于需要稳定增益的应用,如压力传感器、光传感器等。

而反馈输出型的全差分运放器则通过反馈网络来调整增益,适用于需要可调增益的应用,如音频放大器、滤波器等。

在设计全差分运放电路时,需要考虑以下几个关键因素:1.输入电阻和输入电容:全差分运放电路的输入电阻应尽可能大,以减小输入电流,避免对信号源的干扰。

同时,输入电容也应尽可能小,以提高信号的快速响应。

2.带宽:全差分运放电路的带宽需要根据实际应用需求进行选择。

一般情况下,带宽越大,电路越容易产生共模干扰。

因此,需要根据具体应用需求来平衡带宽和抗干扰能力。

3.输出电阻:全差分运放电路的输出电阻应尽可能小,以实现较高的加载能力和输出电压稳定性。

4.功耗:全差分运放电路的功耗应尽可能小,以提高系统的能效和延长电池寿命。

设计全差分运放电路时,可以按照以下步骤进行:1.确定应用需求:首先需要明确电路的功能和应用场景,包括所需的增益、带宽和动态范围等。

2.选择运放器:根据应用需求选择合适的全差分运放器,考虑增益范围、带宽、功耗和价格等因素。

3.选择电阻和电容器:根据所选的运放器的输入和输出特性,选择合适的电阻和电容器,以满足输入和输出阻抗的要求。

4.建立电路模型:根据电路需求和所选元件的特性,建立电路模型进行电路仿真,并进行参数优化。

5.PCB设计:根据电路模型进行PCB设计,注意信号、电源和地的布线问题,尽量减少共模干扰。

全差分运放增益计算全差分运放(Fully Differential Amplifier,简称FDA)是一种特殊的运放电路,具有两个输入端和两个输出端。

它的增益计算可以通过以下步骤进行:1. 假设输入端A为正输入,输入端B为负输入,输出端C为正输出,输出端D为负输出。

2. 在没有输入信号时,假设运放的输出电压为Vc和Vd。

根据差分运放的特性,Vc和Vd应该相等,即Vc=Vd。

3. 当输入信号为差模信号时(即输入端A和输入端B的电压相等但极性相反),假设差模信号为Vdm,则输入端A的电压为(Vcm+Vdm)/2,输入端B的电压为(Vcm-Vdm)/2,其中Vcm为输入端A和输入端B的共模电压。

4. 当输入信号为共模信号时(即输入端A和输入端B的电压相等且极性相同),假设共模信号为Vcm,则输入端A的电压为(Vcm+Vdm)/2,输入端B的电压为(Vcm+Vdm)/2。

5. 根据差分运放的特性,输出端C和输出端D的电压差应该与输入信号乘以放大倍数,即Vc-Vd=Av*(Vcm-Vdm)。

6. 根据步骤3和步骤5的结果,可以得到输出端C和输出端D的电压分别为Vc=(Vcm+Vdm)/2+Av*(Vcm-Vdm)/2,Vd=(Vcm+Vdm)/2-Av*(Vcm-Vdm)/2。

7. 根据步骤2的结果,Vc和Vd相等,可以得到Vcm和Vdm的关系式为Vcm=Av*Vdm。

8. 将步骤7的结果代入步骤6的公式中,可以得到输出端C和输出端D的电压分别为Vc=(1+Av)*Vcm/2,Vd=(1-Av)*Vcm/2。

9. 根据步骤8的结果,可以计算出全差分运放的增益为Av=2*(Vc-Vd)/Vcm。

需要注意的是,全差分运放的增益计算是基于理想情况下的运放电路,实际电路中可能会存在一些非理想因素,如偏置电流、偏置电压等,这些因素可能会对增益计算结果产生影响。

因此,在实际应用中,需要根据具体的电路参数进行相应的修正和调整。

全差分运放阻抗匹配计算下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by the editor. I hope that after you download them, they can help yousolve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you!In addition, our shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts,other materials and so on, want to know different data formats and writing methods, please pay attention!全差分运放是一种常用的电路元件,在电子学领域有着广泛的应用。

两级CMOS全差分运算放大器的设计和仿真 (2)1、软件的安装 (2)1.1 Cadence orcad的安装 (2)1.2 Hspice的安装 (2)1.3Cosmos Scope的安装 (2)2、实验要求 (2)3、电路图手工计算 (3)3.1 运放主结构计算 (3)3.2 偏置电路 (5)3.3 共模反馈电路 (7)4、使用Orcad绘制电路图 (7)5、电路仿真 (11)6、仿真结果查看 (13)7、其他性能参数的仿真 (15)两级CMOS全差分运算放大器的设计和仿真1、软件的安装在该试验中要用到三个软件,分别为Cadence orcad(绘制电路图与网表提取工具),Hspice (电路仿真工具)和Cosmos Scope(仿真结果查看工具)。

所有用到的软件安装程序均放在D盘EDA文件夹中。

1.1 Cadence orcad的安装打开D盘中的\eda\OrCad9.23,点击Setup.exe,点击下一步,到输入Install Code步骤,打开Crack文件夹中的Install.tex文件,将Orcad Capture后面的码复制到Install Code里,然后点击下一步。

直至安装完毕。

1.2 Hspice的安装打开D盘eda\hspice_vA-2008.03,点击Hspice的安装程序进行安装,均点击下一步,直至安装结束。

然后将该文件夹中的hspice2008.lic文件拷贝到C:\synopsys\Hspice_A-2008.03下。

右键点击电脑桌面我的电脑/属性/高级/环境变量/系统变量(如果只想让管理员用,则是administrator的用户变量)/新建/变量名lm_license_file 变量值就是license文件的路径,/hspice2008.lic,也就是变量值为C:\synopsys\Hspice_A-2008.03\hspice2008.lic 然后确定。

1.3Cosmos Scope的安装打开D盘eda\cosmos2007\HSpice_CosmosScope_Z-2007.03-SP1_win,点击安装程序进行安装。

全差分运放的噪声计算全差分运放的噪声计算是在电子电路设计中非常重要的一个参数。

全差分运放是一种用于信号处理和放大的集成电路,其设计目的是提供高品质、低噪声的放大功能。

在设计电路时,需要计算全差分运放的噪声水平,以确保在实际应用中获得最佳性能。

全差分运放的噪声主要包括输入电压噪声、输入电流噪声和输出电压噪声。

输入电压噪声是指输入端产生的噪声电压,通常由运放的电压噪声和输入电阻带来。

输入电流噪声是指输入端产生的噪声电流,通常由运放的输入电流噪声和输入电阻带来。

输出电压噪声是指运放输出端产生的噪声电压,通常由运放的电压噪声和输出电阻带来。

为了计算全差分运放的总噪声水平,可以采用以下步骤:1. 首先,需要了解全差分运放的输入电压噪声、输入电流噪声和输出电压噪声的数据表。

这些数据通常包含在运放的数据手册中,可以从厂商的官方网站上获取。

2. 其次,根据电路设计的具体参数,计算输入电压噪声的影响。

输入电压噪声可以通过运放的电压噪声和输入电阻的噪声电压计算得出。

一般来说,输入电压噪声对全差分运放的总噪声水平的影响比较显著,需要进行仔细的计算和分析。

3. 然后,计算输入电流噪声的影响。

输入电流噪声通常由运放的输入电流噪声和输入电阻的噪声电流引起。

在设计电路时,需要考虑输入电流噪声对信号的影响,特别是在低信噪比的应用中。

4. 最后,计算输出电压噪声的影响。

输出电压噪声通常由运放的电压噪声和输出电阻的噪声电压引起。

在设计电路时,需要确保输出电压噪声在可接受的范围内,以保证电路的性能和稳定性。

通过以上步骤的计算和分析,可以得出全差分运放的总噪声水平。

在电路设计中,噪声是一个非常重要的参数,对电路的性能和稳定性有着重要的影响。

因此,在设计电路时,需要仔细计算和分析全差分运放的噪声水平,以确保电路的性能达到设计要求。

全差分运放的英语

(最新版)

目录

1.差分运放的概念

2.全差分运放的特点

3.全差分运放的应用

4.全差分运放的英语表达

正文

1.差分运放的概念

差分运放(Differential amplifier),是一种模拟电路,主要用于放大差分输入信号。

差分放大电路有两个输入端,分别为非反相输入端和反相输入端。

当两个输入端的电压存在差分时,差分运放会产生输出电压,从而实现对差分信号的放大。

2.全差分运放的特点

全差分运放(Common-mode rejection ratio,CMRR),是一种衡量差分运放抑制共模输入信号能力的参数。

全差分运放的特点有以下几点:(1)高共模抑制比:全差分运放的共模抑制比很高,可以有效抑制共模输入信号,提高电路的抗干扰能力。

(2)恒定的偏置电压:全差分运放的输出电压与输入电压之间的差分电压成正比,且偏置电压基本恒定,不随输入电压的变化而变化。

(3)低输入偏差电流:全差分运放的输入偏差电流很小,可以降低电路的输入偏差电压,提高电路的精度。

3.全差分运放的应用

全差分运放在电子电路中具有广泛的应用,如:

(1)信号放大:全差分运放可以用于对差分信号进行放大,提高信号的抗干扰能力。

(2)模拟滤波:全差分运放可以用于构成滤波电路,对模拟信号进行滤波处理。

(3)传感器信号处理:全差分运放可以用于处理传感器输出的差分信号,提高传感器的测量精度。

4.全差分运放的英语表达

全差分运放的英语表达为:Common-mode rejection ratio(CMRR)。

全差分运放输入阻抗不平衡摘要:一、全差分运放简介二、输入阻抗不平衡的概念三、全差分运放输入阻抗不平衡的原因四、全差分运放输入阻抗不平衡的影响五、解决全差分运放输入阻抗不平衡的方法正文:全差分运放(Full-Differential Operational Amplifier)是一种广泛应用于模拟信号处理和通信系统的运算放大器。

它具有两个输入端和一个输出端,可以对两个输入信号的差值进行放大。

然而,全差分运放在使用过程中可能会出现输入阻抗不平衡的问题,这将对信号处理性能产生影响。

本文将针对全差分运放的输入阻抗不平衡问题进行详细探讨。

输入阻抗不平衡是指全差分运放的两个输入端之间的输入阻抗不相等。

在全差分运放中,输入阻抗的不平衡会导致两个输入信号的电压放大倍数不相等,从而使输出信号失真。

当输入阻抗不平衡严重时,可能导致运放工作不稳定,甚至出现自激振荡。

全差分运放输入阻抗不平衡的原因主要有以下几点:1.制造工艺差异:由于生产工艺的限制,全差分运放的输入晶体管可能存在参数差异,导致输入阻抗不相等。

2.温度影响:温度变化会影响全差分运放中晶体管的参数,进而导致输入阻抗不平衡。

3.电源电压波动:电源电压的波动可能使输入晶体管的工作状态发生变化,从而导致输入阻抗不平衡。

全差分运放输入阻抗不平衡会对信号处理性能产生如下影响:1.输出信号失真:输入阻抗不平衡会导致输出信号失真,降低信号处理系统的性能。

2.系统稳定性降低:输入阻抗不平衡可能使全差分运放工作不稳定,进而影响整个信号处理系统的稳定性。

3.系统噪声增加:输入阻抗不平衡会降低系统的信噪比,从而降低信号处理性能。

为解决全差分运放输入阻抗不平衡的问题,可以采取以下方法:1.选用参数一致的晶体管:通过选用参数一致的晶体管,可以降低输入阻抗不平衡的程度。

2.温度补偿:采用温度补偿技术,通过对运放进行温度敏感的调整,以减小温度对输入阻抗的影响。

3.电源去耦:对电源进行去耦处理,减小电源电压波动对输入阻抗的影响。

全差分运放结构全差分运放结构是一种常见的电路结构,它在模拟电路设计中具有重要的作用。

全差分运放结构由两个差分放大器组成,可以实现对输入信号的放大和滤波处理。

本文将介绍全差分运放结构的原理、特点和应用。

我们来了解一下全差分运放结构的原理。

全差分运放结构由两个差分放大器组成,其中一个差分放大器的输出与另一个差分放大器的输入相连。

这样设计的好处是可以将输入信号的正负半周分别放大,从而实现对信号的放大和滤波。

差分放大器的输入端连接了两个信号源,一个为正向输入,一个为反向输入。

通过调整这两个输入信号的幅值和相位,可以实现对输入信号的放大和相位调节。

全差分运放结构的特点主要有以下几个方面。

首先,它具有很高的共模抑制比,可以抑制输入信号的共模干扰。

其次,它具有很高的增益稳定性,可以保证输出信号的稳定性和准确性。

此外,全差分运放结构还具有很好的线性度和动态范围,可以实现对输入信号的高精度放大。

全差分运放结构在实际应用中有着广泛的应用。

首先,它可以用于模拟信号的放大和滤波处理。

在音频放大器和功率放大器中,全差分运放结构可以实现对音频信号的放大和滤波,从而提高音质和功率输出。

其次,全差分运放结构还可以用于数据采集系统和传感器接口电路中。

通过对传感器信号进行放大和滤波处理,可以提高信号的可靠性和抗干扰能力。

此外,全差分运放结构还可以用于通信系统和仪器设备中,实现对输入信号的放大和调节。

在实际应用中,我们还需要考虑一些问题。

首先是电源电压的选择。

全差分运放结构通常需要较高的电源电压,以保证其工作性能和稳定性。

其次是输入信号的范围和幅值。

输入信号的范围和幅值需要根据具体的应用需求进行选择,以保证信号的准确性和稳定性。

此外,还需要考虑输入端的阻抗和输出端的负载能力,以保证信号的传输质量和可靠性。

全差分运放结构是一种常见且重要的电路结构,它可以实现对输入信号的放大和滤波处理。

全差分运放结构具有很高的共模抑制比、增益稳定性和线性度,适用于各种模拟电路设计和应用场景。

全差分运放(Fully Differential Amplifier)是一种基于差分输入和差分输出的放大器电路,能够在差分信号中放大信号同时抑制共模信号。

共模点(Common Mode Point)则是指全差分运放的输入共模电压的值。

在全差分运放器中,共模点是指两个输入端的电压相等时的电压值。

在理想情况下,全差分运放器能够将共模信号进行完全抵消,使其在输出端不产生任何增益。

但在实际电路中,由于器件的不匹配和偏置电流等影响,使得共模信号无法完全抵消,会在输出端产生一定的共模幅度。

当全差分运放器失去共模抑制能力时,通常会出现共模放大(Common-Mode Gain)的情况,即输入的共模电压在输出端产生了有放大的幅度。

共模放大会引入不必要的噪声和失真,影响电路的性能。

为了实现更好的共模抑制性能,可以采取一些措施,如优化差分对输入电路的设计、增加电流源的稳定性和匹配性,以及采用高质量的元件等。

另外,可通过加入补偿电路、调整工作点和增加反馈等方式来提高共模抑制能力和共模稳定性。

总之,共模点是指全差分运放器的输入共模电压值,通过优化电路设计和采取相应措施,可以提高共模抑制性能,减少共模放大现象,提高差分信号的放大效果。

CMOS模拟集成电路实验报告实验课7 全差分运放的仿真方法目标:1、了解全差分运放的各项指标2、掌握全差分运放各项指标的仿真方法,对全差分运放的各指标进行仿真,给出各指标的仿真结果。

本次实验课使用的全差分运放首先分析此电路图,全差分运算放大器是一种具有差分输入,差分输出结构的运算放大器。

其相对于单端输出的放大器具有一些优势:因为当前的工艺尺寸在减少,所以供电的电源电压越来越小,所以在供电电压很小的情况下,单端输出很难理想工作,为了电路有很大的信号摆幅,采用类似上图的全差分运算放大器,其主要由主放大器和共模反馈环路组成。

1、开环增益的仿真得到的仿真图为1.开环增益:首先开环增益计算方法是低频工作时(<200Hz) ,运放开环放大倍数;通过仿真图截点可知增益为73.3db。

2.增益带宽积:随着频率的增大,A0会开始下降,A0下降至0dB 时的频率即为GBW,所以截取其对应增益为0的点即可得到其增益带宽积为1.03GB。

3.相位裕度:其计算方法为增益为0的时候对应的VP的纵坐标,如图即为-118,则其相位裕度为-118+180=62,而为保证运放工作的稳定性,当增益下降到0dB 时,相位的移动应小于180 度,一般取余量应大于60度,即相位的移动应小于120 度;所以得到的符合要求。

在做以上仿真的时候,关键步骤在于设定VCMFB,为了得到大的增益,并且使相位裕度符合要求,一直在不停地改变VCMFB,最初只是0.93,0.94,0.95的变化,后来发现增益还是远远不能满足要求,只有精确到小数点后4为到5位才能得到大增益。

2.CMRR 的仿真分析此题可得共模抑制比定义为差分增益和共模增益的比值,它反映了一个放大器对于共模信号和共模噪声的抑制能力。

因此需要仿真共模增益和差分增益。

可以利用两个放大器,一个连成共模放大,一个连成差模放大,用图1仿真差分增益图1用图2仿真共模增益图2将两个仿真写在一个sp文件中可以得到如下结果:相角仿真因为CMRR 的相角为=Vp(V op,Von)-Vp(V o p)黄色的为Vp(Vo p),红色的为Vp(V op,Von),两者相减,得到CMRR 的相角的仿真图为,其中蓝线为CMRR的相角仿真图,其它两条为上面的线,将它们放在一起对比:CMRR的幅度仿真其CMRR 的幅值为=Vdb(V op,V on)-Vdb(V op),蓝线为Vdb(V op,V on),粉线为Vdb(V op),两者相减得到绿线,即为CMRR的幅值特性曲线截取其在100HZ之前的增益值可得低频时增益为49.1db。

全差分放大器(转自小辉辉的博客)

Title: Fully differential amplifiers

By Jim Karki

Systems Specialist, High-Speed Amplifiers

Introduction

专业音频工程师通常使用术语“平衡”来指代差分信号传输。

这也告知了我们对称的概念,同时它在差分系统中也是非常重要的。

在差分系统中,驱动器有平衡的输出,传输线有平衡的特性,并且接收器有平衡的输入。

通常由两个方法用来处理差分信号:电子法和变压器法。

1. 电子的方法有着如成本低、尺寸和重量小以及优异的低频、直流响应等特点。

2. 变压器提供的好处是优异的共模抑制比、直流隔离、无功耗(效率几乎为100%),并且抗恶劣的EMC环境干扰。

本文着重介绍对于差分信号情况下的集成全差分放大器。

这里将讨论一些基本的操作,如怎样将单端信号转换成差分信号以及怎样搭建有源抗混叠滤波器。

What is an integrated, fully differential amplifier?

一个集成的全差分放大器在框架上与标准运算放大器是非常相似的。

图1显示了一个简化版的集成全差分放大器。

Q1和Q2是输入差分对。

在一个标准运算放大器中,输出电流是只从输入差分对的一边取出的,并且输入电流是用来建立一个单端输出电压的。

在一个全差分放大器中,来自差分输入对两边的电流都是用于在由Q3/Q5集电极和Q4/Q6集电极处形成的高阻抗节点处建立电压的。

这些电压然后被缓冲至差分输出OUT+和OUT-。

对于一阶近似,送到IN+和IN-的共模电压并没有使得流过Q1或者Q2的电流产生变化,因此没有产生输出电压;它被抑制了。

共模输出电压不是由输入端控制的。

VCM误差放大器通过对输入端采样、将其与VCM处的电压作比较并调节内部反馈的方式来控制共模

输出电压。

这两个互补放大器路径共享同一个输入差分对,它们的特性是经过非常良好的匹配的,并且这样的框架使得它们的工作点互相靠的很近。

因此,两个放大器中的失真也是匹配的,结果导致了差分信号的对称失真。

对称失真倾向于抵消偶次谐波。

实验室测试证明,当信号被差分地测量时,对比于测量任何一端的单端输出,在1MHz处THS4141的差分输出中的二次谐波分量减少了大约5dB。

测量出的三次谐波分量没有变化。

Voltage definitions

为了理解一个全差分放大器是怎样工作的,理解用于描述放大器的电压定义是非常重要的。

图2 显示了代表全差分放大器及其输入输出电压定义的框图。

在+和-输入之间的电压差是差分输入电压VID。

两个输入电压的平均值是共模输入电压VIC。

在+和-输出之间的电压差是差分输出电压VOD。

共模输出电压VOC是两个输出电压的平均值并且是由VCM处的电压控制的。

Af是与频率相关的放大器差分增益,因此VOD=VID x Af。

Increased noise immunity

现实中总会发生这种情况,当信号从一处传送至另一处,噪声会耦合进入线路。

在一个差分系统中,保持传送线路互相尽可能靠近会使得被耦合进入电感的噪声表现为共模电压。

在电源中常见的噪声也会表现为共模电压,系统对于外界噪声更具有抗干扰性。

图3显示了全差分放大器的噪声抗干扰性。

Increased dynamic range

由于在差分输出中相位变化的缘故,在同样电压摆幅的情况下,差分输出的动态范围相比单端输出提高了两倍(如图4)。

Basic Circuits

为了在全差分放大器中保持平衡,必须从两边的输出以及两边的输入中均采取对称的反馈。

两边形成了对称的反相放大器,并且反相放大器拓扑较容易适配全差分放大器。

图5显示了怎样通过使用对称反馈来保持一个平衡的放大器,其中反馈电阻RF和输入电阻RG 是相等的。

在两个反馈路径中保持对称来保持优良的CMRR性能是非常重要的。

CMRR是直接正比于电阻匹配误差的。

举个例子来说,一个0.1%的误差导致了60dB的CMRR。

对由于不匹配电阻导致的反馈中的微小变化来说,放大器的差分增益约为两边的平均增益。

输出平衡是由VCM误差放大器保持的。

从前,产生差分信号一直是非常麻烦的。

一旦差分方法被使用,需要多达三个放大器以及直流隔离电容来设置共模输出电压。

集成的全差分放大器提供了一个更好的解决方案。

图6 显示了一个将单端信号转换为差分信号的例子。

全差分放大器的一个主要应用即ADC输入情况下的信号处理。

低通滤波器需要用来去除高频噪声防止其混叠进入感兴趣的频带。

多级反馈(MFB)是一个很容易适配全差分放大器的优良拓扑。

一个MFB电路用于在一个二阶低通滤波器转移函数中实现一个复合极点对。

这里有一个例子如图7所示。

该滤波器电路额转移函数为

K设定通带增益,fC是滤波器的截止频率,FSF是频率范围因数,Q是品质因数。

其中Re是复合极点对的实部,Im是复合极点对的虚部。

设定R2=R,R3=mR,C1=C,C2=nC,结果有:

开始先确定比率,m和n,需要要的增益以及设计的该类滤波器的Q值,然后选择C并且计算需要fC的R值。

R4、Rt和C3的组合有着多重影响。

R4将放大器输出与ADC的输入想隔离。

R4和Rt为在放大器和ADC之间的传输线提供双重中断,并且形成了一个分压器。

C3帮助吸收ADC 输入端口注射的电荷。

R4和C3形成了一个实极点,它与MFB级中的复合极点协同制作一个三阶滤波器,甚至它可以被简单地放置在感兴趣的频率之外。

一些带有差分输入的ADC会提供合适的VCM输出。

典型地,在这里需要做的一切即提供旁路电容-0.1uF和/或者0.01uF。

如果VCM没有被提供,VCM可以从如图8所示的ADC参考电压处产生。

在求和点处的电压即为参考电压的中间点并且它将VOC集中于ADC 输入范围的中间点。

每个电源引脚应该有一个6.8uF到10uF之间的钽电容与0.01uF到0.1uF的陶瓷电容互相靠近并联在一起。

图7 显示了10uF和0.1uF电源旁路电容器。

Conclusion

集成全差分放大器与标准单端运算放大器非常相似,除了全差分放阿呆器的输出是从差分输入对的两边取出从而产生差分输出的。

当与单端系统相比,差分系统提供了提升的外部噪声抗干扰性能、减少的偶次谐波和双倍动态范围。

通过实行两个对称的反馈路径,反相放大器拓扑非常容易适配全差分放大器。

集成全差分放大器非常适合驱动差分ADC输入。

他们为抗混叠滤波提供了简易的方法,并且所需的共模电压可以很方便地通过VCM输入来设定。