全差分运算放大器设计说明

- 格式:doc

- 大小:526.00 KB

- 文档页数:17

全差分运算放大器设计概要全差分运算放大器是一种常见的电子电路,它可以将输入信号的差分放大,并在输出端提供差分信号。

全差分运算放大器广泛应用于模拟与数字信号处理中,如低噪声放大器、滤波器和交叉耦合放大器等领域。

本文将介绍全差分运算放大器的设计概要,包括电路结构、设计要点和性能指标等。

[图片]该电路由两个共模反馈放大器组成,其中一个作为正放大器,另一个作为负放大器。

输入信号通过差分输入端口加到两个反馈放大器上,经过放大后,在输出端口提供差分信号。

为了保证优良的性能,必须对电路的参数进行适当的设计和调整。

首先,需要确定全差分运算放大器的增益要求。

增益是指输出信号与输入信号之间的比例关系。

在不同的应用中,增益要求可能不同。

根据增益要求,可以选择合适的放大器型号和电路拓扑结构。

其次,需要选择适当的放大器元件。

放大器元件包括晶体管、电阻、电容等。

选择合适的元件是设计成功的关键。

晶体管的选择要考虑其增益、噪声系数、带宽等指标。

电阻和电容的选择要考虑其阻值、容值、精度等因素。

然后,需要确定电路的偏置方案。

全差分运算放大器需要提供适当的偏置电压,以确保电路能够正常工作。

偏置电压的选择要考虑元件的工作状态和参数的稳定性。

常见的偏置方案包括电流镜偏置、电流源偏置等。

设计完成后,需要对电路进行性能测试和优化。

性能测试包括增益、带宽、噪声系数、非线性失真等指标的测试。

根据测试结果,可以进行相应的电路优化,以满足设计要求。

最后,需要对电路进行可靠性分析。

可靠性分析是为了确保电路在长时间工作过程中不会出现故障。

可靠性分析包括温度分析、电路重要参数的敏感度分析等。

全差分运算放大器设计的关键在于电路的结构和元件的选择。

合理的电路结构和适当的元件选择可以使电路具有较高的增益、宽带和低噪声等性能。

此外,还需要注意电路的偏置方案和可靠性分析,以确保电路的正常工作和长时间可靠性。

总之,全差分运算放大器是一种重要的电子电路,具有广泛的应用前景。

全差分套筒式运算放大器设计1、设计内容本设计基于经典的全差分套筒式结构设计了一个高增益运算放大器,采用镜像电流源作为偏置。

为了获得更大的输出摆幅及差模增益,电路采用了共模反馈及二级放大电路。

本设计所用到的器件均采用SMIC 0.18µm的工艺库。

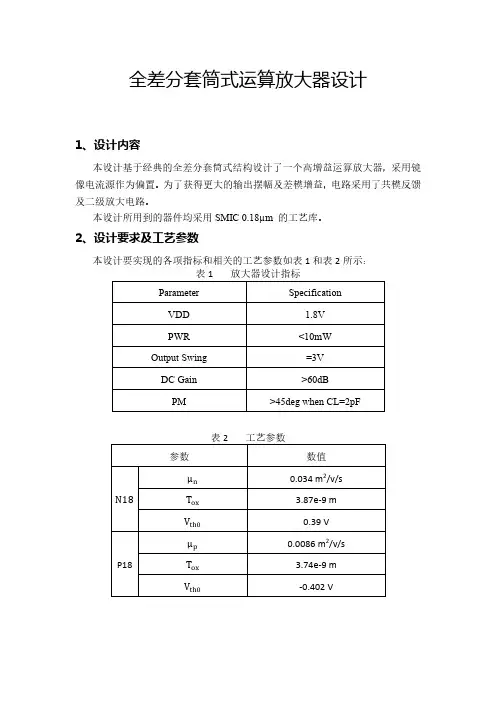

2、设计要求及工艺参数本设计要实现的各项指标和相关的工艺参数如表1和表2所示:3、放大器设计3.1 全差分套筒式放大器拓扑结构与实际电路图1 全差分套筒式放大器拓扑结构图2 最终电路图3.2 设计过程在图1中,Mb1和M9组成的恒流源为差放提供恒流源偏置,且M1,M2完全一样,即两管子所有参数均相同。

Mb2、M7和M8构成了镜像电流源,M5、M6和M7、M8构成了共源共栅电流源,M1、M2、M3、M4构成了共源共栅结构,可以显著提高输出阻抗,提高放大倍数(把M3的输出阻抗提高至原来的(gm3 + gmb3)ro2倍。

但同时降低了输出电压摆幅。

为了提高摆幅,控制增益,在套筒式差分放大器输出端增加二级放大。

本设计中功率上限为10mW,可以给一级放大电路分配3mA的电流。

设计要求摆幅为3V,所以图1中M1、M3、M5、M9的过驱动电压之和不大于1.8-3/2=0.3V。

我们可以平均分配每个管子的过驱动电压。

根据漏电计算流公式(1)(考虑沟道长度调制效应),可以计算出每个管子的宽长比。

I D=12μn C ox WL(V GS−V TH)2(1+λV DS)(1)其中,C ox等于ε/t ox,μn和t ox可以从工艺库中查找。

4、仿真结果经过调试优化之后的仿真结果如以下各图所示:图3 增益及相位裕度从图中可以看出,本设计的低频增益达到了74.25dB,达到了预期要求。

3dB 带宽为35kHz左右,比较小,可见设计还有改进的余地。

当CL为2pF时,相位裕度:PM=180°+∠βH(ω)=180°−125.5°=54.5°电源电压为1.8V时,输出摆幅如下图所示,达到了3V。

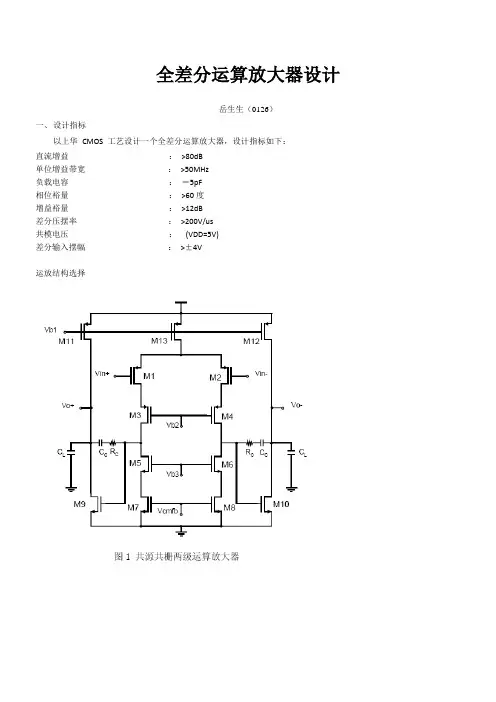

全差分运算放大器设计岳生生(0126)一、设计指标以上华CMOS 工艺设计一个全差分运算放大器,设计指标如下:直流增益:>80dB单位增益带宽:>50MHz负载电容:=5pF相位裕量:>60度增益裕量:>12dB差分压摆率:>200V/us共模电压:(VDD=5V)差分输入摆幅:>±4V运放结构选择运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。

如图2所示;(b )折叠共源共栅,folded-cascode 。

如图3所示;(c )共源共栅,telescopic 。

如图1的前级所示。

本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT NV之和小于,输出端的所有PMOS 管的,DSAT PV之和也必须小于。

对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。

另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。

考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。

两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。

性能指标分析差分直流增益 (Adm>80db)该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12)第一级增益 1351113571135135753()m m m o o o o o m m m m o o o o m m g g g g g g G A R r r r r g g r r r r=-=-=-+P第二级增益92291129911()m o o o m m o o g g G A R r r g g=-=-=-+P 整个运算放大器的增益:4135912135753911(80)10m m m m overallo o o o m m o o dB g g g gAA A g g g gr r r r ==≥++差分压摆率 (>200V/us )转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。

全差分运算放大器设计全差分运放(Fully-Differential Amplifier,简称FDA)是一种特殊的运放,它具有两个差动输入和两个差动输出。

全差分运放具有许多优点,包括良好的共模抑制和电源抑制比,适用于高精度传感器信号放大、功率放大和模拟信号处理等领域。

在这篇文章中,我将介绍全差分运放的设计原理和步骤。

首先,我们需要确定设计的要求和规范。

这包括增益要求、带宽要求、电源电压和输入输出电阻等参数。

根据这些要求,我们可以选择合适的运放器件和电路拓扑。

全差分运放的常见电路拓扑有两级差分放大器、共射共源放大器和增益交换放大器等。

在这里,我们以两级差分放大器为例进行设计。

第一步是选择运放器件。

我们需要根据设计要求选择适合的运放器件,可以根据其增益带宽积、供电电压范围和失调电流等参数进行选择。

一般来说,我们可以选择低失调电流、高增益带宽积和低电压噪声的器件。

第二步是确定电路拓扑。

在两级差分放大器中,第一级是差分放大器,第二级是共射共源放大器。

差分放大器的作用是提供高输入阻抗和共模抑制比,共射共源放大器的作用是提供电流放大和驱动能力。

由于这两级放大器要分别满足不同的要求,我们可以选择不同的放大倍数和器件参数来优化电路性能。

第三步是确定偏置电路。

偏置电路的作用是提供恒定的工作电流,这可以通过电流源和电阻网络来实现。

偏置电流的选择要根据运放器件的要求和特点,可以使用恒流源或电流反馈等方法来实现。

第四步是确定反馈电路。

反馈电路的作用是控制放大倍数和增益稳定性,可以使用电阻、电容或者电流源等元件来实现。

选择适当的反馈方式可以减小失调电压和非线性,提高性能。

第五步是进行电路仿真和优化。

通过电路仿真,我们可以验证设计的性能和满足要求。

优化可以通过调整电路参数和进行迭代仿真来实现,以达到设计要求。

第六步是进行电路布局和线路板设计。

在设计布局时,要注意分离放大器电路和干扰源,减少电源和信号线的串扰。

线路板设计要保证差分信号走线的对称性和阻抗匹配,以提高传输性能。

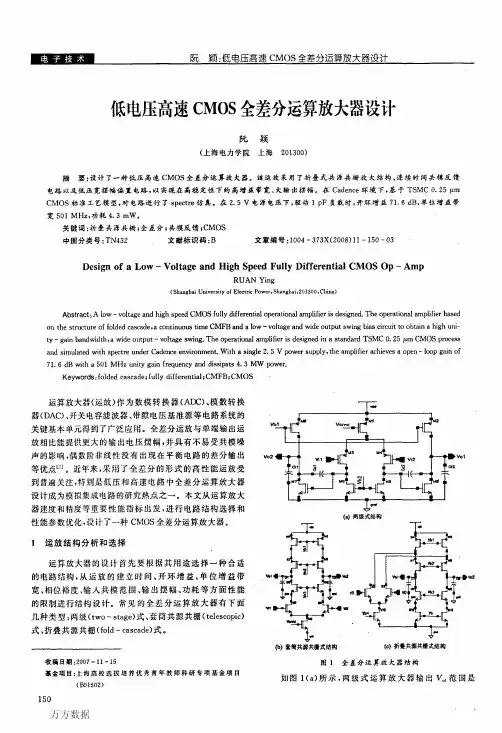

第28卷 第2期2005年6月电 子 器 件Chinese Journal of Elect ron Devices Vol.28 No.2J un.2005Analysis and Design of Fully Differential G ain 2Boosted OpampW A N G J i n 1,Q I U Yu 2li n 1,T I A N Ze21.I nstit ute of Microelect ronic of Chinese A cadem y of S ciences ,Bei j ing 100029,China;2.Depart ment of Elect ronic Science ,N ort hwestern Universit y ,X i ’an 710069,ChinaAbstract :The gain 2boosting technology is presented and analyzed.Wit h gain 2boosting ,a f ully differential gain 2boo sted telescopic cascode opamp is propo saled and designed.The main opamp is a f ully differential telescopic opamp and has a switched capacitor CM FB circuit.The boo sting opamp is a f ully differential fol 2ded cascode opamp and has a co ntinuous time CM FB circuit.The opamp is designed in SM IC 0.35μmixed 2signal CMOS p rocess wit h 3.3V power supply and achieved a dc gain of 129dB wit h a 161M Hz unity gain f requency.K ey w ords :f ully differential ,gain 2boo sted ;opamp EEACC :1220全差分增益提高运算放大器的分析与设计王 晋1,仇玉林1,田 泽21.中国科学院微电子研究所,北京,100029;2.西北大学电子科学系,西安,710069收稿日期:2004212203作者简介:王 晋(19732)男,博士研究生,主要从事模拟集成电路和混合集成电路设计,wangjin0215@ ;仇玉林(19422)男,研究员、博士生导师,wangjin0215@摘 要:通过增益提高技术,一个全差分增益提高套筒式共源共栅运算放大器被提出和设计。

设计报告——全差分放大电路设计姓名:李国锋单位:中科院半导体所1. 设计指标Supply VDD3.3V Dynamic range at output (DR) >=70dB Closed-loop gain2 Feedback capacitance(C F ) 0.5pF Load capacitance(C L ) 3pF Settling accuracy <=0.05% Settling time(ts)<=25ns Differential AC Loop Phase Margin>45。

Differential AC Loop Phase Margin >60。

Power consumption as low as possible technology process CSMC (CMOS 0.18um)2.放大器结构的选择2.1整体闭环电路的拓补结构图12.2半边等效电路图2 电容Cs 的大小可从下式得出:由闭环增益,得2=vf A pF pF C A C f vf s 15.0*2*=== 电容Cp 可以估计为:0.5p C pF =2.3 参数的初步估算2.3.1 开环增益的确定:建立误差由两部分组成:一是增益有限造成的静态误差,二是由于运放工作速度造成的动态误差。

由图2,根据基尔霍夫定律可以建立起以下公式333()*()in s P out F V V C s V C s V V C −−=−s '33**1m oout o LG r V V A V r sC ==+由以上方程可以得到:()*(1out s m oin F m o s F p o L V C G r V C G r C C C r sC =−++++)设静态误差是0.02%2=vf A *99.98%actual =2 *99.98%()()s m o s F m o s F p F s F p C G r C AA C G r C C C C A C C C ==−+++−+++得到A=199962.3.2增益带宽积GBW 的确定 2.3.2.1 确定主极点p w主极点 可以根据运放工作速度造成的动态误差确定p w 1/1/out ZinP V s w AV s w −=−+到时域变成()11p w t pactual z w u t A e w−⎛⎞⎛⎞=−+⎜⎟⎜⎟⎜⎟⎝⎠⎝⎠当t=25ns 时,误差小于0.05% 推出320p w M =2.3.2.2 确定GBW/2*p w GBW πβ= 其中14F s F p C C C C β==++需要引起高度注意的是β是1/4,而不是1/2。

全差分CMOS运算放大器的设计全差分CMOS运算放大器(Fully Differential CMOS Operational Amplifier)是一种常用于模拟、混合信号和通信电路中的放大器。

全差分运算放大器结合了差分放大器和普通运算放大器的优点,具有更好的共模抑制、抗干扰能力和更高的增益。

1.设计差动放大器:差动放大器是全差分CMOS运算放大器的核心部分,其一般由两个输入差分对和一个负载电阻组成。

在设计差动放大器时,首先需要确定放大器的增益、带宽和功耗等要求。

然后,选择适当的晶体管尺寸和偏置电流来满足这些要求。

2.设计电流镜:电流镜主要用于稳定差动放大器的工作点。

常用的电流镜电路有P型电流镜和N型电流镜。

在设计电流镜时,需要考虑放大器的输入阻抗、输出阻抗和功耗。

3.设计共模反馈电路:共模反馈电路主要用于提高全差分CMOS运算放大器的共模抑制比。

在设计共模反馈电路时,需要确定合适的电压分压比例和电容值,以及选择合适的晶体管尺寸和偏置电流。

4.偏置电流源设计:5.电源设计:6.输入和输出接口设计:7.稳定性分析和优化:在设计全差分CMOS运算放大器时,还需要进行稳定性分析和优化。

常用的稳定性分析技术有迭代法、校正法和频率响应法。

稳定性优化技术有补偿电容法、极点分布法和增益调整法。

8.仿真和验证:最后,设计完成的全差分CMOS运算放大器需要进行仿真和验证。

常用的仿真和验证工具有SPICE软件、电路仿真器和实验测量仪器。

通过仿真和验证,可以评估放大器的性能和电路的可靠性。

最后,需要注意的是,在进行全差分CMOS运算放大器的设计时,应遵循设计规范和标准,如功耗规范、电压规范和噪声规范,以确保设计的可靠性和一致性。

同时,应密切关注工艺制程、温度变化等因素对电路性能的影响,并进行相应的校准和补偿。

最完整的全差分运算放大器设计全差分运算放大器是一种特殊的运算放大器,它采用了差模输入和差模输出的电路结构,能够获得更高的共模抑制比和更好的抗干扰能力。

在本文中,我们将详细介绍全差分运算放大器的设计步骤和关键考虑因素。

首先,我们需要确定设计的目标和规格。

这包括放大器的增益、带宽、输入和输出阻抗等参数。

在设计全差分运算放大器时,通常需要考虑放大器的直流特性和交流特性。

接下来,我们将详细介绍全差分运算放大器的设计步骤。

1.选择工作点:为了实现差模输入和差模输出,我们需要选择适当的工作点。

一个常用的方法是将输入差模信号的平均值调整到放大器的线性工作区域,这可以通过调整偏置电流源和电阻来实现。

2.设计输入级:输入级通常采用差模对称结构,包括差模差分放大电路和公模放大电路。

在设计差模差分放大电路时,需要选择合适的晶体管,并确定电流增益。

公模放大电路的设计要考虑与差模放大电路的匹配。

3.设计输出级:输出级通常采用差模共源结构。

在设计输出级时,需要确定合适的负载电阻和电流源,并考虑稳定性和功率消耗等因素。

4.频率补偿:全差分运算放大器的频率响应通常需要进行补偿。

一种常用的方法是使用频率补偿电容和电阻,以提高放大器的带宽和稳定性。

5.抑制共模信号:全差分运算放大器的一个重要特性是能够抑制共模信号。

为了实现更好的共模抑制比,我们可以采用一些技术,如共模反馈、差模共源结构等。

在设计全差分运算放大器时,需要考虑一些关键因素。

首先是热噪声和干扰的抑制。

由于全差分运算放大器的输入端采用了差模输入,它能够抑制共模干扰和热噪声。

其次是功耗的控制,尽量减小功耗,提高能效。

还要注意防止震荡和保证放大器的稳定性。

综上所述,全差分运算放大器设计需要考虑许多因素,包括放大器的增益、带宽、输入和输出阻抗等参数。

在设计过程中,需要选择合适的工作点、设计合适的输入级和输出级、实施频率补偿,并考虑共模抑制和稳定性等因素。

通过合理的设计和优化,我们可以获得一个高性能的全差分运算放大器。

对于全差分放大器,一般可以得到更大的swing (由于差分信号),同时可以实现对共模干扰、噪声以及偶数阶的非线性的抑制;但其需要有两个匹配的反馈网络,以及共模反馈电路顺便提一下,对于全差分的折叠共源共栅(folded cascode)放大器,需要注意转换速率(正向与负向)对输入对差分对的尾电流源和cascode电流源的考虑非主极点的位置–输入对管的drain节点(注意全差分没有镜像极点的问题..),如果考虑PMOS输入的结构,将会折叠到n管的cascode,从而减小此节点阻抗,提高此非主极点的频率;但是P输入结构亦有其问题,如直流增益和cmfb电路的速度(考虑cmfb控制的为cascode的pmos电流源)关于共模反馈CMFB从反馈环路来看,共模的稳定问题来源于闭环的共模增益:由于输入差分对的尾电流源的local-feedback,通常共模增益较小,导致运放无法控制其输出共模点;通过CMFB共模反馈电路,可以提高共模反馈环路的增益,以稳定共模信号。

设计CMFB需考虑补偿以减小环路的稳定时间(settling time)和提高稳定性。

从性能上,我们希望共模反馈的单位增益带宽足够大,但由于cmfb的环路相较于差模通路可能有更多高频极点,故此在一定的功耗要求下其UGB一般比较难做的高,有书中提到可以将其设计为差模UGB 的1/3一般共模反馈的方法是控制放大器的电流源,这里如果是folded-cascode的结构,可以考虑用cmfb控制cascode的电流源而不是输入差分对的电流源—-因其在共模环路中有较少的节点–>更容易补偿等..(另一种考虑是控制尾电流源可能导致共模增益的问题)另外,对于cmfb控制的尾电流源,常见将尾电流源分为两半,其中之一由cmfb控制,另一半接恒定偏置电流;这种结构的具体分析可见Gray书12.4.2节的内容,简单来说,single-stage的opamp中控制尾电流源的cmfb结构,其UGB主要为gmt/CL, 其中gmt为尾电流源的跨导,这里拆分尾电流源来减半cmc共模控制的部分,这样UGB减小,即缩减带宽来提升共模反馈环路的相位裕度,当然cmfb的增益相应也减小了;另外恒定偏置部分也可帮助共模电压的初始建立,减小cmfb大的扰动。

基于CMOS全差分运算放大器的全集成有源滤波器的设计_解读全集成有源滤波器是一种基于CMOS全差分运算放大器的滤波器设计,通过集成电路的方式实现滤波器的功能。

CMOS全差分运算放大器具有低功耗、高增益、高输入阻抗和低输出阻抗的特点,适合用于滤波器设计。

在全集成有源滤波器的设计中,首先需要确定滤波器的类型和性能要求,包括截止频率、通带增益、阻带衰减等。

选择合适的滤波器类型可以根据实际应用需求,常见的有低通滤波器、高通滤波器、带通滤波器和带阻滤波器等。

以设计一个低通滤波器为例,设计流程如下:首先确定滤波器的截止频率。

截止频率是滤波器的特征参数之一,决定了滤波器的频率响应。

根据实际需求选择合适的截止频率。

然后确定滤波器的阶数。

滤波器的阶数决定了滤波器对信号的衰减速度。

一般而言,阶数越高,滤波器的陡峭度越高,但相应的设计复杂度也增加。

根据实际需求选择合适的阶数。

接下来根据截止频率和阶数的要求,可以利用标准滤波器设计方法进行设计。

常用的设计方法有巴特沃斯法、切比雪夫法、椭圆法等。

每种方法的特点和性能各有不同,根据实际需求选择合适的设计方法。

设计完成后,需要根据选择的CMOS全差分运算放大器,进行电路图设计和电路参数计算。

CMOS全差分运算放大器的电路图包括输入级、差动放大级和输出级等。

通过合理的设计和参数选择,实现所需的滤波器增益和频率特性。

最后,进行电路模拟和性能分析。

利用仿真工具对设计的滤波器进行电路模拟和分析,验证滤波器的性能是否符合预期要求。

如果需要,可以进行电路参数的微调和优化。

总结起来,基于CMOS全差分运算放大器的全集成有源滤波器的设计是一个系统性的工程,包括滤波器类型选择、截止频率和阶数的确定、设计方法选择、电路图设计和电路参数计算等。

通过合理的设计和参数选择,可以实现满足实际应用需求的滤波器。

全差分运算放大器结构框图解析常见的全差分运算放大器电路分析全差分(运算放大器)就是一种具有差分输入,差分输出结构的运算(放大器)。

(差分放大器)相对于单端输出的放大器具有如下一些优势。

首先,由于随着CMOS 工艺尺寸不断缩小,从0.5μm 减小至0.35μm,0.18μm,90nm,(芯片)的(供电)电压也不断减小从5V降到3.5V,1.8V,1.2V甚至更低。

在如此低的供电电压的情况下,单端输出的运算放大器很难能理想地工作,为了保证电路能够得到足够大的(信号)摆幅,我们需要采用全差分的运算放大器结构。

其次,全差分运算放大器能够有效抑制电路的共模信号,并且能够减小电路的偶次谐波失真。

但是为了得到这些性能,全差分运算放大器需要一个共模反馈环路来控制输出的共模电平。

理想情况下,这个共模反馈控制环路会使得输出的共模电平稳定在VDD/2。

所以,一个全差分放大器通常由主放大器和共模反馈环路两部分组成,它在现代的(电路设计)中应用非常广泛。

1.全差分运算放大器结构框图共模反馈的基本思想就是由一个共模采样电路取得电路的输出共模信号,然后把共模信号与一个参考信号相比较,将比较后的误差信号放大后再输入主放大器以调节输出共模电压。

对于输入的差分信号来说,共模反馈环路不会对交流信号产生影响,相当于说共模环路对于交流是开路的。

所以,电路的差分增益和相位就由主放大器决定。

但是,对于输入的共模信号,共模反馈环路决定了输出的共模电平,这时,共模环路的增益和相位就会对电路的输出共模电平的精度和稳定性产生影响。

全差分放大器在应用中的一种电路形式,差分输出的信号摆幅vO1-vO2 为单端信号vO1(vO2)摆幅的两倍,所以在输出端可以有较大的输出动态范围,相对于单端输出提高了处理信号的幅度能力。

2. 常见的全差分运算放大器电路(a)是普通的全差分放大器电路,通常作为一个放大器的输入级部分。

图7-3(b)是折叠式全差分运算放大器电路,它的增益会比较大,可以达到60~70dB,但同时会消耗比较大的功耗,因为它有四条支路需要(电流)。

0中国集成电路设计♦China lntegrated Circult一种具有高增益和超带宽的全差分跨导运算放大器罗杨贵1,曾以成1,邓欢2,唐金波21.湘潭大学物理与光电工程学院;2.湖南毂梁微电子有限公司摘要:基于GSMC0.18um CM OS工艺,设计了一种应用于12位ADC的全差分运算放大器。

为了提高增益,在套筒式共源共栅结构上运用了增益提高技术。

为了提高输入跨导,采用隔离效果更好的深N阱CMOS作为输入端,从而提升增益带宽。

为了降低功耗,利用单端放大器作为辅助运放。

整体电路结构简单优化。

仿真结果表明,运算放大器直流开环增益大于100dB,单位增益带宽大于800M H z,相位裕度大于70毅,完全满足目标ADC的性能要求,是一种新型且质量较高的运放,也可应用于其它场合。

关键词:增益提高;套筒式共源共栅;高增益带宽;深N阱中图分类号:TN432文献标识码:AA Fully Differential Transconductance Operational Amplifierwith high Gain and ultra GBWLUO Yang-gui,ZENG YirCheng1,DENG Huan2,TANG Jn-bo21.SchoolofPhysicsand Opibe]ectronics,X iangtan University;2.H unan Greai-Leo M icroe]ectronicsCO.LTDAbstract:Based on theGM SC0.18um CM OS process,a fuUy differentialoperationalam plifierlbr12-bitADC is designed.In orderto increase the gain,a gain-enhancing technique is used on the te]escopic cascode structure.In order to increase input transconductance,the deep N-W elltansistorwith better isolation function was used as the input,thereby to enhance the gain bandwidth.In order to reduce power consumption,a single-ended amplifier is used as an auxiliary operational amplifier.The overall circuit structure is simple and optimized.The simulation results show that the operational amplifier DC open-loop gain is greater than100dB,the unity gain bandwidth is greater than800MHz, and the phase margin is greater than70毅,which fully meets the performance requirements of ADC.It is a new and high-quality operational amplifier that can also be applied to other applications.Keywords:Gain enhancement;Telescopic cascode;High gain bandwidth;Deep N_well0引言模数转换器作为连接模拟信号与数字信号的桥梁,越来越显示出其重要性。

一个全差分运放电路的设计王彦、嵇楚内容安排• • • • • 1)运放的设计要求 2)结构的选取 3)参数计算 4)仿真结果 5)性能指标• • • • • • • • • • • •DC gian: Gain Bandwidth: Loading: Phase margin: Gain margin: Slew rate: Common mode: GBW of CMFB: Equivalent input noise: Input offset voltage: Output swing:一、设计要求(spec)>80dB >50Mhz =5pF >60 degree >12dB 200V/us 2.5 V(VDD = 5V) >10 Mhz <20 nV / Hz <10 mv > ± 2v (each output)二、电路结构三、参数计算• 1)由Slewrate(200V/us)和C L (5pF) 确定各路 • 电流: 采用R、C电容补偿的方法,选取 C C=2pF 输入级决定的Slewrate: I4 SRrise = CC ,得: I 4 = 400 µ A ,I 9 = 400µA 输出级决定的Slewrate:SR fall = I6选取Cfb =1pf,得:C Ltotal=I6 CC + C L + C fbI 6 = 1.6mA2)输入级跨导gm1选取• DC gain>80dB,AV 0 = 2 × AV 1 × AV 2 = 2 × g m1 g m5 g g m5 × ≈ 2 × m1 × 1 g g ds 3 g + g + 1 g ds 3 + ds 2 g ds1 g ds 5 + g ds 6 + ds 5 ds 6 R fb R fb gm2其中:g ds = λI ds =VE I ds L另外,由于miller电容补偿效应,主极点P1 ≈ g ds 3 2π * AV 2 C C g m1 > 50 MHz 2π C C GBW = AV 1 × AV 2 × P1 ≈g m1 > 6.28 *10 −4 −4 取: g m1 = 7 *103)输出级跨导gm5的选取• 输出级引入次极点Cc Vin Cp +ROA为输入级的寄生电容VoCL + CfbF=CC CC + C PP2 ≈0g m5 CC 2π(C L + C fb ) CC + C PGBWGBW ) > 600 θm = 90 − arctan( P 2 GBW gm1 CL + Cfb 1 = < P gm5 CC 3 2Phase MarginP2P1g m 5 > 3 3 g m1取g m 5 = 8 * g m1 = 56 *10 −44)管子参数的选取• 由模型文件提供:µ nCox = 95 *10 −6 µA / V 2 µ p Cox = 31*10 −6 µA / V 2 VTp ≈ −1V VTn ≈ 0.73V4)M1、M5、M7管子的 选 择W Lg m1(A,B) = 2βI1 = β I 5( W1 40 ) A, B = L1 1W7 20 ( ) A, B = L7 1(W7 40 )C = L7 1g m 5 ( A, B ) = 2βI 6W5 103 ( ) A, B = L5 14)M4、M6、M9管子的 选择W L• 由于output-swing>4V,取电流源的饱 V 和压降为0.5V: DSAT 6 = 0.5W6 2 1 I 6 = µ p Cox VDSAT 2 L6W6 400 ( ) A, B = L6 1W4 100 = L4 1W9 100 = L9 1四、仿真结果1)••••5VG Ω5)Input offset voltage•计算出各管的域值电压偏差和相应的宽长比偏差,代入model和网表后,采用montecarlo法分析,输入电压一端固定为2.5V,另一端则以2.5V为基准进行DC扫描,当输出为2.5V时,相应的扫描电压va即为失调电压。

全差分运算放大器设计岳生生(6)一、设计指标以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下:✧直流增益: >80dB✧单位增益带宽: >50MHz✧负载电容:=5pF✧相位裕量: >60度✧增益裕量: >12dB✧差分压摆率: >200V/us✧共模电压: 2.5V (VDD=5V)✧差分输入摆幅: >±4V二、运放结构选择运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。

如图2所示;(b )折叠共源共栅,folded-cascode 。

如图3所示;(c )共源共栅,telescopic 。

如图1的前级所示。

本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT NV之和小于0.5V ,输出端的所有PMOS管的,DSAT PV之和也必须小于0.5V 。

对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。

另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。

考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。

两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。

三、性能指标分析1、 差分直流增益 (Adm>80db)该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益1351113571135135753()m m m o o o o o m m m m o o o o m m g g gg gg G A R r rr r g g r r r r=-=-=-+第二级增益92291129911()m o o o m m o o gg G AR r rgg=-=-=-+整个运算放大器的增益:4135912135753911(80)10m m m m overallo o o o m m o o dB g g g gAA A g g g gr r r r ==≥++2、 差分压摆率 (>200V/us )转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。

全差分运算放大器设计岳生生(6)一、设计指标以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下:✧直流增益:>80dB✧单位增益带宽:>50MHz✧负载电容:=5pF✧相位裕量:>60度✧增益裕量:>12dB✧差分压摆率:>200V/us✧共模电压:2.5V (VDD=5V)✧差分输入摆幅:>±4V二、运放结构选择运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。

如图2所示;(b )折叠共源共栅,folded-cascode 。

如图3所示;(c )共源共栅,telescopic 。

如图1的前级所示。

本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT NV之和小于0.5V ,输出端的所有PMOS管的,DSAT PV之和也必须小于0.5V 。

对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。

另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。

考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。

两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。

三、性能指标分析1、 差分直流增益 (Adm>80db)该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益1351113571135135753()m m m o o o o o m m m m o o o o m m g g gg ggG A R r r r r g g r r r r=-=-=-+P第二级增益92291129911()m o o o m m o o gg G AR r r gg=-=-=-+P整个运算放大器的增益:4135912135753911(80)10m m m m overallo o o o m m o o dB g g g gAA A g g g gr r r r ==≥++2、 差分压摆率 (>200V/us )转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。

定义转换速率SR :1)、输入级: max1max|2|Cc out DS CCd SR dtI v I CC===单位增益带宽1m uCg C ω=,可以得到1m CugC ω=所以 11111112222DS DS DS u ueff uDS Cm eff SR I I IV g I CVωωω====其中1eff GS th VV V =-=因此提高两级运算放大器转换速率的可以尽可能增大管子M1的有效电压1eff V。

2)、输出级:max9max|2|Cc out DS CCLd SR dtIv I CC C===+该运算放大器的转换速率139min ,2DS DS C C L SR I I C C C ⎧⎫⎪⎪=⎨⎬+⎪⎪⎩⎭3、 静态功耗:该运放没有功耗指标,这里我们以15mW 为例简单分析。

运放的静态功耗()()91013staticDS DS DS dd ss V V PI I I =-++静态功耗确定了整个电路的静态电流最大值:15350staticDC ddssmwmA V VPI VV ==≈--我们将该电流分配到电路的不同地方。

例如,100ua 给偏置电路,2900ua 归两级放大电路。

4、 相位裕度 >60度,单位增益带宽>40MHz假设运放只有两个极点P1、P2。

(实际上,会有更多的极点,同时还会在右半平面或者左半平面的零点)。

由于密勒补偿电容Cc 的存在, P1和P2将会分开很远。

假设12p p ωω=,这样在单位增益带宽频率uω处第一极点引入-90度相移,整个相位裕度是60度。

所以第二极点在单位增益带宽频率处的相移为-30度。

22212160,90,18030tan 300.577 1.73,2p p up uuPM PM ϕϕϕωωωωωω≥≈=--≤≤=⇒≥o o ooo取=另外,主极点235713573553901195399011()()(1)o o o o o o o m m m m o p Cm m m m Co g g g g ggggg gr rr r g g g g CC g gω++≅≅++o1+,开环增益1359135753911m m m m oo o o o m m o o g g g g A g g g gr r r r =++110m up CgA Cωω==为得到高的单位增益带宽,应该使非主极点2p 最大化。

5、 共模负反馈:CMFB对于全差分运放,为了稳定输出共模电压,应加入共模负反馈电路。

在设计输出平衡的全差分运算放大器的时候,必须考虑到以下几点:✧ 共模负反馈的开环直流增益要求足够大,最好能够于差分开环直流增益相当; ✧ 共模负反馈的单位增益带宽也要求足够大,最好接近差分单位增益带宽; ✧ 为了确保共模负反馈的稳定,一般情况下要求进行共模回路补偿; ✧ 共模信号监测器要求具有很好的线性特性;✧ 共模负反馈与差模信号无关,即使差模信号通路是关断的。

该运算放大采用连续时间方式(Continuous-Time Approach )来实现共模负反馈功能。

如图4所示。

该结构共用了共模放大器和差模放大器的输入级中电流镜及输出负载。

这样,一方面降低了功耗;另一方面保证共模放大器与差模放大器在交流特性上保持一致。

因为共模放大器的输出级与差模放大器的输出级可以完全共用,电容补偿电路也一样。

只要差模放大器频率特性是稳定的,则共模负反馈也是稳定的。

这种共模负反馈电路使得全差分运算放大器可以像单端输出的运算放大器一样设计,而不用考虑共模负反馈电路对全差分放大器的影响。

6、电压偏置电路:宽摆幅电流源(如图5所示)在共源共栅输入级中需要三个电压偏置,为了使得输入级的动态围大一些,图中的宽摆幅电流源来产生所需要的三个偏置电压。

根据宽摆幅电流源的设计要求,必须满足:12356137814410111244B B B B B B B B B B B B B W W W L L L W W W W W W W L L L L L L L W W W L L L ⎛⎫⎛⎫⎛⎫== ⎪ ⎪ ⎪⎝⎭⎝⎭⎝⎭⎛⎫⎛⎫⎛⎫⎛⎫⎛⎫⎛⎫⎛⎫====== ⎪ ⎪⎪ ⎪ ⎪ ⎪ ⎪⎝⎭⎝⎭⎝⎭⎝⎭⎝⎭⎝⎭⎝⎭⎛⎫⎛⎫⎛⎫== ⎪ ⎪ ⎪⎝⎭⎝⎭⎝⎭ 7、 Miller 补偿电阻电阻Rc 可以单独用来控制零点的位置,主要有以下几种方法: I 、 将零点搬移到无穷远处,消除零点,Rc 必须等于91/m g 。

II 、 把零点从右半平面移动到左半平面,并且落在第二极点2p ω上。

这样,输出负载电容引起的极点就去除了。

这样做必须满足以下条件:291911()m z p LC Cm gCC R gωω=→=--得到电阻值为91(1)L C Cm C R gC=+III 、 把零点从右半平面移动到左半平面,并且使其稍微大于单位增益带宽频率uω。

比如超过20%1.2zu ωω>因为21911,m C p u u CCLm g R g CCR ωωω→≈=-?并且得到电阻值为111.2C m R g≈四、手工计算在0.6um 工艺库文件中得到工艺参数:22,,119/,51.7/,0.73, 1.02oxoxTH N TH P npA V A V V V CCV V μμμμ====-1、 确定Miller 补偿电容为了保证相位裕量有60度,我们要求第二极点2p ω和零点zω满足以下两个条件:9191210,210,2m m m m z u p u ccLcg g g g CC CCωωωω≥≥→≥≥则,0.20.251CL pF pF CC ≥=⨯=.这里,我们取Cc =2PF 。

2、 确定两级放大器中的工作电流共模负反馈的输入端电流与差模输入端相同,因此输入级的工作电流()1222100/2133.3333DS C SR V us pf uA C I ⎛⎫=⋅=⋅= ⎪⎝⎭ 由于有一些寄生电容,预留一些余量,我们取1200DS uA I=,则,14,13400DS DS uA I I ==。

输出级工作电流为,()11100/88002DS CL CMFB SRV us pf uA C C C I =++=⋅=。

同样,由于一些寄生电容,预留一些余量取11900DS uA I=。

3、 计算放大管的跨导mg根据全差分Slew Rate 要求,111111131.523322DS DS u DS u eff uDS Cm eff SR I I I V gI CVωωω=⨯===M1管的有效电压,6122200/0.42533 6.285010eff u SR V usV V ω⨯===⨯⨯⨯ M2管的跨导1111222000.9420.425DS m eff uAm VI gV-⨯===Ω()1216621210.94286um42.9,2um251.71020010m m W W W W L L L L g ---=Ω⎛⎫⎛⎫⎛⎫⎛⎫→==== ⎪ ⎪ ⎪ ⎪⨯⨯⨯⨯⎝⎭⎝⎭⎝⎭⎝⎭取=。

根据第二极点是单位增益带宽的两倍,91222m m u Lcgg pCCω=→=M9管的跨导 31190.94210225 4.712m Lm cpf m pfg g C C--⨯=⨯⨯=⨯⨯=Ω()216699 4.71103.621191090010m m W L g ---Ω⎛⎫=→== ⎪⨯⨯⨯⨯⎝⎭。

取91001W umL um ⎛⎫= ⎪⎝⎭,M9管的有效电压9199229000.3824.71DS eff m uA V m I V g-⨯===Ω 4、 电流源偏置管和Cascode 管的尺寸假定电流源偏置管M13、M11、M12、M7和M8,和Cascode 管M3-M6的有效电压Veff =0.3V ,这样可以计算出所有管子的尺寸参数。

假定130.3eff V V =,则613621313240010174251.7100.32DS eff oxW L p I Cu V--⨯⨯⎛⎫=== ⎪⨯⨯⎝⎭ 11111112131112131399390391.5,441DS DS W W W W W W um L W L L L L L um L I I⎛⎫ ⎪⎛⎫⎛⎫⎛⎫⎛⎫⎛⎫⎝⎭==→=====⎪ ⎪ ⎪ ⎪ ⎪⎛⎫⎝⎭⎝⎭⎝⎭⎝⎭⎝⎭ ⎪⎝⎭ M11-M12管子的有效电压,11120.3eff eff V VV ==假定70.3eff V V =,则676277872300106056.0,2119100.312DS eff oxW W W um L L L um n I C V μ--⨯⨯⎛⎫⎛⎫⎛⎫===== ⎪ ⎪ ⎪⨯⨯⎝⎭⎝⎭⎝⎭ 假定50.3eff V V =,则656255652300106056.0,2119100.312DS eff oxW W W um L L L um n IC V μ--⨯⨯⎛⎫⎛⎫⎛⎫===== ⎪ ⎪ ⎪⨯⨯⎝⎭⎝⎭⎝⎭ 假定30.3eff V V =,则63623343230010129128.9,51.7100.3122DS eff oxW W W umL L L um p I C V μ--⨯⨯⎛⎫⎛⎫⎛⎫=====⎪ ⎪ ⎪⨯⨯⎝⎭⎝⎭⎝⎭ Cascode 管M3的跨导为,61333223001020.3DS m eff m I gV--⨯⨯===Ω5、 Miller 补偿电阻Rc 的确定我们将零点从右半平面移到左半平面,并且使其为单位增益带宽频率uω的1.2倍,则118851.2C m R g==Ω6、 偏置电路的管子尺寸根据所有MOS 的有效电压,我们可以计算出配置电压Vb1-Vb4的值。