清华大学数字集成电路作业一

- 格式:pdf

- 大小:189.55 KB

- 文档页数:1

2011-2012《数字VLSI 》第四次课程作业

(一) 请计算P 型树动态逻辑反相器的上拉逻辑努力(g )和本征延时(p),并与

NMOS 管驱动能力减半的HI-skew 反相器的上拉逻辑努力与本征延时进行比较。

假设标准反相器的PMOS 和NMOS 尺寸之比为2,自载系数等于1。

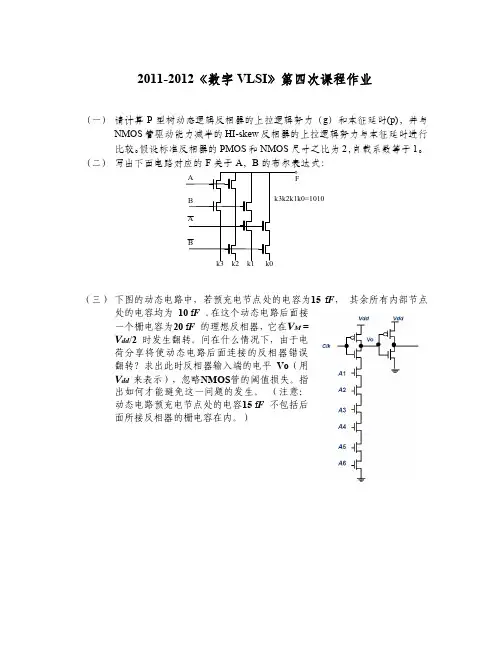

(二) 写出下面电路对应的F 关于A ,B 的布尔表达式:

(三) 下图的动态电路中,若预充电节点处的电容为15 f F , 其余所有内部节点

处的电容均为 10 f F 。

在这个动态电路后面接

一个栅电容为20 f F 的理想反相器,它在V M =

V dd /2 时发生翻转。

问在什么情况下,由于电

荷分享将使动态电路后面连接的反相器错误

翻转?求出此时反相器输入端的电平 Vo (用

V dd 来表示),忽略NMOS 管的阈值损失。

指

出如何才能避免这一问题的发生。

(注意:

动态电路预充电节点处的电容15 f F 不包括后

面所接反相器的栅电容在内。

)。

清华大学数字电路题库一、填空题 : (每空1分,共10分)1. (30.25) 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

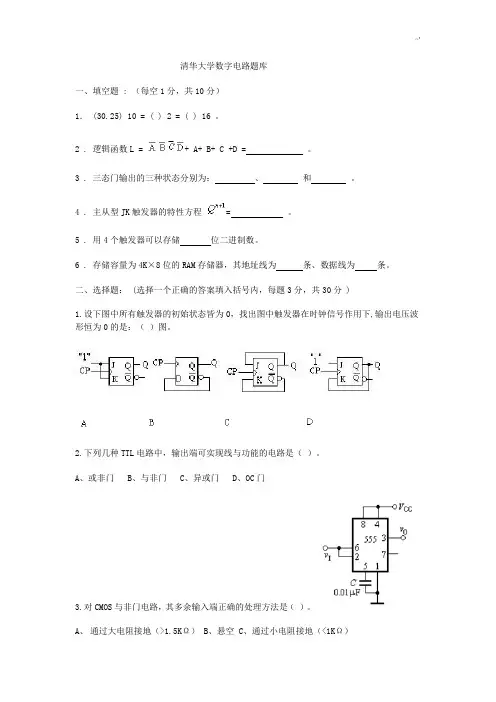

二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 )1.设下图中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。

2.下列几种TTL电路中,输出端可实现线与功能的电路是()。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>1.5KΩ)B、悬空C、通过小电阻接地(<1KΩ)B、 D、通过电阻接V CC4.图2所示电路为由555定时器构成的()。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路()。

A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是()。

A、并行A/D转换器B、计数型A/D转换器C、逐次渐进型A/D转换器B、 D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如下图所示,则该电路为()。

A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用()。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器B、D、10位D/A转换器9、已知逻辑函数与其相等的函数为()。

A、 B、 C、 D、10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

A、4B、6C、8D、16三、逻辑函数化简(每题5分,共10分)1、用代数法化简为最简与或式Y= A +2、用卡诺图法化简为最简或与式Y= + C +A D,约束条件:A C + A CD+AB=0四、分析下列电路。

![试题标准答案模版A4-数字集成电路设计A答案[1]](https://uimg.taocdn.com/b1c5702d0b1c59eef9c7b432.webp)

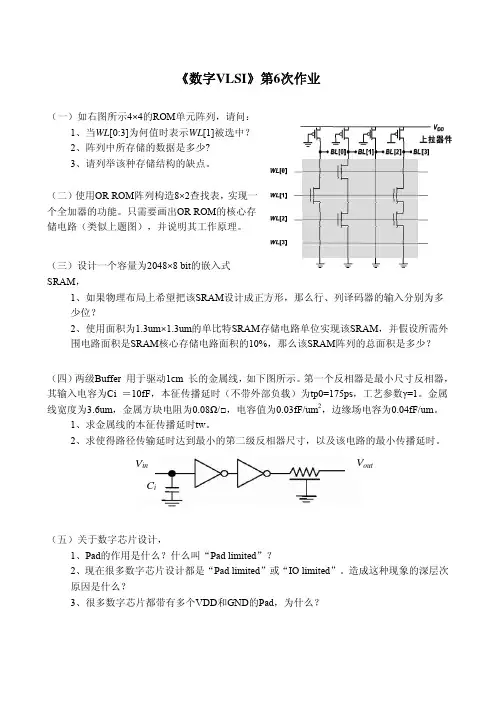

《数字VLSI 》第6次作业(一)如右图所示4×4的ROM 单元阵列,请问:1、当WL [0:3]为何值时表示WL [1]被选中?2、阵列中所存储的数据是多少?3、请列举该种存储结构的缺点。

(二)使用OR ROM 阵列构造8×2查找表,实现一个全加器的功能。

只需要画出OR ROM 的核心存储电路(类似上题图),并说明其工作原理。

(三)设计一个容量为2048×8 bit 的嵌入式SRAM ,1、如果物理布局上希望把该SRAM 设计成正方形,那么行、列译码器的输入分别为多少位?2、使用面积为1.3um×1.3um 的单比特SRAM 存储电路单位实现该SRAM ,并假设所需外围电路面积是SRAM 核心存储电路面积的10%,那么该SRAM 阵列的总面积是多少?(四)两级Buffer 用于驱动1cm 长的金属线,如下图所示。

第一个反相器是最小尺寸反相器,其输入电容为Ci =10fF ,本征传播延时(不带外部负载)为tp0=175ps ,工艺参数γ=1。

金属线宽度为3.6um ,金属方块电阻为0.08Ω/□,电容值为0.03fF/um 2,边缘场电容为0.04fF/um 。

1、求金属线的本征传播延时tw 。

2、求使得路径传输延时达到最小的第二级反相器尺寸,以及该电路的最小传播延时。

(五)关于数字芯片设计,1、Pad 的作用是什么?什么叫“Pad limited ”?2、现在很多数字芯片设计都是“Pad limited ”或“IO limited ”。

造成这种现象的深层次原因是什么?3、很多数字芯片都带有多个VDD 和GND 的Pad,为什么? C i V inV out。

Assignment1郭星宇2015E8000961083高能物理研究所电子学院9312班1.Give a formal or descriptive definition for each of the following terms.●ITRS:International technology Roadmap for Semiconductor国际半导体技术规划。

●System-level synthesis:系统级综合。

将自然语言(如英语)转化成算法表示的过程。

●Gate-Equivalent:等效门,用于衡量数字电路的复杂程度的基本单位,基于为完成一个电路功能而互独立的逻辑门数量。

●Logic synthesis:逻辑级综合。

从数据流表示转换到结构逻辑表示。

●Technology Nodes:技术结点。

用于描述半导体器件的尺寸,单位为纳米。

●Layout synthesis:版图综合。

指从逻辑门表示转换到版图表示。

●Feature size:特征尺寸。

COMS中表示工艺尺寸的参数,等于晶体管长度的一半。

●Partial design tree:设计树,包括自顶向下设计和自底向上设计两个概念。

●IC design complexity sources:集成电路设计复杂性的来源。

●Design window:设计窗口,它是指设计树中设计者所使用的层次的范围。

●Behavioral representation:行为描述。

通过定义的输入输出响应来描述的方式。

●Digital design space:数字设计空间,包括cost、speed、power dissipation。

●Abstraction hierarchy:A set of interrelation representation levels that allow a system to be represented in varying amounts of detail。

《数字集成电路基础》作业答案第一次作业1、查询典型的TTL与CMOS系列标准电路各自的VIH、VIL、VOH和VOL,注明资料出处。

2、简述摩尔定律的内涵,如何引领国际半导体工艺的发展。

第二次作业1、说明CMOS电路的Latch Up效应;请画出示意图并简要说明其产生原因;并简述消除“Latch-up”效应的方法。

答:在单阱工艺的MOS器件中(P阱为例),由于NMOS管源与衬底组成PN结,而PMOS 管的源与衬底也构成一个PN结,两个PN结串联组成PNPN结构,即两个寄生三极管(NPN 和PNP),一旦有因素使得寄生三极管有一个微弱导通,两者的正反馈使得电流积聚增加,产生自锁现象。

影响:产生自锁后,如果电源能提供足够大的电流,则由于电流过大,电路将被烧毁。

消除“Latch-up”效应的方法:版图设计时:为减小寄生电阻Rs和Rw,版图设计时采用双阱工艺、多增加电源和地接触孔数目,加粗电源线和地线,对接触进行合理规划布局,减小有害的电位梯度;工艺设计时:降低寄生三极管的电流放大倍数:以N阱CMOS为例,为降低两晶体管的放大倍数,有效提高抗自锁的能力,注意扩散浓度的控制。

为减小寄生PNP管的寄生电阻Rs,可在高浓度硅上外延低浓度硅作为衬底,抑制自锁效应。

工艺上采用深阱扩散增加基区宽度可以有效降低寄生NPN管的放大倍数;具体应用时:使用时尽量避免各种串扰的引入,注意输出电流不易过大。

2、什么是器件的亚阈值特性,对器件有什么影响?答:器件的亚阈值特性是指在分析MOSFET时,当Vgs<Vth时MOS器件仍然有一个弱的反型层存在,漏源电流Id并非是无限小,而是与Vgs呈现指数关系,这种效应称作亚阈值效应。

影响:亚阈值导电会导致较大的功率损耗,在大型电路中,如内存中,其信息能量损耗可能使存储信息改变,使电路不能正常工作。

3、什么叫做亚阈值导电效应?并简单画出logI D-V GS特性曲线。

答:GS在分析MOSFET时,我们一直假设:当V GS下降到低于V TH时器件会突然关断。

2011-2012《数字VLSI》第二次课程作业

一、在以下的电路中,假设初始状态时所有的电容电压均为零。

求当开关闭合时经

过多少时间在A点处的电压上升到1/2 V E 。

假设电路中所有的电阻都相等为R,而所有的电容也都相等为C 。

二、请根据下图的组合逻辑图完成下列优化过程:A, B, C三个信号的到达时间相同。

已知标准反相器的PMOS管与NMOS管的沟道宽度之比Wp/Wn=2, 所有逻辑门的自载系数 =1,

Z端的路径电气努力F=460.8,

(1)假设电路中所有逻辑门的尺寸系数都等于1,请找出该电路的关键路径,并给出与之对应的输入矢量。

(2)采用逻辑努力的方法对找到的关键路径进行尺寸优化:关键路径的最优级数等于几,

是否需要插入缓冲级,如需插入应插入几级?如果需要插入缓冲器,按照缓冲器加

在关键路径末端的情况,计算关键路径的最小归一化延时,并给出优化后G3的尺

寸系数;

(3)在(2)的优化结果之上,为了在不影响整体电路速度的前提下充分降低功耗,剩余

的非关键路径的延时应该设计成多少?按照这一优化目标,确定不在关键路径上的

逻辑门的尺寸系数。

请画出逻辑门G2的静态互补CMOS逻辑形式的晶体管级电路图并标出输入信号名称(不

用标晶体管尺寸),输入信号的排列应考虑延时的优化问题。

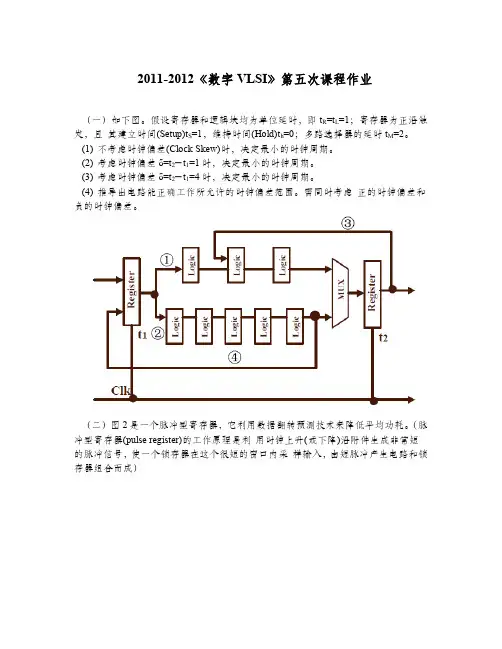

2011-2012《数字VLSI》第五次课程作业

(一)如下图。

假设寄存器和逻辑块均为单位延时,即t R=t L=1;寄存器为正沿触发,且其建立时间(Setup)t S=1,维持时间(Hold)t h=0;多路选择器的延时t M=2。

(1) 不考虑时钟偏差(Clock Skew)时,决定最小的时钟周期。

(2) 考虑时钟偏差δ=t2−t1=1时,决定最小的时钟周期。

(3) 考虑时钟偏差δ=t2−t1=4时,决定最小的时钟周期。

(4) 推导出电路能正确工作所允许的时钟偏差范围。

需同时考虑正的时钟偏差和负的时钟偏差。

(二)图2是一个脉冲型寄存器,它利用数据翻转预测技术来降低平均功耗。

(脉冲型寄存器(pulse register)的工作原理是利用时钟上升(或下降)沿附件生成非常短的脉冲信号,使一个锁存器在这个很短的窗口内采样输入,由短脉冲产生电路和锁存器组合而成)

a. 简要描述电路的工作原理。

b. 如果所有NMOS 管具有相同尺寸,所有PMOS 管也具有相同尺寸,粗略估计在多大的输入翻转概率下这个电路将比不采用数据翻转预测的电路更省功耗?

(三)下图的静态寄存器,假设原始状态Q=1,时钟上升沿到之前D=0。

为了使得时钟上 升沿到达之后,Q 的状态正确改变,I1、T2、I4的晶体管尺寸应该满足什么条件?请列出关 系式。

假设NMOS 和PMOS 的工艺增益因子分别为k n ’、k p ’,饱和电压都等于V DSA T ,阈 值电压都等于V T 。

为了简单起见,近似认为I3的输出只有在输入电压超过V dd /2时才翻转;单位尺寸传输门的导通电阻为常数R t 。

QI

B Q

I L。

2011-2012《数字VLSI》第三次课程作业1)下图为一个两输入的或非门,晶体管的尺寸如图所示,kn’=2kp’ 。

表中为考虑静态时的情形,请将噪声容限按最小至最大排列。

噪声容限最小的情形标为1,如噪声容限相同时可用同样的数字标注(请标注在表格右边的空列中。

)图12) A two-stage buffer is used to drive a metal wire of 1 cm. The first inverter is of minimum size with an input capacitance Ci=10 fF and an internal propagation delay tp0=50 ps and load dependent delay of 5ps/fF. The width of the metal wire is 3.6 μm. The sheet resistance of the metal is 0.08 Ω/□, the capacitance value is 0.03 fF/μm2 and the fringing field ca pacitance is 0.04fF/μm.a. What is the propagation delay of the metal wire?b. Compute the optimal size of the second inverter. What is the minimum delay through the buffer?c. If the input to the first inverter has 25% chance of making a 0-to-1 transition, and the whole chip is running at 20MHz with a 2.5V supply voltage, then what’s the power consumed by the metal wire?3) To connect a processor to an external memory an off -chip connection is necessary. The copper wire on the board is 15 cm long and acts as a transmission line with a characteristic impedance of 100Ω.(See Figure 2). The memory input pins present a veryhigh impedance which can be considered infinite. The bus driver is a CMOS inverter consisting of very large devices: (50/0.25) for the NMOS and (150/0.25) for the PMOS, where all sizes are in μm. The m inimum size device, (0.25/0.25) for NMOS and(0.75/0.25) for PMOS, has the on resistance 35 kΩ.a. Determine the time it takes for a change in the signal to propagate from source to destination (time of flight). The wire inductance per unit length equals 75*10-8 H/m.b. Determine how long it will take the output signal to stay within 10% of its final value. You can model the driver as a voltage source with the driving device acting as a series resistance. Assume a supply and step voltage of 2.5V. Hint: draw the lattice diagram for the transmission line.c. Resize the dimensions of the driver to minimize the total delay.Figure 2. The driver, the connecting copper wire and the memory block being accessed.。

编者按:本习题册根据《数字电路制作与测试》项目式教学的内容,总结归纳了本课程需要掌握的主要知识点,并针对各个知识点,从不同的角度、以不同的形式出题供学生练习。

本习题册有填空题、判断题、分析与设计题等形式,学生可选择自己喜欢的形式进行练习使用。

当然,大学的学习不同高中阶段的学习,以课堂听讲、消化理解、思考提问、实践练习为主要学习手段,不提倡学生沉溺于题海,由于项目式课程的学习内容比较宽泛、动手实践的机会较多,很多学生忽视了基本知识的掌握,在此编辑本习题册旨在帮助学生强化基本概念的掌握,若有了扎实的理论、正确的概念,那么得出正确的实践结果将更加快捷,实践中所遇问题便会迎刃而解,可进一步锻炼分析问题和解决问题的能力。

愿本习题册能帮助学生及时解决学习中出现的问题,轻松地进行《数字电路制作与测试》项目式课程的学习。

编者2014年2月项目一加法器电路的设计与测试主要知识点:1.模拟信号特点2.数字信号特点3.数制和码制1)十进制、二进制、八进制、十六进制2)进制之间互相转换3)BCD码4)格雷码4.基本门电路逻辑功能及描述方法5.复合门电路逻辑功能及描述方法6.TTL特殊门电路OC门和三态门7.CMOS特殊门电路OD门、CMOS三态门及CMOS传输门*8.TTL和CMOS电路的外部特性和使用方法9.逻辑代数的基本定律和规则(十条规律、三个规则及常用公式的证明)10.逻辑函数的表示方法(逻辑表达式、逻辑符号、真值表、波形图等)11.逻辑函数的变换和化简(公式法化简、卡诺图化简、具有无关项的卡诺图的化简、Multisim化简)12.逻辑函数表达式(一般表达式、最小项表达式、最大项表达式)13.组合逻辑电路的分析和设计方法一、判断题:1.通常电信号可以分为模拟信号和数字信号,如语音信号就是一种数字信号。

()2.模拟信号在幅值和时间上都是连续的,而数字信号则是离散的,因此他们之间不能相互转换。

()3.实际数字系统中,数字信号不可能立即上升或下降,通常将从低向高变化过渡的时间定义为上升时间t r,指波形从幅值的10%到100%所经历的时间。

说明:[难度等级(E容易M中等C难),需要的设计工具,与之相关的章节]第5章CMOS反相器4. [E, None, 3.3.3]对于图5.3中的输出负载为3pF的反相器:a. 计算t plh,t phl和t pb. 上升延时和下降延时是否相等?为什么?c. 计算静态和动态功耗,假设门的时钟频率尽可能的快。

图5.3 电阻负载反相器7. 考虑图5.5中的电路。

器件M1是一个标准的NMOS器件。

器件M2除了阈值电压为负并且其值为-0.4V之外,和M1有共同的特性。

假设耗尽型器件M2的所有电流公式和不等式(来决定工作模式)与规范的NMOS器件相同。

并假设输入IN有0V到2.5V的摆幅。

图5.5 一个耗尽型负载的NMOS反相器a.器件M2的栅极和源极相连。

如果V IN =0V,那么输出电压是多少?在稳态,对于这个输入,器件M2的工作模式是什么?b.计算V IN =2.5V时的输出电压。

为简化计算,你可以假设V OUT很小。

在稳态,对于这个输入,器件M2的工作模式是什么?c.假设Pr(LN=0)=0.3,这个电路的静态功耗是多少?8. [M, None, 3.3.3]一个NMOS晶体管用来向一个大电容充电,如图5.6所示:a. 确定这个电路的t pLH,假设输入节点有一个0到2.5V的理想阶跃信号。

b. 假设一个5kΩ的电阻R S用来对电容放电至地,确定t pHL的值。

c. 确定在对电容充电期间从电源得到多少能量。

其中多少能量在M1中被消耗?在放电期间,多少能量在下拉电阻上消耗?当R S减小至1kΩ时又是多少?d. NMOS晶体管用一个PMOS器件代替,k p和原先NMOS的k n相等。

替换后的结构是否比以前快?解释为什么。

图5.6 注明W/L比的电路图12. 考虑图5.9的低摆幅驱动:a. 输出节点(V out)的电压摆幅是多少?假设γ =0。

b. 输入端有一个从0V 到2.5V的翻转,估算(i)来自于电源的能量和(ii)能量损耗。

2011-2012《数字VLSI》第一次课程作业

(一) 考虑图一的静态互补CMOS逻辑门, 写出它的布尔表达式,并画出下拉网络的结构。

(二)图二中假设所有NMOS器件的衬底均接地,电源电压为2.5V。

设输入 IN 的摆幅为 0V 至 2.5V,NMOS管的V T0 = 0.54V,|ΦF|=0.32V。

考虑静态情形,并忽略寄生电容。

(1)设衬偏系数γ=0,晶体管M2工作在什么模式(线性?饱和?截止?) (2)设衬偏系数γ=0,当IN = 0V 时,OUT = ?

(3)设衬偏系数γ=0.5,求节点X 处的电压。

(三) 如图三所示电路,已知M1的V T0=0.43V,V DSAT=0.63V,k’=115×10‐6A/V2,沟道尺寸如图所示,单位沟道长度的覆盖电容Cgso=Cgdo=0.31fF/μm,单位面积的氧化层电容Cox=6 fF/μm2。

请计算(忽略体效应和沟道长度调制效应):

(1) 当Vin = 2.5 V时Vout 的稳态电压(记为VOL)是多少?M1管处在什么工作区? (2) 如果Vin从0V上升到 2.5 V,而Vout的初始电压等于2.5V,那么从In端变化开始到Vout达到稳态这个过程中由In端注入的总净电荷量等于多少?

图 一

图 二

图 三。